Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                               |

|----------------------------|-----------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                        |

| Core Processor             | MIPS32® microAptiv™                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                            |

| Speed                      | 200MHz                                                                                        |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, SQI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT                            |

| Number of I/O              | 120                                                                                           |

| Program Memory Size        | 1MB (1M x 8)                                                                                  |

| Program Memory Type        | FLASH                                                                                         |

| EEPROM Size                | -                                                                                             |

| RAM Size                   | 640K x 8                                                                                      |

| /oltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                   |

| Data Converters            | A/D 45x12b                                                                                    |

| Oscillator Type            | Internal                                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                             |

| Mounting Type              | Surface Mount                                                                                 |

| Package / Case             | 169-LFBGA                                                                                     |

| Supplier Device Package    | 169-LFBGA (11x11)                                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1064dag169t-i-6j             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 7-3: INTERRUPT REGISTER MAP (CONTINUED)

| ess                         |                                 | 4         |       |           |       |       |       |       |             |         | Bits     |      |      |      |      |      |       |             |            |

|-----------------------------|---------------------------------|-----------|-------|-----------|-------|-------|-------|-------|-------------|---------|----------|------|------|------|------|------|-------|-------------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14     | 29/13 | 28/12 | 27/11 | 26/10 | 25/9        | 24/8    | 23/7     | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0        | All Resets |

|                             | OFF1                            | 56 31:1   |       | _         | _     | _     | _     | _     | _           |         | _        | _    | _    | _    | _    | _    | VOFF< | <17:16>     | 0000       |

|                             |                                 | 15:0      |       |           |       |       |       |       |             | VOFF<1  |          |      |      | 1    | 1    |      |       | _           | 0000       |

| 07B4                        | OFF1                            | 57 31:1   |       | _         | _     | _     | _     | _     | _           | _       | _        | _    | _    | _    | _    | _    | VOFF  | <17:16>     | 0000       |

|                             |                                 | 15:0      |       |           |       |       |       |       |             | VOFF<1  | 5:1>     |      |      | 1    | 1    |      |       | _           | 0000       |

| 07B8                        | OFF1                            | 58 31:1   |       | _         | _     | _     | _     | _     | _           |         | _        | _    | _    | _    | _    | _    | VOFF  | <17:16>     | 0000       |

|                             |                                 | 15:0      |       |           |       |       |       |       |             | VOFF<1  |          |      |      |      |      |      |       |             | 0000       |

| 07BC                        | OFF1                            | 59 31:1   |       | _         | _     | _     | _     | _     | _           |         | _        | _    | _    | _    | _    | _    | VOFF  | <17:16>     | 0000       |

|                             |                                 | 15:0      |       |           |       |       |       |       |             | VOFF<1  |          |      |      |      |      |      |       |             | 0000       |

| 07C0                        | OFF1                            | 60 31:1   |       | _         | _     | _     | _     | _     | _           |         |          | _    | _    | _    | _    | _    | VOFF  | <17:16>     | 0000       |

|                             |                                 | 15:0      |       |           |       |       |       |       |             | VOFF<1  |          |      | ı    |      |      |      |       |             | 0000       |

| 07C4                        | OFF1                            | 61 31:1   |       | _         | _     | _     | _     | _     | _           |         | _        | _    | _    | _    | _    | _    | VOFF  | <17:16>     | 0000       |

|                             |                                 | 15:0      |       | 1         | 1     | 1     |       |       |             | VOFF<1  |          |      | 1    |      |      |      |       |             | 0000       |

| 07C8                        | OFF1                            | 62 31:1   |       | _         | _     | _     | _     | _     | _           |         | _        | _    | _    | _    | _    | _    | VOFF  | <17:16>     | 0000       |

|                             |                                 | 15:0      |       | 1         | 1     | 1     |       |       |             | VOFF<1  |          |      | ı    |      |      | 1    |       | <u> </u>    | 0000       |

| 07CC                        | OFF1                            | 63 31:1   |       | _         | _     | _     | _     | _     | _           |         |          | _    | _    | _    | _    | _    | VOFF  | <17:16>     | 0000       |

|                             |                                 | 15:0      |       | 1         | 1     | 1     |       |       |             | VOFF<1  |          |      | 1    |      |      |      |       |             | 0000       |

| 07D0                        | OFF1                            | 64 31:1   |       | _         | _     | _     | _     | _     | _           |         |          | _    | _    | _    | _    | _    | VOFF  | <17:16>     | 0000       |

|                             |                                 | 15:0      |       |           |       |       |       |       |             | VOFF<1  |          |      |      |      |      |      | VOEE  |             | 0000       |

| 07D4                        | OFF1                            | 65 31:1   |       | _         | _     | _     | _     | _     | _           | -       |          | _    | _    | _    | _    | _    | VOFF  | <17:16>     | 0000       |

|                             |                                 | 15:0      |       |           |       |       |       |       |             | VOFF<1  |          |      |      |      |      |      | VOEE  |             | 0000       |

| 07D8                        | OFF1                            | 66 31:1   |       | _         | _     | _     | _     | _     | _           |         |          | _    | _    | _    | _    | _    | VOFF  | <17:16>     | 0000       |

|                             |                                 | 15:0      |       |           |       |       |       |       |             | VOFF<1  | 5:1>     |      |      |      |      |      | VOEE  | <u> </u>    | 0000       |

| 07DC                        | OFF1                            | 67 31:1   |       | _         | _     | _     | _     | _     | _           | VOFF<1  | <u> </u> | _    | _    | _    | _    | _    | VOFF  | <17:10>     | 0000       |

|                             |                                 | 31:1      |       |           |       |       |       |       |             | VUFF<1  | 0:1>     |      |      |      |      |      | VOEE  |             | 0000       |

| 07E0                        | OFF1                            | 68 31.1   |       | _         | _     | _     | _     |       |             | VOFF<1  |          | _    | _    | _    | _    | _    | VOFF  | 17.10       | 0000       |

|                             |                                 | 31:1      |       | _         |       |       |       |       | _           | VOFF    | -        |      | _    | _    | _    |      | VOEE  |             | 0000       |

| 07E4                        | OFF1                            | 69 15:0   |       | _         | _     | _     | _     | _     | _           | VOFF<1  |          | _    | _    | _    | _    | _    | VOFF  | 17.10       | 0000       |

|                             |                                 | 31:1      |       | _         | _     | _     | _     | _     | _           | VOFF(1) | -        | _    | _    |      | _    | _    | VOEE  |             | 0000       |

| 07E8                        | OFF1                            | 70 31.1   |       | _         | _     | _     | _     | _     | _           | VOFF<1  |          | _    | _    | _    | _    | _    | VOFF  | 17.10       | 0000       |

|                             |                                 | 31:1      |       |           |       |       |       |       | _           | VOFF    | _        | _    |      | _    | _    | _    | VOEE  |             | _          |

| 07EC                        | OFF1                            | 71 15:0   |       | _         | _     | _     | _     |       |             | VOFF<1  |          | _    | _    | _    | _    | _    | VOFF  | 17.10       | 0000       |

|                             |                                 | _         |       |           |       |       |       |       | _           | VOFF    |          | _    |      | _    | _    | _    | VOEE  | <u> </u>    |            |

| 07F0                        | OFF1                            | 72 31:1   |       | _         | _     | _     | _     | _     | _           | VOFF<1  |          | _    | _    | _    | _    | _    | VOFF  |             | 0000       |

|                             |                                 | 31:1      |       | _         |       |       |       |       |             |         |          |      |      |      |      |      | VOEE  | <u> </u>    |            |

| 07F4                        | OFF1                            | 73 15:0   |       | _         | _     | _     | _     | _     | _           | VOFF<1  | <u> </u> | _    | _    | _    | _    | _    | VUFF* | -11.10>     | 0000       |

|                             | <u> </u>                        |           |       |           |       |       |       |       |             | VUFF<1  |          |      |      |      |      | _    | VOEE  | <br><17:16> | 0000       |

| 07F8                        | OFF1                            | 74 31:1   |       | _         | _     | _     | _     | _     | _           | VOFF<1  | <u> </u> | _    | _    | _    | _    | _    | VUFF  |             | 0000       |

| Logon                       | 1                               |           |       | on Posot: |       |       |       |       | chown in ho |         | 0.14     |      |      |      |      |      |       | _           | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

<sup>2:</sup> This bit is only available on devices with a Crypto module.

# REGISTER 11-6: USBIE0CSR2: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 2 (ENDPOINT 0)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | -                 | _                 | _                 |                   |                   | NAKLIM<4:0>       |                  |                  |

| 23:16        | R/W-0             | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | SPEE              | D<1:0>            | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 13.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7.0          | U-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          | _                 |                   |                   |                   | RXCNT<6:0>        |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-29 Unimplemented: Read as '0'

bit 28-24 NAKLIM<4:0>: Endpoint 0 NAK Limit bits

The number of frames/microframes (Hi-Speed transfers) after which Endpoint 0 should time-out on receiving a stream of NAK responses.

bit 23-22 SPEED<1:0>: Operating Speed Control bits

11 = Low-Speed

10 = Full-Speed

01 = Hi-Speed

00 = Reserved

bit 21-7 **Unimplemented:** Read as '0'

bit 6-0 RXCNT<6:0>: Receive Count bits

The number of received data bytes in the Endpoint 0 FIFO. The value returned changes as the contents of the FIFO change and is only valid while the RXPKTRDY bit is set.

**NOTES:**

#### REGISTER 22-4: SQI1CON: SQI CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 04:04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | r-0              | R/W-0                 |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | SCHECK <sup>(1)</sup> |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 23:16        | DDRMODE           | DASSERT           | DEVSE             | L<1:0>            | LANEMO            | DDE<1:0>          | CMDIN            | IIT<1:0>              |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 15:8         |                   |                   |                   | TXRXCOU           | NT<15:8>          |                   |                  |                       |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 7:0          |                   |                   |                   | TXRXCOU           | INT<7:0>          |                   |                  |                       |

Legend:r = ReservedR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-26 Unimplemented: Read as '0'

bit 25 Reserved: Must be programmed as '0'

bit 24 **SCHECK:** Flash Status Check bit<sup>(1)</sup>

1 = Check the status of the Flash

0 = Do not check the status of the Flash

bit 23 **DDRMODE:** Double Data Rate Mode bit

1 = Set the SQI transfers to DDR mode

0 = Set the SQI transfers to SDR mode

bit 22 DASSERT: Chip Select Assert bit

1 = Chip Select is deasserted after transmission or reception of the specified number of bytes

0 = Chip Select is not deasserted after transmission or reception of the specified number of bytes

bit 21-20 DEVSEL<1:0>: SQI Device Select bits

11 = Reserved

10 = Reserved

01 = Select Device 1

00 = Select Device 0

bit 19-18 LANEMODE<1:0>: SQI Lane Mode Select bits

11 = Reserved

10 = Quad Lane mode

01 = Dual Lane mode

00 = Single Lane mode

bit 17-16 CMDINIT<1:0>: Command Initiation Mode Select bits

If it is Transmit, commands are initiated based on a write to the transmit register or the contents of TX buffer. If CMDINIT is Receive, commands are initiated based on reads to the read register or RX buffer availability.

11 = Reserved

10 = Receive

01 = Transmit

00 = Idle

bit 15-0 TXRXCOUNT<15:0>: Transmit/Receive Count bits

These bits specify the total number of bytes to transmit or received (based on CMDINIT).

**Note 1:** When this bit is set to '1', the SQI module uses the SQI1MEMSTAT register to control the status check command process.

#### REGISTER 25-5: PMDIN: PARALLEL PORT INPUT DATA REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 | _                 | _                 | _                 |                   | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.6         |                   |                   |                   | DATAIN<           | 15:8>             |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              |                   |                   |                   | DATAIN<           | <7:0>             |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 **DATAIN<15:0>:** Port Data Input bits

This register is used for both Parallel Master Port mode and Enhanced Parallel Slave mode.

In Parallel Master mode, a write to the MSB triggers the write transaction on the PMP port. Similarly, a read to the MSB triggers the read transaction on the PMP port.

When MODE16 = 1, MSB = DATAIN<15:8>. When MODE16 = 0, MSB = DATAIN<7:0>.

Note: This register is not used in Dual Buffer Master mode (i.e., DUALBUF bit (PMPCON<17>) = 1).

### 26.1 EBI Control Registers

### TABLE 26-1: EBI REGISTER MAP

|                             | LE 20-1.         |               | I ILC  | SIEKI    | 117-31 |             |          |           |         |              |                  |          |          |       |          |           |            |        |              |

|-----------------------------|------------------|---------------|--------|----------|--------|-------------|----------|-----------|---------|--------------|------------------|----------|----------|-------|----------|-----------|------------|--------|--------------|

| ess                         | <del>-</del>     |               |        |          |        |             |          |           |         |              | Bits             |          |          |       |          |           |            |        | "            |

| Virtual Address<br>(BF8E_#) | Register<br>Name | Bit Range     | 31/15  | 30/14    | 29/13  | 28/12       | 27/11    | 26/10     | 25/9    | 24/8         | 23/7             | 22/6     | 21/5     | 20/4  | 19/3     | 18/2      | 17/1       | 16/0   | All Resets   |

| 1014                        | EBICS0           | 31:16         |        |          |        |             |          |           |         | С            | SADDR<15:0       | >        |          |       |          |           |            |        | 2000         |

| 1014                        | EDICOU           | 15:0          | _      | _        | _      | _           | _        | -         | _       | _            | _                | _        | _        | _     | _        | _         | _          | _      | 0000         |

| 1018                        | EBICS1           | 31:16         |        |          |        |             |          |           |         | С            | SADDR<15:0       | >        |          |       |          |           |            |        | 1000         |

| 1010                        | LDICOT           | 15:0          |        | _        | _      | _           | _        | _         | _       | _            | _                | _        | _        | _     | _        | _         | _          | _      | 0000         |

| 101C                        | EBICS2           | 31:16         |        |          |        |             |          |           |         | С            | SADDR<15:0       | >        |          |       |          |           |            |        | 2040         |

| 1010                        | LDIOOZ           | 15:0          | _      | _        | _      | _           | _        | _         | _       | _            | _                | _        | _        | _     | _        | _         | _          | _      | 0000         |

| 1020                        | EBICS3           | 31:16         |        |          |        |             |          |           |         | С            | SADDR<15:0       | >        |          |       |          |           |            |        | 1040         |

| 1020                        | LDIOOO           | 15:0          | _      | _        | _      | _           | _        | _         | _       | _            | _                | _        | _        | _     | _        | _         | _          | _      | 0000         |

| 1054                        | EBIMSK0          | 31:16         |        | _        |        | _           | _        | _         | _       | _            | _                | _        | _        | _     | _        | _         | _          | _      | 0000         |

|                             |                  | 15:0          |        | _        |        |             | _        | REC       | SEL<2:0 | >            | M                | EMTYPE<2 | 2:0>     |       | М        | EMSIZE<4: | 0>         | 1      | 0020         |

| 1058                        | EBIMSK1          | 31:16         |        | _        |        |             | _        | _         | _       | _            | _                | _        | _        |       | _        | _         | _          | _      | 0000         |

|                             |                  | 15:0          |        | _        | _      | _           | _        | REC       | SEL<2:0 | >            | M                | EMTYPE<2 | 2:0>     |       | M        | EMSIZE<4: | 0>         | 1      | 0020         |

| 105C                        | EBIMSK2          | 31:16         |        | _        | _      | _           | _        | _         | _       | _            | _                | _        | _        |       | _        | _         | _          | _      | 0000         |

|                             |                  | 15:0          |        | _        | _      |             | _        | REC       | SEL<2:0 | <b> &gt;</b> |                  | EMTYPE<2 |          |       | M        | EMSIZE<4  |            |        | 0120         |

| 1060                        | EBIMSK3          | 31:16         |        | _        |        | _           | _        |           |         | _            | _                |          | _        | _     | <u> </u> |           | _          | _      | 0000         |

|                             |                  | 15:0          |        | _        |        |             |          |           | SEL<2:0 |              |                  | EMTYPE<2 |          |       | M        | EMSIZE<4: |            |        | 0120         |

| 1094                        | EBISMT0          | 31:16         |        | _        |        |             | _        | RDYMODE   |         |              | PAGEMODE         |          | TPRC<    | <3:0> | TDO      |           | TBTA<2:0>  |        | 041C         |

|                             |                  | 15:0          |        |          | I VVI  | P<5:0>      |          | DDVMODE   | TWR     |              | TAS<             |          | TDDO     | ٠٥.٥٠ | TRC<     |           | TDTA 40.05 |        | 2D4B         |

| 1098                        | EBISMT1          | 31:16<br>15:0 |        | _        |        | —<br>P<5:0> | _        | RDYMODE   | TWR     |              | PAGEMODE<br>TAS< |          | TPRC<    | 3:0>  | TDC      |           | TBTA<2:0>  |        | 041C         |

|                             |                  |               |        |          | I VVI  | P<5:0>      |          | DDVMODE   |         |              | PAGEMODE         |          | TPRC<    | 2.05  | TRC<     |           | TBTA<2:0>  |        | 2D4B<br>041C |

| 109C                        | EBISMT2          | 31:16<br>15:0 |        | _        |        | P<5:0>      | _        | RUTIVIOUE | TWR     |              | TAS<             | L        | IPRU     | ·3.U> | TRC<     |           | 1B1A\2.0>  |        | 2D4B         |

|                             |                  | 31:16         |        |          | I      | P<5.0>      |          |           | IVVR    | < 1.U>       | IASS             | 1.0>     |          | _     |          | 5.0>      |            |        | 0000         |

| 10A0                        | EBIFTRPD         | 15:0          |        | _        | _      |             | _        | _         |         | _            | _                |          | PD<11:0> | _     | _        | _         | _          | _      | 0000         |

|                             |                  | 31:16         |        |          |        |             | _        |           |         |              |                  |          | PD<11.0> | l –   | _        | _         | _          | _      | 0000         |

| 10A4                        | EBISMCON         | 15:0          |        | WIDTH2<2 |        |             | <u> </u> | 2:0>      | - 51    | I <u> </u>   |                  | _        |          |       |          |           |            | SMRP   | 0201         |

|                             |                  |               | الالاق |          |        |             |          | -2.0/     | 1       |              |                  |          | _        | _     | _        | _         | _          | SIVINE | UZUI         |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## REGISTER 29-21: ADCCMPCONX: ADC DIGITAL COMPARATOR 'x' CONTROL REGISTER ('x' = 2 THROUGH 6)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | R-0, HS, HC       | R-0, HS, HC       | R-0, HS, HC       | R-0, HS, HC      | R-0, HS, HC      |

| 13.0         | _                 | _                 | _                 |                   |                   | AINID<4:0>        |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R-0, HS, HC       | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | ENDCMP            | DCMPGIEN          | DCMPED            | IEBTWN            | IEHIHI            | IEHILO            | IELOHI           | IELOLO           |

Legend:HS = Hardware SetHC = Hardware ClearedR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### bit 31-13 Unimplemented: Read as '0'

bit 12-8 AINID<4:0>: Digital Comparator 'x' Analog Input Identification (ID) bits

When a digital comparator event occurs (DCMPED = 1), these bits identify the analog input being monitored by the Digital Comparator.

**Note:** Only analog inputs <31:0> can be processed by the Digital Comparator module 'x' ('x' = 1-5).

11111 = AN31 is being monitored 11110 = AN30 is being monitored

•

00001 = AN1 is being monitored 00000 = AN0 is being monitored

- bit 7 **ENDCMP:** Digital Comparator 'x' Enable bit

- 1 = Digital Comparator 'x' is enabled

- 0 = Digital Comparator 'x' is not enabled, and the DCMPED status bit (ADCCMPxCON<5>) is cleared

- bit 6 **DCMPGIEN:** Digital Comparator 'x' Global Interrupt Enable bit

- 1 = A Digital Comparator 'x' interrupt is generated when the DCMPED status bit (ADCCMPxCON<5>) is set

- 0 = A Digital Comparator 'x' interrupt is disabled

- bit 5 **DCMPED:** Digital Comparator 'x' "Output True" Event Status bit

The logical conditions under which the digital comparator gets "True" are defined by the IEBTWN, IEHIHI, IEHILO, IELOHI and IELOLO bits.

**Note:** This bit is cleared by reading the AINID<5:0> bits (ADCCMP0CON<13:8>) or by disabling the Digital Comparator module (by setting ENDCMP to '0').

- 1 = Digital Comparator 'x' output true event has occurred (output of Comparator is '1')

- 0 = Digital Comparator 'x' output is false (output of Comparator is '0')

- bit 4 **IEBTWN:** Between Low/High Digital Comparator 'x' Event bit

- 1 = Generate a digital comparator event when the DCMPLO<15:0> bits ≤ DATA<31:0> bits < DCMPHI<15:0> bits

- 0 = Do not generate a digital comparator event

- bit 3 **IEHIHI:** High/High Digital Comparator 'x' Event bit

- 1 = Generate a Digital Comparator ' $\vec{x}$  Event when the DCMPHI<15:0> bits  $\leq$  DATA<31:0> bits

- 0 = Do not generate an event

- bit 2 **IEHILO:** High/Low Digital Comparator 'x' Event bit

- 1 = Generate a Digital Comparator 'x' Event when the DATA<31:0> bits < DCMPHI<15:0> bits

- 0 = Do not generate an event

#### REGISTER 29-32: ADCANCON: ADC ANALOG WARM-UP CONTROL REGISTER (CONTINUED)

bit 7 ANEN7: Shared ADC (ADC7) Analog and Bias Circuitry Enable bit

- 1 = Analog and bias circuitry enabled. Once the analog and bias circuit is enabled, the ADC module needs a warm-up time, as defined by the WKUPCLKCNT<3:0> bits.

- 0 = Analog and bias circuitry disabled

- bit 5-6 **Unimplemented:** Read as '0'

- bit 4-0 ANEN4: ANEN0: ADC4-ADC0 Analog and Bias Circuitry Enable bits

- 1 = Analog and bias circuitry enabled. Once the analog and bias circuit is enabled, the ADC module needs a warm-up time, as defined by the WKUPCLKCNT<3:0> bits.

- 0 = Analog and bias circuitry disabled

#### 31.1 **Ethernet Control Registers**

### TABLE 31-3: ETHERNET CONTROLLER REGISTER SUMMARY

| SSS                         |                                 | -             |       |                   |              |       |       |       |              | Ві           | its          |               |        |        |         |         |         |               |            |

|-----------------------------|---------------------------------|---------------|-------|-------------------|--------------|-------|-------|-------|--------------|--------------|--------------|---------------|--------|--------|---------|---------|---------|---------------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14             | 29/13        | 28/12 | 27/11 | 26/10 | 25/9         | 24/8         | 23/7         | 22/6          | 21/5   | 20/4   | 19/3    | 18/2    | 17/1    | 16/0          | All Resets |

| 2000                        | ETHOOM4                         | 31:16         |       |                   |              |       |       |       |              | PTV<         | :15:0>       |               |        |        |         |         |         |               | 0000       |

| 2000                        | ETHCON1                         | 15:0          | ON    | _                 | SIDL         | _     | _     | _     | TXRTS        | RXEN         | AUTOFC       | _             | _      | MANFC  | _       | _       | _       | BUFCDEC       | 0000       |

| 2010                        | ETHCON2                         | 31:16         |       | _                 | _            | _     | ı     | _     | _            | _            | _            | _             | _      | _      | _       | _       | _       | _             | 0000       |

|                             | 211100112                       | 15:0          |       | _                 | _            | _     | _     |       |              |              | XBUFSZ<6:0   | )>            |        |        | _       | _       | _       | _             | 0000       |

| 2020                        | ETHTXST                         | 31:16         |       |                   |              |       |       |       | =:/0=:=      | TXSTADE      | )R<31:16>    |               |        |        |         |         |         |               | 0000       |

|                             |                                 | 15:0          |       |                   |              |       |       |       | TXSTADE      |              | ND +04+40+   |               |        |        |         |         | _       | _             | 0000       |

| 2030                        | ETHRXST                         | 31:16<br>15:0 |       |                   |              |       |       |       | DVCTADI      |              | DR<31:16>    |               |        |        |         |         |         |               | 0000       |

|                             |                                 | 31:16         |       | RXSTADDR<15:2>    |              |       |       |       |              |              |              |               |        |        |         |         |         |               |            |

| 2040                        | ETHHT0                          | 15:0          |       | HI<31:0>          |              |       |       |       |              |              |              |               |        |        |         |         |         |               |            |

|                             |                                 | 31:16         |       |                   |              |       |       |       |              |              |              |               |        |        |         |         |         |               | 0000       |

| 2050                        | ETHHT1                          | 15:0          |       |                   |              |       |       |       |              | HT<6         | 3:32>        |               |        |        |         |         |         |               | 0000       |

| 2000                        | ET. 101 41 40                   | 31:16         |       | 9000<br>PMM<31:0> |              |       |       |       |              |              |              |               |        |        |         |         |         |               |            |

| 2060                        | ETHPMM0                         | 15:0          |       |                   |              |       |       |       |              | PMM          | <31:0>       |               |        |        |         |         |         |               | 0000       |

| 2070                        | ETHPMM1                         | 31:16         |       |                   |              |       |       |       |              | DMM<         | 63:32>       |               |        |        |         |         |         |               | 0000       |

| 2070                        |                                 | 15:0          |       |                   |              |       |       |       |              | 1 IVIIVI S   |              |               |        |        |         |         |         |               | 0000       |

| 2080                        | ETHPMCS                         | 31:16         |       | _                 | _            | _     | _     | _     | _            | _            | _            | _             | _      | _      | _       | _       | _       | _             | 0000       |

|                             |                                 | 15:0          |       |                   |              |       |       |       |              | PMCS         | <15:0>       |               | _      |        |         |         |         |               | 0000       |

| 2090                        | ETHPMO                          | 31:16<br>15:0 |       | _                 | _            | _     | _     | _     | _            | - PMO        | —<br><15:0>  | _             | _      | _      | _       | _       | _       | _             | 0000       |

|                             |                                 | 31:16         | _     | _                 | _            | _     | _     | _     | _            |              | _            | _             | _      | _      | _       | _       | _       | _             | 0000       |

| 20A0                        | ETHRXFC                         |               |       |                   |              |       |       |       |              |              | CRC          | CRC           | RUNT   |        |         | NOT     |         |               |            |

|                             |                                 | 15:0          | HTEN  | MPEN              | _            | NOTPM |       | PMMOI | DE<3:0>      |              | ERREN        | OKEN          | ERREN  | RUNTEN | UCEN    | MEEN    | MCEN    | BCEN          | 0000       |

| 20B0                        | ETHRXWM                         | 31:16         |       | _                 | _            | _     | _     | _     | _            | _            |              |               |        |        | M<7:0>  |         |         |               | 0000       |

|                             |                                 | 15:0          |       | _                 | _            | _     |       | _     | _            | _            |              |               |        |        | M<7:0>  |         |         |               | 0000       |

| 20C0                        | ETHIEN                          | 31:16         |       |                   |              |       | _     | _     | -            |              |              |               | RX     |        | TX      | TX      | RX      | —<br>PV       | 0000       |

| 2000                        | LITTILIN                        | 15:0          | _     | TX<br>BUSEIE      | RX<br>BUSEIE | _     | _     | _     | EW<br>MARKIE | FW<br>MARKIE | RX<br>DONEIE | PK<br>TPENDIE | ACTIE  | _      | DONEIE  | ABORTIE | BUFNAIE | RX<br>OVFLWIE | 0000       |

| 20D0                        | ETHIRQ                          | 31:16         | _     |                   | _            | _     | -     | _     | _            | _            | _            | _             | _      | _      |         | _       |         | _             | 0000       |

| 2000                        | LIHIKU                          | 15:0          | _     | TXBUSE            | RXBUSE       | _     | -     | -     | EWMARK       | FWMARK       | RXDONE       | PKTPEND       | RXACT  | _      | TXDONE  | TXABORT | RXBUFNA | RXOVFLW       | 0000       |

| 20E0                        | ETHSTAT                         | 31:16         | _     | _                 | _            | _     | _     | _     | _            | _            |              |               |        | BUFC   | NT<7:0> |         |         |               | 0000       |

| 2000                        | LITIOIAI                        | 15:0          |       | _                 | _            | _     | _     | _     | _            | _            | BUSY         | TXBUSY        | RXBUSY | _      | _       | _       | _       | _             | 0000       |

| 2100                        | ETH                             | 31:16         | _     | _                 | _            | _     | _     | _     | _            | _            | _            | _             | _      | _      | _       | _       | _       | _             | 0000       |

|                             | RXOVFLOW                        | 15:0          | b D.  |                   |              |       |       |       |              | RXOVFLW      | CNT<15:0>    |               |        |        |         |         |         |               | 0000       |

Legend:

PIC32MZ Graphics (DA) Family

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table (with the exception of ETHSTAT) have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

Reset values default to the factory programmed value.

#### REGISTER 31-38: EMAC1SA1: ETHERNET CONTROLLER MAC STATION ADDRESS 1 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | 1                 | _                 | _                 | _                 |                  | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | 1                 | _                 | _                 | _                 |                  |                  |

| 15:8         | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P            | R/W-P            |

| 15.6         |                   |                   |                   | STNADDI           | R4<7:0>           |                   |                  |                  |

| 7:0          | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P            | R/W-P            |

| 7.0          |                   |                   |                   | STNADDI           | R3<7:0>           |                   |                  |                  |

Legend:

P = Programmable bit

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as '0'

-n = Value at POR

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-8 STNADDR4<7:0>: Station Address Octet 4 bits

These bits hold the fourth transmitted octet of the station address.

bit 7-0 STNADDR3<7:0>: Station Address Octet 3 bits

These bits hold the third transmitted octet of the station address.

**Note 1:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

2: This register is loaded at reset from the factory preprogrammed station address.

#### REGISTER 35-1: CTMUCON: CTMU CONTROL REGISTER (CONTINUED)

```

bit 9

IDISSEN: Analog Current Source Control bit(2)

1 = Analog current source output is grounded

0 = Analog current source output is not grounded

bit 8

CTTRIG: Trigger Control bit

1 = Trigger output is enabled

0 = Trigger output is disabled

bit 7-2

ITRIM<5:0>: Current Source Trim bits

011111 = Maximum positive change from nominal current

011110

000001 = Minimum positive change from nominal current

000000 = Nominal current output specified by IRNG<1:0>

111111 = Minimum negative change from nominal current

100010

100001 = Maximum negative change from nominal current

bit 1-0

IRNG<1:0>: Current Range Select bits<sup>(3)</sup>

11 = 100 times base current

10 = 10 times base current

```

01 = Base current level 00 = 1000 times base current<sup>(4)</sup>

- **Note 1:** When this bit is set for Pulse Delay Generation, the EDG2SEL<2:0> bits must be set to '1110' to select the C2OUT pin.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 44-20) in **Section 44.0** "Electrical Characteristics" for current values.

- **4:** This bit setting is not available for the CTMU temperature diode.

# REGISTER 36-14: GLCDLxRES: GRAPHICS LCD CONTROLLER LAYER 'x' RESOLUTION REGISTER ('x' = 0-2)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | _                 | _                 | _                 | _                 | _                 |                   | RESX<10:8>       |                  |

| 22.46        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        |                   |                   |                   | RESX<             | <7:0>             |                   |                  |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | _                 | _                 | _                 | _                 |                   | RESY<10:8>       |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | RESY<             | <7:0>             |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-27 Unimplemented: Read as '0'

bit 26-16 RESX<10:0>: X Dimension Layer Pixel Resolution bits

These bits specify the layer pixel resolution in the X dimension.

bit 15-11 Unimplemented: Read as '0'

bit 10-0 RESY<10:0>: Y Dimension Layer Pixel Resolution bits

These bits specify the layer pixel resolution in the Y dimension.

# REGISTER 36-19: GLCDCURLUTx: GRAPHICS LCD CONTROLLER CURSOR LUT REGISTER 'x' ('x' = 0-15)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                 | -                 | _                 | -                 | -                | _                |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        |                   |                   |                   | RED<              | 7:0>              |                   |                  |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | GREEN             | <7:0>             |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | BLUE<             | 7:0>              |                   |                  | ·                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-24 Unimplemented: Read as '0'

bit 23-16 RED<7:0>: Cursor Lookup Table Red Component bit

bit 15-8 GREEN<7:0>: Cursor Lookup Table Green Component bit

bit 7-0 BLUE<7:0>: Cursor Lookup Table Blue Component bit

Note: The bits in this register contain the 8-bit RGB color value (0-255).

#### REGISTER 38-1: DDRTSEL: DDR TARGET SELECT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 |                   |                   |                   |                  | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 |                   |                   |                   |                  | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 13.6         | _                 | _                 | _                 |                   |                   |                   |                  | _                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   |                   |                   | TSEL              | <7:0>             |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-0 TSEL<7:0>: Target Select bits

These bits select the target to program arbitration parameters. This field must be set before an arbitration parameter is programmed for a target. The value in this field represents the target number (0-4) multiplied by the field size of the arbitration parameter.

REGISTER 38-4: DDRMINCMD: DDR MINIMUM COMMAND REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

|              | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |

| 7.0          | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |

| 7:0          | MINCMD<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-0 MINCMD<7:0>: Minimum Command bits

These bits in conjunction with the RQPER<7:0> bits (DDRRQPER<7:0>) determine the percentage of total bandwidth that is allocated to the target. If the number of DDR bursts specified by MINCMD<7:0> are not serviced for the target when it has been requesting access for (RQPER<7:0> \* 4) number of clocks, then the target's requests are treated with high priority until this condition becomes satisfied.

**Note:** The TSEL<7:0> bits (DDRTSEL<7:0>) must be programmed with the target number multiplied by the size of the MINLIMIT field (5) before this register is used to program the minimum burst limit for that target.

#### TABLE 44-8: DC CHARACTERISTICS: IDLE CURRENT (IDLE)

| DC CHARACTI                                               | ERISTICS               |         | Standard Operating Conditions: $V_{DDIO} = 2.2V$ to 3.6V, $V_{DDCORE} = 1.7V$ to 1.9V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |                        |  |  |

|-----------------------------------------------------------|------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|--|

| Parameter<br>No.                                          | Typical <sup>(2)</sup> | Maximum | Units                                                                                                                                                                                       | Conditions             |  |  |

| Idle Current (IIDLE): Core Off, Clock on Base Current (1) |                        |         |                                                                                                                                                                                             |                        |  |  |

| DC30                                                      | 19                     | 35      | mA                                                                                                                                                                                          | 8 MHz <sup>(3)</sup>   |  |  |

| DC31                                                      | 55                     | 70      | mA                                                                                                                                                                                          | 100 MHz <sup>(3)</sup> |  |  |

| DC32                                                      | 90                     | 123     | mA                                                                                                                                                                                          | 200 MHz                |  |  |

**Note 1:** The test conditions for IIDLE current measurements are as follows:

- VDDR1V8 = 1.8V

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL is disabled (USBPMD = 1), VUSB3V3 is connected to Vss, PBCLKx divisor = 1:2 ('x' ≠ 7)

- CPU is in Idle mode (CPU core Halted)

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared (except USBPMD)

- WDT, DMT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDDIO

- · RTCC and JTAG are disabled

- I/O Analog Charge Pump is disabled (IOANCPEN bit (CFGCON<7>) = 0)

- ADC Input Charge Pump is disabled (AICPMPEN bit (ADCCON1<12> = 0)

- 2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: This parameter is characterized, but not tested in manufacturing.

TABLE 44-11: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS (CONTINUED)

| DC CHARACTERISTICS |      |                                                                                                                                                                                                                                                                  | Standard Operating Conditions: $V_{DDIO} = 2.2V$ to 3.6V, $V_{DDCORE} = 1.7V$ to 1.9V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |      |      |       |                            |

|--------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|----------------------------|

| Param.             | Sym. | Characteristic                                                                                                                                                                                                                                                   | Min.                                                                                                                                                                                        | Тур. | Max. | Units | Conditions <sup>(1)</sup>  |

|                    |      | Output High Voltage I/O Pins 4x Sink Driver Pins - RA0-RA3, RA9, RA10, RA14, RA15 RB0, RB4, RB6, RB7, RB10, RB11, RB12, RB14 RC12-RC15 RD6, RD7, RD11, RD14 RE8, RE9 RF2, RF3, RF8, RF12 RG15 RH0, RH1, RH4-RH14 RJ0-RJ2, RJ8, RJ9, RJ11                         | 2.4                                                                                                                                                                                         | _    | _    | V     | IOH ≥ -10 mA, VDDIO = 3.3V |

| DO20               | Vон  | Output High Voltage I/O Pins: 8x Sink Driver Pins - RA4, RA5 RB2, RB3, RB5, RB8, RB9, RB13, RB14, RB15 RC1-RC4 RD0-RD3, RD9, RD10, RD12, RD13 RE0-RE7 RF0, RF1, RF4, RF5, RF13 RG0, RG1, RG6, RG7, RG8, RG9 RH2, RH3, RH7, RH15 RJ3-RJ7, RJ10, RJ12-RJ15 RK0-RK7 | 2.4                                                                                                                                                                                         | _    | _    | V     | IOH ≥ -15 mA, VDDIO = 3.3V |

|                    |      | Output High Voltage I/O Pins: 12x Source Driver Pins - RA6, RA7 RD4, RD5 RG12-RG14                                                                                                                                                                               | 2.4                                                                                                                                                                                         | _    | _    | V     | IOH ≥ -20 mA, VDDIO = 3.3V |

Note 1: Parameters are characterized, but not tested.

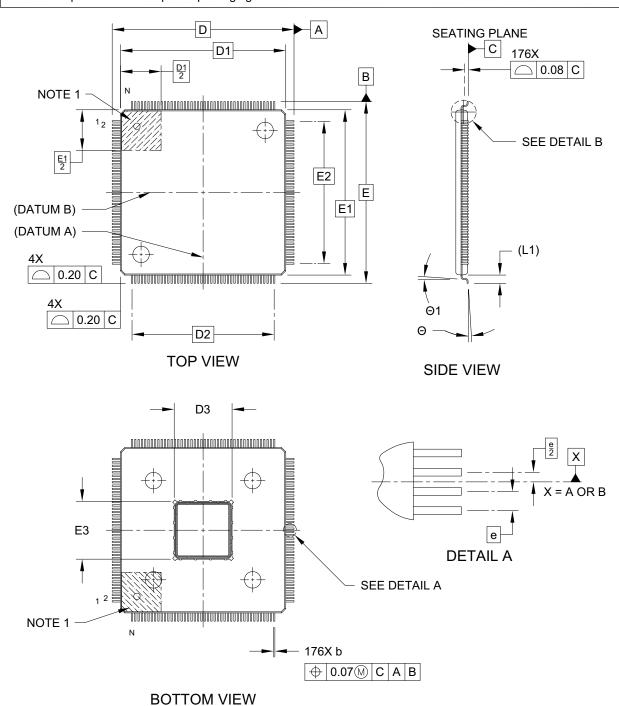

# 176-Lead Low Profile Quad Flat Pack (2J) - 20x20x1.4 mm Body [LQFP] With 7x7 mm Exposed Pad

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-367A Sheet 1 of 2

### **APPENDIX A: REVISION HISTORY**

### **Revision A (July 2015)**

This is the initial released version of the document.

### **Revision B (November 2015)**

In this revision, the document status has been updated from Advance Information to Preliminary.

This revision includes the following major changes, which are referenced by their respective chapter in Table A-1.

In addition, minor updates to text and formatting were incorporated throughout the document.

TABLE A-1: MAJOR SECTION UPDATES

| Section Name                                                                                                                        | Update Description                                                                                                                               |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                                                                                                                     | • •                                                                                                                                              |  |  |  |  |

| 32-bit Graphics Applications<br>MCUs (up to 2 MB Live Update<br>Flash, 640 KB SRAM, and 32<br>MB DDR2 SDRAM) with XLP<br>Technology | The pin names for 169-pin devices were updated (see Table 5).  The pin names for 288-pin devices were updated (see Table 7).                     |  |  |  |  |

| 4.0 "Memory Organization"                                                                                                           | The Boot Flash Sequence and Configuration Word Summary tables were updated (see Table 4-3 and Table 4-4).                                        |  |  |  |  |

|                                                                                                                                     | The BFxSEQ3/ABFxSEQ3: Boot Flash 'x' Sequence Word 0 Register was updated (see Register 4-1).                                                    |  |  |  |  |

| 6.0 "Resets"                                                                                                                        | The All Resets values were updated for the RCON register in the Resets Register Map (see Table 6-1).                                             |  |  |  |  |

| 7.0 "CPU Exceptions and Interrupt Controller"                                                                                       | The OFF199 register was added to the Interrupt Register Map (see Table 7-3).                                                                     |  |  |  |  |

| 8.0 "Oscillator Configuration"                                                                                                      | The All Resets values for the OSCON and PB6DIV registers were updated in the Oscillator Register Map (see Table 8-2).                            |  |  |  |  |

|                                                                                                                                     | The PLLODIV<2:0> bit values in the SPLLCON register were updated (see Register 8-3).                                                             |  |  |  |  |

| 10.0 "Direct Memory Access (DMA) Controller"                                                                                        | The All Resets values were updated in the DMA Channel 0 through Channel 7 Register Map (see Table 10-3).                                         |  |  |  |  |

| 11.0 "Hi-Speed USB with On-<br>The-Go (OTG)"                                                                                        | The All Resets value for bits 15:0 of the USBOTG register was updated in the USB Register Map 1 (see Table 11-1).                                |  |  |  |  |

|                                                                                                                                     | The value at POR was updated for bits 24 and 13 of the USBCRCON register (see Register 11-30).                                                   |  |  |  |  |

| 12.0 "I/O Ports"                                                                                                                    | The TRISC bits in the PORTC Register Map were updated (see Table 12-5).                                                                          |  |  |  |  |

|                                                                                                                                     | The ANSH3 bit was added to the ANSELH register in the PORTH Register Map (see Table 12-10).                                                      |  |  |  |  |

|                                                                                                                                     | The RPD15R register was removed from the Peripheral Pin Select Output Register Map (see Table 12-14).                                            |  |  |  |  |

| 18.0 "Watchdog Timer (WDT)"                                                                                                         | The All Resets value for bits 15:0 of the WDTCON register in the Watchdog Timer Register Map was updated (see Table 18-1).                       |  |  |  |  |

| 21.0 "Serial Peripheral<br>Interface (SPI) and Inter-IC<br>Sound (I <sup>2S)"</sup>                                                 | The All Resets value for bits 15:0 of the SPI1STAT and SPI1CON2 registers in the Watchdog Timer Register Map were updated (see Table 21-1).      |  |  |  |  |

| 22.0 "Serial Quad Interface (SQI)"                                                                                                  | The All Resets value for bits 15:0 of the SQI1XCON1 register in the Serial Quadrature Interface (SQI) Register Map was updated (see Table 22-1). |  |  |  |  |

### **Worldwide Sales and Service**

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd.

Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/

support

Web Address:

www.microchip.com

Atlanta Duluth, GA Tel: 678-957-961

Tel: 678-957-9614 Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

**Boston** Westborough, MA Tel: 774-760-0087

Fax: 774-760-0088 Chicago Itasca. IL

Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles Mission Viejo, CA Tel: 949-462-9523

Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

**Raleigh, NC** Tel: 919-844-7510

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

**Australia - Sydney** Tel: 61-2-9868-6733

**China - Beijing** Tel: 86-10-8569-7000

China - Chengdu Tel: 86-28-8665-5511

**China - Chongqing** Tel: 86-23-8980-9588

**China - Dongguan** Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029 China - Hangzhou

Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

**China - Nanjing** Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

**China - Shanghai** Tel: 86-21-3326-8000

China - Shenyang Tel: 86-24-2334-2829

**China - Shenzhen** Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

China - Wuhan

Tel: 86-27-5980-5300 China - Xian

Tel: 86-29-8833-7252

**China - Xiamen** Tel: 86-592-2388138

**China - Zhuhai** Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631

India - Pune Tel: 91-20-4121-0141

**Japan - Osaka** Tel: 81-6-6152-7160

**Japan - Tokyo** Tel: 81-3-6880- 3770

Korea - Daegu Tel: 82-53-744-4301

Korea - Seoul Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

**Singapore** Tel: 65-6334-8870

**Taiwan - Hsin Chu** Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

#### **EUROPE**

**Austria - Wels** Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828

Fax: 45-4485-2829 Finland - Espoo Tel: 358-9-4520-820

**France - Paris** Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79 **Germany - Garching**Tel: 49-8931-9700

**Germany - Haan** Tel: 49-2129-3766400

**Germany - Heilbronn** Tel: 49-7131-67-3636

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Germany - Rosenheim** Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Padova Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7289-7561

Poland - Warsaw Tel: 48-22-3325737 Romania - Bucharest

Tel: 40-21-407-87-50 **Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**Sweden - Gothenberg** Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820