Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

EXFL

| Product Status             | Active                                                                                        |

|----------------------------|-----------------------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                            |

| Speed                      | 200MHz                                                                                        |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, SQI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT                            |

| Number of I/O              | 120                                                                                           |

| Program Memory Size        | 1MB (1M x 8)                                                                                  |

| Program Memory Type        | FLASH                                                                                         |

| EEPROM Size                | -                                                                                             |

| RAM Size                   | 640K × 8                                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                   |

| Data Converters            | A/D 45x12b                                                                                    |

| Oscillator Type            | Internal                                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                             |

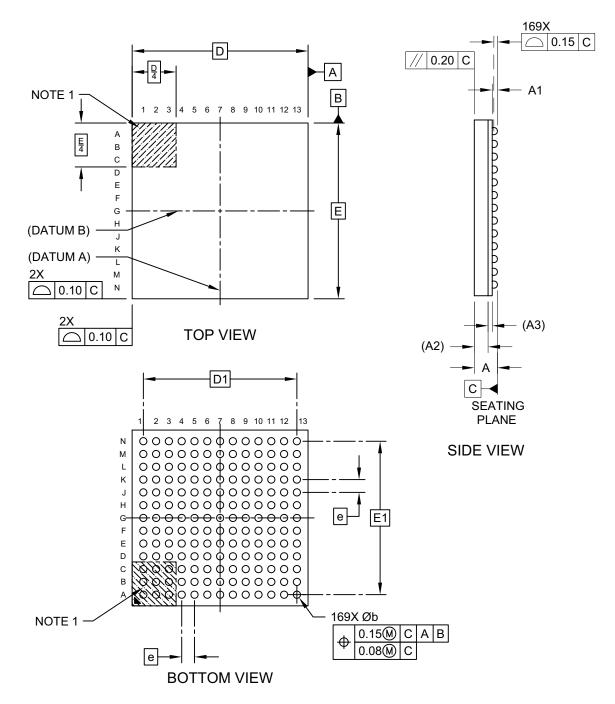

| Mounting Type              | Surface Mount                                                                                 |

| Package / Case             | 176-LQFP Exposed Pad                                                                          |

| Supplier Device Package    | 176-LQFP (20x20)                                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1064dag176-i-2j              |

|                            |                                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the PIC32MZ Graphics (DA) Family of devices. It is not intended to be a comprehensive reference source. For detailed information, refer to Section 48. "Memory Organization and Permissions" (DS60001214), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MZ DA microcontrollers provide 4 GB of unified virtual memory address space. All memory regions, including program, data memory, SFRs and Configuration registers, reside in this address space at their respective unique addresses. The program and data memories can be optionally partitioned into user and kernel memories. In addition, PIC32MZ DA devices allow execution from data memory.

Key features include:

- 32-bit native data width

- Separate User (KUSEG) and Kernel (KSEG0/ KSEG1/KSEG2/KSEG3) mode address space

- · Separate Boot Flash memory for protected code

- Robust bus exception handling to intercept runaway code

- Cacheable (KSEG0/KSEG2) and non-cacheable (KSEG1/KSEG3) address regions

- Read-Write permission access to predefined memory regions

#### 4.1 Memory Layout

PIC32MZ DA microcontrollers implement two address schemes: virtual and physical. All hardware resources, such as program memory, data memory and peripherals, are located at their respective physical addresses. Virtual addresses are exclusively used by the CPU to fetch and execute instructions as well as access peripherals. Physical addresses are used by bus master peripherals, such as DMA and the Flash controller, that access memory independently of the CPU.

The main memory maps for the PIC32MZ DA devices are illustrated in Figure 4-1. Figure 4-2 provides memory map information for Boot Flash and boot alias. Table 4-1 provides memory map information for Program Flash, RAM, and DDR2 SDRAM. Table 4-2 provides memory map information for Special Function Registers (SFRs).

#### TABLE 4-9: SYSTEM BUS VIOLATION FLAG REGISTER MAP

| ess                         |                  | 0         |       |       |       |       |       |       |      | Bi   | ts   |        |        |        |        |        |        |        |               |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|--------|--------|--------|--------|--------|--------|--------|---------------|

| Virtual Address<br>(BFxx_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All<br>Resets |

| 8F_<br>0510                 | SBFLAG0          | 31:16     | _     | —     | —     | _     | _     | _     | _    | -    |      | —      | -      | _      | _      | -      | —      | —      | 0000          |

| 0510                        | SBFLAGU          | 15:0      |       | _     | _     | _     | -     | _     | _    | _    | _    | T0PGV0 | T3PGV  | T6PGV  | T2PGV  | T5PGV  | T4PGV  | T1PGV  | 0000          |

| 90_<br>0510                 |                  | 31:16     |       | _     | _     | _     | -     | _     | _    | _    | _    | _      | _      | _      | _      | _      | _      | _      | 0000          |

| 0510                        | SBFLAG1          | 15:0      |       | _     | _     | _     | -     | _     | _    | _    | _    | T0PGV1 | T12PGV | T11PGV | T10PGV | T9PGV  | T8PGV  | T7PGV  | 0000          |

| 91_<br>0510                 |                  | 31:16     | -     | _     | _     | _     |       | _     | _    | _    | _    | -      | _      | _      | _      | _      | _      | _      | 0000          |

| 0510                        | SBFLAG2          | 15:0      | _     | _     | —     | —     | _     | —     | _    | _    |      | —      | _      | _      | T0PGV2 | T15PGV | T14PGV | T13PGV | 0000          |

| 92_<br>0510                 |                  | 31:16     | _     | _     | —     | —     | _     | —     | _    | _    |      | —      | _      | _      | _      | _      | _      | _      | 0000          |

| 0510                        | SBFLAG3          | 15:0      | —     |       | _     | —     | —     | _     | _    | _    | _    | —      | —      | _      | _      | —      | T0PGV3 | T16PGV | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-13: SYSTEM BUS TARGET PROTECTION GROUP 3 REGISTER MAP

|                             | LL <del>4</del> -13. |           |       |       | _     |        |        |       |       | Bi    |        |       |           |      |        |        |          |        |               |

|-----------------------------|----------------------|-----------|-------|-------|-------|--------|--------|-------|-------|-------|--------|-------|-----------|------|--------|--------|----------|--------|---------------|

| Virtual Address<br>(BF8F_#) | Register<br>Name     | Bit Range | 31/15 | 30/14 | 29/13 | 28/12  | 27/11  | 26/10 | 25/9  | 24/8  | 23/7   | 22/6  | 21/5      | 20/4 | 19/3   | 18/2   | 17/1     | 16/0   | All<br>Resets |

|                             |                      | 31:16     | MULTI | —     | —     | —      |        | CODE  | <3:0> |       | _      | _     | —         |      | _      | _      | _        |        | 0000          |

| 8C20                        | SBT3ELOG1            | 15:0      |       | •     | •     | INITIC | )<7:0> |       |       |       |        | REGIO | N<3:0>    | •    | _      |        | CMD<2:0> |        | 0000          |

| 8C24                        | SBT3ELOG2            | 31:16     | -     | —     | —     | —      |        | —     | —     | —     | _      | _     | —         |      | —      | —      | _        |        | 0000          |

| 0024                        | SBISELOG2            | 15:0      | -     | —     | —     | —      |        | —     | —     | —     | _      | _     | —         |      | —      | —      | GROU     | P<1:0> | 0000          |

| 8C28                        | SBT3ECON             | 31:16     | -     | —     | —     | —      |        | —     | —     | ERRP  | _      | _     | —         |      | —      | —      | _        |        | 0000          |

| 0020                        | SBIJECON             | 15:0      | -     | —     | —     | —      |        | —     | —     | —     | _      | _     | —         |      | —      | —      | _        |        | 0000          |

| 8C30                        | SBT3ECLRS            | 31:16     | -     | —     | —     | —      |        | —     | —     | —     | _      | _     | —         |      | —      | —      | _        |        | 0000          |

| 8030                        | SBISECLKS            | 15:0      |       | —     | —     | —      |        | —     | _     | —     | —      | —     | —         | —    | —      | _      | _        | CLEAR  | 0000          |

| 8C38                        | SBT3ECLRM            | 31:16     |       | —     | —     | _      |        | —     | _     | —     | _      | _     | _         |      | —      | _      | _        |        | 0000          |

| 0030                        | SBISECLRIN           | 15:0      |       | —     | —     | —      |        | —     | _     | —     | —      | —     | —         | —    | —      | _      | _        | CLEAR  | 0000          |

| 8C40                        | SBT3REG0             | 31:16     |       |       |       |        |        |       |       | BASE< | :21:6> |       |           |      |        |        |          |        | xxxx          |

| 8040                        | SBISKEGU             | 15:0      |       |       | BASE  | <5:0>  |        |       | PRI   | —     |        |       | SIZE<4:0> |      |        | _      | _        |        | xxxx          |

| 8C50                        | SBT3RD0              | 31:16     | _     | —     | —     | —      | —      | —     | —     | —     | —      | —     | —         | —    | —      | —      | —        | -      | xxxx          |

| 80.30                       | SBISKDU              | 15:0      | _     | —     | —     | —      | _      | —     | —     | —     | _      | —     | _         | —    | GROUP3 | GROUP2 | GROUP1   | GROUP0 | xxxx          |

| 8C58                        | SBT3WR0              | 31:16     | _     | —     | —     | —      | _      | —     | —     | —     | _      | —     | —         | —    |        | —      | —        | _      | xxxx          |

| 0000                        | 3013000              | 15:0      | _     | —     | —     | ·      | —      | —     |       | —     | _      | —     |           | —    | GROUP3 | GROUP2 | GROUP1   | GROUP0 | xxxx          |

| 8C60                        | SBT3REG1             | 31:16     |       |       |       |        |        |       | -     | BASE< | :21:6> |       |           |      |        | -      |          |        | xxxx          |

| 0000                        | OBTOREOT             | 15:0      |       |       | BASE  | <5:0>  |        | -     | PRI   | —     |        |       | SIZE<4:0> |      | _      | —      | —        | _      | xxxx          |

| 8C70                        | SBT3RD1              | 31:16     | _     | —     | —     | —      | _      | —     | —     | —     | _      | —     | —         | —    |        | —      | —        | _      | xxxx          |

| 0070                        | SBISKET              | 15:0      | _     | —     | —     | —      | _      | —     | —     | —     | _      | —     | —         | —    | GROUP3 | GROUP2 | GROUP1   | GROUP0 | xxxx          |

| 8C78                        | SBT3WR1              | 31:16     | _     | —     | _     |        | _      | _     | _     | —     | _      | _     | _         | —    | _      | _      | —        |        | xxxx          |

| 0070                        | 3613000              | 15:0      | _     | —     | —     | —      | _      | —     | —     | —     | _      | —     | —         | —    | GROUP3 | GROUP2 | GROUP1   | GROUP0 | xxxx          |

| 8C80                        | SBT3REG2             | 31:16     |       |       |       |        |        |       |       | BASE< | :21:6> |       |           |      |        |        |          |        | xxxx          |

| 0000                        | OBTOREOZ             | 15:0      |       |       | BASE  | <5:0>  |        |       | PRI   | —     |        |       | SIZE<4:0> |      |        |        |          |        | xxxx          |

| 8C90                        | SBT3RD2              | 31:16     | _     | —     | —     | —      | _      | —     | —     | —     | _      | —     | —         | —    |        | —      | —        | _      | xxxx          |

| 0000                        | 0010102              | 15:0      | _     | —     | —     | —      | _      | —     | —     | —     | _      | —     | —         | —    | GROUP3 | GROUP2 | GROUP1   | GROUP0 | xxxx          |

| 8C98                        | SBT3WR2              | 31:16     | _     | —     | —     | —      | _      | —     | —     | —     | _      | —     | —         | —    |        | —      | —        | _      | xxxx          |

| 0000                        | OBTOWINE             | 15:0      | _     | —     | —     | ·      | —      | —     |       | —     | _      | —     | _         | —    | GROUP3 | GROUP2 | GROUP1   | GROUP0 | xxxx          |

PIC32MZ Graphics (DA) Family

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note: For reset values listed as 'xxxx', please refer to Table 4-8 for the actual reset values.

#### REGISTER 5-1: NVMCON: PROGRAMMING CONTROL REGISTER (CONTINUED)

bit 6 **BFSWAP:** Boot Flash Bank Swap Control bit<sup>(3,4)</sup>

- 1 = Boot Flash Bank 2 is mapped to the lower boot region and Boot Flash Bank 1 is mapped to the upper mapped region

- 0 = Boot Flash Bank 1 is mapped to the lower boot region and Boot Flash Bank 2 is mapped to the upper mapped region

- bit 5-4 Unimplemented: Read as '0'

- bit 3-0 NVMOP<3:0>: NVM Operation bits

- These bits are only writable when WREN = 0.

- 1111 = Reserved

- •

- 1000 = Reserved

- 0111 = Program erase operation: erase all of program Flash memory (all pages must be unprotected, PWP<23:0> = 0x000000)

- 0110 = Upper program Flash memory erase operation: erases only the upper mapped region of program Flash (all pages in that region must be unprotected)

- 0101 = Lower program Flash memory erase operation: erases only the lower mapped region of program Flash (all pages in that region must be unprotected)

- 0100 = Page erase operation: erases page selected by NVMADDR, if it is not write-protected

- 0011 = Row program operation: programs row selected by NVMADDR, if it is not write-protected

- 0010 = Quad Word (128-bit) program operation: programs the 128-bit Flash word selected by NVMADDR, if it is not write-protected

- 0001 = Word program operation: programs word selected by NVMADDR, if it is not write-protected<sup>(2)</sup> 0000 = No operation

- Note 1: These bits are only reset by a Power-on Reset (POR) and are not affected by other reset sources.

- 2: This operation results in a "no operation" (NOP) when the Dynamic Flash ECC Configuration bits = 00 (FECCCON<1:0> (DVCFG0<9:8>)), which enables ECC at all times. For all other FECCCON<1:0> bit settings, this command will execute, but will not write the ECC bits for the word and can cause DED errors if dynamic Flash ECC is enabled (FECCCON<1:0> = 01). Refer to Section 52. "Flash Program Memory with Support for Live Update" (DS60001193) for information regarding ECC and Flash programming.

- **3:** This bit can only be modified when the WREN bit = 0, the NVMKEY unlock sequence is satisfied, and the SWAPLOCK<1:0> bits (NVMCON2<7:6>) are cleared to '0'.

- **4:** The BFSWAP value is determined by the values the user programmed Sequence Numbers in each boot panel.

#### REGISTER 5-7: NVMBWP: FLASH BOOT (PAGE) WRITE-PROTECT REGISTER

| bit 4 | UBWP4: Upper Boot Alias Page 4 Write-protect bit <sup>(1)</sup>                                                                                                                                 |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Write protection for physical address 0x01FC30000 through 0x1FC33FFF enabled</li> <li>0 = Write protection for physical address 0x01FC30000 through 0x1FC33FFF disabled</li> </ul> |

| bit 3 | UBWP3: Upper Boot Alias Page 3 Write-protect bit <sup>(1)</sup>                                                                                                                                 |

|       | <ul> <li>1 = Write protection for physical address 0x01FC2C000 through 0x1FC2FFFF enabled</li> <li>0 = Write protection for physical address 0x01FC2C000 through 0x1FC2FFFF disabled</li> </ul> |

| bit 2 | UBWP2: Upper Boot Alias Page 2 Write-protect bit <sup>(1)</sup>                                                                                                                                 |

|       | <ul> <li>1 = Write protection for physical address 0x01FC28000 through 0x1FC2BFFF enabled</li> <li>0 = Write protection for physical address 0x01FC28000 through 0x1FC2BFFF disabled</li> </ul> |

| bit 1 | UBWP1: Upper Boot Alias Page 1 Write-protect bit <sup>(1)</sup>                                                                                                                                 |

|       | <ul> <li>1 = Write protection for physical address 0x01FC24000 through 0x1FC27FFF enabled</li> <li>0 = Write protection for physical address 0x01FC24000 through 0x1FC27FFF disabled</li> </ul> |

| bit 0 | UBWP0: Upper Boot Alias Page 0 Write-protect bit <sup>(1)</sup>                                                                                                                                 |

|       | <ul> <li>1 = Write protection for physical address 0x01FC20000 through 0x1FC23FFF enabled</li> <li>0 = Write protection for physical address 0x01FC20000 through 0x1FC23FFF disabled</li> </ul> |

|       |                                                                                                                                                                                                 |

**Note 1:** These bits are only available when the NVMKEY unlock sequence is performed and the associated Lock bit (LBWPULOCK or UBWPULOCK) is set.

**Note:** The bits in this register are only writable when the NVMKEY unlock sequence is followed.

### 11.0 HI-SPEED USB WITH ON-THE-GO (OTG)

Note: This data sheet summarizes the features of the PIC32MZ DA family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 51. "Hi-Speed (OTG)" USB with **On-The-Go** (DS60001326) in the "PIC32 Family Reference Manual", which is available the site from Microchip web (www.microchip.com/PIC32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 embedded host, device, or OTG implementation with a minimum of external components.

The module supports Hi-Speed, Full-Speed, or Low-Speed in any of the operating modes. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the RAM controller, packet encode/decode, UTM synchronization, endpoint control, a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is illustrated in Figure 11-1.

The USB module includes the following features:

- USB Hi-Speed, Full-Speed, and Low-Speed support for host and device

- USB OTG support with one or more Hi-Speed, Full-Speed, or Low-Speed device

- · Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- · Integrated USB transceiver

- Transaction handshaking performed by hardware

- Integrated 8-channel DMA to access system RAM and Flash

- Seven transmit endpoints and seven receive endpoints, in addition to Endpoint 0

- Session Request Protocol (SRP) and Host Negotiation Protocol (HNP) support

- Suspend and resume signaling support

- Dynamic FIFO sizing

- Integrated RAM for the FIFOs, eliminating the need for system RAM for the FIFOs

- · Link power management support

- Note 1: The implementation and use of the USB specifications, as well as other third party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

- 2: If the USB module is used, the Primary Oscillator (POSC) is limited to either 12 MHz or 24 MHz.

#### REGISTER 11-8: USBIENCSR0: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 0 (ENDPOINT 1-7) (CONTINUED)

bit 15-11 MULT<4:0>: Multiplier Control bits

For Isochronous/Interrupt endpoints or of packet splitting on Bulk endpoints, multiplies TXMAXP by MULT+1 for the payload size.

For Bulk endpoints, MULT can be up to 32 and defines the number of "USB" packets of the specified payload into which a single data packet placed in the FIFO should be split, prior to transfer. The data packet is required to be an exact multiple of the payload specified by TXMAXP.

For Isochronous/Interrupts endpoints operating in Hi-Speed mode, MULT may be either 2 or 3 and specifies the maximum number of such transactions that can take place in a single microframe.

#### bit 10-0 TXMAXP<10:0>: Maximum TX Payload per transaction Control bits

This field sets the maximum payload (in bytes) transmitted in a single transaction. The value is subject to the constraints placed by the USB Specification on packet sizes for Bulk, Interrupt and Isochronous transfers in Full-Speed and Hi-Speed operations.

TXMAXP must be set to an even number of bytes for proper interrupt generation in DMA Mode 1.

#### TABLE 12-13: PERIPHERAL PIN SELECT INPUT REGISTER MAP (CONTINUED)

| ess                         |                      |           |       |       |       |       |       |       |      | E    | Bits |      |      |      |      |        |          |      |            |

|-----------------------------|----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|--------|----------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2   | 17/1     | 16/0 | All Resets |

| 1400                        | SS6R                 | 31:16     | _     | —     | —     | -     | —     | —     | —    | -    | —    | —    | -    | —    | —    | —      | —        | —    | 0000       |

| 14DC                        | 220K                 | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | SS6R   | <3:0>    |      | 0000       |

| 4450                        | C1RXR <sup>(1)</sup> | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | —      | _        | —    | 0000       |

| 14E0                        | UIRAR' /             | 15:0      | _     | _     | _     | —     | —     | _     | —    | _    | _    | _    | _    | _    |      | C1RX   | R<3:0>   |      | 0000       |

| 14E4                        | C2RXR <sup>(1)</sup> | 31:16     | _     | _     | _     | —     | —     | _     | —    | _    | _    | _    | _    | _    | _    | —      | _        | —    | 0000       |

| 1464                        | GZRAR <sup>Y</sup>   | 15:0      |       | —     | —     | —     | —     | —     | —    | -    | —    | —    | -    | —    |      | C2RX   | R<3:0>   |      | 0000       |

| 1400                        | REFCLKI1R            | 31:16     | _     | _     | _     | —     | —     | _     | —    | _    | _    | _    | _    | _    | _    | —      | _        | —    | 0000       |

| 14E0                        | REFULKIIR            | 15:0      | _     | _     | _     | —     | —     | _     | —    | _    | _    | _    | _    | _    |      | REFCLK | l1R<3:0> |      | 0000       |

| 1450                        | <b>REFCLKI3R</b>     | 31:16     | _     | _     | _     | —     | —     | _     | —    | _    | _    | _    | _    | _    | _    | —      | _        | —    | 0000       |

| 14F0                        | REFULKISK            | 15:0      | _     | —     | —     | —     | —     | —     | —    | —    | —    | —    | _    | —    |      | REFCLK | I3R<3:0> |      | 0000       |

| 1454                        | REFCLKI4R            | 31:16     | _     | —     | —     | —     | —     | —     | —    | —    | —    | —    | _    | —    | —    | —      |          | —    | 0000       |

| 1464                        | REFULKI4R            | 15:0      | _     | _     | _     | —     | _     | —     | _    | _    | _    | _    | _    | _    |      | REFCLK | 14R<3:0> |      | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| REGIST   | ER 20-1: RTCCON: REAL-TIME CLOCK AND CALENDAR CONTROL REGISTER                                                                                                                                                                 |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10-9 | RTCCLKSEL<1:0>: RTCC Clock Select bits                                                                                                                                                                                         |

|          | When a new value is written to these bits, the Seconds Value register should also be written to properly reset the clock prescalers in the RTCC.                                                                               |

|          | 11 = Reserved                                                                                                                                                                                                                  |

|          | 10 = Reserved                                                                                                                                                                                                                  |

|          | <ul><li>01 = RTCC uses the external 32.768 kHz Secondary Oscillator (SOSC)</li><li>00 = RTCC uses the internal 32 kHz oscillator (LPRC)</li></ul>                                                                              |

| bit 8-7  | RTCOUTSEL<1:0>: RTCC Output Data Select bits <sup>(2)</sup>                                                                                                                                                                    |

|          | 11 = Reserved                                                                                                                                                                                                                  |

|          | 10 = RTCC Clock is presented on the RTCC pin                                                                                                                                                                                   |

|          | 01 = Seconds Clock is presented on the RTCC pin                                                                                                                                                                                |

|          | 00 = Alarm Pulse is presented on the RTCC pin when the alarm interrupt is triggered                                                                                                                                            |

| bit 6    | RTCCLKON: RTCC Clock Enable Status bit                                                                                                                                                                                         |

|          | 1 = RTCC Clock is actively running                                                                                                                                                                                             |

|          | 0 = RTCC Clock is not running                                                                                                                                                                                                  |

| bit 5-4  | Unimplemented: Read as '0'                                                                                                                                                                                                     |

| bit 3    | RTCWREN: Real-Time Clock Value Registers Write Enable bit <sup>(3)</sup>                                                                                                                                                       |

|          | 1 = Real-Time Clock Value registers can be written to by the user                                                                                                                                                              |

|          | 0 = Real-Time Clock Value registers are locked out from being written to by the user                                                                                                                                           |

| bit 2    | RTCSYNC: Real-Time Clock Value Registers Read Synchronization bit                                                                                                                                                              |

|          | 1 = Real-time clock value registers can change while reading (due to a rollover ripple that results in an invalid data read). If the register is read twice and results in the same data, the data can be assumed to be valid. |

|          | 0 = Real-time clock value registers can be read without concern about a rollover ripple                                                                                                                                        |

| bit 1    | HALFSEC: Half-Second Status bit <sup>(4)</sup>                                                                                                                                                                                 |

|          | 1 = Second half period of a second                                                                                                                                                                                             |

|          | 0 = First half period of a second                                                                                                                                                                                              |

| bit 0    | RTCOE: RTCC Output Enable bit                                                                                                                                                                                                  |

|          |                                                                                                                                                                                                                                |

- 1 = RTCC output is enabled

- 0 = RTCC output is not enabled

- **Note 1:** The ON bit is only writable when RTCWREN = 1.

- **2:** Requires RTCOE = 1 (RTCCON<0>) for the output to be active.

- 3: The RTCWREN bit can be set only when the write sequence is enabled.

- 4: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

Note: This register is reset only on a Power-on Reset (POR).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | -                 | _                 | _                 | _                 | _                 | _                 | -                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -                 | —                 | _                 | _                 | -                 | _                 | -                | —                |

| 45.0         | R-0               | R/W-0, HS, SC     | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         | IBF               | IBOV              | _                 | _                 | IB3F              | IB2F              | IB1F             | IB0F             |

| 7.0          | R-1               | R/W-0, HS, SC     | U-0               | U-0               | R-1               | R-1               | R-1              | R-1              |

| 7:0          | OBE               | OBUF              | _                 | _                 | OB3E              | OB2E              | OB1E             | OB0E             |

#### REGISTER 25-7: PMSTAT: PARALLEL PORT STATUS REGISTER (SLAVE MODES ONLY)

| Legend:           | HS = Hardware Set | SC = Software Cleared     |                    |

|-------------------|-------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **IBF:** Input Buffer Full Status bit

- 1 = All writable input buffer registers are full

- 0 = Some or all of the writable input buffer registers are empty

- bit 14 IBOV: Input Buffer Overflow Status bit

- 1 = A write attempt to a full input byte buffer occurred (must be cleared in software)

- 0 = No overflow occurred

- bit 13-12 Unimplemented: Read as '0'

- bit 11-8 **IBxF:** Input Buffer 'x' Status Full bits

- 1 = Input Buffer contains data that has not been read (reading buffer will clear this bit)

- 0 = Input Buffer does not contain any unread data

- bit 7 **OBE:** Output Buffer Empty Status bit

- 1 = All readable output buffer registers are empty

- 0 = Some or all of the readable output buffer registers are full

- bit 6 **OBUF:** Output Buffer Underflow Status bit

- 1 = A read occurred from an empty output byte buffer (must be cleared in software)

- 0 = No underflow occurred

- bit 5-4 Unimplemented: Read as '0'

- bit 3-0 **OBxE:** Output Buffer 'x' Status Empty bits

- 1 = Output buffer is empty (writing data to the buffer will clear this bit)

- 0 = Output buffer contains data that has not been transmitted

| Name       |       | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|------------|-------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

|            | 23:16 |                   |                   |                   | ENCKEY<2          | 3:16>             |                   |                  |                  |

|            | 15:8  |                   |                   |                   | ENCKEY<           | 15:8>             |                   |                  |                  |

|            | 7:0   |                   |                   |                   | ENCKEY<           | :7:0>             |                   |                  |                  |

| SA_ENCKEY3 | 31:24 |                   |                   |                   | ENCKEY<3          | 31:24>            |                   |                  |                  |

|            | 23:16 |                   |                   |                   | ENCKEY<2          | 3:16>             |                   |                  |                  |

|            | 15:8  |                   |                   |                   | ENCKEY<           | 15:8>             |                   |                  |                  |

|            | 7:0   |                   |                   |                   | ENCKEY<           | :7:0>             |                   |                  |                  |

| SA_ENCKEY4 | 31:24 |                   |                   |                   | ENCKEY<3          | 31:24>            |                   |                  |                  |

|            | 23:16 |                   |                   |                   | ENCKEY<2          | 3:16>             |                   |                  |                  |

|            | 15:8  |                   |                   |                   | ENCKEY<           | 15:8>             |                   |                  |                  |

|            | 7:0   |                   |                   |                   | ENCKEY<           | :7:0>             |                   |                  |                  |

| SA_ENCKEY5 | 31:24 |                   |                   |                   | ENCKEY<3          | 31:24>            |                   |                  |                  |

|            | 23:16 |                   |                   |                   | ENCKEY<2          | 23:16>            |                   |                  |                  |

|            | 15:8  |                   |                   |                   | ENCKEY<           | 15:8>             |                   |                  |                  |

|            | 7:0   |                   |                   |                   | ENCKEY<           | :7:0>             |                   |                  |                  |

| SA_ENCKEY6 | 31:24 |                   |                   |                   | ENCKEY<3          | 31:24>            |                   |                  |                  |

|            | 23:16 |                   |                   |                   | ENCKEY<2          | 3:16>             |                   |                  |                  |

|            | 15:8  |                   |                   |                   | ENCKEY<           |                   |                   |                  |                  |

|            | 7:0   |                   |                   |                   | ENCKEY<           | :7:0>             |                   |                  |                  |

| SA_ENCKEY7 | 31:24 |                   |                   |                   | ENCKEY<3          | 31:24>            |                   |                  |                  |

| _          | 23:16 |                   |                   |                   | ENCKEY<2          | 3:16>             |                   |                  |                  |

|            | 15:8  |                   |                   |                   | ENCKEY<           | 15:8>             |                   |                  |                  |

|            | 7:0   |                   |                   |                   | ENCKEY<           | :7:0>             |                   |                  |                  |

| SA_ENCKEY8 | 31:24 |                   |                   |                   | ENCKEY<3          |                   |                   |                  |                  |

| -          | 23:16 |                   |                   |                   | ENCKEY<2          | 3:16>             |                   |                  |                  |

|            | 15:8  |                   |                   |                   | ENCKEY<           |                   |                   |                  |                  |

|            | 7:0   |                   |                   |                   | ENCKEY<           |                   |                   |                  |                  |

| SA_AUTHIV1 | 31:24 |                   |                   |                   | AUTHIV<3          |                   |                   |                  |                  |

| -          | 23:16 |                   |                   |                   | AUTHIV<2          | 3:16>             |                   |                  |                  |

|            | 15:8  |                   |                   |                   | AUTHIV<1          |                   |                   |                  |                  |

|            | 7:0   |                   |                   |                   | AUTHIV<           | 7:0>              |                   |                  |                  |

| SA_AUTHIV2 | 31:24 |                   |                   |                   | AUTHIV<3          |                   |                   |                  |                  |

| -          | 23:16 |                   |                   |                   | AUTHIV<2          |                   |                   |                  |                  |

|            | 15:8  |                   |                   |                   | AUTHIV<1          |                   |                   |                  |                  |

|            | 7:0   |                   |                   |                   | AUTHIV<           |                   |                   |                  |                  |

| SA_AUTHIV3 | 31:24 |                   |                   |                   | AUTHIV<3          | 1:24>             |                   |                  |                  |

| -          | 23:16 |                   |                   |                   | AUTHIV<2          | 3:16>             |                   |                  |                  |

|            | 15:8  |                   |                   |                   | AUTHIV<1          | 5:8>              |                   |                  |                  |

|            | 7:0   |                   |                   |                   | AUTHIV<           | 7:0>              |                   |                  |                  |

| SA_AUTHIV4 | 31:24 |                   |                   |                   | AUTHIV<3          | 1:24>             |                   |                  |                  |

|            | 23:16 |                   |                   |                   | AUTHIV<2          |                   |                   |                  |                  |

|            | 15:8  |                   |                   |                   | AUTHIV<1          | 5:8>              |                   |                  |                  |

|            | 7:0   |                   |                   |                   | AUTHIV<           | 7:0>              |                   |                  |                  |

| SA_AUTHIV5 | 31:24 |                   |                   |                   | AUTHIV<3          | 1:24>             |                   |                  |                  |

|            | 23:16 |                   |                   |                   | AUTHIV<2          | 3:16>             |                   |                  |                  |

|            | 15:8  |                   |                   |                   | AUTHIV<1          | 5:8>              |                   |                  |                  |

|            | 7:0   |                   |                   |                   | AUTHIV<           | 7:0>              |                   |                  |                  |

| SA_AUTHIV6 | 31:24 |                   |                   |                   | AUTHIV<3          | 1:24>             |                   |                  |                  |

|            | 23:16 |                   |                   |                   | AUTHIV<2          | 3:16>             |                   |                  |                  |

|            | 15:8  |                   |                   |                   | AUTHIV<1          | 5:8>              |                   |                  |                  |

|            | 7:0   |                   |                   |                   | AUTHIV<           | 7:0>              |                   |                  |                  |

| SA_AUTHIV7 | 31:24 |                   |                   |                   | AUTHIV<3          | 1:24>             |                   |                  |                  |

|            | 23:16 |                   |                   |                   | AUTHIV<2          | 3:16>             |                   |                  |                  |

|            | 15:8  |                   |                   |                   | AUTHIV<1          |                   |                   |                  |                  |

|            | 7:0   |                   |                   |                   | AUTHIV<           |                   |                   |                  |                  |

| SA_AUTHIV8 | 31:24 |                   |                   |                   | AUTHIV<3          |                   |                   |                  |                  |

| -          | 23:16 |                   |                   |                   | AUTHIV<2          |                   |                   |                  |                  |

|            | 15:8  |                   |                   |                   | AUTHIV<1          |                   |                   |                  |                  |

|            | 7:0   |                   |                   |                   | AUTHIV<           |                   |                   |                  |                  |

#### FIGURE 27-11: CRYPTO ENGINE SECURITY ASSOCIATION STRUCTURE (CONTINUED)

#### TABLE 29-2: ADC REGISTER MAP (CONTINUED)

|                    |                       | ø         |       |                           |       |       |       |       |      | Bit     | 6       |       |      |      |      |      |      |      |   |

|--------------------|-----------------------|-----------|-------|---------------------------|-------|-------|-------|-------|------|---------|---------|-------|------|------|------|------|------|------|---|

| Virtual<br>Address | Register<br>Name      | Bit Range | 31/15 | 30/14                     | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8    | 23/7    | 22/6  | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 |   |

| 3608               | ADC2CFG <sup>1)</sup> | 31:16     |       |                           |       |       |       |       | I    | ADCCFG  | <31:16> |       |      |      |      |      |      |      | 0 |

|                    |                       | 15:0      |       |                           |       |       |       |       |      | ADCCFG  | <15:0>  |       |      |      |      |      |      |      | ( |

| 360C               | ADC3CFG <sup>1)</sup> | 31:16     |       |                           |       |       |       |       |      | ADCCFG- | <31:16> |       |      |      |      |      |      |      |   |

|                    |                       | 15:0      |       |                           |       |       |       |       |      | ADCCFG  | <15:0>  |       |      |      |      |      |      |      |   |

| B610               | ADC4CFG <sup>1)</sup> | 31:16     |       |                           |       |       |       |       |      | ADCCFG- |         |       |      |      |      |      |      |      |   |

|                    |                       | 15:0      |       |                           |       |       |       |       |      | ADCCFG  | <15:0>  |       |      |      |      |      |      |      |   |

| 361C               | ADC7CFG <sup>1)</sup> | 31:16     |       |                           |       |       |       |       |      | ADCCFG- | <31:16> |       |      |      |      |      |      |      |   |

|                    |                       | 15:0      |       |                           |       |       |       |       |      | ADCCFG  | <15:0>  |       |      |      |      |      |      |      | - |

| B640               | ADCSYSCFG1            | 31:16     |       |                           |       |       |       |       |      | AN<31   | :16>    |       |      |      |      |      |      |      |   |

|                    |                       | 15:0      |       | -                         |       | -     |       | -     |      | AN<1    | 5:0>    |       |      |      |      |      |      |      |   |

| 3644               | ADCSYSCFG2            | 31:16     | _     | _                         | _     | -     | _     | —     | —    | —       | _       | _     | —    | -    | -    | -    | -    | -    |   |

|                    |                       | 15:0      | —     | —                         | —     | -     |       |       |      |         |         | AN<43 | :32> |      |      |      |      |      |   |

| 8A00               | ADCDATA0              | 31:16     |       | DATA<31:16>               |       |       |       |       |      |         |         |       |      |      |      |      |      |      |   |

|                    |                       | 15:0      |       | DATA<01.102<br>DATA<15:0> |       |       |       |       |      |         |         |       |      |      |      |      |      |      |   |

| 3A04               | ADCDATA1              | 31:16     |       |                           |       |       |       |       |      | DATA<3  | 1:16>   |       |      |      |      |      |      |      |   |

|                    |                       | 15:0      |       |                           |       |       |       |       |      | DATA<   | 5:0>    |       |      |      |      |      |      |      |   |

| BA08               | ADCDATA2              | 31:16     |       |                           |       |       |       |       |      | DATA<3  | 1:16>   |       |      |      |      |      |      |      |   |

|                    |                       | 15:0      |       |                           |       |       |       |       |      | DATA<   | 5:0>    |       |      |      |      |      |      |      |   |

| BA0C               | ADCDATA3              | 31:16     |       |                           |       |       |       |       |      | DATA<3  | 1:16>   |       |      |      |      |      |      |      |   |

|                    |                       | 15:0      |       |                           |       |       |       |       |      | DATA<   | 5:0>    |       |      |      |      |      |      |      |   |

| BA10               | ADCDATA4              | 31:16     |       |                           |       |       |       |       |      | DATA<3  | 1:16>   |       |      |      |      |      |      |      |   |

|                    |                       | 15:0      |       |                           |       |       |       |       |      | DATA<   | 5:0>    |       |      |      |      |      |      |      |   |

| BA14               | ADCDATA5              | 31:16     |       |                           |       |       |       |       |      | DATA<3  | 1:16>   |       |      |      |      |      |      |      | - |

|                    |                       | 15:0      |       |                           |       |       |       |       |      | DATA<   | 5:0>    |       |      |      |      |      |      |      | ( |

| BA18               | ADCDATA6              | 31:16     |       |                           |       |       |       |       |      | DATA<3  | 1:16>   |       |      |      |      |      |      |      |   |

|                    |                       | 15:0      |       |                           |       |       |       |       |      | DATA<   | 5:0>    |       |      |      |      |      |      |      | 1 |

| 3A1C               | ADCDATA7              | 31:16     |       |                           |       |       |       |       |      | DATA<3  | 1:16>   |       |      |      |      |      |      |      |   |

|                    |                       | 15:0      |       |                           |       |       |       |       |      | DATA<   | 5:0>    |       |      |      |      |      |      |      |   |

| BA20               | ADCDATA8              | 31:16     |       |                           |       |       |       |       |      | DATA<3  | 1:16>   |       |      |      |      |      |      |      |   |

|                    |                       | 15:0      |       |                           |       |       |       |       |      | DATA<   | 5:0>    |       |      |      |      |      |      |      |   |

| 3A24               | ADCDATA9              | 31:16     |       |                           |       |       |       |       |      | DATA<3  | 1:16>   |       |      |      |      |      |      |      |   |

|                    |                       | 15:0      |       |                           |       |       |       |       |      | DATA<   | 5:0>    |       |      |      |      |      |      |      |   |

| BA28               | ADCDATA10             | 31:16     |       |                           |       |       |       |       |      | DATA<3  | 1:16>   |       |      |      |      |      |      |      | ( |

|                    |                       | 15:0      |       |                           |       |       |       |       |      | DATA<   | 5:0>    |       |      |      |      |      |      |      |   |

| BA2C               | ADCDATA11             | 31:16     |       |                           |       |       |       |       |      | DATA<3  | 1:16>   |       |      |      |      |      |      |      |   |

|                    |                       | 15:0      |       |                           |       |       |       |       |      | DATA<   | 5:0>    |       |      |      |      |      |      |      |   |

| BA30               | ADCDATA12             | 31:16     |       |                           |       |       |       |       |      | DATA<3  | 1:16>   |       |      |      |      |      |      |      |   |

|                    |                       | 15:0      |       |                           |       |       |       |       |      | DATA<   | 5:0>    |       |      |      |      |      |      |      |   |

**PIC32MZ Graphics (DA) Family**

#### REGISTER 29-2: ADCCON2: ADC CONTROL REGISTER 2 (CONTINUED)

The ADCDIV<6:0> bits divide the ADC control clock (TQ) to generate the clock for the Shared ADC, ADC7 (TAD7).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1          | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------------|------------------|--|--|--|--|--|--|

| 04.04        | R/W-0                     | R/W-0            |  |  |  |  |  |  |

| 31:24        | ADCSE             | L<1:0>            |                   | CONCLKDIV<5:0>    |                   |                   |                           |                  |  |  |  |  |  |  |

| 00.40        | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0                     | R/W-0            |  |  |  |  |  |  |

| 23:16        | DIGEN7            | —                 | _                 | DIGEN4            | DIGEN3            | DIGEN2            | DIGEN1                    | DIGEN0           |  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0, HS, HC       | R/W-0                     | R-0, HS, HC      |  |  |  |  |  |  |

| 15:8         | V                 | REFSEL<2:0        | >                 | TRGSUSP           | UPDIEN            | UPDRDY            | SAMP <sup>(1,2,3,4)</sup> | RQCNVRT          |  |  |  |  |  |  |

| 7:0          | R/W-0             | R/W, HC           | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                     | R/W-0            |  |  |  |  |  |  |

| 7:0          | GLSWTRG           | GSWTRG            |                   |                   | ADINS             | SEL<5:0>          |                           |                  |  |  |  |  |  |  |

#### REGISTER 29-3: ADCCON3: ADC CONTROL REGISTER 3

| Legend:           | HC = Hardware Set | HS = Hardware Cleared                   |

|-------------------|-------------------|-----------------------------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0'      |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared x = Bit is unknown |

bit 31-30 ADCSEL<1:0>: Analog-to-Digital Clock Source (TCLK) bits

11 = FRC 10 = REFCLK3 01 = System Clock (Tcy) 00 = PBCLK3

#### bit 29-24 CONCLKDIV<5:0>: Analog-to-Digital Control Clock (Tq) Divider bits

#### bit 23 **DIGEN7:** Shared ADC (ADC7) Digital Enable bit 1 = ADC7 is digital enabled 0 = ADC7 is digital disabled

#### bit 22-21 Unimplemented: Read as '0'

#### bit 20 DIGEN4: ADC4 Digital Enable bit

- 1 = ADC4 is digital enabled

- 0 = ADC4 is digital disabled

#### bit 19 **DIGEN3:** ADC3 Digital Enable bit

- 1 = ADC3 is digital enabled

- 0 = ADC3 is digital disabled

- **Note 1:** The SAMP bit has the highest priority and setting this bit will keep the S&H circuit in Sample mode until the bit is cleared. Also, usage of the SAMP bit will cause settings of SAMC<9:0> bits (ADCCON2<25:16>) to be ignored.

- 2: The SAMP bit only connects Class 2 and Class 3 analog inputs to the shared ADC, ADC7. All Class 1 analog inputs are not affected by the SAMP bit.

- **3:** The SAMP bit is not a self-clearing bit and it is the responsibility of application software to first clear this bit and only after setting the RQCNVRT bit to start the analog-to-digital conversion.

- 4: Normally, when the SAMP and RQCNVRT bits are used by software routines, all TRGSRCx<4:0> bits and STRGSRC<4:0> bits should be set to '00000' to disable all external hardware triggers and prevent them from interfering with the software-controlled sampling command signal SAMP and with the software-controlled trigger RQCNVRT.

# REGISTER 29-4: ADCTRGMODE: ADC TRIGGERING MODE FOR DEDICATED ADC REGISTER bit 9 STRGEN1: ADC1 Presynchronized Triggers bit 1 = ADC1 uses presynchronized triggers 0 = ADC1 does not use presynchronized triggers

- bit 8 **STRGEN0:** ADC0 Presynchronized Triggers bit 1 = ADC0 uses presynchronized triggers

- a ADC0 uses presynchronized triggers

a ADC0 does not use presynchronized triggers

- bit 7 5 Unimplemented: Deed es '.'

- bit 7-5 **Unimplemented:** Read as ' '

- bit 4 SSAMPEN4: ADC4 Synchronous Sampling bit

- 1 = ADC4 uses synchronous sampling for the first sample after being idle or disabled

0 = ADC4 does not use synchronous sampling

- bit 3 **SSAMPEN3:** ADC3 Synchronous Sampling bit 1 = ADC3 uses synchronous sampling for the first sample after being idle or disabled

- 0 = ADC3 does not use synchronous sampling

- bit 2 **SSAMPEN2:** ADC2Synchronous Sampling bit 1 = ADC2 uses synchronous sampling for the first sample after being idle or disabled 0 = ADC2 does not use synchronous sampling

- bit 1 **SSAMPEN1:** ADC1 Synchronous Sampling bit 1 = ADC1 uses synchronous sampling for the first sample after being idle or disabled 0 = ADC1 does not use synchronous sampling

- bit 0 **SSAMPEN0:** ADC0 Synchronous Sampling bit 1 = ADC0 uses synchronous sampling for the first sample after being idle or disabled

- 0 = ADC0 does not use synchronous sampling

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|           | FLTEN3            | MSEL3<1:0>        |                   | FSEL3<4:0>        |                   |                   |                  |                  |

| 23:16     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|           | FLTEN2            | MSEL2<1:0>        |                   | FSEL2<4:0>        |                   |                   |                  |                  |

| 15:8      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|           | FLTEN1            | MSEL1<1:0>        |                   | FSEL1<4:0>        |                   |                   |                  |                  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|           | FLTEN0            | MSEL0<1:0>        |                   | FSEL0<4:0>        |                   |                   |                  |                  |

#### REGISTER 30-10: CIFLTCON0: CAN FILTER CONTROL REGISTER 0

#### Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 31                 | FLTEN3: Filter 3 Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | 1 = Filter is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                        | 0 = Filter is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| bit 30-29              | MSEL3<1:0>: Filter 3 Mask Select bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                        | 11 = Acceptance Mask 3 selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                        | 10 = Acceptance Mask 2 selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                        | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| bit 28-24              | FSEL3<4:0>: FIFO Selection bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DIL 20-24              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                        | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                        | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                        | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                        | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                        | 00001 = Message matching filter is stored in FIFO buffer 1                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                        | 00000 = Message matching filter is stored in FIFO buffer 0                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| bit 23                 | FLTEN2: Filter 2 Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                        | 1 = Filter is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                        | 1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| bit 22-21              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| bit 22-21              | 0 = Filter is disabled<br><b>MSEL2&lt;1:0&gt;:</b> Filter 2 Mask Select bits<br>11 = Acceptance Mask 3 selected                                                                                                                                                                                                                                                                                                                                                                                             |

| bit 22-21              | <ul> <li>0 = Filter is disabled</li> <li>MSEL2&lt;1:0&gt;: Filter 2 Mask Select bits</li> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> </ul>                                                                                                                                                                                                                                                                                                                           |

| bit 22-21              | <ul> <li>0 = Filter is disabled</li> <li>MSEL2&lt;1:0&gt;: Filter 2 Mask Select bits</li> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> </ul>                                                                                                                                                                                                                                                                                  |

|                        | 0 = Filter is disabled<br><b>MSEL2&lt;1:0&gt;:</b> Filter 2 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                                                                                                                                                                                                                    |