Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                                                               |

|----------------------------|-----------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                        |

| Core Processor             | MIPS32® microAptiv™                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                            |

| Speed                      | 200MHz                                                                                        |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, SQI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT                            |

| Number of I/O              | 120                                                                                           |

| Program Memory Size        | 2MB (2M x 8)                                                                                  |

| Program Memory Type        | FLASH                                                                                         |

| EEPROM Size                | -                                                                                             |

| RAM Size                   | 256K x 8                                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                   |

| Data Converters            | A/D 45x12b                                                                                    |

| Oscillator Type            | Internal                                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                             |

| Mounting Type              | Surface Mount                                                                                 |

| Package / Case             | 288-LFBGA                                                                                     |

| Supplier Device Package    | 288-LFBGA (15x15)                                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2025daa288t-i-4j             |

|                            |                                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin     | F                | Pin Numbe       | er                                           | Pin     | Buffer |                                                                              |

|---------|------------------|-----------------|----------------------------------------------|---------|--------|------------------------------------------------------------------------------|

| Name    | 169-pin<br>LFBGA | 176-pin<br>LQFP | 288-pin<br>LFBGA                             | Туре    | Туре   | Description                                                                  |

|         |                  |                 |                                              |         | PC     | DRTD                                                                         |

| RD0     | H3               | 79              | V5                                           | I/O     | ST     | PORTD is a bidirectional I/O port                                            |

| RD1     | G1               | 73              | M4                                           | I/O     | ST     |                                                                              |

| RD2     | G2               | 74              | R6                                           | I/O     | ST     |                                                                              |

| RD3     | G3               | 75              | T6                                           | I/O     | ST     |                                                                              |

| RD4     | F1               | 70              | K4                                           | I/O     | ST     |                                                                              |

| RD5     | F2               | 71              | L4                                           | I/O     | ST     |                                                                              |

| RD6     | K11              | 121             | V16                                          | I/O     | ST     |                                                                              |

| RD7     | M10              | 120             | T15                                          | I/O     | ST     |                                                                              |

| RD9     | H1               | 76              | U6                                           | I/O     | ST     |                                                                              |

| RD10    | H2               | 77              | V6                                           | I/O     | ST     |                                                                              |

| RD11    | N10              | 119             | U15                                          | I/O     | ST     |                                                                              |

| RD12    | J1               | 80              | U5                                           | I/O     | ST     |                                                                              |

| RD13    | J2               | 81              | N4                                           | I/O     | ST     |                                                                              |

| RD14    | E9               | 158             | J18                                          | I/O     | ST     |                                                                              |

| RD15    | F11              | 157             | J16                                          | I/O     | ST     |                                                                              |

|         |                  |                 |                                              |         | PC     | DRTE                                                                         |

| RE0     | C4               | 40              | B7                                           | I/O     | ST     | PORTE is a bidirectional I/O port                                            |

| RE1     | A4               | 36              | D8                                           | I/O     | ST     |                                                                              |

| RE2     | N3               | 99              | V10                                          | I/O     | ST     |                                                                              |

| RE3     | M3               | 98              | T9                                           | I/O     | ST     |                                                                              |

| RE4     | B3               | 43              | B6                                           | I/O     | ST     |                                                                              |

| RE5     | F3               | 17              | K3                                           | I/O     | ST     |                                                                              |

| RE6     | F6               | 23              | C11                                          | I/O     | ST     |                                                                              |

| RE7     | C7               | 24              | B11                                          | I/O     | ST     |                                                                              |

| RE8     | E6               | 25              | C10                                          | I/O     | ST     |                                                                              |

| RE9     | D6               | 26              | B10                                          | I/O     | ST     |                                                                              |

|         |                  |                 |                                              |         | P      | DRTF                                                                         |

| RF0     | L1               | 91              | V7                                           | I/O     | ST     | PORTF is a bidirectional I/O port                                            |

| RF1     | K3               | 90              | U7                                           | I/O     | ST     |                                                                              |

| RF2     | A3               | 41              | A7                                           | I/O     | ST     |                                                                              |

| RF3     | M1               | 93              | U8                                           | I/O     | ST     |                                                                              |

| RF4     | L3               | 44              | U9                                           | I/O     | ST     |                                                                              |

| RF5     | K2               | 89              | T7                                           | I/O     | ST     |                                                                              |

| RF8     | J3               | 82              | P4                                           | I/O     | ST     |                                                                              |

| RF12    | C6               | 27              | A11                                          | I/O     | ST     |                                                                              |

| RF13    | A6               | 28              | A10                                          | I/O     | ST     |                                                                              |

| Legend: | ST = Sch         | nmitt Trigge    | mpatible in<br>er input with<br>ansistor Log | CMOS le | vels   | Analog = Analog inputP = PowerO = OutputI = InputPPS = Peripheral Pin Select |

#### **TABLE 1-6:** PORTA THROUGH PORTK PINOUT I/O DESCRIPTIONS (CONTINUED)

| TABLE 1-12: | PMP PINOUT I/O DESCRIPTIONS |

|-------------|-----------------------------|

|-------------|-----------------------------|

|          |                  | Pin Numbe       | r                | <b>D</b> !  | Duffer         |                                                                                           |

|----------|------------------|-----------------|------------------|-------------|----------------|-------------------------------------------------------------------------------------------|

| Pin Name | 169-pin<br>LFBGA | 176-pin<br>LQFP | 288-pin<br>LFBGA | Pin<br>Type | Buffer<br>Type | Description                                                                               |

|          |                  |                 |                  | Pa          | arallel Mast   | er Port                                                                                   |

| PMA0     | H13              | 142             | N17              | I/O         | TTL/ST         | Parallel Master Port Address bit 0 Input (Buffered Slave modes) and Output (Master modes) |

| PMA1     | J11              | 136             | R18              | I/O         | TTL/ST         | Parallel Master Port Address bit 1 Input (Buffered Slave modes) and Output (Master modes) |

| PMA2     | C5               | 33              | B9               | 0           | —              | Parallel Master Port Address (Demultiplexed Master modes)                                 |

| PMA3     | H11              | 135             | R17              | 0           | —              |                                                                                           |

| PMA4     | J12              | 139             | N15              | 0           | —              |                                                                                           |

| PMA5     | A11              | 174             | B18              | 0           | —              |                                                                                           |

| PMA6     | F3               | 69              | K3               | 0           | _              |                                                                                           |

| PMA7     | B12              | 173             | E16              | 0           |                |                                                                                           |

| PMA8     | N2               | 96              | V9               | 0           | —              |                                                                                           |

| PMA9     | M2               | 95              | Т8               | 0           | _              |                                                                                           |

| PMA10    | K3               | 90              | U7               | 0           | _              |                                                                                           |

| PMA11    | L1               | 91              | V7               | 0           | _              |                                                                                           |

| PMA12    | J1               | 80              | U5               | 0           | _              |                                                                                           |

| PMA13    | J2               | 81              | N4               | 0           | _              |                                                                                           |

| PMA14    | G2               | 74              | R6               | 0           | _              |                                                                                           |

| PMA15    | G3               | 75              | T6               | 0           | _              |                                                                                           |

| PMCS1    | G2               | 74              | R6               | 0           | _              | Parallel Master Port Chip Select 1 Strobe                                                 |

| PMCS2    | G3               | 75              | T6               | 0           | _              | Parallel Master Port Chip Select 2 Strobe                                                 |

| PMD0     | C4               | 40              | B7               | I/O         | TTL/ST         | Parallel Master Port Data (Demultiplexed Master mode) or                                  |

| PMD1     | A4               | 36              | D8               | I/O         | TTL/ST         | Address/Data (Multiplexed Master modes)                                                   |

| PMD2     | N3               | 99              | V10              | I/O         | TTL/ST         |                                                                                           |

| PMD3     | M3               | 98              | T9               | I/O         | TTL/ST         |                                                                                           |

| PMD4     | B3               | 43              | B6               | I/O         | TTL/ST         |                                                                                           |

| PMD5     | B7               | 17              | A12              | I/O         | TTL/ST         |                                                                                           |

| PMD6     | F6               | 23              | C11              | I/O         | TTL/ST         |                                                                                           |

| PMD7     | C7               | 24              | B11              | I/O         | TTL/ST         |                                                                                           |

| PMD8     | K2               | 89              | T7               | I/O         | TTL/ST         |                                                                                           |

| PMD9     | L3               | 97              | U9               | I/O         | TTL/ST         |                                                                                           |

| PMD10    | A9               | 10              | A15              | I/O         | TTL/ST         |                                                                                           |

| PMD11    | G10              | 143             | N18              | I/O         | TTL/ST         | 1                                                                                         |

| PMD12    | A8               | 14              | C13              | I/O         | TTL/ST         |                                                                                           |

| PMD13    | G12              | 144             | M16              | I/O         | TTL/ST         | 1                                                                                         |

| PMD14    | L11              | 127             | V17              | I/O         | TTL/ST         | 1                                                                                         |

| PMD15    | H1               | 76              | U6               | I/O         | TTL/ST         |                                                                                           |

| PMALL    | H13              | 142             | N17              | 0           | <u> </u>       | Parallel Master Port Address Latch Enable Low Byte<br>(Multiplexed Master modes)          |

| PMALH    | J11              | 136             | R18              | 0           | _              | Parallel Master Port Address Latch Enable High Byte<br>(Multiplexed Master modes)         |

| PMRD     | B8               | 16              | A13              | 0           | <u> </u>       | Parallel Master Port Read Strobe                                                          |

| PMWR     | A7               | 15              | B13              | 0           | <u> </u>       | Parallel Master Port Write Strobe                                                         |

| Legend:  |                  | -               | atible input     | -           | An             | alog = Analog input P = Power                                                             |

Legend: CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

O = Output I = Input PPS = Peripheral Pin Select

#### TABLE 1-23: POWER, GROUND, AND VOLTAGE REFERENCE PINOUT I/O DESCRIPTIONS

| Pin Name |                                                               | Pin Numbe                                                                       | r                                                                                                                                                                      | Pin       | Buffer     | Description                                                                                                                                                         |  |  |  |

|----------|---------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|          | 169-pin<br>LFBGA                                              | 176-pin<br>LQFP                                                                 | 288-pin<br>LFBGA                                                                                                                                                       | Туре      | Туре       |                                                                                                                                                                     |  |  |  |

|          |                                                               |                                                                                 |                                                                                                                                                                        | Po        | wer and Gr | pund                                                                                                                                                                |  |  |  |

| AVdd     | D9                                                            | 3, 4                                                                            | F13, G13                                                                                                                                                               | P         | P          | Positive supply for analog modules. This pin must be                                                                                                                |  |  |  |

|          | 20                                                            | 0, 1                                                                            | 1 10, 010                                                                                                                                                              |           |            | connected at all times.                                                                                                                                             |  |  |  |

| AVss     | C8, D8                                                        | 5, 6                                                                            | F12, G12                                                                                                                                                               | Р         | Р          | Ground reference for analog modules. This pin must be connected at all times.                                                                                       |  |  |  |

| VDDIO    | B6, G9,<br>H9, J9,<br>K9, L6,<br>L7, L9                       | 19, 38, 86,<br>102, 117,<br>124, 155,<br>156, 165                               | F11, F15,<br>G11, G15,<br>H11, H12,<br>H13, H15,<br>J10, J15,<br>K10, L11,<br>L12, M12,<br>M13, M15,<br>N12, N13,<br>R9, R10,<br>R12, R13,                             | Ρ         | _          | Positive supply for peripheral logic and I/O pins. This pin must be connected at all times.                                                                         |  |  |  |

| VDDCORE  | B4, C9,<br>L8, N1                                             | 18, 39, 84,<br>116                                                              | R14<br>D7, D14,<br>R11, V4                                                                                                                                             | Р         |            | 1.8V positive supply for peripheral logic. This pin must be connected at all times.                                                                                 |  |  |  |

| Vss      | C2, F5,<br>G5, G6,<br>G7, G8,<br>H7, H8,<br>J7, J8, K7,<br>K8 | 21, 22, 29,<br>37, 48, 49,<br>83, 87, 94,<br>103, 115,<br>122, 123,<br>153, 154 | A5, B5,<br>C7, D10,<br>D11, D12,<br>D13, F9,<br>F10, G10,<br>H10, J11,<br>J12, J13,<br>K11, K12,<br>K13, K15,<br>L10, L13,<br>L15, M10,<br>M11, N10,<br>N11, R7,<br>R8 | Ρ         |            | Ground reference for logic, I/O pins, and USB. This pin must be connected at all times.                                                                             |  |  |  |

| HLVDIN   | B12                                                           | 173                                                                             | E16                                                                                                                                                                    | Р         | _          | Low-voltage detect pin.                                                                                                                                             |  |  |  |

| Vbat     | D10                                                           | 166                                                                             | F16                                                                                                                                                                    | Р         | —          | Positive supply for the battery backed section. It is<br>recommended to connect this pin to VDDIO if VBAT mode is<br>not used (i.e., not connected to the battery). |  |  |  |

| VDDR1V8  | H5, H6,<br>J5, J6, K5,<br>K6<br>( <b>Note 2</b> )             | 57, 58, 59,<br>60, 61, 62,<br>63, 67, 68,<br>72, 78<br>( <b>Note 2</b> )        | H6, H7,<br>H8, J6, J7,<br>J8, K6,<br>K7, K8,<br>L6, L7, L8<br>( <b>Note 2</b> )                                                                                        | Ρ         |            | Positive supply for the DDR2 SDRAM memory.                                                                                                                          |  |  |  |

| Legend:  | CMOS = C                                                      | MOS-compa                                                                       | atible input or                                                                                                                                                        | output    | Ana        | log = Analog input P = Power                                                                                                                                        |  |  |  |

|          | ST = Schm                                                     | itt Trigger in                                                                  | put with CMC<br>stor Logic inp                                                                                                                                         | OS levels | O =        | Output I = Input<br>= Peripheral Pin Select                                                                                                                         |  |  |  |

Note 1: The metal plane at the bottom of the device is internally tied to VSS1V8 and must be connected to 1.8V ground externally.

**2:** This pin must be tied to Vss through a 20k  $\Omega$  resistor in devices without DDR.

**3:** This pin is a No Connect in devices without DDR.

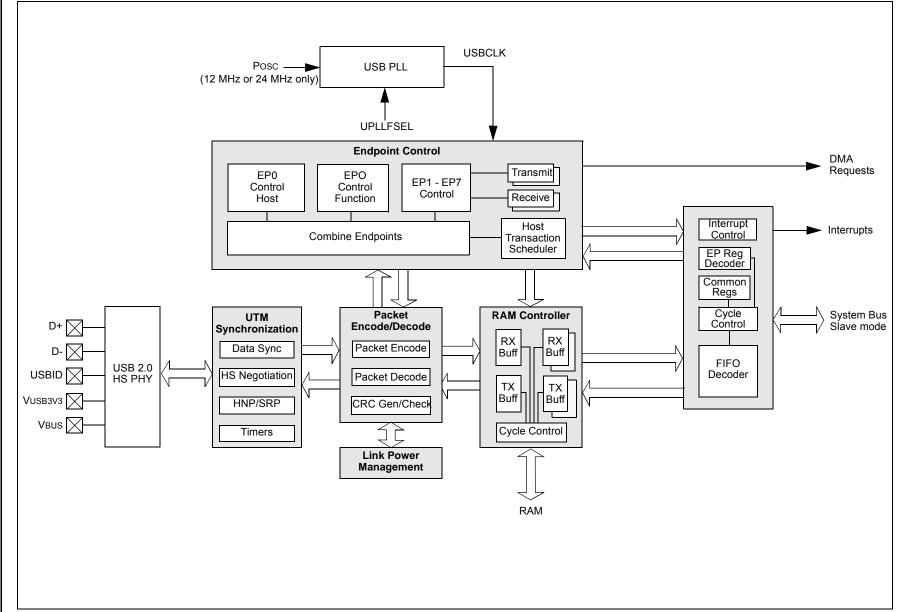

# FIGURE 11-1: PIC32MZ DA FAMILY USB INTERFACE DIAGRAM

PIC32MZ Graphics (DA) Family

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit Bit<br>29/21/13/5 28/20/12/4 |       | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|----------------------------------|-------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-1                            | R/W-1 | R/W-1             | R/W-1             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 31:24        | VPLEN<7:0>        |                   |                                  |       |                   |                   |                  |                  |  |  |  |  |  |  |

| 22:16        | R/W-0             | R/W-1             | R/W-0                            | R/W-1 | R/W-1             | R/W-1             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 23:16        |                   | WTCO              | N<3:0>                           |       | WTID<3:0>         |                   |                  |                  |  |  |  |  |  |  |

| 15:0         | R-1               | R-0               | R-0                              | R-0   | R-1               | R-1               | R-0              | R-0              |  |  |  |  |  |  |

| 15:8         |                   | DMACHA            | NS<3:0>                          |       | RAMBITS<3:0>      |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R-0               | R-1               | R-1                              | R-1   | R-0               | R-1               | R-1              | R-1              |  |  |  |  |  |  |

| 7:0          |                   | RXENDF            | PTS<3:0>                         |       | TXENDPTS<3:0>     |                   |                  |                  |  |  |  |  |  |  |

# **REGISTER 11-16: USBINFO: USB INFORMATION REGISTER**

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-24 VPLEN<7:0>: VBUS pulsing charge length bits Sets the duration of the VBUS pulsing charge in units of 546.1 µs. (The default setting corresponds to 32.77 ms.)

- bit 23-20 WTCON<3:0>: Connect/Disconnect filter control bits Sets the wait to be applied to allow for the connect/disconnect filter in units of 533.3 ns. The default setting corresponds to 2.667 µs.

- bit 19-6 WTID<3:0>: ID delay valid control bits Sets the delay to be applied from IDPULLUP being asserted to IDDIG being considered valid in units of 4.369ms. The default setting corresponds to 52.43ms.

- bit 15-12 DMACHANS<3:0>: DMA Channels bits These read-only bits provide the number of DMA channels in the USB module. For the PIC32MZ DA family, this number is 8.

#### bit 11-8 RAMBITS<3:0>: RAM address bus width bits These read-only bits provide the width of the RAM address bus. For the PIC32MZ DA family, this number is 12.

bit 7-4 RXENDPTS<3:0>: Included RX Endpoints bits

> This read-only register gives the number of RX endpoints in the design. For the PIC32MZ DA family, this number is 7.

bit 3-0 TXENDPTS<3:0>: Included TX Endpoints bits

These read-only bits provide the number of TX endpoints in the design. For the PIC32MZ DA family, this number is 7.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | -                 | _                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | _                 | _                 | _                 | —                 | _                 |                   | -                | _                |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 10.0         | _                 | _                 | -                 | —                 | _                 |                   | —                | _                |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | _                 | _                 | _                 | —                 | [pin name]R<3:0>  |                   |                  |                  |  |  |

#### **REGISTER 12-1:** [pin name]R: PERIPHERAL PIN SELECT INPUT REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-4 Unimplemented: Read as '0'

bit 3-0 [*pin name*]R<3:0>: Peripheral Pin Select Input bits Where [*pin name*] refers to the pins that are used to configure peripheral input mapping. See Table for input pin selection values.

**Note:** Register values can only be changed if the IOLOCK Configuration bit (CFGCON<13>) = 0.

#### REGISTER 12-2: RPnR: PERIPHERAL PIN SELECT OUTPUT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 |     |     | Bit<br>28/20/12/4 | Bit Bit<br>27/19/11/3 26/18/10/2 |       | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-----|-----|-------------------|----------------------------------|-------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0 | U-0 | U-0               | U-0                              | U-0   | U-0              | U-0              |  |  |

| 31:24        | —                 | _   | _   | _                 | _                                |       | -                | —                |  |  |

| 23:16        | U-0               | U-0 | U-0 | U-0               | U-0                              | U-0   | U-0              | U-0              |  |  |

| 23.10        | —                 | _   | _   | -                 | _                                | _     | -                | —                |  |  |

| 45.0         | U-0               | U-0 | U-0 | U-0               | U-0                              | U-0   | U-0              | U-0              |  |  |

| 15:8         | _                 | —   | _   | _                 | _                                | —     | _                | —                |  |  |

| 7.0          | U-0               | U-0 | U-0 | U-0               | R/W-0                            | R/W-0 | R/W-0            | R/W-0            |  |  |

| 7:0          | _                 | _   |     | _                 | RPnR<3:0>                        |       |                  |                  |  |  |

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-4 Unimplemented: Read as '0'

bit 3-0 **RPnR<3:0>:** Peripheral Pin Select Output bits See Table for output pin selection values.

**Note:** Register values can only be changed if the IOLOCK Configuration bit (CFGCON<13>) = 0.

# 14.2 Timer2-Timer9 Control Registers

# TABLE 14-1: TIMER2 THROUGH TIMER9 REGISTER MAP

| ess                         |                                 |           | Bits  |       |       |       |       |       |      |      |        |      |           |      |      |      |      |      |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|--------|------|-----------|------|------|------|------|------|------------|

| Virtual Address<br>(BF84_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7   | 22/6 | 21/5      | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 0200                        | T2CON                           | 31:16     | _     | —     | —     | —     | —     | —     | —    | -    | —      |      | _         | _    | -    | —    | —    | —    | 000        |

| 0200                        | 12001                           | 15:0      | ON    |       | SIDL  | —     | —     | —     |      | _    | TGATE  | -    | CKPS<2:0  | >    | T32  |      | TCS  | —    | 000        |

| 0210                        | TMR2                            | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —      | —    | —         | —    | —    |      | —    | —    | 00         |

| 0210                        |                                 | 15:0      |       |       |       |       |       |       |      | TMR2 | <15:0> |      |           |      |      |      |      |      | 00         |

| 0220                        | PR2                             | 31:16     | —     |       | —     | —     | —     | —     |      | —    | —      | —    | —         | —    | —    |      | —    | —    | 000        |

| 0220                        | 1142                            | 15:0      |       |       |       |       |       |       |      | PR2< | :15:0> |      |           |      |      |      |      |      | FFI        |

| 0400                        | T3CON                           | 31:16     | —     |       | —     | —     | —     | —     |      | _    | —      | —    | —         | —    | _    | —    | —    | —    | 000        |

| 0400                        | 10001                           | 15:0      | ON    |       | SIDL  | —     | —     | —     |      | _    | TGATE  | -    | TCKPS<2:0 | >    | _    |      | TCS  | —    | 000        |

| 0410                        | TMR3                            | 31:16     | —     |       | —     | —     | —     | —     |      | —    | —      | —    | —         | —    | —    |      | —    | —    | 000        |

| 0110                        | 111110                          | 15:0      |       |       |       |       |       |       |      | TMR3 | <15:0> |      |           |      |      |      |      |      | 000        |

| 0420                        | PR3                             | 31:16     | _     |       | —     | —     | —     | —     |      | _    | —      | _    | —         | _    | —    | —    | —    | —    | 000        |

| 0420                        | 110                             | 15:0      |       | -     |       |       |       |       | -    | PR3< | :15:0> |      |           |      |      | -    |      |      | FF         |

| 0600                        | T4CON                           | 31:16     | _     |       | —     | —     | —     | —     |      | _    | —      | _    | —         | _    | _    |      |      | —    | 00         |

| 0000                        | 14001                           | 15:0      | ON    |       | SIDL  | —     | —     |       |      | _    | TGATE  | -    | FCKPS<2:0 | >    | T32  | _    | TCS  | —    | 000        |

| 0610                        | TMR4                            |           |       |       |       |       |       |       |      |      |        |      | —         | 000  |      |      |      |      |            |

| 0010                        | 11011.44                        | 15:0      |       | -     |       |       |       |       | -    | TMR4 | <15:0> |      |           |      |      | -    |      |      | 000        |

| 0620                        | PR4                             | 31:16     | _     | _     | —     | —     | —     | —     | _    | -    | —      | -    | —         | _    | -    | —    | —    | —    | 000        |

| 0020                        | 1114                            | 15:0      |       | -     |       |       |       |       | -    | PR4< | :15:0> |      |           |      |      | -    |      |      | FFI        |

| 0800                        | T5CON                           | 31:16     | _     | _     | —     | —     | —     | —     | _    | -    | —      | -    | —         | _    | -    | —    | —    | —    | 000        |

| 0000                        | 13001                           | 15:0      | ON    | _     | SIDL  | —     | —     | —     | _    | _    | TGATE  | -    | FCKPS<2:0 | >    | _    | _    | TCS  | —    | 000        |

| 0810                        | TMR5                            | 31:16     | _     |       | —     | —     | —     | —     |      | _    | —      | _    | —         | _    | —    | —    | —    | —    | 000        |

| 0010                        | TIMIXO                          | 15:0      |       | -     |       |       |       |       | -    | TMR5 | <15:0> |      |           |      |      | -    |      |      | 000        |

| 0820                        | PR5                             | 31:16     | _     |       | —     | —     | —     | —     |      | _    | —      | _    | —         | _    | —    | —    | —    | —    | 000        |

| 0020                        | 110                             | 15:0      |       | -     |       |       |       |       | -    | PR5< | :15:0> |      |           |      |      | -    |      |      | FFI        |

| 000                         | T6CON                           | 31:16     | _     | _     | —     | —     | —     | —     | _    | -    | —      | -    | —         | _    | -    | —    | —    | —    | 000        |

| 0A00                        | TOCON                           | 15:0      | ON    | _     | SIDL  | —     | _     | —     | _    |      | TGATE  | -    | FCKPS<2:0 | >    | T32  | _    | TCS  | —    | 000        |

| 0 \ 1 0                     | TMR6                            | 31:16     | _     | _     | _     | _     | _     | _     | _    |      | _      |      | _         | _    |      | _    | _    | _    | 000        |

| UAIU                        | TIVIRO                          | 15:0      |       |       |       |       |       |       |      | TMR2 | <15:0> |      |           |      |      |      |      |      | 000        |

| 0A20                        | PR6                             | 31:16     | _     |       | _     | _     | _     | _     | _    | _    | —      |      | _         | _    | _    |      | _    | _    | 000        |

| UA2U                        | PRO                             | 15:0      |       |       |       |       |       |       |      | PR2< | :15:0> |      |           |      |      |      |      |      | FFI        |

| 0000                        | TTOON                           | 31:16     | _     | _     | _     | _     | _     | —     | _    | —    | _      | _    | _         | —    | _    | _    | _    | _    | 000        |

| 0000                        | T7CON                           | 15:0      | ON    |       | SIDL  | _     | _     | _     |      |      | TGATE  | -    | CKPS<2:0  | >    | _    |      | TCS  | _    | 000        |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

Note 1:

# **REGISTER 14-1:** TxCON: TYPE B TIMER CONTROL REGISTER ('x' = 2-9) (CONTINUED)

- bit 2 Unimplemented: Read as '0'

- bit 1 TCS: Timer Clock Source Select bit<sup>(1)</sup>

- 1 = External clock from TxCK pin

- 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

- **Note 1:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer1, Timer3, Timer5, Timer7, and Timer9). All timer functions are set through the even numbered timers.

- 2: While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

- 3: This bit is available only on even numbered timers (Timer2, Timer4, Timer6, and Timer8).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.04        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | —                 | _                 | _                 | INIT2SCHECK       | INIT2CO           | UNT<1:0>          | INIT2TY          | PE<1:0>          |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | INIT2CMD3<7:0>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | INIT2CMD2<7:0>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   | INIT2CMD1<7:0>    |                   |                   |                   |                   |                  |                  |  |  |  |

#### REGISTER 22-26: SQI1XCON4: SQI XIP CONTROL REGISTER 4

# Legend:

| Legena.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-29 Unimplemented: Read as '0'

- bit 28 INIT2SCHECK: Flash Initialization 2 Command Status Check bit

- 1 = Check the status after executing the INIT2 commands

- 0 = Do not check the status

- bit 27-26 INIT2COUNT<1:0>: Flash Initialization 2 Command Count bits

- 11 = INIT2CMD1, INIT2CMD2, and INIT2CMD3 are sent

- 10 = INIT2CMD1 and INIT2CMD2 are sent, but INIT2CMD3 is still pending

- 01 = INIT2CMD1 is sent, but INIT2CMD2 and INIT2CMD3 are still pending

- 00 = No commands are sent

- bit 25-24 INIT2TYPE<1:0>: Flash Initialization 2 Command Type bits

- 11 = Reserved

- 10 = INIT2 commands are sent in Quad Lane mode

- 01 = INIT2 commands are sent in Dual Lane mode

- 00 = INIT2 commands are sent in Single Lane mode

- bit 24-16 **INIT2CMD3<7:0>:** Flash Initialization Command 3 bits Third command of the Flash initialization.

- bit 15-8 **INIT2CMD2<7:0>:** Flash Initialization Command 2 bits Second command of the Flash initialization.

- bit 7-0 **INIT2CMD1<7:0>:** Flash Initialization Command 1 bits First command of the Flash initialization.

**Note:** Some Flash devices require write enable and sector unprotect commands before write/read operations and this register is useful in working with those Flash types (XIP mode only)

| ess (                                   |                                    | ۵         |        |         |        |       |        |       |       | В          | its         |         |       |          |          |       |        |        | s          |

|-----------------------------------------|------------------------------------|-----------|--------|---------|--------|-------|--------|-------|-------|------------|-------------|---------|-------|----------|----------|-------|--------|--------|------------|

| Virtual Address<br>(BF82_#)             | Register<br>Name                   | Bit Range | 31/15  | 30/14   | 29/13  | 28/12 | 27/11  | 26/10 | 25/9  | 24/8       | 23/7        | 22/6    | 21/5  | 20/4     | 19/3     | 18/2  | 17/1   | 16/0   | All Resets |

| 2600                                    | U4MODE <sup>(1)</sup>              | 31:16     | _      | —       | —      | _     | —      |       | —     | _          | SLPEN       | ACTIVE  | —     | _        | _        | CLKSE | L<1:0> | RUNOVF | 000        |

| 2000                                    | OHNODE                             | 15:0      | ON     | —       | SIDL   | IREN  | RTSMD  |       | UEN   | <1:0>      | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE  | L<1:0> | STSEL  | 000        |

| 2610                                    | U4STA <sup>(1)</sup>               | 31:16     |        |         |        | MASK  | <7:0>  |       |       |            |             |         |       | ADDR     | <7:0>    |       |        |        | 000        |

| 2010                                    | 0431A                              | 15:0      | UTXISE | EL<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT       | URXISI      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR  | OERR   | URXDA  | 011        |

| 2620                                    | U4TXREG                            | 31:16     | -      | —       | —      | —     | —      | —     | —     | —          | _           | _       | —     | —        | —        | _     | —      | —      | 000        |

| 2020 0417/1120                          |                                    | 15:0      | _      | —       | _      | -     | —      | _     | _     | TX8        |             |         |       | Transmit | Register |       |        |        | 000        |

| 2630                                    | U4RXREG                            | 31:16     |        | —       | -      | -     | _      | -     | —     | -          | —           | —       | -     | -        | -        | —     | —      | —      | 0000       |

| 2030                                    | 04NANEG                            | 15:0      | -      | —       | —      | —     | —      | —     | —     | RX8        |             |         |       | Receive  | Register |       |        |        | 0000       |

| 2640                                    | U4BRG <sup>(1)</sup>               | 31:16     | -      | —       | —      | —     | —      | —     | —     | —          | _           | _       | —     | —        | —        | _     | —      | —      | 0000       |

| 2040                                    | 15:0 Baud Rate Generator Prescaler |           |        |         |        |       | 0000   |       |       |            |             |         |       |          |          |       |        |        |            |

| 2800 U5MODE <sup>(1)</sup>              |                                    | 31:16     | _      | _       | —      | —     | —      | _     | _     | _          | SLPEN       | ACTIVE  | _     | _        | _        | CLKSE | L<1:0> | RUNOVF | 0000       |

|                                         |                                    | 15:0      | ON     | —       | SIDL   | IREN  | RTSMD  | _     | UEN   | <1:0>      | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE  | L<1:0> | STSEL  | 0000       |

| 0040                                    | U5STA <sup>(1)</sup>               | ADDR<7:0> |        |         |        |       |        |       | 0000  |            |             |         |       |          |          |       |        |        |            |

| 2810                                    | 055TA.                             | 15:0      | UTXISE | EL<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT       | URXISI      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR  | OERR   | URXDA  | 0110       |

| 0000                                    | U5TXREG                            | 31:16     | _      | _       | —      | -     | —      | -     | _     | -          | _           | _       | —     | -        | -        | _     | —      | —      | 0000       |

| 2820                                    | USIAREG                            | 15:0      | —      | —       | —      | _     | —      | _     | —     | TX8        |             |         |       | Transmit | Register |       |        |        | 0000       |

| 2020                                    | U5RXREG                            | 31:16     | _      | _       | —      | _     | —      | _     | _     | _          | _           | _       | —     | —        | _        | _     | —      | _      | 0000       |

| 2830                                    | USKAREG                            | 15:0      | —      | —       | —      | _     | —      | _     | —     | RX8        |             |         |       | Receive  | Register |       |        |        | 0000       |

| 2840                                    | U5BRG <sup>(1)</sup>               | 31:16     | -      | —       | —      | —     | —      | —     | —     | —          | _           | _       | —     | —        | —        | _     | —      | —      | 0000       |

| 2040                                    | USBRG /                            | 15:0      |        |         |        |       |        |       | Bau   | d Rate Gen | erator Pres | caler   |       |          |          |       |        |        | 0000       |

| 24.00                                   | U6MODE <sup>(1)</sup>              | 31:16     | -      | _       | _      | _     | _      | _     | _     | _          | SLPEN       | ACTIVE  | _     | _        | _        | CLKSE | L<1:0> | RUNOVF | 0000       |

| 2A00                                    | UDE                                | 15:0      | ON     | —       | SIDL   | IREN  | RTSMD  | _     | UEN   | <1:0>      | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE  | L<1:0> | STSEL  | 0000       |

| 0440                                    | U6STA <sup>(1)</sup>               | 31:16     |        |         |        | MASK  | <7:0>  |       |       |            |             |         |       | ADDR     | <7:0>    |       |        |        | 0000       |

| 2A10                                    | 0651A.                             | 15:0      | UTXISE | EL<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT       | URXISI      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR  | OERR   | URXDA  | 0110       |

|                                         |                                    | 31:16     | _      | —       | _      | _     | —      | _     | —     | _          | _           | —       | _     | _        | _        | _     | _      | _      | 0000       |

| 2A20 U6TXREG 15:0 TX8 Transmit Register |                                    |           | 0000   |         |        |       |        |       |       |            |             |         |       |          |          |       |        |        |            |

| 0400                                    |                                    | 31:16     | _      | —       | _      | _     | —      | _     | —     | -          | —           | —       | —     | —        | —        | —     | —      | —      | 0000       |

| 2A30                                    | U6RXREG                            | 15:0      | _      | _       | _      | _     | _      | _     | _     | RX8        |             |         |       | Receive  | Register |       |        |        | 0000       |

| 24.40                                   | U6BRG <sup>(1)</sup>               | 31:16     | _      | _       | _      | _     | _      | _     | _     | —          | —           | —       | —     | _        | _        | —     | —      | _      | 0000       |

| 2A40                                    | UOBRG"                             | 15:0      |        |         |        |       |        |       | Bau   | d Rate Gen | erator Pres | caler   |       |          |          |       |        |        | 0000       |

### TABLE 24-1: UART1 THROUGH UART6 REGISTER MAP (CONTINUED)

This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more informa-Note 1: tion.

## REGISTER 24-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 12        | IREN: IrDA <sup>®</sup> Encoder and Decoder Enable bit                                                                               |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------|

|               | 1 = IrDA is enabled                                                                                                                  |

|               | 0 = IrDA is disabled                                                                                                                 |

| bit 11        | RTSMD: Mode Selection for UxRTS Pin bit                                                                                              |

|               | 1 = UxRTS pin is in Simplex mode                                                                                                     |

| 1:1.40        | 0 = UxRTS pin is in Flow Control mode                                                                                                |

| bit 10        | Unimplemented: Read as '0'                                                                                                           |

| bit 9-8       | UEN<1:0>: UARTx Module Enable bits <sup>(1)</sup>                                                                                    |

|               | 11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register            |

|               | 10 = UxTX, UxRX, UxCTS and UxRTS pins are enabled and used                                                                           |

|               | 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by corresponding bits                                   |

|               | in the PORTx register                                                                                                                |

|               | 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register |

| bit 7         | WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit                                                                       |

|               | 1 = Wake-up enabled                                                                                                                  |

| <b>h</b> it C | 0 = Wake-up disabled                                                                                                                 |

| bit 6         | LPBACK: UARTx Loopback Mode Select bit<br>1 = Loopback mode is enabled                                                               |

|               | 0 = Loopback mode is disabled                                                                                                        |

| bit 5         | ABAUD: Auto-Baud Enable bit                                                                                                          |

|               | 1 = Enable baud rate measurement on the next character – requires reception of Sync character (0x55);                                |

|               | cleared by hardware upon completion                                                                                                  |

| L:1 4         | 0 = Baud rate measurement disabled or completed                                                                                      |

| bit 4         | <b>RXINV:</b> Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'                                                           |

|               | 0 = UxRX Idle state is '1'                                                                                                           |

| bit 3         | BRGH: High Baud Rate Enable bit                                                                                                      |

|               | 1 = High-Speed mode – 4x baud clock enabled                                                                                          |

|               | 0 = Standard Speed mode – 16x baud clock enabled                                                                                     |

| bit 2-1       | PDSEL<1:0>: Parity and Data Selection bits                                                                                           |

|               | <ul><li>11 = 9-bit data, no parity</li><li>10 = 8-bit data, odd parity</li></ul>                                                     |

|               | 01 = 8-bit data, even parity                                                                                                         |

|               | 00 = 8-bit data, no parity                                                                                                           |

| bit 0         | STSEL: Stop Selection bit                                                                                                            |

|               | 1 = 2 Stop bits                                                                                                                      |

|               | 0 = 1 Stop bit                                                                                                                       |

|               |                                                                                                                                      |

Note 1: These bits are present for legacy compatibility, and are superseded by PPS functionality on these devices (see Section 12.4 "Peripheral Pin Select (PPS)" for more information).

| Bit<br>Range | Bit<br>31/23/15/7         | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1          | Bit<br>24/16/8/0 |  |

|--------------|---------------------------|-------------------|-------------------|-------------------|----------------------|-------------------|---------------------------|------------------|--|

| 24.24        | U-0                       | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0                       | U-0              |  |

| 31:24        | _                         | _                 | _                 | _                 | _                    | _                 | _                         | —                |  |

| 00.40        | U-0                       | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0                       | U-0              |  |

| 23:16        |                           | _                 | _                 | -                 | -                    | _                 | _                         | —                |  |

| 45.0         | R-0                       | R/W-0             | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0                     | R/W-0            |  |

| 15:8         | BUSY                      | IRQM              | <1:0>             | INCM              | <1:0>                | MODE16            | MODE                      | =<1:0>           |  |

| 7.0          | R/W-0                     | R/W-0             | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0                     | R/W-0            |  |

| 7:0          | WAITB<1:0> <sup>(1)</sup> |                   |                   | WAITM             | <3:0> <sup>(1)</sup> |                   | WAITE<1:0> <sup>(1)</sup> |                  |  |

#### REGISTER 25-2: PMMODE: PARALLEL PORT MODE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **BUSY:** Busy bit (Master mode only)

- 1 = Port is busy

- 0 = Port is not busy

- bit 14-13 **IRQM<1:0>:** Interrupt Request Mode bits

- 11 = Reserved, do not use

- 10 = Interrupt generated when Read Buffer 3 is read or Write Buffer 3 is written (Buffered PSP mode) or on a read or write operation when PMA<1:0> =11 (Addressable Slave mode only)

- 01 = Interrupt generated at the end of the read/write cycle

- 00 = No Interrupt generated

- bit 12-11 INCM<1:0>: Increment Mode bits

- 11 = Slave mode read and write buffers auto-increment (MODE<1:0> = 00 only)

- 10 = Decrement ADDR<15:0> by 1 every read/write cycle<sup>(2)</sup>

- 01 = Increment ADDR<15:0> by 1 every read/write cycle<sup>(2)</sup>

- 00 = No increment or decrement of address

#### bit 10 MODE16: 8/16-bit Mode bit

- 1 = 16-bit mode: a read or write to the data register invokes a single 16-bit transfer

0 = 8-bit mode: a read or write to the data register invokes a single 8-bit transfer

- bit 9-8 **MODE<1:0>:** Parallel Port Mode Select bits

- 11 = Master mode 1 (PMCSx, PMRD/PMWR, PMENB, PMA<x:0>, PMD<7:0> and PMD<8:15><sup>(3)</sup>)

- 10 = Master mode 2 (PMCSx, PMRD, PMWR, PMA<x:0>, PMD<7:0> and PMD<8:15><sup>(3)</sup>)

- 01 = Enhanced Slave mode, control signals (PMRD, PMWR, PMCS, PMD<7:0> and PMA<1:0>)

- 00 = Legacy Parallel Slave Port, control signals (PMRD, PMWR, PMCS and PMD<7:0>)

## bit 7-6 WAITB<1:0>: Data Setup to Read/Write Strobe Wait States bits<sup>(1)</sup>

- 11 = Data wait of 4 TPB; multiplexed address phase of 4 TPB

- 10 = Data wait of 3 TPB; multiplexed address phase of 3 TPB

- 01 = Data wait of 2 TPB; multiplexed address phase of 2 TPB

- 00 = Data wait of 1 TPB; multiplexed address phase of 1 TPB (default)

- **Note 1:** Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPBCLK cycle for a write operation; WAITB = 1 TPBCLK cycle, WAITE = 0 TPBCLK cycles for a read operation.

- 2: Address bits, A15 and A14, are not subject to automatic increment/decrement if configured as Chip Select CS2 and CS1.

- 3: These pins are active when MODE16 = 1 (16-bit mode).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                 | _                 | _                 | -                 | —                 | _                 | _                | —                |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | -                 | -                 | _                 | -                 | —                 | -                 | -                | —                |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | _                 | _                 | _                 |                   |                   | TRPD              | <11:8>           |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | TRPD<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |

# REGISTER 26-4: EBIFTRPD: EXTERNAL BUS INTERFACE FLASH TIMING REGISTER

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-12 Unimplemented: Read as '0'

bit 11-0 TRPD<11:0>: Flash Timing bits

These bits define the number of clock cycles to hold the external Flash memory in reset.

**Step 4:** The user sets the ON bit to '1', which enables the ADC control clock. The following ADCx activation sequence is to be followed at all times:

**Step 5:** The user waits for the interrupt/polls the BGVR-RDY bit (ADCCON2<31>) and the WKRDYx bit (ADCANCON<15,13:8>) = 1, which signals that the device analog environment (band gap and VREF) is ready.

**Step 6:** Set the DIGENx bit (ADCCON3<15,13:8>) to '1', which enables the digital circuitry to immediately begin processing incoming triggers to perform data conversions.

Standard non-interleaved dedicated Class\_1 ADCx throughput rate formula is shown in Equation 29-1.

# EQUATION 29-1: THROUGHPUT RATE

```

ADC Throughput Rate = 1/((Sample time + Conversion time)(TAD))

= 1 / ((SAMC+# bit resolution+1)(TAD))

```

Example:

SAMC = 3 TAD, 12-bit mode, TAD = 20 ns = 50 MHz: Throughput rate: = 1 / ((3+13)(20 ns))

= 1/(16 \* 20 ns)

= 3.125 msps

# TABLE 29-1: PIC32MZXXDAXX INTERLEAVED ADC THROUGHPUT RATES

| #No.of Interleaved | ADC TAD(min) = 20ns (50Mhz max) |                       |                      |                      |  |  |  |  |

|--------------------|---------------------------------|-----------------------|----------------------|----------------------|--|--|--|--|

| ADC Possible       | 12-bit<br>(max.) msps           | 10-bit<br>(max.) msps | 8-bit<br>(max.) msps | 6-bit<br>(max.) msps |  |  |  |  |

| 1                  | 3.125 msps                      | 3.571 msps            | 4.167 msps           | 5.0 msps             |  |  |  |  |

| 2                  | 6.250 msps                      | 7.143 msps            | 8.333 msps           | 10.00 msps           |  |  |  |  |

| 3                  | 8.330 msps                      | 10.00 msps            | 12.50 msps           | 12.50 msps           |  |  |  |  |

| 4                  | 12.50 msps                      | 12.50 msps            | 16.667 msps          | 16.667 msps          |  |  |  |  |

**Note:** Interleaved ADCs in this context means connecting the same analog source signal to multiple dedicated Class\_1 ADCs (i.e., ADC0-ADC5), and using independent staggered trigger sources accordingly for each interleaved ADC.

- Note 1: Prior to enabling the ADC module, the user application must copy the ADC calibration data (DEVADC0-DEVADC4, DEVADC7; see Register 41-8) from the Configuration memory into the ADC Configuration registers (ADC0CFG-ADC4CFG, ADC7CFG).

- 2: If VDDIO is greater than 2.5V, set the AICPMPEN bit (ADCCON1<12>) and the IOANCPEN bit (CFGCON<7>) to '0'. If VDDIO is less than 2.5V, set both bits to '1'.

|              | GAP REGISTER      |                   |                   |                   |                   |                   |                  |                  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        | —                 | —                 | _                 | _                 |                   | _                 | —                | _                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | —                 | —                 | -                 | _                 | _                 | -                 | —                | _                |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15.0         | —                 | —                 | -                 | _                 | _                 | -                 | —                | _                |  |

| 7:0          | U-0               | R/W-0             | R/W-0             | R/W-1             | R/W-0             | R/W-0             | R/W-1            | R/W-0            |  |

| 7:0          | _                 |                   |                   | B2                | BIPKTGP<6:0       | )>                |                  |                  |  |

#### REGISTER 31-25: EMAC1IPGT: ETHERNET CONTROLLER MAC BACK-TO-BACK INTERPACKET GAP REGISTER

#### Legend:

| Legena.           |                  |                          |                    |  |

|-------------------|------------------|--------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

#### bit 31-7 Unimplemented: Read as '0'

#### bit 6-0 B2BIPKTGP<6:0>: Back-to-Back Interpacket Gap bits

This is a programmable field representing the nibble time offset of the minimum possible period between the end of any transmitted packet to the beginning of the next. In Full-Duplex mode, the register value should be the desired period in nibble times minus 3. In Half-Duplex mode, the register value should be the desired period in nibble times minus 6. In Full-Duplex the recommended setting is 0x15 (21d), which represents the minimum IPG of 0.96  $\mu$ s (in 100 Mbps) or 9.6  $\mu$ s (in 10 Mbps). In Half-Duplex mode, the recommended setting is 0x12 (18d), which also represents the minimum IPG of 0.96  $\mu$ s (in 100 Mbps) or 9.6  $\mu$ s (in 100 Mbps) (in 100 Mbps) or 9.6  $\mu$ s (in 100 Mbps) (in 100 Mbps) (in 100 Mbps) or 9

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

# 36.0 GRAPHICS LCD (GLCD) CONTROLLER

Note 1: This data sheet summarizes the features of the PIC32MZ Graphics (DA) Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 54. "Graphics LCD Controller" (DS60001379), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Graphics LCD (GLCD) Controller is designed to directly interface with display panels with up to 24-bit color depth.

The GLCD Controller transfers display data from a memory device and formats it for a display device. The memory may be internal RAM or DDR2.