Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                                        |

|----------------------------|-----------------------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                            |

| Speed                      | 200MHz                                                                                        |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, SQI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT                            |

| Number of I/O              | 120                                                                                           |

| Program Memory Size        | 2MB (2M x 8)                                                                                  |

| Program Memory Type        | FLASH                                                                                         |

| EEPROM Size                | -                                                                                             |

| RAM Size                   | 256K x 8                                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                   |

| Data Converters            | A/D 45x12b                                                                                    |

| Oscillator Type            | Internal                                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                             |

| Mounting Type              | Surface Mount                                                                                 |

| Package / Case             | 169-LFBGA                                                                                     |

| Supplier Device Package    | 169-LFBGA (11x11)                                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2025dab169t-i-hf             |

|                            |                                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 7: PIN NAMES FOR 288-PIN DEVICES (CONTINUED)

| 288-P                | IN LFBGA (BOTTOM VIE                                                                                           | N)  |   |                    |                      |          |

|----------------------|----------------------------------------------------------------------------------------------------------------|-----|---|--------------------|----------------------|----------|

|                      |                                                                                                                | A1  |   |                    | V1                   |          |

| PI                   | C32MZ1025DAA288<br>C32MZ1025DAB288<br>C32MZ1064DAA288                                                          | F6  |   |                    | N6                   |          |

| PI<br>PI<br>PI<br>PI | C32MZ1064DAB288<br>C32MZ2025DAA288<br>C32MZ2025DAB288<br>C32MZ2025DAB288<br>C32MZ2064DAA288<br>C32MZ2064DAB288 | F13 |   |                    | N1                   | 3<br>V18 |

|                      | Polarity Indica                                                                                                | A1  | 8 |                    |                      |          |

| Ball/Pin<br>Number   | Full Pin Name                                                                                                  |     |   | Ball/Pin<br>Number | Full Pin Name        |          |

| V3                   | DDRA15                                                                                                         |     | - | V11                | ERXDV/ECRSDV/RH13    |          |

| V4                   | VDDCORE                                                                                                        |     |   | V12                | ERXD3/RH9            |          |

| V5                   | RTCC/RPD0/RD0                                                                                                  |     |   | V13                | ETXD2/RH0            |          |

| V6                   | SCK4/RD10                                                                                                      |     |   | V14                | ETXD0/RJ8            |          |

| V7                   | GD6/EBIA11/RPF0/PMA11/RF0                                                                                      |     |   | V15                | ETXERR/RJ0           |          |

| V8                   | GD21/EBIA23/RH15                                                                                               |     |   | V16                | ETXEN/RPD6/RD6       |          |

|                      |                                                                                                                |     |   | V17                | GD1/EBID14/PMD14/RA4 |          |

| V9                   | GD3/EBIA8/RPG0/PMA8/RG0                                                                                        |     |   | V 17               |                      |          |

The RPn pins can be used by remappable peripherals. See Table 1 and Table 4 for the available peripherals and 12.4 "Peripheral Pin Select (PPS)" for restrictions.

2: Every I/O port pin (RAx-RKx) can be used as a change notification pin (CNAx-CNKx). See 12.0 "I/O Ports" for more information.

**3:** Shaded pins are 5V tolerant.

4: This pin must be tied to Vss through a 20k  $\Omega$  resistor when DDR is not connected in the system.

5: This pin is a No Connect when DDR is not connected in the system.

6: These pins are restricted to input functions only.

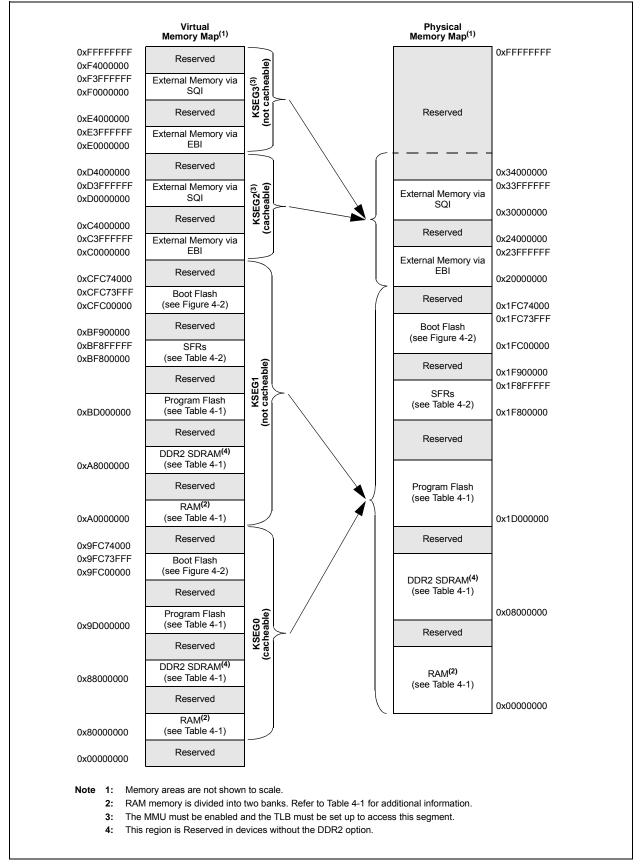

## FIGURE 4-1: PIC32MZ DA FAMILY MEMORY MAP

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 |                   | —                 | _                 | -                 | _                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 |                   | —                 | —                 |                   | _                 | _                | -                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 |                   | —                 | —                 |                   | _                 | _                | -                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | _                 | _                 | _                 | GROU             | P<1:0>           |

#### **REGISTER 4-7:** SBTxELOG2: SYSTEM BUS TARGET 'x' ERROR LOG REGISTER 2 ('x' = 0-13)

#### Legend:

| R = Readable bit |  |

|------------------|--|

|------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

|-------------------|------------------|------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

bit 31-3 Unimplemented: Read as '0'

- bit 1-0 GROUP<1:0>: Requested Permissions Group bits

- 11 = Group 3

- 10 = Group 2

- 01 = Group 1

- 00 = Group 0

Note: Refer to Table 4-8 for the list of available targets and their descriptions.

#### **REGISTER 4-8:** SBTxECON: SYSTEM BUS TARGET 'x' ERROR CONTROL REGISTER ('x' = 0.13)

|              |                   | x = 0.13          |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 31:24        | —                 | _                 | _                 | _                 | _                 | _                 | -                | ERRP             |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 |                   | _                 | —                 |                   | _                 | —                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | _                 | _                 | -                | _                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | —                 |                   |                   |                   |                   |                   |                  | —                |

#### Legend:

| 0                 |                  |                                    |

|-------------------|------------------|------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

bit 31-25 Unimplemented: Read as '0'

bit 24 ERRP: Error Control bit

1 = Report protection group violation errors

0 = Do not report protection group violation errors

Unimplemented: Read as '0' bit 23-0

Note: Refer to Table 4-8 for the list of available targets and their descriptions.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 21.24        | R/W-1             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | PWPULOCK          | —                 | —                 | —                 | _                 |                   | _                | —                |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | PWP<23:16>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8         | PWP<15:8>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   |                   |                   | PWP<              | :7:0>             |                   |                  |                  |  |  |  |

#### REGISTER 5-6: NVMPWP: PROGRAM FLASH WRITE-PROTECT REGISTER

#### Legend:

| Legena.           |                               |                      |                    |

|-------------------|-------------------------------|----------------------|--------------------|

| R = Readable bit  | Readable bit W = Writable bit |                      | read as '0'        |

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared | x = Bit is unknown |

bit 31 **PWPULOCK:** Program Flash Memory Page Write-protect Unlock bit

1 = Register is not locked and can be modified

0 = Register is locked and cannot be modified

This bit is only clearable and cannot be set except by any reset.

- bit 30-24 **Unimplemented:** Read as '0'

- bit 23-0 PWP<23:0>: Flash Program Write-protect (Page) Address bits

Physical memory below address 0x1Dxxxxxx is write protected, where 'xxxxxx' is specified by PWP<23:0>. When PWP<23:0> has a value of '0', write protection is disabled for the entire program Flash. If the specified address falls within the page, the entire page and all pages below the current page will be protected.

**Note:** The bits in this register are only writable when the NVMKEY unlock sequence is followed.

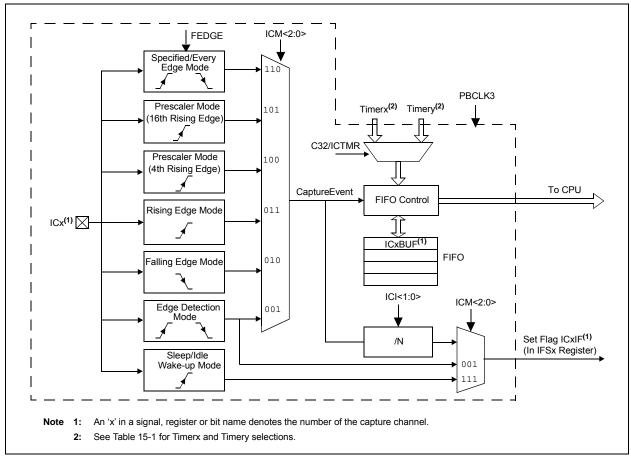

## 15.0 INPUT CAPTURE

Note: This data sheet summarizes the features of the PIC32MZ Graphics (DA) Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 15. "Input Capture" (DS60001122), which is available from the Documentation > Manual Reference section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin.

Capture events are caused by the following:

- Capture timer value on every edge (rising and falling), specified edge first

- Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of six 16-bit timers for the time base, or two of six 16-bit timers together to form a 32-bit timer. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during Sleep and Idle modes

- · Interrupt on input capture event

- 4-word FIFO buffer for capture values; Interrupt optionally generated after 1, 2, 3, or 4 buffer locations are filled

- Input capture can also be used to provide additional sources of external interrupts

## FIGURE 15-1: INPUT CAPTURE BLOCK DIAGRAM

| Bit<br>Range                      | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04                             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 31:24                             |                   | YEAR1             | 0<3:0>            |                   |                   | YEAR0             | 1<3:0>           |                  |

| 00.40                             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 23:16                             |                   | MONTH             | 10<3:0>           |                   | MONTH01<3:0>      |                   |                  |                  |

| 45.0                              | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15:8                              |                   | DAY10             | <3:0>             |                   | DAY01<3:0>        |                   |                  |                  |

| 7.0                               | U-0               | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 7:0                               | _                 | -                 | _                 |                   |                   | WDAYO             | 1<3:0>           |                  |

|                                   |                   |                   |                   |                   |                   |                   |                  |                  |

| Legend:                           |                   |                   |                   |                   |                   |                   |                  |                  |

| R = Readable bit W = Writable bit |                   |                   | e bit             | U = Unimple       | emented bit, re   | ead as '0'        |                  |                  |

'0' = Bit is cleared

## REGISTER 20-4: RTCDATE: REAL-TIME CLOCK DATE VALUE REGISTER

bit 31-28 YEAR10<3:0>: Binary-Coded Decimal Value of Years bits, 10 digits

'1' = Bit is set

bit 27-24 YEAR01<3:0>: Binary-Coded Decimal Value of Years bits, 1 digit

bit 23-20 MONTH10<3:0>: Binary-Coded Decimal Value of Months bits, 10 digits; contains a value from 0 to 1

bit 19-16 **MONTH01<3:0>:** Binary-Coded Decimal Value of Months bits, 1 digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary-Coded Decimal Value of Days bits, 10 digits; contains a value from 0 to 3

bit 11-8 DAY01<3:0>: Binary-Coded Decimal Value of Days bits, 1 digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

-n = Value at POR

bit 3-0 WDAY01<3:0>: Binary-Coded Decimal Value of Weekdays bits,1 digit; contains a value from 0 to 6

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

x = Bit is unknown

#### REGISTER 22-20: SQI1BDRXDSTAT: SQI BUFFER DESCRIPTOR DMA RECEIVE STATUS REGISTER

|              |                   | LOIDIEN           |                   |                   |                   |                   |                  |                  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 31:24        | U-0               | U-0               | U-0               | R-x               | R-x               | R-x               | R-x              | U-0              |  |

|              | —                 | _                 | _                 |                   | RXSTATE<3:0>      |                   |                  |                  |  |

| 23:16        | U-0               | U-0               | U-0               | R-x               | R-x               | R-x               | R-x              | R-x              |  |

|              | —                 | _                 | _                 |                   |                   |                   |                  |                  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15:8         |                   | —                 | _                 | _                 | _                 |                   | _                | _                |  |

| 7.0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | R-x              | R-x              |  |

| 7:0          | RXCURBUFLEN<7:0>  |                   |                   |                   |                   |                   |                  |                  |  |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-29 Unimplemented: Read as '0'

bit 28-25 **RXSTATE<3:0>:** Current DMA Receive State Status bits These bits provide information on the current DMA receive states.

bit 24-21 Unimplemented: Read as '0'

bit 20-16 **RXBUFCNT<4:0>:** DMA Buffer Byte Count Status bits These bits provide information on the internal buffer space.

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **RXCURBUFLEN<7:0>:** Current DMA Receive Buffer Length Status bits These bits provide the length of the current DMA receive buffer.

## REGISTER 22-21: SQI1THR: SQI THRESHOLD CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | _                 | —                 | —                 | _                | _                |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | —                 | _                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 |                   | THRES             | 6<3:0>           |                  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-4 Unimplemented: Read as '0'

bit 3-0 **THRES<3:0>:** SQI Control Threshold Value bits

The SQI control threshold interrupt is asserted when the amount of space indicated by THRES<6:0> is available in the SQI control buffer.

# 27.1 Crypto Engine Control Registers

## TABLE 27-2: CRYPTO ENGINE REGISTER MAP

| ess                         |                  |               |       |         |       |         |          |       |        | I      | Bits          |       |        |        |         |         |         |        | 6          |

|-----------------------------|------------------|---------------|-------|---------|-------|---------|----------|-------|--------|--------|---------------|-------|--------|--------|---------|---------|---------|--------|------------|

| Virtual Address<br>(BF8E_#) | Register<br>Name | Bit Range     | 31/15 | 30/14   | 29/13 | 28/12   | 27/11    | 26/10 | 25/9   | 24/8   | 23/7          | 22/6  | 21/5   | 20/4   | 19/3    | 18/2    | 17/1    | 16/0   | All Resets |

| 5000                        | CEVER            | 31:16         |       |         |       | REVISIO | ON<7:0>  |       |        |        |               |       |        | VERSIC | )N<7:0> |         |         |        | 0000       |

| 3000                        | CLVLK            | 15:0          |       |         |       |         |          |       |        | ID<    | <15:0>        |       |        |        |         |         |         |        | 0000       |

| 5004                        | CECON            | 31:16         | _     | _       | _     | —       | _        | -     | —      | _      | _             | —     | —      | _      | _       | —       | —       | _      | 0000       |

| 0004                        | OLOON            | 15:0          | —     | —       | —     | —       | —        | —     | —      | —      | SWAPOEN       | SWRST | SWAPEN | —      |         | BDPCHST | BDPPLEN | DMAEN  | 0000       |

| 5008                        | CEBDADDR -       | 31:16         |       |         |       |         |          |       |        | BDPAD  | DR<31:0>      |       |        |        |         |         |         |        | 0000       |

|                             |                  | 15:0          |       |         |       |         |          |       |        | 001710 | 511 0110      |       |        |        |         |         |         |        | 0000       |

| 500C                        | CERDPADDR        | 31:16         |       |         |       |         |          |       |        | BASEA  | DDR<31:0>     |       |        |        |         |         |         |        | 0000       |

|                             |                  | 15:0          |       |         |       |         |          |       |        |        |               |       |        |        |         |         |         |        | 0000       |

| 5010                        | CESTAT           | 31:16         | ER    | RMODE<2 | :0>   | E       | RROP<2:0 | >     | ERRPHA |        | —             | —     |        | BDSTA  | TE<3:0> |         | START   | ACTIVE | ++         |

|                             |                  | 15:0          |       |         |       |         |          |       |        |        | RL<15:0>      |       |        |        |         |         |         |        | 0000       |

| 5014                        | CEINTSRC         | 31:16         | _     | _       |       | _       |          |       | —      |        | _             |       |        | _      | -       |         |         |        | 0000       |

|                             |                  | 15:0          | —     |         |       | _       | _        |       | _      |        | _             |       | _      | _      | AREIF   | PKTIF   | CBDIF   | PENDIF | 0000       |

| 5018                        | CEINTEN          | 31:16         | _     |         | _     | _       | _        | _     | _      | _      | _             | _     | _      | _      |         | PKTIE   |         |        | 0000       |

|                             |                  | 15:0<br>31:16 | _     |         | _     |         | _        | _     | _      | _      | _             | _     | _      | _      |         |         |         |        | 0000       |

| 501C                        | CEPOLLCON        | 15:0          |       | —       | —     | —       | —        | —     | —      |        | <br>CON<15:0> | —     | _      | —      | —       | —       | —       | _      | 0000       |

| -                           |                  | 31:16         | _     | _       | _     |         | _        | _     | _      |        |               | _     |        |        |         |         | _       | _      | 0000       |

| 5020                        | CEHDLEN          | 15:0          | _     |         |       |         |          |       |        |        |               |       |        | HDRLE  | N<7:0>  |         |         |        | 0000       |

|                             |                  | 31:16         | _     |         |       |         |          |       | _      |        |               | _     |        |        |         | _       | _       | _      | 0000       |

| 5024                        | CETRLLEN         | 15:0          | _     | _       |       | _       |          |       |        |        |               |       |        | TRLRLE |         |         |         |        | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

|              |                   |                   |                   |                   |                   | -                 |                           |                  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1          | Bit<br>24/16/8/0 |  |  |

| 24.24        | R/W-0                     | R/W-0            |  |  |

| 31:24        | ADCSE             | L<1:0>            |                   | CONCLKDIV<5:0>    |                   |                   |                           |                  |  |  |

| 00.40        | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0                     | R/W-0            |  |  |

| 23:16        | DIGEN7            | —                 | _                 | DIGEN4            | DIGEN3            | DIGEN2            | DIGEN1                    | DIGEN0           |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0, HS, HC       | R/W-0                     | R-0, HS, HC      |  |  |

| 15:8         | V                 | REFSEL<2:0        | >                 | TRGSUSP           | UPDIEN            | UPDRDY            | SAMP <sup>(1,2,3,4)</sup> | RQCNVRT          |  |  |

| 7:0          | R/W-0             | R/W, HC           | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                     | R/W-0            |  |  |

| 7:0          | GLSWTRG           | GSWTRG            |                   |                   | ADINS             | SEL<5:0>          |                           |                  |  |  |

#### REGISTER 29-3: ADCCON3: ADC CONTROL REGISTER 3

| Legend:           | HC = Hardware Set | HS = Hardware Cleared                   |

|-------------------|-------------------|-----------------------------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0'      |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared x = Bit is unknown |

bit 31-30 ADCSEL<1:0>: Analog-to-Digital Clock Source (TCLK) bits

11 = FRC 10 = REFCLK3 01 = System Clock (Tcy) 00 = PBCLK3

#### bit 29-24 CONCLKDIV<5:0>: Analog-to-Digital Control Clock (Tq) Divider bits

## bit 23 **DIGEN7:** Shared ADC (ADC7) Digital Enable bit 1 = ADC7 is digital enabled 0 = ADC7 is digital disabled

## bit 22-21 Unimplemented: Read as '0'

#### bit 20 DIGEN4: ADC4 Digital Enable bit

- 1 = ADC4 is digital enabled

- 0 = ADC4 is digital disabled

## bit 19 **DIGEN3:** ADC3 Digital Enable bit

- 1 = ADC3 is digital enabled

- 0 = ADC3 is digital disabled

- **Note 1:** The SAMP bit has the highest priority and setting this bit will keep the S&H circuit in Sample mode until the bit is cleared. Also, usage of the SAMP bit will cause settings of SAMC<9:0> bits (ADCCON2<25:16>) to be ignored.

- 2: The SAMP bit only connects Class 2 and Class 3 analog inputs to the shared ADC, ADC7. All Class 1 analog inputs are not affected by the SAMP bit.

- **3:** The SAMP bit is not a self-clearing bit and it is the responsibility of application software to first clear this bit and only after setting the RQCNVRT bit to start the analog-to-digital conversion.

- 4: Normally, when the SAMP and RQCNVRT bits are used by software routines, all TRGSRCx<4:0> bits and STRGSRC<4:0> bits should be set to '00000' to disable all external hardware triggers and prevent them from interfering with the software-controlled sampling command signal SAMP and with the software-controlled trigger RQCNVRT.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        | FLTEN19           | MSEL1             | 9<1:0>            |                   | I                 | SEL19<4:0>        | •                |                  |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | FLTEN18           | MSEL18<1:0>       |                   |                   | I                 | SEL18<4:0>        | •                |                  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | FLTEN17           | MSEL1             | 7<1:0>            |                   | I                 | SEL17<4:0>        | •                |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | FLTEN16           | MSEL1             | 6<1:0>            |                   | I                 | SEL16<4:0>        | •                |                  |

## REGISTER 30-14: CIFLTCON4: CAN FILTER CONTROL REGISTER 4

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

| bit 31                 | FLTEN19: Filter 19 Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | 1 = Filter is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                        | 0 = Filter is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| bit 30-29              | MSEL19<1:0>: Filter 19 Mask Select bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                        | 11 = Acceptance Mask 3 selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                        | 10 = Acceptance Mask 2 selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                        | 01 = Acceptance Mask 1 selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                        | 00 = Acceptance Mask 0 selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| bit 28-24              | FSEL19<4:0>: FIFO Selection bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                        | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                        | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                        | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                        | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                        | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                        | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| bit 23                 | FLTEN18: Filter 18 Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                        | 1 = Filter is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |