Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

シメテリ

| Product Status             | Active                                                                                        |

|----------------------------|-----------------------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                            |

| Speed                      | 200MHz                                                                                        |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, SQI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT                            |

| Number of I/O              | 120                                                                                           |

| Program Memory Size        | 2MB (2M x 8)                                                                                  |

| Program Memory Type        | FLASH                                                                                         |

| EEPROM Size                |                                                                                               |

| RAM Size                   | 256K x 8                                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                   |

| Data Converters            | A/D 45x12b                                                                                    |

| Oscillator Type            | Internal                                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                             |

| Mounting Type              | Surface Mount                                                                                 |

| Package / Case             | 288-LFBGA                                                                                     |

| Supplier Device Package    | 288-LFBGA (15x15)                                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2025dab288-i-4j              |

|                            |                                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# REGISTER 6-1: RCON: RESET CONTROL REGISTER

| bit 4 | <b>WDTO:</b> Watchdog Timer Time-out Flag bit<br>1 = WDT Time-out has occurred<br>0 = WDT Time-out has not occurred             |

|-------|---------------------------------------------------------------------------------------------------------------------------------|

| bit 3 | <b>SLEEP:</b> Wake From Sleep Flag bit<br>1 = Device was in Sleep mode<br>0 = Device was not in Sleep mode                      |

| bit 2 | <b>IDLE:</b> Wake From Idle Flag bit<br>1 = Device was in Idle mode<br>0 = Device was not in Idle mode                          |

| bit 1 | <b>BOR:</b> Brown-out Reset Flag bit <sup>(1)</sup><br>1 = Brown-out Reset has occurred<br>0 = Brown-out Reset has not occurred |

| bit 0 | <b>POR:</b> Power-on Reset Flag bit <sup>(1)</sup><br>1 = Power-on Reset has occurred<br>0 = Power-on Reset has not occurred    |

Note 1: User software must clear this bit to view the next detection.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   |                   |                   |                   |                   |                   |                  | -                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 |                   |                   |                   |                   |                  | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | —                 | _                 | _                 | _                 | —                 | _                | _                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 |                   | _                 | _                | VREGS            |

# REGISTER 6-4: PWRCON: POWER CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

bit 31-1 Unimplemented: Read as '0'

bit 0 VREGS: Voltage Regulator Stand-by Enable bit

1 = Voltage regulator will remain active during Sleep

0 = Voltage regulator will go to Stand-by mode during Sleep

### **TABLE 10-3**: DMA CHANNEL 0 THROUGH CHANNEL 7 REGISTER MAP (CONTINUED)

| SS                          |                                 |               |             |       |               |       |               |       |      | Bits         | 5                        |                  |                 |                  |                  |        |             |             |            |

|-----------------------------|---------------------------------|---------------|-------------|-------|---------------|-------|---------------|-------|------|--------------|--------------------------|------------------|-----------------|------------------|------------------|--------|-------------|-------------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15       | 30/14 | 29/13         | 28/12 | 27/11         | 26/10 | 25/9 | 24/8         | 23/7                     | 22/6             | 21/5            | 20/4             | 19/3             | 18/2   | 17/1        | 16/0        | All Resets |

|                             | DCH4SSA                         | 31:16<br>15:0 |             |       |               |       |               |       |      | CHSSA<       | 31:0>                    |                  |                 |                  |                  |        |             |             | XXX<br>XXX |

| 13A0                        | DCH4DSA                         | 31:16<br>15:0 |             |       |               |       |               |       |      | CHDSA<       | :31:0>                   |                  |                 |                  |                  |        |             |             | XXX<br>XXX |

| 13B0                        | DCH4SSIZ                        | 31:16<br>15:0 | —           | _     | —             | —     | —             | _     | —    | —<br>CHSSIZ< | —<br>:15 <sup>.</sup> 0> | —                | _               | —                | —                | —      | —           | _           | 000        |

| 13C0                        | DCH4DSIZ                        | 31:16<br>15:0 | _           |       |               |       |               |       |      |              |                          |                  |                 |                  |                  |        |             |             |            |

| 13D0                        | DCH4SPTR                        | 31:16<br>15:0 | _           | _     | _             | _     | _             | _     | —    | CHSPTR       |                          | _                | _               | _                | _                | —      | _           | —           | 000        |

| 13E0                        | DCH4DPTR                        | 31:16<br>15:0 | _           | _     | —             | _     | _             | _     | —    | CHDPTR       | _                        | _                | _               | _                | _                | _      | —           | —           | 000        |

| 3F0                         | DCH4CSIZ                        | 31:16<br>15:0 | _           | _     | _             | _     | _             | _     | _    | CHCSIZ       |                          | _                | _               | _                | _                | _      | _           | _           | 000        |

| 1400                        | DCH4CPTR                        | 31:16<br>15:0 | _           | _     | —             | —     | —             | —     | —    | CHCPTR       |                          | _                | _               | _                | _                | —      | —           | _           | 000        |

| 1410                        | DCH4DAT                         | 31:16<br>15:0 | _           | _     | _             | _     | _             | _     | _    | CHPDAT       | _                        | _                | _               | _                | _                | —      | _           | _           | 000        |

| 1420                        | DCH5CON                         | 31:16         |             |       |               | CHPIG |               |       |      | -            | _                        | _                | _               | _                | _                | _      | _           | _           | 77(        |

|                             | DCH5ECON                        | 15:0<br>31:16 | CHBUSY<br>— | _     | CHPIGNEN<br>— |       | CHPATLEN<br>— |       |      | CHCHNS<br>—  | CHEN                     | CHAED            | CHCHN           | CHAEN<br>CHAIR   | —<br>Q<7:0>      | CHEDET | CHPR        | <1:0>       | 000<br>001 |

|                             |                                 | 15:0<br>31:16 | _           | _     | _             | CHSIR | Q<7:0>        | _     | _    | _            | CFORCE<br>CHSDIE         | CABORT<br>CHSHIE | PATEN<br>CHDDIE | SIRQEN<br>CHDHIE | AIRQEN<br>CHBCIE |        | —<br>CHTAIE | —<br>CHERIE | FF0        |

| 1440                        | DCH5INT                         | 15:0<br>31:16 | -           | _     | —             | _     | -             | _     | —    | —            | CHSDIF                   | CHSHIF           | CHDDIF          | CHDHIF           | CHBCIF           | CHCCIF | CHTAIF      | CHERIF      |            |

| 1450                        | DCH5SSA                         | 15:0<br>31:16 |             |       |               |       |               |       |      | CHSSA<       | :31:0>                   |                  |                 |                  |                  |        |             |             | xxx        |

| 1460                        | DCH5DSA                         | 15:0          |             |       |               |       |               |       |      | CHDSA<       | :31:0>                   |                  |                 |                  |                  |        |             |             | xxx        |

| 1470                        | DCH5SSIZ                        | 31:16<br>15:0 | —           | _     | —             | —     | —             | _     | —    | CHSSIZ       |                          | _                | _               | —                | _                | _      | —           | _           | 000<br>xxx |

| 1480                        | DCH5DSIZ                        | 31:16<br>15:0 | _           | _     |               | _     | —             |       |      | —<br>CHDSIZ∢ |                          | —                | _               | _                | _                | _      |             | _           | 000<br>xxx |

| 1490                        | DCH5SPTR                        | 31:16<br>15:0 | _           | _     | _             | _     | —             | —     | _    |              | —<br><15:0>              | —                | _               | —                | _                | —      | —           | —           | 000        |

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for Note 1: more information.

### Virtual Address (BF80\_#) Bits Bit Range Resets Register Name 31/15 30/14 29/13 28/12 27/11 26/10 25/9 24/8 23/7 22/6 21/5 20/4 19/3 18/2 17/1 16/0 ₹ 31:16 0000 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ IC4R 1444 15:0 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_\_\_\_ \_ \_ IC4R<3:0> 0000 31:16 0000 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ 1448 IC5R 15:0 IC5R<3:0> 0000 \_\_\_\_ — \_ — \_ — — — \_ — — \_ 31:16 0000 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ 144C IC6R 15:0 \_ \_\_\_\_ \_ \_ \_ \_ \_ \_ \_ IC6R<3:0> 0000 — \_ \_ 31:16 \_ \_ \_ 0000 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ 1450 IC7R 15:0 \_ \_\_\_\_ IC7R<3:0> 0000 — — \_ — — — — — — — 31:16 0000 — \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ 1454 IC8R 15:0 \_ IC8R<3:0> 0000 \_ \_ \_\_\_\_ \_ — — — — — — — 31:16 \_ \_ \_ \_\_\_\_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ 0000 1458 IC9R 15:0 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ IC9R<3:0> 0000 31:16 \_ \_ \_ 0000 \_ \_ \_\_\_\_ — \_ \_ \_ \_ \_ — — 1460 OCFAR 15:0 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ OCFAR<3:0> 0000 31:16 — \_ \_ \_ \_ \_ \_ \_ \_ \_\_\_\_ \_ \_ \_ 0000 \_\_\_\_ \_\_\_\_ 1468 U1RXR 15:0 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ U1RXR<3:0> 0000 31:16 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ 0000 \_ \_\_\_\_ \_ \_\_\_\_ **U1CTSR** 146C 15:0 \_ \_ U1CTSR<3:0> 0000 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ 31:16 0000 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ 1470 U2RXR 15:0 \_ \_ \_ U2RXR<3:0> 0000 \_ \_ \_ \_ \_ \_ \_ \_ \_ 31:16 \_ \_ \_ \_\_\_\_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_\_\_\_ \_ 0000 1474 **U2CTSR** 15:0 \_ \_ \_ \_\_\_\_ \_ \_ \_ \_ \_ \_ \_ \_ U2CTSR<3:0> 0000 31:16 \_ \_ \_ 0000 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ — 1478 **U3RXR** 15:0 U3RXR<3:0> \_ \_ 0000 \_ \_\_\_\_ \_ \_ \_ \_ \_\_\_\_ \_ \_ \_ 31:16 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ 0000 147C **U3CTSR** 15:0 U3CTSR<3:0> 0000 \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ \_ 31:16 \_ 0000 \_ \_ \_\_\_\_ \_ \_ \_ \_\_\_\_ \_ \_ \_ \_ \_ \_ 1480 U4RXR 15:0 U4RXR<3:0> 0000 \_ \_ \_\_\_\_ \_ \_\_\_\_ \_ \_ \_ \_ \_\_\_\_ \_ \_\_\_\_ 31:16 \_ \_ \_ \_ \_ 0000 \_\_\_\_ \_\_\_\_ — \_ \_ \_\_\_\_ — — \_ 1484 U4CTSR 15:0 U4CTSR<3:0> 0000 \_ \_ \_ \_ \_ \_ \_

PIC32MZ

Graphics

(DA) Family

# TABLE 12-13: PERIPHERAL PIN SELECT INPUT REGISTER MAP (CONTINUED)

0

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 12-14: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| SS                          |                  |           |       |       |       |       |       |       |      | E    | Bits |      |      |      |      |       |         |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|---------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1    | 16/0 | All Resets |

| 1654                        | RPF5R            | 31:16     |       | —     | _     |       |       | _     | _    |      | _    | _    | _    |      |      | —     | _       | —    | 0000       |

| 1                           |                  | 15:0      | —     | _     | _     | -     | -     | _     |      | -    | _    | _    | -    | _    |      | RPF5  | R<3:0>  |      | 0000       |

| 1000                        | DDEAD            | 31:16     | _     | _     | _     | —     | -     | —     | _    | -    | _    | _    | —    | _    | _    | -     | —       | —    | 0000       |

| 1660 RPF8R                  |                  | 15:0      | _     |       | _     | _     | _     | _     |      | _    | _    | _    | _    | _    |      | RPF8  | R<3:0>  |      | 0000       |

| 4070                        | 005400           | 31:16     | _     |       | _     | _     | _     | _     |      | _    | _    | _    | _    | _    | _    | —     | —       | _    | 0000       |

| 1670                        | RPF12R           | 15:0      | _     |       | _     | _     | —     | _     |      | —    | _    | _    | _    | _    |      | RPG12 | 2R<3:0> |      | 0000       |

| 4000                        | DDOOD            | 31:16     | _     |       | _     | _     | —     | _     |      | —    | _    | _    | _    | _    | _    | —     | —       | _    | 0000       |

| 1680                        | RPG0R            | 15:0      | _     |       | _     | _     | —     | _     |      | —    | _    | _    | _    | _    |      | RPG1  | R<3:0>  |      | 0000       |

| 4004                        | 00040            | 31:16     | _     |       | _     | _     | —     | _     |      | —    | _    | _    | _    | _    | _    | —     | —       | _    | 0000       |

| 1684                        | RPG1R            | 15:0      | _     |       | _     | -     | _     | _     |      | _    | _    | _    | _    | _    |      | RPG1  | R<3:0>  |      | 0000       |

| 4000                        | 00070            | 31:16     | _     |       | _     | _     | —     | _     |      | —    | _    | _    | _    | _    | _    | —     | —       | _    | 0000       |

| 169C                        | RPG7R            | 15:0      | —     | _     | _     |       | _     | —     | _    | _    | _    | _    | _    | _    |      | RPG7  | R<3:0>  |      | 0000       |

| 40.40                       | DDOOD            | 31:16     | _     |       | _     | -     | _     | _     |      | _    | _    | _    | _    | _    | _    | —     | _       | _    | 0000       |

| 16A0                        | RPG8R            | 15:0      | _     | _     | _     |       | _     | _     | _    | _    | _    | _    | _    | _    |      | RPG8  | R<3:0>  |      | 0000       |

| 10.1.1                      | DDOOD            | 31:16     | _     | —     | _     | _     | _     | _     | —    | _    | _    | —    | _    | —    | _    | —     | —       | —    | 0000       |

| 16A4                        | RPG9R            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPG9  | R<3:0>  |      | 0000       |

PIC32MZ Graphics (DA) Family

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 14-1: TIMER2 THROUGH TIMER9 REGISTER MAP (CONTINUED)

|                             |                                 |                                                |       |       |       |       |       |       | (    | /    |        |      |          |      |      |      |      |      |            |

|-----------------------------|---------------------------------|------------------------------------------------|-------|-------|-------|-------|-------|-------|------|------|--------|------|----------|------|------|------|------|------|------------|

| ess                         |                                 |                                                |       |       |       |       |       |       |      | Bi   | its    |      |          |      |      |      |      |      |            |

| Virtual Address<br>(BF84_#) | Register<br>Name <sup>(1)</sup> | Bit Range                                      | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7   | 22/6 | 21/5     | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

|                             | TMR7                            | 31:16                                          | —     |       | _     |       | —     | _     | _    | —    | —      |      | _        |      |      | _    |      | _    | 0000       |

| 0010                        |                                 | 15:0                                           |       |       |       |       |       |       |      | TMR3 | <15:0> |      |          |      |      |      |      |      | 0000       |

| 0C20                        | PR7                             | 31:16                                          |       |       |       |       |       |       |      |      |        |      |          |      |      |      |      |      |            |

| 0020                        |                                 | R7         15:0         PR3<15:0>         FFFF |       |       |       |       |       |       |      |      |        |      |          |      |      |      |      |      |            |

| 0500                        | T8CON                           | 31:16                                          | —     | _     | _     | -     | _     |       | _    | _    | _      | -    |          | -    | -    | -    | -    | -    | 0000       |

|                             |                                 | 15:0                                           | ON    | _     | SIDL  | _     | _     | _     | —    | —    | TGATE  |      | CKPS<2:0 | >    | T32  | _    | TCS  | _    | 0000       |

| 0E10                        | TMR8                            | 31:16                                          | _     | _     | _     |       |       |       | _    | _    | -      |      |          |      |      |      |      |      | 0000       |

|                             | TIVINO                          | 15:0                                           |       |       |       |       |       |       |      | TMR4 | <15:0> |      |          |      |      |      |      |      | 0000       |

| 0E20                        | PR8                             | 31:16                                          | —     | —     | _     |       |       |       | _    | -    | -      |      |          |      |      |      |      |      | 0000       |

| 0220                        | 110                             | 15:0                                           |       |       |       |       |       |       |      | PR4< | 15:0>  |      |          |      |      |      |      |      | FFFF       |

| 1000                        | T9CON                           | 31:16                                          | _     | _     | —     | _     | —     | -     | —    | —    | —      | -    | _        | _    | _    | _    | _    | _    | 0000       |

| 1000                        | 13001                           | 15:0                                           | ON    | _     | SIDL  | _     | —     | -     | —    | —    | TGATE  |      | CKPS<2:0 | >    | _    | _    | TCS  | _    | 0000       |

| 1010                        | TMR9                            | 31:16                                          | _     | _     | —     | _     | —     | -     | —    | —    | —      | -    | _        | _    | _    | _    | _    | _    | 0000       |

| 1010                        | 110113                          | 15:0                                           |       |       |       |       |       |       |      | TMR5 | <15:0> |      |          |      |      |      |      |      | 0000       |

| 1020                        | PR9                             | 31:16                                          | —     | —     | _     |       |       |       | _    | -    | -      |      |          |      |      |      |      |      | 0000       |

| 1020                        | 113                             | 15:0                                           |       |       |       |       |       |       |      | PR5< | 15:0>  |      |          |      |      |      |      |      | FFFF       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

PIC32MZ Graphics (DA) Family

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                 | —                 | —                 | _                 | _                | —                |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 23:16        |                   | MONT              | H10<3:0>          |                   |                   | MONTH             | 01<3:0>          |                  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15:8         |                   | DAY               | 10<1:0>           |                   |                   | DAY01             | <3:0>            |                  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 7:0          | _                 | _                 | _                 |                   |                   | WDAY0             | 1<3:0>           |                  |

# REGISTER 20-6: ALRMDATE: ALARM DATE VALUE REGISTER

# Legend:

| Legenu.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-24 Unimplemented: Read as '0'

bit 23-20 MONTH10<3:0>: Binary Coded Decimal value of months bits, 10 digits; contains a value from 0 to 1

bit 19-16 MONTH01<3:0>: Binary Coded Decimal value of months bits, 1 digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary Coded Decimal value of days bits, 10 digits; contains a value from 0 to 3

bit 11-8 DAY01<3:0>: Binary Coded Decimal value of days bits, 1 digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

bit 3-0 WDAY01<3:0>: Binary Coded Decimal value of weekdays bits, 1 digit; contains a value from 0 to 6

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-----------------------|-----------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                     | _                     | _                 | _                 | _                 | _                 | _                | _                |

| 00.40        | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                     | —                     | _                 | _                 | —                 | —                 | —                | —                |

|              | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | CS2 <sup>(1)</sup>    | CS1 <sup>(3)</sup>    |                   |                   |                   | -10.05            |                  |                  |

|              | ADDR15 <sup>(2)</sup> | ADDR14 <sup>(4)</sup> |                   |                   | ADDR              | <13:8>            |                  |                  |

| 7:0          | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              |                       |                       |                   | ADDR<             | 7:0>              |                   |                  |                  |

### REGISTER 25-3: PMADDR: PARALLEL PORT ADDRESS REGISTER

# Legend:

| Logona.           |                  |                                         |  |

|-------------------|------------------|-----------------------------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |  |

### bit 31-16 **Unimplemented:** Read as '0'

- bit 15 **CS2:** Chip Select 2 bit<sup>(1)</sup>

- 1 = Chip Select 2 is active

- 0 = Chip Select 2 is inactive

- bit 15 ADDR<15>: Target Address bit 15<sup>(2)</sup>

- bit 14 CS1: Chip Select 1 bit<sup>(3)</sup>

- 1 = Chip Select 1 is active 0 = Chip Select 1 is inactive

- bit 14 ADDR<14>: Target Address bit 14<sup>(4)</sup>

- bit 13-0 ADDR<13:0>: Address bits

- **Note 1:** When the CSF<1:0> bits (PMCON<7:6>) = 10 or 01.

- **2:** When the CSF<1:0> bits (PMCON<7:6>) = 00.

- **3:** When the CSF<1:0> bits (PMCON<7:6>) = 10.

- **4:** When the CSF<1:0> bits (PMCON<7:6>) = 00 or 01.

**Note:** If the DUALBUF bit (PMCON<17>) = 0, the bits in this register control both read and write target addressing. If the DUALBUF bit = 1, the bits in this register are not used. In this instance, use the PMRADDR register for Read operations and the PMWADDR register for Write operations.

# FIGURE 27-6: FORMAT OF BD\_DSTADDR

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31-24        |                   | BD_DSTADDR<31:24> |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 23-16        |                   | BD_DSTADDR<23:16> |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 15-8         |                   | BD_DSTADDR<15:8>  |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7-0          |                   | BD_DSTADDR<7:0>   |                   |                   |                   |                   |                  |                  |  |  |  |  |

bit 31-0 **BD\_DSTADDR:** Buffer Destination Address The destination address of the buffer that needs to be passed through the PE-CRDMA for encryption or authentication. This address must be on a 32-bit boundary.

# FIGURE 27-7: FORMAT OF BD\_NXTADDR

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31-24        |                   |                   |                   | BD_NXTAD          | DR<31:24>         |                   |                  |                  |

| 23-16        |                   | BD_NXTADDR<23:16> |                   |                   |                   |                   |                  |                  |

| 15-8         |                   | BD_NXTADDR<15:8>  |                   |                   |                   |                   |                  |                  |

| 7-0          |                   |                   |                   | BD_NXTAI          | DDR<7:0>          |                   |                  |                  |

## bit 31-0 **BD\_NXTADDR:** Next BD Pointer Address Has Next Buffer Descriptor The next buffer can be a next segment of the previous buffer or a new packet.

# FIGURE 27-8: FORMAT OF BD\_UPDPTR

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31-24        |                   |                   |                   | BD_UPDAD          | DR<31:24>         |                   |                  |                  |

| 23-16        |                   | BD_UPDADDR<23:16> |                   |                   |                   |                   |                  |                  |

| 15-8         |                   |                   |                   | BD_UPDAD          | DR<15:8>          |                   |                  |                  |

| 7-0          |                   |                   |                   | BD_UPDA           | DDR<7:0>          |                   |                  |                  |

### bit 31-0 BD\_UPDADDR: UPD Address Location

The update address has the location where the CRDMA results are posted. The updated results are the ICV values, key output values as needed.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0                     | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | —                       | _                 | —                | —                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0                     | U-0               | U-0              | U-0              |

| 23:16        | -                 | _                 | —                 | _                 | —                       | _                 | —                | —                |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | R/W-0                   | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | —                 | _                 | LOAD              | TRNGMODE <sup>(1)</sup> | CONT              | PRNGEN           | TRNGEN           |

| 7.0          | R/W-0             | R/W-1             | R/W-1             | R/W-0             | R/W-0                   | R/W-1             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | PLE               | N<7:0>                  |                   |                  |                  |

# REGISTER 28-2: RNGCON: RANDOM NUMBER GENERATOR CONTROL REGISTER

# Legend:

| Legena:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31-13 | Unimplemented: Read as '0'                                                                                                                              |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 12    | LOAD: Device Select bit                                                                                                                                 |

|           | This bit is self-clearing and is used to load the seed from the TRNG (i.e., the random value) as a seed to the PRNG.                                    |

| bit 11    | TRNGMODE: True Random Number Generator Mode bit <sup>(1)</sup>                                                                                          |

|           | <ul><li>1 = Enhanced TRNG mode is selected</li><li>0 = Normal TRNG mode is selected</li></ul>                                                           |

| bit 10    | CONT: PRNG Number Shift Enable bit                                                                                                                      |

|           | <ul> <li>1 = The PRNG random number is shifted every cycle</li> <li>0 = The PRNG random number is shifted when the previous value is removed</li> </ul> |

| bit 9     | PRNGEN: PRNG Operation Enable bit                                                                                                                       |

|           | <ul><li>1 = PRNG operation is enabled</li><li>0 = PRNG operation is not enabled</li></ul>                                                               |

| bit 8     | TRNGEN: TRNG Operation Enable bit                                                                                                                       |

|           | 1 = TRNG operation is enabled                                                                                                                           |

|           | 0 = TRNG operation is not enabled                                                                                                                       |

| bit 7-0   | PLEN<7:0>: PRNG Polynomial Length bits                                                                                                                  |

|           | These bits contain the length of the polynomial used for the PRNG.                                                                                      |

# Note 1: This bit is effective only when the TRNGEN bit is set to '1'.

1

# REGISTER 31-1: ETHCON1: ETHERNET CONTROLLER CONTROL REGISTER 1 (CONTINUED)

- bit 7 AUTOFC: Automatic Flow Control bit

- 1 = Automatic Flow Control is enabled

- 0 = Automatic Flow Control is disabled

Setting this bit will enable automatic Flow Control. If set, the full and empty watermarks are used to automatically enable and disable the Flow Control, respectively. When the number of received buffers BUFCNT (ETHSTAT<16:23>) rises to the full watermark, Flow Control is automatically enabled. When the BUFCNT falls to the empty watermark, Flow Control is automatically disabled.

This bit is only used for Flow Control operations and affects both TX and RX operations.

### bit 6-5 Unimplemented: Read as '0'

### bit 4 MANFC: Manual Flow Control bit

- 1 = Manual Flow Control is enabled

- 0 = Manual Flow Control is disabled

Setting this bit will enable manual Flow Control. If set, the Flow Control logic will send a PAUSE frame using the PAUSE timer value in the PTV register. It will then resend a PAUSE frame every 128 \* PTV<15:0>/2 TX clock cycles until the bit is cleared.

**Note:** For 10 Mbps operation, TX clock runs at 2.5 MHz. For 100 Mbps operation, TX clock runs at 25 MHz.

When this bit is cleared, the Flow Control logic will automatically send a PAUSE frame with a 0x0000 PAUSE timer value to disable Flow Control.

This bit is only used for Flow Control operations and affects both TX and RX operations.

### bit 3-1 Unimplemented: Read as '0'

bit 0 BUFCDEC: Descriptor Buffer Count Decrement bit

The BUFCDEC bit is a write-1 bit that reads as '0'. When written with a '1', the Descriptor Buffer Counter, BUFCNT, will decrement by one. If BUFCNT is incremented by the RX logic at the same time that this bit is written, the BUFCNT value will remain unchanged. Writing a '0' will have no effect.

This bit is only used for RX operations.

**Note 1:** It is not recommended to clear the RXEN bit and then make changes to any RX related field/register. The Ethernet Controller must be reinitialized (ON cleared to '0'), and then the RX changes applied.

NOTES:

### REGISTER 36-18: GLCDCURDATAX: GRAPHICS LCD CONTROLLER CURSOR DATA 'n' REGISTER ('n' = 0-127)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4 | Bit<br>27/19/11/3           | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|----------------------|-------------------|-----------------------------|-------------------|-----------------------|------------------|

| 04.04        | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0                       | R/W-0             | R/W-0                 | R/W-0            |

| 31:24        |                   | PIXELxy           | <3:0> <sup>(1)</sup> |                   |                             | PIXELxy           | /<3:0> <sup>(1)</sup> |                  |

| 00.40        | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0                       | R/W-0             | R/W-0                 | R/W-0            |

| 23:16        |                   | PIXELxy           | <3:0>(1)             |                   | PIXELxy<3:0> <sup>(1)</sup> |                   |                       |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0                       | R/W-0             | R/W-0                 | R/W-0            |

| 15:8         |                   | PIXELxy           | <3:0> <sup>(1)</sup> |                   |                             | PIXELxy           | /<3:0> <sup>(1)</sup> |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0                       | R/W-0             | R/W-0                 | R/W-0            |

| 7:0          |                   | PIXELxy           | <3:0> <sup>(1)</sup> |                   |                             | PIXELxy           | /<3:0> <b>(1)</b>     |                  |

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |  |

|-------------------|------------------|----------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |

bit 31-28 PIXELxy<3:0>: Pixel 'xy' Color Lookup bits<sup>(1)</sup>

bit 27-24 **PIXELxy<3:0>:** Pixel 'xy' Color Lookup bits<sup>(1)</sup>

bit 23-20 **PIXELxy<3:0>:** Pixel 'xy' Color Lookup bits<sup>(1)</sup>

bit 19-16 **PIXELxy<3:0>:** Pixel 'xy' Color Lookup bits<sup>(1)</sup>

bit 15-12 **PIXELxy<3:0>:** Pixel 'xy' Color Lookup bits<sup>(1)</sup>

bit 11-8 **PIXELxy<3:0>:** Pixel 'xy' Color Lookup bits<sup>(1)</sup>

bit 7-4 **PIXELxy<3:0>:** Pixel 'xy' Color Lookup bits<sup>(1)</sup>

bit 3-0 **PIXELxy<3:0>:** Pixel 'xy' Color Lookup bits<sup>(1)</sup>

**Note 1:** For the PIXELxy bits, x = 0-31 and y = 0-31 (i.e., GLCDCURDATA0 contains PIXEL00 through PIXEL07 with PIXEL00 in the most significant nibble).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 7:0          | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |

| 7:0          |                   |                   |                   | MINCM             | D<7:0>            |                   |                  |                  |

### REGISTER 38-4: DDRMINCMD: DDR MINIMUM COMMAND REGISTER

## Legend:

| Logona.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-8 Unimplemented: Read as '0'

bit 7-0 MINCMD<7:0>: Minimum Command bits

These bits in conjunction with the RQPER<7:0> bits (DDRRQPER<7:0>) determine the percentage of total bandwidth that is allocated to the target. If the number of DDR bursts specified by MINCMD<7:0> are not serviced for the target when it has been requesting access for (RQPER<7:0> \* 4) number of clocks, then the target's requests are treated with high priority until this condition becomes satisfied.

**Note:** The TSEL<7:0> bits (DDRTSEL<7:0>) must be programmed with the target number multiplied by the size of the MINLIMIT field (5) before this register is used to program the minimum burst limit for that target.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0, HC        | R/W-0, HC        |

| 31:24        | —                 | _                 | —                 | _                 | _                 | _                 | ADEISE           | ACEISE           |

| 00.40        | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |

| 23:16        | CLEISE            | DEBEISE           | DCRCEISE          | DTOEISE           | CIDXEISE          | CEBEISE           | CCRCEISE         | CTOEISE          |

| 45.0         | R-0, HC           | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R-0, HC          |

| 15:8         | FTZEISE           | _                 | —                 | _                 | _                 |                   | —                | CARDISE          |

| 7:0          | R/W-1, HC         | R/W-1, HC        | R/W-1, HC        |

|              | CARDRISE          | CARDIISE          | BRRDYISE          | BWRDYISE          | DMAISE            | BGISE             | TXEISE           | CEISE            |

### REGISTER 39-11: SDHCINTSEN: SDHC INTERRUPT SIGNAL ENABLE REGISTER

| Legend:           |                  | HC = Hardware Cleared                   |     |

|-------------------|------------------|-----------------------------------------|-----|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown | own |

### bit 31-26 Unimplemented: Read as '0'

| bit 25  | ADEISE: ADMA Error Interrupt Signal Enable bit<br>1 = ADMA error signal is enabled                                    |

|---------|-----------------------------------------------------------------------------------------------------------------------|

|         | 0 = ADMA error signal is masked                                                                                       |

| bit 24  | ACEISE: Auto CMD12 Error Interrupt Signal Enable bit                                                                  |

|         | 1 = Auto CMD12 error signal is enabled                                                                                |

|         | 0 = Auto CMD12 error signal is masked                                                                                 |

| bit 23  | CLEISE: Current-Limit Error Interrupt Signal Enable bit                                                               |

|         | <ul> <li>1 = Current-limit error signal is enabled</li> <li>0 = Current-limit error signal is masked</li> </ul>       |

| bit 22  | DEBEISE: Data End Bit Error Interrupt Signal Enable bit                                                               |

|         | 1 = Data end bit error signal is enabled                                                                              |

|         | 0 = Data end bit error signal is masked                                                                               |

| bit 21  | DCRCEISE: Data CRC Error Interrupt Signal Enable bit                                                                  |

|         | 1 = Data CRC error signal is enabled                                                                                  |

| 1.11.00 | 0 = Data CRC error signal is masked                                                                                   |

| bit 20  | DTOEISE: Data Time-out Error Interrupt Signal Enable bit                                                              |

|         | <ul> <li>1 = Data time-out error signal is enabled</li> <li>0 = Data time-out error signal is masked</li> </ul>       |

| bit 19  | CIDXEISE: Command Index Error Interrupt Signal Enable bit                                                             |

|         | 1 = Command index error signal is enabled                                                                             |

|         | 0 = Command index error signal is masked                                                                              |

| bit 18  | CEBEISE: Command End Bit Error Interrupt Signal Enable bit                                                            |

|         | 1 = Command End bit error signal is enabled                                                                           |

|         | 0 = Command End bit error signal is masked                                                                            |

| bit 17  | CCRCEISE: Command CRC Error Interrupt Signal Enable bit                                                               |

|         | 1 = Command CRC error signal is enabled                                                                               |

| 1:1.40  | 0 = Command CRC error signal is masked                                                                                |

| bit 16  | <b>CTOEISE:</b> Command Time-out Error Interrupt Signal Enable bit                                                    |

|         | <ul> <li>1 = Command time-out error signal is enabled</li> <li>0 = Command time-out error signal is masked</li> </ul> |

| bit 15  | <b>FTZEISE:</b> Fixed to Zero Error Interrupt Signal Enable bit                                                       |

|         | This bit is set if any or all bits, 0 through 9, in this register are set.                                            |

|         | 1 = Error was detected                                                                                                |

|         | 0 = No error was detected                                                                                             |

|         |                                                                                                                       |

# TABLE 40-3: PERIPHERAL MODULE DISABLE BITS AND LOCATIONS

| Peripheral                   | PMDx Bit Name | Register Name and Bit Location |  |  |  |

|------------------------------|---------------|--------------------------------|--|--|--|

| ADC                          | ADCMD         | PMD1<0>                        |  |  |  |

| CTMU                         | CTMUMD        | PMD1<8>                        |  |  |  |

| Comparator Voltage Reference | CVRMD         | PMD1<12>                       |  |  |  |

| High/Low-Voltage Detect      | HLVDMD        | PMD1<20>                       |  |  |  |

| Comparator 1                 | CMP1MD        | PMD2<0>                        |  |  |  |

| Comparator 2                 | CMP2MD        | PMD2<1>                        |  |  |  |

| Input Capture 1              | IC1MD         | PMD3<0>                        |  |  |  |

| Input Capture 2              | IC2MD         | PMD3<1>                        |  |  |  |

| Input Capture 3              | IC3MD         | PMD3<2>                        |  |  |  |

| Input Capture 4              | IC4MD         | PMD3<3>                        |  |  |  |

| Input Capture 5              | IC5MD         | PMD3<4>                        |  |  |  |

| Input Capture 6              | IC6MD         | PMD3<5>                        |  |  |  |

| Input Capture 7              | IC7MD         | PMD3<6>                        |  |  |  |

| Input Capture 8              | IC8MD         | PMD3<7>                        |  |  |  |

| Input Capture 9              | IC9MD         | PMD3<8>                        |  |  |  |

| Output Compare 1             | OC1MD         | PMD3<16>                       |  |  |  |

| Output Compare 2             | OC2MD         | PMD3<17>                       |  |  |  |

| Output Compare 3             | OC3MD         | PMD3<18>                       |  |  |  |

| Output Compare 4             | OC4MD         | PMD3<19>                       |  |  |  |

| Output Compare 5             | OC5MD         | PMD3<20>                       |  |  |  |

| Output Compare 6             | OC6MD         | PMD3<21>                       |  |  |  |

| Output Compare 7             | OC7MD         | PMD3<22>                       |  |  |  |

| Output Compare 8             | OC8MD         | PMD3<23>                       |  |  |  |

| Output Compare 9             | OC9MD         | PMD3<24>                       |  |  |  |

| Timer1                       | T1MD          | PMD4<0>                        |  |  |  |

| Timer2                       | T2MD          | PMD4<1>                        |  |  |  |

| Timer3                       | T3MD          | PMD4<2>                        |  |  |  |

| Timer4                       | T4MD          | PMD4<3>                        |  |  |  |

| Timer5                       | T5MD          | PMD4<4>                        |  |  |  |

| Timer6                       | T6MD          | PMD4<5>                        |  |  |  |

| Timer7                       | T7MD          | PMD4<6>                        |  |  |  |

| Timer8                       | T8MD          | PMD4<7>                        |  |  |  |

| Timer9                       | T9MD          | PMD4<8>                        |  |  |  |

| UART1                        | U1MD          | PMD5<0>                        |  |  |  |

| UART2                        | U2MD          | PMD5<1>                        |  |  |  |

| UART3                        | U3MD          | PMD5<2>                        |  |  |  |

| UART4                        | U4MD          | PMD5<3>                        |  |  |  |

| UART5                        | U5MD          | PMD5<4>                        |  |  |  |

| UART6                        | U6MD          | PMD5<5>                        |  |  |  |

| SPI1                         | SPI1MD        | PMD5<8>                        |  |  |  |

| SPI2                         | SPI2MD        | PMD5<9>                        |  |  |  |

**Note 1:** The USB module must not be busy after clearing the associated ON bit and prior to setting the USBMD bit.

**2:** This peripheral is not available on all devices. Refer to the pin feature tables (Table 2 through Table 4) to determine availability.

| DC CHA        | ARACTERIS           | TICS                                                                            | Standard Operating Conditions: VDDIO = 2.2V to 3.6V,VDDCORE = 1.7V to 1.9V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |                   |                   |       |                          |  |

|---------------|---------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|-------|--------------------------|--|

| Param.<br>No. | Symbol              | Characteristics                                                                 | Min.                                                                                                                                                                            | Тур.              | Max.              | Units | Conditions               |  |

| Operati       | ng Voltage          |                                                                                 |                                                                                                                                                                                 |                   |                   |       |                          |  |

| DC10          | Vddio               | I/O Supply Voltage (Note 1)                                                     | 2.2                                                                                                                                                                             | _                 | 3.6               | V     | —                        |  |

| DC11          | VDDCORE             | Core Supply Voltage (Note 1)                                                    | 1.7                                                                                                                                                                             | 1.8               | 1.9               | V     | —                        |  |

| DC12          | SVDDIO/<br>SVDDCORE | VDDIO/VDDCORE Rise Rate<br>to Ensure Internal<br>Power-on Reset Signal (Note 2) | 0.000011                                                                                                                                                                        | _                 | 1.1               | V/µs  | 300 ms to 3 µs @<br>3.3v |  |

| DC13          | VBAT                | Battery Supply Voltage                                                          | 2.2                                                                                                                                                                             |                   | 3.6               | V     | —                        |  |

| DC14          | VDDR1V8             | DDR Memory Supply Voltage                                                       | 1.7                                                                                                                                                                             | 1.8               | 1.9               | V     | —                        |  |

| DC15          | DDRVREF             | DDR Reference Voltage                                                           | 0.49 x<br>VDDR1V8                                                                                                                                                               | 0.50 x<br>Vddr1v8 | 0.51 x<br>Vddr1v8 | V     | —                        |  |

### TABLE 44-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

**Note 1:** Overall functional device operation below operating voltages guaranteed (but not characterized) until Reset is issued. All device Analog modules, when enabled, will function, but with degraded performance below operating voltages. Refer to Table 44-5 for Reset values.

2: Voltage on VDDIO must always be greater than or equal to VDDCORE during power-up.

# TABLE 44-5: ELECTRICAL CHARACTERISTICS: RESETS

| DC CHARACTERISTICS (Note 1) |                     |                                                                               | Standard Operating Conditions: VDDIO = 2.2V to 3.6V,VDDCORE = 1.7V to 1.9V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |      |       |            |   |  |

|-----------------------------|---------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|---|--|

| Param.<br>No.               | Symbol              | Min. Typ. Ma                                                                  |                                                                                                                                                                                 | Max. | Units | Conditions |   |  |

| RST10                       | Vporio              | VDDIO POR Voltage<br>(Note 2)                                                 | Vss +<br>0.3                                                                                                                                                                    | _    | 1.75  | V          | — |  |

| RST11                       | VPORCORE<br>/VBATSW | VDDCORE POR Voltage<br>(Note 2)<br>VDDCORE to VBAT Switch<br>Voltage (Note 3) | Vss +<br>0.3                                                                                                                                                                    | _    | 1.7   | V          | _ |  |

| RST12                       | VBORIO              | BOR Event on VDDIO transition high-to-low (Note 4)                            | 1.92                                                                                                                                                                            | —    | 2.2   | V          | — |  |

| RST13                       | VPORBAT             | POR Event on VBAT (Note 4)                                                    | 1.35                                                                                                                                                                            | _    | 2.2   | V          | _ |  |

| RST14                       | Vhvd1v8             | High Voltage Detect on<br>VDDR1V8 pins                                        | 2.16                                                                                                                                                                            | —    | 2.24  | V          | _ |  |

Note 1: Parameters are for design guidance only and are not tested in manufacturing.

- 2: This is the limit to which VDDIO/VDDCORE must be lowered to ensure Power-on Reset.

- 3: Device enters VBAT mode upon VDDCORE Power-on Reset.

- 4: Overall functional device operation below operating voltages guaranteed (but not characterized) until Reset is issued. All device Analog modules, when enabled, will function, but with degraded performance below operating voltages.

| DC CHARACTERISTICS |      |                                                                                                                                                                                                                                                                                                                    |                | Standard Operating Conditions: VDDIO = 2.2V to 3.6V,VDDCORE = 1.7V to 1.9V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |       |                           |                                                                |  |  |

|--------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------------|----------------------------------------------------------------|--|--|

| Param.             | Sym. | Characteristic                                                                                                                                                                                                                                                                                                     | Min. Typ. Max. |                                                                                                                                                                                 | Units | Conditions <sup>(1)</sup> |                                                                |  |  |

|                    |      | Output High Voltage<br>I/O Pins<br>4x Sink Driver Pins -                                                                                                                                                                                                                                                           | 1.5            |                                                                                                                                                                                 |       | V                         | $IOH \ge -14 \text{ mA}, \text{ VDDIO} = 3.3 \text{ V}$        |  |  |

|                    |      |                                                                                                                                                                                                                                                                                                                    | 2.0            |                                                                                                                                                                                 |       | V                         | IOH $\geq$ -12 mA, VDDIO = 3.3V                                |  |  |

| DO20a              | Vон1 | RA0-RA3, RA9, RA10, RA14, RA15<br>RB0, RB4, RB6, RB7, RB10, RB11, RB12,<br>RB14<br>RC12-RC15<br>RD6, RD7, RD11, RD14<br>RE8, RE9<br>RF2, RF3, RF8, RF12<br>RG15<br>RH0, RH1, RH4-RH14<br>RJ0-RJ2, RJ8, RJ9, RJ11                                                                                                   |                |                                                                                                                                                                                 | _     | v                         | Іон ≥ -7 mA, Vddio = 3.3V                                      |  |  |

|                    |      | Output High Voltage<br>I/O Pins:<br>8x Sink Driver Pins -<br>70H1 RA4, RA5<br>RB2, RB3, RB5, RB8, RB9, RB10, RB13,<br>RB14, RB15<br>RC1-RC4<br>RD0-RD3, RD9, RD10, RD12, RD13<br>RE0-RE7<br>RF0, RF1, RF4, RF5, RF13<br>RG0, RG1, RG6, RG7, RG8, RG9<br>RH2, RH3, RH7, RH15<br>RJ3-RJ7, RJ10, RJ12-RJ15<br>RK0-RK7 | 1.5            |                                                                                                                                                                                 |       | V                         | $IOH \ge -22 \text{ mA}, \text{ VDDIO} = 3.3 \text{ V}$        |  |  |

|                    |      |                                                                                                                                                                                                                                                                                                                    | 2.0            | —                                                                                                                                                                               | _     | V                         | IOH $\geq$ -18 mA, VDDIO = 3.3V                                |  |  |

|                    |      |                                                                                                                                                                                                                                                                                                                    | 3.0            |                                                                                                                                                                                 |       | V                         | ІОН ≥ -10 mA, VDDIO = 3.3V                                     |  |  |

|                    |      | <b>Output High Voltage</b><br>I/O Pins:<br>12x Source Driver Pins -                                                                                                                                                                                                                                                | 1.5            | —                                                                                                                                                                               | —     | V                         | $\text{IOH} \geq -32 \text{ mA}, \text{ VDDIO} = 3.3 \text{V}$ |  |  |

|                    |      |                                                                                                                                                                                                                                                                                                                    | 2.0            |                                                                                                                                                                                 |       | V                         | $IOH \geq -25 \text{ mA}, \text{ VDDIO} = 3.3 \text{ V}$       |  |  |

|                    |      | RA6, RA7<br>RD4, RD5<br>RG12-RG14                                                                                                                                                                                                                                                                                  |                | _                                                                                                                                                                               | _     | V                         | Іон ≥ -14 mA, Vddio = 3.3V                                     |  |  |

# TABLE 44-11: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS (CONTINUED)

Note 1: Parameters are characterized, but not tested.

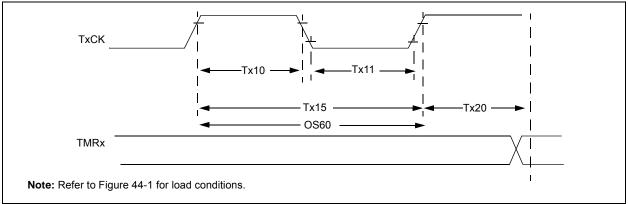

### FIGURE 44-6: TIMER1-TIMER9 EXTERNAL CLOCK TIMING CHARACTERISTICS

# TABLE 44-32: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS<sup>(1)</sup>

| AC CHARACTERISTICS |                             |                                                                                                      |                                |   | Standard Operating Conditions: VDDIO = 2.2V to 3.6V,VDDCORE = 1.7V to 1.9V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |      |      |         |                                                       |  |  |

|--------------------|-----------------------------|------------------------------------------------------------------------------------------------------|--------------------------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|---------|-------------------------------------------------------|--|--|

| Param.<br>No.      | Symbol                      | Charac                                                                                               | teristics <sup>(2)</sup>       |   | Min.                                                                                                                                                                            | Тур. | Max. | Units   | Conditions                                            |  |  |

| TA10               | TA10 TTXH TXCK<br>High Time |                                                                                                      | Synchronous, with prescaler    |   | [(12.5 ns or 1 TPBCLK3)<br>/N] + 20 ns                                                                                                                                          |      | _    | ns      | Must also meet<br>parameter TA15<br>( <b>Note 3</b> ) |  |  |

|                    |                             |                                                                                                      | Asynchronous, with prescaler   |   | 10                                                                                                                                                                              | _    | _    | ns      | —                                                     |  |  |

| TA11               | ΤτxL                        | TxCK<br>Low Time                                                                                     | Synchronous, with prescaler    |   | [(12.5 ns or 1 TPBCLK3)<br>/N] + 20 ns                                                                                                                                          | —    | —    | ns      | Must also meet<br>parameter TA15<br>( <b>Note 3</b> ) |  |  |