Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                                                               |

|----------------------------|-----------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                        |

| Core Processor             | MIPS32® microAptiv™                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                            |

| Speed                      | 200MHz                                                                                        |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, SQI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT                            |

| Number of I/O              | 120                                                                                           |

| Program Memory Size        | 2MB (2M x 8)                                                                                  |

| Program Memory Type        | FLASH                                                                                         |

| EEPROM Size                | -                                                                                             |

| RAM Size                   | 256K x 8                                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                   |

| Data Converters            | A/D 45x12b                                                                                    |

| Oscillator Type            | Internal                                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                             |

| Mounting Type              | Surface Mount                                                                                 |

| Package / Case             | 288-LFBGA                                                                                     |

| Supplier Device Package    | 288-LFBGA (15x15)                                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2025dab288t-i-4j             |

|                            |                                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 CPU

- Note 1: This data sheet summarizes the features of the PIC32MZ Graphics (DA) Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 50. "CPU for Devices with MIPS32<sup>®</sup> microAptiv™ and M-Class Cores" (DS60001192), available which is from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

- 2: MIPS32<sup>®</sup> microAptiv<sup>™</sup> Microprocessor Core resources are available at: http://www.imgtec.com.

The MIPS32 microAptiv Microprocessor Core is the heart of the PIC32MZ DA family device processor. The CPU fetches instructions, decodes each instruction, fetches source operands, executes each instruction and writes the results of instruction execution to the proper destinations.

## 3.1 Features

PIC32MZ DA family processor core key features:

- 5-stage pipeline

- · 32-bit address and data paths

- MIPS32 Enhanced Architecture (Release 2):

- Multiply-accumulate and multiply-subtract instructions

- Targeted multiply instruction

- Zero/One detect instructions

- WAIT instruction

- Conditional move instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- GPR shadow registers to minimize latency for interrupt handlers

- Bit field manipulation instructions

- Virtual memory support

- microMIPS compatible instruction set:

- Improves code size density over MIPS32, while maintaining MIPS32 performance.

- Supports all MIPS32 instructions (except branchlikely instructions)

- Fifteen additional 32-bit instructions and 39 16-bit instructions corresponding to commonly-used MIPS32 instructions

- Stack pointer implicit in instruction

- MIPS32 assembly and ABI compatible

- MMU with Translation Lookaside Buffer (TLB) mechanism:

- 32 dual-entry fully associative Joint TLB

- 4-entry fully associative Instruction TLB

- 4-entry fully associative Data TLB

- 4 KB pages

- · Separate L1 data and instruction caches:

- 32 KB 4-way Instruction Cache (I-Cache)

- 32 KB 4-way Data Cache (D-Cache)

- Autonomous Multiply/Divide Unit (MDU):

- Maximum issue rate of one 32x32 multiply per clock

- Early-in iterative divide. Minimum 12 and maximum 38 clock latency (dividend (*rs*) sign extension-dependent)

- Power Control:

- Minimum frequency: 0 MHz

- Low-Power mode (triggered by WAIT instruction)

- Extensive use of local gated clocks

- EJTAG Debug and Instruction Trace:

- Support for single stepping

- Virtual instruction and data address/value breakpoints

- Hardware breakpoint supports both address match and address range triggering.

- Eight instruction and four data complex breakpoints

- iFlowtrace<sup>®</sup> version 2.0 support:

- Real-time instruction program counter

- Special events trace capability

- Two performance counters with 34 userselectable countable events

- Disabled if the processor enters Debug mode

- Four Watch registers:

- Instruction, Data Read, Data Write options

- Address match masking options

- DSP ASE Extension:

- Native fractional format data type operations

- Register Single Instruction Multiple Data (SIMD) operations (add, subtract, multiply, shift)

- GPR-based shift

- Bit manipulation

- Compare-Pick

- DSP Control Access

- Indexed-Load

- Branch

- Multiplication of complex operands

- Variable bit insertion and extraction

- Virtual circular buffers

- Arithmetic saturation and overflow handling

- Zero-cycle overhead saturation and rounding operations

## TABLE 4-14: SYSTEM BUS TARGET PROTECTION GROUP 4 REGISTER MAP (CONTINUED)

| ess                         |                               |           |            |       |       |       |       |       |      | Bi   |      |      |           |      |        |        |        |        |               |

|-----------------------------|-------------------------------|-----------|------------|-------|-------|-------|-------|-------|------|------|------|------|-----------|------|--------|--------|--------|--------|---------------|

| Virtual Address<br>(BF8F_#) | Register<br>Name<br>Bit Range | Bit Range | 31/15      | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5      | 20/4 | 19/3   | 18/2   | 17/1   | 16/0   | All<br>Resets |

| 90B0                        | SBT4RD3                       | 31:16     | _          | —     | —     | —     |       | —     | —    | —    |      | —    |           | —    | —      | —      | —      |        | xxxx          |

| 9080                        | SB14RD3                       | 15:0      | Ι          | _     | _     | _     | _     | _     | _    | _    | _    | _    | _         | _    | GROUP3 | GROUP2 | GROUP1 | GROUP0 | xxxx          |

| 0000                        | SBT4WR3                       | 31:16     | Ι          | _     | _     | _     | _     | _     | _    | _    | _    | _    | _         | _    | _      | _      | _      | _      | xxxx          |

| 90B8                        |                               | 15:0      | Ι          | _     | _     | _     | _     | _     | _    | _    | _    | _    | _         | _    | GROUP3 | GROUP2 | GROUP1 | GROUP0 | xxxx          |

| 0000                        | SBT4REG4                      | 31:16     | BASE<21:6> |       |       |       |       |       |      |      |      | xxxx |           |      |        |        |        |        |               |

| 90C0                        | SB14REG4                      | 15:0      |            |       | BASE  | <5:0> |       |       | PRI  | —    |      |      | SIZE<4:0> |      |        | _      | _      | _      | xxxx          |

| 0000                        |                               | 31:16     | Ι          | _     | _     | _     | _     | _     | _    | _    | _    | _    | _         | _    | _      | _      | _      | _      | xxxx          |

| 90D0                        | SBT4RD4                       | 15:0      |            | _     | _     | _     | _     | _     | _    | —    | _    | —    | _         | —    | GROUP3 | GROUP2 | GROUP1 | GROUP0 | xxxx          |

| 0000                        |                               | 31:16     | _          | —     | —     | —     | _     | —     | _    | —    | _    | —    | _         | —    | _      | _      | _      | _      | xxxx          |

| 90D8                        | SBT4WR4                       | 15:0      | _          | _     | _     | _     |       | _     | _    |      |      | —    | _         | _    | GROUP3 | GROUP2 | GROUP1 | GROUP0 | xxxx          |

PIC32MZ Graphics (DA) Family

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note: For reset values listed as 'xxxx', please refer to Table 4-8 for the actual reset values.

# 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MZ Graphics (DA) Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 52. "Flash Program Memory with Support for Live Update" (DS60001193), which is available from the Documentation > Reference Manual section of the PIC32 web Microchip site (www.microchip.com/pic32).

PIC32MZ DA devices contain an internal Flash program memory for executing user code, which includes the following features:

- Two Flash banks for live update support

- · Dual boot support

- Write protection for program and Boot Flash

- ECC support

There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 52. "Flash Program Memory with Support for Live Update"** (DS60001193) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the *"PIC32 Flash Programming Specification"* (DS60001145), which is available for download from the Microchip website.

Note: In PIC32MZ DA devices, the Flash page size is 16 KB (4K IW) and the row size is 2 KB (512 IW).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        |                   |                   |                   | ROTRIN            | √<8:1>            |                   |                  |                  |

| 00.40        | R/W-0             | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | ROTRIM<0>         |                   |                   |                   | —                 |                   | —                | _                |

| 45.0         | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | _                 | _                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          |                   | _                 |                   | _                 |                   |                   |                  |                  |

#### **REGISTER 8-5: REFOXTRIM: REFERENCE OSCILLATOR TRIM REGISTER ('x' = 1-4)**

## Legend:

| 0                 |                  |                          |                    |  |

|-------------------|------------------|--------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

bit 31-23 ROTRIM<8:0>: Reference Oscillator Trim bits

bit 22-0 Unimplemented: Read as '0'

**Note 1:** While the ON bit (REFOxCON<15>) is '1', writes to this register do not take effect until the DIVSWEN bit is also set to '1'.

Do not write to this register when the ON bit (REFOxCON<15>) is not equal to the ACTIVE bit (REFOxCON<8>).

3: Specified values in this register do not take effect if RODIV<14:0> (REF0xCON<30:16>) = 0.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2         | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0                     | U-0              | U-0              |

| 51.24     |                   | _                 | —                 | —                 |                   | PFMSECEN                  |                  | —                |

| 23:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                       | U-0              | U-0              |

| 23.10     |                   | _                 | _                 | —                 | _                 | _                         |                  | —                |

| 15:8      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                       | U-0              | U-0              |

| 15.0      |                   | _                 | _                 | —                 | _                 | _                         |                  | —                |

| 7:0       | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | R/W-1                     | R/W-1            | R/W-1            |

| 7.0       |                   | _                 | PREFEN            | N<1:0>            |                   | PFMWS<2:0> <sup>(1)</sup> |                  |                  |

#### REGISTER 9-1: PRECON: PREFETCH MODULE CONTROL REGISTER

## Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 31-27 | Unimplemented: Write '0'; ignore read                                                                                                                          |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 26    | PFMSECEN: Flash SEC Interrupt Enable bit                                                                                                                       |

|           | <ul><li>1 = Generate an interrupt when the PFMSEC bit (PRESTAT&lt;26&gt;) is set</li><li>0 = Do not generate an interrupt when the PFMSEC bit is set</li></ul> |

| bit 25-6  | Unimplemented: Write '0'; ignore read                                                                                                                          |

| bit 5-4   | PREFEN<1:0>: Predictive Prefetch Enable bits                                                                                                                   |

|           |                                                                                                                                                                |

- 11 = Enable predictive prefetch for any address

- 10 = Enable predictive prefetch for CPU instructions and CPU data

- 01 = Enable predictive prefetch for CPU instructions only

- 00 = Disable predictive prefetch

## bit 3 Unimplemented: Write '0'; ignore read

#### bit 2-0 **PFMWS<2:0>:** PFM Access Time Defined in Terms of SYSCLK Wait States bits<sup>(1)</sup>

- 111 = Seven Wait states

- •

- •

- •

- 010 = Two Wait states

- 001 = One Wait state

- 000 = Zero Wait states

- Note 1: For the Wait states to SYSCLK relationship, refer to Table 44-16 in Section44.0 "Electrical Characteristics".

# PIC32MZ Graphics (DA) Family

| Bit Range            | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 21.04                | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 31:24 COUNTER<31:24> |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40                | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 23:16                | COUNTER<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0                 | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 15:8                 | COUNTER<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0                  | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 7:0                  |                   |                   |                   | COUNTE            | R<7:0>            |                   |                  |                  |  |  |  |  |

## REGISTER 17-5: DMTCNT: DEADMAN TIMER COUNT REGISTER

# Legend:

| 3                                          |                  |                       |                  |

|--------------------------------------------|------------------|-----------------------|------------------|

| R = Readable bit                           | W = Writable bit | U = Unimplemented bit |                  |

| -n = Bit Value at POR: ('0', '1', x = unkn | own)             | P = Programmable bit  | r = Reserved bit |

bit 31-8 COUNTER<31:0>: Read current contents of DMT counter

## REGISTER 17-6: DMTPSCNT: POST STATUS CONFIGURE DMT COUNT STATUS REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 21.04     | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 31:24     |                   | •                 |                   | PSCNT<            | 31:24>            |                   |                  |                  |  |  |  |

| 02:16     | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 23:16     | PSCNT<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0      | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8      | PSCNT<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0       | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0       |                   |                   |                   | PSCNT             | <7:0>             |                   |                  |                  |  |  |  |

| Legend:                                  |                  |                       |                  |

|------------------------------------------|------------------|-----------------------|------------------|

| R = Readable bit                         | W = Writable bit | U = Unimplemented bit |                  |

| -n = Bit Value at POR: ('0', '1', x = un | known)           | P = Programmable bit  | r = Reserved bit |

bit 31-8 **PSCNT<31:0>:** DMT Instruction Count Value Configuration Status bits This is always the value of the DMTCNT<3:0> bits in the DEVCFG1 Configuration register.

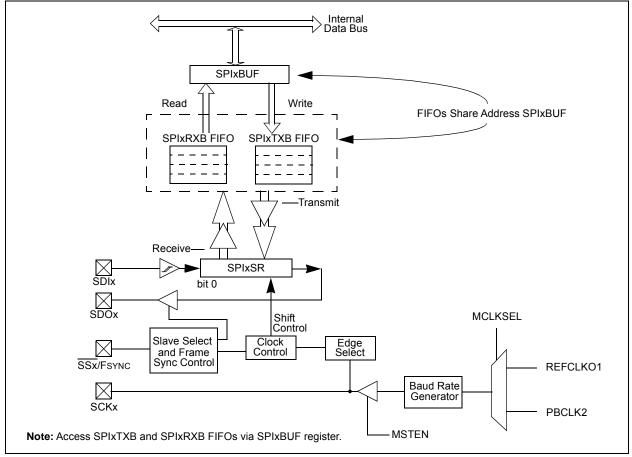

# 21.0 SERIAL PERIPHERAL INTERFACE (SPI) AND INTER-IC SOUND (I<sup>2</sup>S)

Note: This data sheet summarizes the features of the PIC32MZ Graphics (DA) Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial Peripheral Interface (SPI)" (DS60001106), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The SPI/I<sup>2</sup>S module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontroller devices, as well as digital audio devices. These peripheral devices may be Serial EEPROMs, Shift registers, display drivers, Analog-to-Digital Converters (ADC), etc.

The SPI/I<sup>2</sup>S module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces.

Some of the key features of the SPI module are:

- Master and Slave modes support

- · Four different clock formats

- Enhanced Framed SPI protocol support

- User-configurable 8-bit, 16-bit and 32-bit data width

- Separate SPI FIFO buffers for receive and transmit

FIFO buffers act as 4/8/16-level deep FIFOs based on 32/16/8-bit data width

- Programmable interrupt event on every 8-bit, 16-bit and 32-bit data transfer

- · Operation during Sleep and Idle modes

- · Audio Codec Support:

- I<sup>2</sup>S protocol

- Left-justified

- Right-justified

- PCM

## FIGURE 21-1: SPI/I<sup>2</sup>S MODULE BLOCK DIAGRAM

### REGISTER 22-9: SQI1INTSTAT: SQI INTERRUPT STATUS REGISTER (CONTINUED)

- bit 2

TXTHRIF: Transmit Buffer Threshold Interrupt Flag bit

1 = Transmit buffer has more than TXINTTHR words of space available

0 = Transmit buffer has less than TXINTTHR words of space available

bit 1

TXFULLIF: Transmit Buffer Full Interrupt Flag bit

1 = The transmit buffer is full

0 = The transmit buffer is not full

bit 0

TXEMPTYIF: Transmit Buffer Empty Interrupt Flag bit

1 = The transmit buffer is empty

- 0 = The transmit buffer has content

- **Note 1:** In the case of Boot/XIP mode, the POR value of the receive buffer threshold is zero. Therefore, this bit will be set to a '1', immediately after a POR until a read request on the System Bus bus is received.

Note: The bits in the register are cleared by writing a '1' to the corresponding bit position.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        | _                 | _                 | —                 | _                 | —                 | _                 | —                | —                |  |  |  |

| 23:16        | U-0               | U-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 23.10        | _                 | —                 | TXBUFFREE<5:0>    |                   |                   |                   |                  |                  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15.0         | _                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |  |

| 7:0          | U-0               | U-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7.0          |                   | _                 |                   | RXBUFCNT<5:0>     |                   |                   |                  |                  |  |  |  |

## REGISTER 22-12: SQI1STAT1: SQI STATUS REGISTER 1

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-22 Unimplemented: Read as '0'

bit 21-16 TXBUFFREE<5:0>: Transmit buffer Available Word Space bits

bit 15-6 Unimplemented: Read as '0'

bit 5-0 RXBUFCNT<5:0>: Number of words of read data in the buffer

## REGISTER 24-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 12        | IREN: IrDA <sup>®</sup> Encoder and Decoder Enable bit                                                                               |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------|

|               | 1 = IrDA is enabled                                                                                                                  |

|               | 0 = IrDA is disabled                                                                                                                 |

| bit 11        | RTSMD: Mode Selection for UxRTS Pin bit                                                                                              |

|               | 1 = UxRTS pin is in Simplex mode                                                                                                     |

| 1:1.40        | 0 = UxRTS pin is in Flow Control mode                                                                                                |

| bit 10        | Unimplemented: Read as '0'                                                                                                           |

| bit 9-8       | UEN<1:0>: UARTx Module Enable bits <sup>(1)</sup>                                                                                    |

|               | 11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register            |

|               | 10 = UxTX, UxRX, UxCTS and UxRTS pins are enabled and used                                                                           |

|               | 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by corresponding bits                                   |

|               | in the PORTx register                                                                                                                |

|               | 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register |

| bit 7         | WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit                                                                       |

|               | 1 = Wake-up enabled                                                                                                                  |

| <b>h</b> it C | 0 = Wake-up disabled                                                                                                                 |

| bit 6         | LPBACK: UARTx Loopback Mode Select bit<br>1 = Loopback mode is enabled                                                               |

|               | 0 = Loopback mode is disabled                                                                                                        |

| bit 5         | ABAUD: Auto-Baud Enable bit                                                                                                          |

|               | 1 = Enable baud rate measurement on the next character – requires reception of Sync character (0x55);                                |

|               | cleared by hardware upon completion                                                                                                  |

| L:1 4         | 0 = Baud rate measurement disabled or completed                                                                                      |

| bit 4         | <b>RXINV:</b> Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'                                                           |

|               | 0 = UxRX Idle state is '1'                                                                                                           |

| bit 3         | BRGH: High Baud Rate Enable bit                                                                                                      |

|               | 1 = High-Speed mode – 4x baud clock enabled                                                                                          |

|               | 0 = Standard Speed mode – 16x baud clock enabled                                                                                     |

| bit 2-1       | PDSEL<1:0>: Parity and Data Selection bits                                                                                           |

|               | <ul><li>11 = 9-bit data, no parity</li><li>10 = 8-bit data, odd parity</li></ul>                                                     |

|               | 01 = 8-bit data, even parity                                                                                                         |

|               | 00 = 8-bit data, no parity                                                                                                           |

| bit 0         | STSEL: Stop Selection bit                                                                                                            |

|               | 1 = 2 Stop bits                                                                                                                      |

|               | 0 = 1 Stop bit                                                                                                                       |

|               |                                                                                                                                      |

Note 1: These bits are present for legacy compatibility, and are superseded by PPS functionality on these devices (see Section 12.4 "Peripheral Pin Select (PPS)" for more information).

## REGISTER 24-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 10  | <b>UTXEN:</b> Transmit Enable bit<br>1 = UARTx transmitter is enabled. UxTX pin is controlled by UARTx (if ON = 1)<br>0 = UARTx transmitter is disabled. Any pending transmission is aborted and buffer is reset                                                                                                                                   |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <b>Note:</b> The event of disabling an enabled transmitter will release the TX pin to the PORT function and reset the transmit buffers to empty. Any pending transmission is aborted and data characters in the transmit buffers are lost. All transmit status flags are cleared and the TRMT bit is set                                           |

| bit 9   | <b>UTXBF:</b> Transmit Buffer Full Status bit (read-only)<br>1 = Transmit buffer is full<br>0 = Transmit buffer is not full, at least one more character can be written                                                                                                                                                                            |

| bit 8   | <ul> <li>TRMT: Transmit Shift Register is Empty bit (read-only)</li> <li>1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed)</li> <li>0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer</li> </ul>                                      |

| bit 7-6 | URXISEL<1:0>: Receive Interrupt Mode Selection bit<br>11 = Reserved<br>10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full<br>01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full<br>00 = Interrupt flag bit is asserted while receive buffer is not empty (i.e., has at least 1 data character) |

| bit 5   | <ul> <li>ADDEN: Address Character Detect bit (bit 8 of received data = 1)</li> <li>1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                                                                       |

| bit 4   | RIDLE: Receiver Idle bit (read-only)<br>1 = Receiver is Idle<br>0 = Data is being received                                                                                                                                                                                                                                                         |

| bit 3   | <ul> <li>PERR: Parity Error Status bit (read-only)</li> <li>1 = Parity error has been detected for the current character</li> <li>0 = Parity error has not been detected</li> </ul>                                                                                                                                                                |

| bit 2   | <ul> <li>FERR: Framing Error Status bit (read-only)</li> <li>1 = Framing error has been detected for the current character</li> <li>0 = Framing error has not been detected</li> </ul>                                                                                                                                                             |

| bit 1   | <b>OERR:</b> Receive Buffer Overrun Error Status bit.<br>This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and RSR to empty state.<br>1 = Receive buffer has overflowed<br>0 = Receive buffer has not overflowed                                                |

| bit 0   | <b>URXDA:</b> Receive Buffer Data Available bit (read-only)<br>1 = Receive buffer has data, at least one more character can be read                                                                                                                                                                                                                |

0 = Receive buffer is empty

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R-0, HS, HC      |

| 31:24        | AFEN              | DATA16EN          | DFMODE            | 0                 | OVRSAM<2:0> A     |                   |                  | AFRDY            |

| 00.10        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | _                 | _                 |                   | CHNLID<4:0>       |                   |                   |                  |                  |

| 45.0         | R-0, HS, HC       | R-0, HS, HC      | R-0, HS, HC      |

| 15:8         | FLTRDATA<15:8>    |                   |                   |                   |                   |                   |                  |                  |

| 7.0          | R-0, HS, HC       | R-0, HS, HC      | R-0, HS, HC      |

| 7:0          |                   |                   |                   | FLTRDAT           | A<7:0>            |                   |                  |                  |

#### **REGISTER 29-16:** ADCFLTRX: ADC DIGITAL FILTER 'x' REGISTER ('x' = 1 THROUGH 6)

| Legend:           | HS = Hardware Set | HC = Hardware Cleared                   |

|-------------------|-------------------|-----------------------------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0'      |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared x = Bit is unknown |

- bit 31 **AFEN:** Digital Filter '*x*' Enable bit

- 1 = Digital filter is enabled

- 0 = Digital filter is disabled and the AFRDY status bit is cleared

- bit 30 DATA16EN: Filter Significant Data Length bit

- 1 = All 16 bits of the filter output data are significant

- 0 = Only the first 12 bits are significant, followed by four zeros

- **Note:** This bit is significant only if DFMODE = 1 (Averaging Mode) and FRACT (ADCCON1<23>) = 1 (Fractional Output Mode).

#### bit **DFMODE:** ADC Filter Mode bit

- 1 = Filter 'x' works in Averaging mode

- 0 = Filter 'x' works in Oversampling Filter mode (default)

#### bit 28-26 OVRSAM<2:0>: Oversampling Filter Ratio bits

If DFMODE is '0':

- 111 = 128 samples (shift sum 3 bits to right, output data is in 15.1 format)

- 110 = 32 samples (shift sum 2 bits to right, output data is in 14.1 format)

- 101 = 8 samples (shift sum 1 bit to right, output data is in 13.1 format)

- 100 = 2 samples (shift sum 0 bits to right, output data is in 12.1 format)

- 011 = 256 samples (shift sum 4 bits to right, output data is 16 bits)

- 010 = 64 samples (shift sum 3 bits to right, output data is 15 bits)

- 001 = 16 samples (shift sum 2 bits to right, output data is 14 bits)

- 000 = 4 samples (shift sum 1 bit to right, output data is 13 bits)

If DFMODE is '1':

- 111 = 256 samples (256 samples to be averaged)

- 110 = 128 samples (128 samples to be averaged)

- 101 = 64 samples (64 samples to be averaged)

- 100 = 32 samples (32 samples to be averaged)

- 011 = 16 samples (16 samples to be averaged)

- 010 = 8 samples (8 samples to be averaged)

- 001 = 4 samples (4 samples to be averaged)

- 000 = 2 samples (2 samples to be averaged)

- bit 25 **AFGIEN:** Digital Filter '*x*' Interrupt Enable bit

- 1 = Digital filter interrupt is enabled and is generated by the AFRDY status bit

- 0 = Digital filter is disabled

| REGISTER 31-22: | ETHALGNERR: ETHERNET CONTROLLER ALIGNMENT ERRORS STATISTICS |

|-----------------|-------------------------------------------------------------|

|                 | REGISTER                                                    |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | —                 | _                 | —                 | _                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | _                 | —                 | _                 | —                 | _                | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | ALGNERRCNT<15:8>  |                   |                   |                   |                   |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | ALGNERRO          | CNT<7:0>          |                   |                  |                  |

## Legend:

| Logona.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 ALGNERRCNT<15:0>: Alignment Error Count bits

Increment count for frames with alignment errors. Note that an alignment error is a frame that has an FCS error and the frame length in bits is not an integral multiple of 8 bits (a.k.a., dribble nibble)

**Note 1:** This register is only used for RX operations.

2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

**3:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should be only done for debug/test purposes.

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1     | Bit<br>24/16/8/0 |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|----------------------|------------------|

| 24.24        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                  | U-0              |

| 31:24        | _                   | _                 |                   | —                 | _                 |                   | _                    | —                |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                  | U-0              |

| 23:16        | _                   | —                 | _                 |                   | _                 | _                 | _                    | —                |

| 45.0         | HC, R/W-y           | U-0               | R/W-0             | R/W-0             | U-0               | U-0               | U-0                  | R/W-0            |

| 15:8         | DSEN <sup>(1)</sup> | _                 | DSGPREN           | RTCDIS            | _                 | _                 | _                    | RTCCWDIS         |

| 7.0          | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0                | R/W-0            |

| 7:0          | _                   | _                 |                   | _                 |                   | _                 | DSBOR <sup>(2)</sup> | RELEASE          |

#### REGISTER 40-1: DSCON: DEEP SLEEP CONTROL REGISTER

| Legend: HC = Hardware Cleared y |                  | y = Value set from Configuration bits on POR |  |  |

|---------------------------------|------------------|----------------------------------------------|--|--|

| R = Readable bit                | W = Writable bit | U = Unimplemented bit, read as '0'           |  |  |

| -n = Value at POR               | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown      |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **DSEN:** Deep Sleep Enable bit<sup>(1)</sup> 1 = Deep Sleep mode is entered on a WAIT instruction 0 = Sleep mode is entered on a WAIT instruction

- bit 14 Unimplemented: Read as '0'

- bit 13 DSGPREN: General Purpose Registers Enable bit

- 1 = General purpose register retention is enabled in Deep Sleep mode

- 0 = No general purpose register retention in Deep Sleep mode

- bit 12 RTCDIS: RTCC Module Disable bit

- 1 = RTCC module is not enabled

- 0 = RTCC module is enabled

- bit 11-9 Unimplemented: Read as '0'

- bit 8 RTCCWDIS: RTCC Wake-up Disable bit

- 1 = Wake-up from RTCC is disabled

- 0 = Wake-up from RTCC is enabled

- bit 7-2 Unimplemented: Read as '0'

- bit 1 DSBOR: Deep Sleep BOR Event Status bit<sup>(2)</sup>

1 = DSBOREN was enabled and VDDCORE dropped below the DSBOR threshold during Deep Sleep<sup>(2)</sup> 0 = DSBOREN was disabled, or VDDCORE did not drop below the DSBOR threshold during Deep Sleep

#### bit 0 RELEASE: I/O Pin State Release bit

- 1 = Upon waking from Deep Sleep, the I/O pins maintain their previous states

- 0 = Release I/O pins and allow their respective TRIS and LAT bits to control their states

- Note 1: To enter Deep Sleep mode, Sleep mode must be executed after setting the DSEN bit.

- 2: Unlike all other events, a Deep Sleep Brown-out Reset (BOR) event will not cause a wake-up from Deep Sleep mode; this bit is present only as a status bit.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | r-1               | r-1               | R/P               | R/P               | R/P               | r-1               | R/P              | R/P              |

| 31.24        | —                 | —                 | IOL1WAY           | PMDL1WAY          | PGL1WAY           | —                 | FETHIO           | FMIIEN           |

| 23:16        | r-1               | r-1               | r-1               | r-1               | R/P               | R/P               | R/P              | R/P              |

| 23.10        | —                 | —                 | —                 | —                 | EXTDDRSIZE<3:0>   |                   |                  |                  |

| 15.0         | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |

| 15:8         | USERID<15:8>      |                   |                   |                   |                   |                   |                  |                  |

| 7:0          | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |

| 7:0          |                   |                   |                   | USERID<           | 7:0>              |                   |                  |                  |

## REGISTER 41-6: DEVCFG3/ADEVCFG3: DEVICE CONFIGURATION WORD 3

| Legend:           | r = Reserved bit | P = Programmable bit                    |

|-------------------|------------------|-----------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

#### bit 31-30 Reserved: Write as '1'

- bit 29 IOL1WAY: Peripheral Pin Select Configuration bit

- 1 = Allow only one reconfiguration

- 0 = Allow multiple reconfigurations

- bit 28 **PMDL1WAY:** Peripheral Module Disable Configuration bit

- 1 = Allow only one reconfiguration

- 0 = Allow multiple reconfigurations

- bit 27 PGL1WAY: Permission Group Lock One Way Configuration bit

- 1 = Allow only one reconfiguration

- 0 = Allow multiple reconfigurations

- bit 26 Reserved: Write as '1'

- bit 25 FETHIO: Ethernet I/O Pin Selection Configuration bit

- 1 = Default Ethernet I/O pins

- 0 = Alternate Ethernet I/O pins

This bit is ignored for devices that do not have an alternate Ethernet pin selection.

#### bit 24 FMIIEN: Ethernet MII Enable Configuration bit

- 1 = MII is enabled

- 0 = RMII is enabled

- bit 23-20 Reserved: Write as '1'

#### bit 19-16 EXTDDRSIZE<3:0>: External DDR2 SDRAM Size bits

This field is used to configure the DDR2 memory map. Refer to Table 4-1 for address mapping details.

- 1111 = 128 MB 1110 = 128 MB . . 0111 = 128 MB 0110 = 64 MB 0101 = 32 MB 0100 = 16 MB 0011 = 8 MB

- 0011 6 MB0010 = 4 MB

- 0001 = 2 MB

- 0000 **= 1** MB

bit 15-0 USERID<15:0>: This is a 16-bit value that is user-defined and is readable via ICSP™ and JTAG

## REGISTER 41-9: CFGCON: CONFIGURATION CONTROL REGISTER (CONTINUED)

- bit 7 IOANCPEN: I/O Analog Charge Pump Enable bit

- 1 = Charge pumps are enabled

- 0 = Charge pumps are disabled

- **Note 1:** For proper analog operation at VDD is less than 2.5V, the AICPMPEN bit (ADCCON1<12>) must be = 1 and the IOANCPEN bit must be set to '1'; however, the charge pumps will consume additional current. These bits should not be set if VDD is greater than 2.5V.

- 2: ADC throughput rate performance is reduced as defined in the table below if ADCCON1<AICP-MPEN> = 1 and CFGCON<IOANCPEN> = 1.

- bit 6 Unimplemented: Read as '0'

- bit 5-4 ECCCON<1:0>: Flash ECC Configuration bits

- 11 = ECC and dynamic ECC are disabled (ECCCON<1:0> bits are writable)

- 10 = ECC and dynamic ECC are disabled (ECCCON<1:0> bits are locked)

- 01 = Dynamic Flash ECC is enabled (ECCCON<1:0> bits are locked)

- 00 = Flash ECC is enabled (ECCCON<1:0> bits are locked; disables word Flash writes)

- bit 3 JTAGEN: JTAG Port Enable bit<sup>(2)</sup>

- 1 = Enable the JTAG port

- 0 = Disable the JTAG port

- bit 2 TROEN: Trace Output Enable bit

- 1 = Enable trace outputs and start trace clock (trace probe must be present)

- 0 = Disable trace outputs and stop trace clock

- bit 1 Unimplemented: Read as '0'

- bit 0 TDOEN: TDO Enable for 2-Wire JTAG

- 1 = 2-wire JTAG protocol uses TDO

- 0 = 2-wire JTAG protocol does not use TDO

- Note 1: To change this bit, the unlock sequence must be performed. Refer to Section 42. "Oscillators with Enhanced PLL" (DS60001250) in the "PIC32 Family Reference Manual" for details.

- 2: The JTAGEN bit is only available at run-time when the JTAGEN (DEVCFG0<2>) fuse bit is set at start-up.

## 44.1 DC Characteristics

#### TABLE 44-1: OPERATING MIPS VS. VOLTAGE

|                | V <sub>DDIO</sub> Range | VDDCORE               |                        | Max. Frequency     |          |

|----------------|-------------------------|-----------------------|------------------------|--------------------|----------|

| Characteristic |                         | (in Volts) (in Volts) | Temp. Range<br>(in °C) | PIC32MZ DA Devices | Comments |

| DC5            | 2.2V-3.6V               | 1.7V-1.9V             | -40°C to +85°C         | 200 MHz            | _        |

**Note 1:** Overall functional device operation below operating voltages guaranteed (but not characterized) until Reset is issued. All device Analog modules, when enabled, will function, but with degraded performance below operating voltages. Refer to Table 44-5 for Reset values.

## TABLE 44-2: THERMAL OPERATING CONDITIONS

| Rating S                                                                                                                                                                 |       | Min.        | Тур.        | Max. | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------|-------------|------|------|

| Industrial Temperature Devices                                                                                                                                           |       |             |             |      |      |

| Operating Junction Temperature Range                                                                                                                                     | TJ    | -40         |             | +125 | °C   |

| Operating Ambient Temperature Range                                                                                                                                      | ТА    | -40         |             | +85  | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>PINT = VDDIO x (IDD – S IOH)<br>I/O Pin Power Dissipation:<br>PI/O = S (({VDDIO – VOH} x IOH) + S (VOL x IOL)) | PD    | PINT + PI/O |             | W    |      |

| Maximum Allowed Power Dissipation                                                                                                                                        | PDMAX | (           | TJ – TA)/θ. | JA   | W    |

#### TABLE 44-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristics                                           | Symbol | Тур. | Max. | Unit | Notes |

|-----------------------------------------------------------|--------|------|------|------|-------|

| Package Thermal Resistance, 169-pin LFBGA (11x11x1.4 mm)  | θJA    | 25   | _    | °C/W | 1     |

| Package Thermal Resistance, 169-pin LFBGA (11x11x1.56 mm) | θJA    | 24   | -    | °C/W | 1,2   |

| Package Thermal Resistance, 176-pin LQFP (20x20x1.45 mm)  | θJA    | 17   | —    | °C/W | 1     |

| Package Thermal Resistance, 176-pin LQFP (20x20x1.45 mm)  | θJA    | 19   | _    | °C/W | 1,2   |

| Package Thermal Resistance, 288-pin LFBGA (15x15x1.4 mm)  | θJA    | 22   |      | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

2: Devices with internal DDR2 SDRAM.

| DC CHA | ARACT                                                                                                                                                                                                                                                                        | ERISTICS                                                                                                                                                                                                         | Standard Operating Conditions:VDDIO = 2.2V to 3.6V,VDDCORE = 1.7V to 1.9V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |      |      |                            |                                                                |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----------------------------|----------------------------------------------------------------|

| Param. | Sym.                                                                                                                                                                                                                                                                         | Characteristic                                                                                                                                                                                                   | Min.                                                                                                                                                                           | Тур. | Max. | Units                      | Conditions <sup>(1)</sup>                                      |

|        |                                                                                                                                                                                                                                                                              | Output High Voltage                                                                                                                                                                                              | 1.5                                                                                                                                                                            |      |      | V                          | $IOH \ge -14 \text{ mA}, \text{ VDDIO} = 3.3 \text{ V}$        |

|        |                                                                                                                                                                                                                                                                              | I/O Pins<br>4x Sink Driver Pins -                                                                                                                                                                                | 2.0                                                                                                                                                                            |      |      | V                          | IOH $\geq$ -12 mA, VDDIO = 3.3V                                |

|        |                                                                                                                                                                                                                                                                              | RA0-RA3, RA9, RA10, RA14, RA15<br>RB0, RB4, RB6, RB7, RB10, RB11, RB12,<br>RB14<br>RC12-RC15<br>RD6, RD7, RD11, RD14<br>RE8, RE9<br>RF2, RF3, RF8, RF12<br>RG15<br>RH0, RH1, RH4-RH14<br>RJ0-RJ2, RJ8, RJ9, RJ11 |                                                                                                                                                                                |      | _    | v                          | Іон ≥ -7 mA, Vddio = 3.3V                                      |

|        |                                                                                                                                                                                                                                                                              | Output High Voltage                                                                                                                                                                                              | 1.5                                                                                                                                                                            |      |      | V                          | $IOH \ge -22 \text{ mA}, \text{ VDDIO} = 3.3 \text{ V}$        |

|        |                                                                                                                                                                                                                                                                              | 8x Sink Driver Pins -                                                                                                                                                                                            | 2.0                                                                                                                                                                            | —    | _    | V                          | IOH $\geq$ -18 mA, VDDIO = 3.3V                                |

| DO20a  | VoH1 RA4, RA5<br>RB2, RB3, RB5, RB8, RB9, RB10, RB13,<br>RB14, RB15<br>RC1-RC4<br>RD0-RD3, RD9, RD10, RD12, RD13<br>RE0-RE7<br>RF0, RF1, RF4, RF5, RF13<br>RG0, RG1, RG6, RG7, RG8, RG9<br>RH2, RH3, RH7, RH15<br>RJ3-RJ7, RJ10, RJ12-RJ15<br>RK0-RK7<br>Output High Voltage | 3.0                                                                                                                                                                                                              |                                                                                                                                                                                |      | V    | ІОН ≥ -10 mA, VDDIO = 3.3V |                                                                |

|        |                                                                                                                                                                                                                                                                              | Output High Voltage                                                                                                                                                                                              | 1.5                                                                                                                                                                            | —    |      | V                          | $\text{IOH} \geq -32 \text{ mA}, \text{ VDDIO} = 3.3 \text{V}$ |

|        |                                                                                                                                                                                                                                                                              | 12x Source Driver Pins -                                                                                                                                                                                         | 2.0                                                                                                                                                                            |      |      | V                          | $IOH \geq -25 \text{ mA}, \text{ VDDIO} = 3.3 \text{ V}$       |

|        |                                                                                                                                                                                                                                                                              | RA6, RA7<br>RD4, RD5<br>RG12-RG14                                                                                                                                                                                | 3.0                                                                                                                                                                            | _    | _    | V                          | Іон ≥ -14 mA, Vddio = 3.3V                                     |

## TABLE 44-11: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS (CONTINUED)

Note 1: Parameters are characterized, but not tested.

# PIC32MZ Graphics (DA) Family

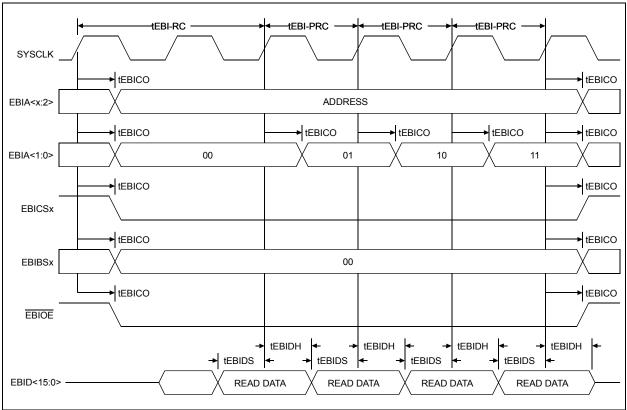

## FIGURE 44-28: EBI PAGE READ TIMING

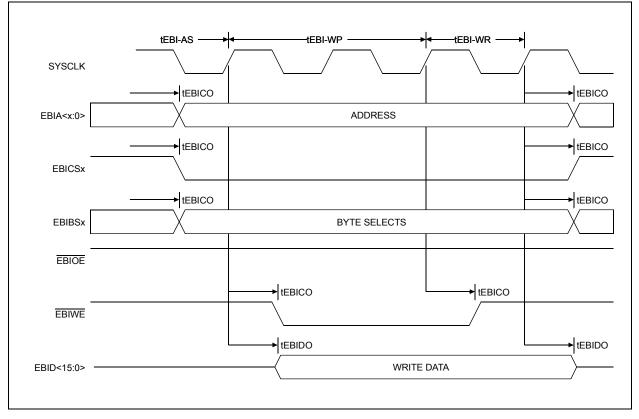

## FIGURE 44-29: EBI WRITE TIMING

# INDEX

| Α                                         |     |

|-------------------------------------------|-----|

| AC Characteristics                        | 749 |

| ADC Specifications                        | 774 |

| Analog-to-Digital Conversion Requirements | 775 |

| DDR2 SDRAM Timing Requirements            | 752 |

| EBI Timing Requirements 743, 748, 785, 7  | 787 |

| EJTAG Timing Requirements                 |     |

| Ethernet                                  | 782 |

| Internal BFRC Accuracy                    | 753 |

| Internal FRC Accuracy                     | 753 |

| Internal RC Accuracy                      | 753 |

| OTG Electrical Specifications             | 781 |

| Parallel Master Port Read Requirements    | 779 |

| Parallel Master Port Write                | 780 |

| Parallel Master Port Write Requirements   | 780 |

| Parallel Slave Port Requirements          | 778 |

| PLL Clock Timing                          | 751 |

| Assembler                                 |     |

| MPASM Assembler                           | 728 |

# В

## Block Diagrams

| Comparator I/O Operating Modes                 | . 573 |

|------------------------------------------------|-------|

| Comparator Voltage Reference                   | . 577 |

| CPU                                            | 52    |

| Crypto Engine 405, 611                         | , 613 |

| CTMU Configurations                            |       |

| Time Measurement                               | . 585 |

| DMA                                            | . 183 |

| Ethernet Controller                            | . 529 |

| Graphics LCD (GLCD) Controller                 | . 592 |

| High/Low-Voltage Detect (HLVD)                 | . 581 |

| Input Capture                                  |       |

| Inter-Integrated Circuit (I2C)                 | . 368 |

| Interrupt Controller                           |       |

| JTAG Programming, Debugging and Trace Ports    | . 723 |

| Output Compare Module                          |       |

| PIC32 CAN Module                               |       |

| PMP Pinout and Connections to External Devices | . 383 |

| Prefetch Module                                |       |

| Prefetch Module Block Diagram                  |       |

| Random Number Generator (RNG)                  |       |

| Reset System                                   |       |

| RTCC                                           |       |

| Serial Quad Interface (SQI)                    |       |

| SPI Module                                     |       |

| Timer1                                         |       |

| Timer2/3/4/5 (16-Bit)                          |       |

| Typical Multiplexed Port Structure             |       |

| UART                                           |       |

| WDT and Power-up Timer                         | , 317 |

| Brown-out Reset (BOR)                          |       |

| and On-Chip Voltage Regulator                  | . 723 |

# С

| C Compilers                             |                 |

|-----------------------------------------|-----------------|

| MPLAB C18                               | 728             |

| Charge Time Measurement Unit. See CTMU. |                 |

| Comparator                              |                 |

| Specifications                          | . 743, 746, 747 |

| Comparator Module                       | 573             |

| Comparator Voltage Reference (CVref     | 577             |

| Configuration Bit                       |                 |

| -                                       |                 |

| Configuring Analog Port Pins         | 258 |

|--------------------------------------|-----|

| Controller Area Network (CAN)        | 491 |

| CP0 Register 16, Select 1)           |     |

| CP0 Register 16, Select 2)           |     |

| CP0 Register 16, Select 3)           |     |

| CPU                                  |     |

| Architecture Overview                | 53  |

| Coprocessor 0 Registers              |     |

| Core Exception Types                 |     |

| EJTAG Debug Support                  |     |

| Power Management                     |     |

| CPU Module                           |     |

| Crypto                               |     |

| Buffer Descriptors                   | 416 |

| Format of SA_CTRL                    | 424 |

| Security Association Structure       | 421 |

| Crypto Engine                        |     |

| Customer Change Notification Service | 819 |

| Customer Notification Service        | 819 |

| Customer Support                     | 819 |

|                                      |     |

## D

| DC Characteristics                     | 732      |

|----------------------------------------|----------|

| I/O Pin Input Specifications           | 738, 742 |

| I/O Pin Output Specifications          | 739      |

| Idle Current (IIDLE)                   | 736      |

| Power-Down Current (IPD)               | 737      |

| Program Memory                         | 744      |

| Temperature and Voltage Specifications | 733      |

| Development Support                    | 727      |

| Direct Memory Access (DMA) Controller  | 183      |

# Е

| Electrical Characteristics                         | 731  |

|----------------------------------------------------|------|

| AC                                                 | 749  |

| High/Low-Voltage Detect                            | 734  |

| Errata                                             | . 15 |

| Ethernet Controller                                | 529  |

| ETHPMM0 (Ethernet Controller Pattern Match Mask 0) | 539  |

| ETHPMM1 (Ethernet Controller Pattern Match Mask 1) | 539  |

| External Bus Interface (EBI)                       | 397  |

| External Clock                                     |      |

| Timer1 Timing Requirements                         | 758  |

| Timer2, 3, 4, 5 Timing Requirements                | 759  |

| Timing Requirements                                | 750  |

| F                                                  |      |

| Flash Program Memory | 111, | 121 |

|----------------------|------|-----|

| RTSP Operation       |      | 111 |

## G

| Graphics LCD (GLCD) Controller 5 | 91 |

|----------------------------------|----|

|----------------------------------|----|

## Н

| High-Voltage Detect (HVD)      |     |

|--------------------------------|-----|

| Hi-Speed USB On-The-Go (OTG)   | 207 |

| I                              |     |

| I/O Ports                      | 257 |

| Parallel I/O (PIO)             | 258 |

| Write/Read Timing              | 258 |

| Input Change Notification      | 258 |

| Instruction Set                | 725 |

| Inter-Integrated Circuit (I2C) | 367 |

|                                |     |