Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                                        |

|----------------------------|-----------------------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                            |

| Speed                      | 200MHz                                                                                        |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, SQI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT                            |

| Number of I/O              | 120                                                                                           |

| Program Memory Size        | 2MB (2M x 8)                                                                                  |

| Program Memory Type        | FLASH                                                                                         |

| EEPROM Size                | -                                                                                             |

| RAM Size                   | 256K x 8                                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                   |

| Data Converters            | A/D 45x12b                                                                                    |

| Oscillator Type            | Internal                                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                             |

| Mounting Type              | Surface Mount                                                                                 |

| Package / Case             | 169-LFBGA                                                                                     |

| Supplier Device Package    | 169-LFBGA (11x11)                                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2025dah169-i-6j              |

|                            |                                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 6: PIN NAMES FOR 176-PIN DEVICES (CONTINUED)

|                                                                                                                                                                                                            | PIN LQFP (TOP VIEW)<br>PIC32MZ1025DAA176<br>PIC32MZ1025DAB176<br>PIC32MZ1064DAA176<br>PIC32MZ1064DAB176<br>PIC32MZ2025DAA176<br>PIC32MZ2025DAB176<br>PIC32MZ2064DAA176<br>PIC32MZ2064DAB176<br>PIC32MZ1025DAG176<br>PIC32MZ1064DAG176<br>PIC32MZ2025DAG176<br>PIC32MZ2025DAH176<br>PIC32MZ2025DAH176<br>PIC32MZ2025DAH176<br>PIC32MZ2064DAG176<br>PIC32MZ2064DAG176<br>PIC32MZ2064DAG176<br>PIC32MZ2064DAH176 | 176                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                               |

| Pin<br>Number                                                                                                                                                                                              | Full Pin Name                                                                                                                                                                                                                                                                                                                                                                                                 | Pin<br>Number                                                                                                                                                                                              | Full Pin Name                                                                                                                                                                                                                                                                                                                 |

| Pin                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                            | Full Pin Name<br>SOSCO/RPC14 <sup>(7)</sup> /T1CK/RC14 <sup>(7)</sup>                                                                                                                                                                                                                                                         |

| Pin<br>Number                                                                                                                                                                                              | Full Pin Name                                                                                                                                                                                                                                                                                                                                                                                                 | <br>Number                                                                                                                                                                                                 | SOSCO/RPC14 <sup>(7)</sup> /T1CK/RC14 <sup>(7)</sup>                                                                                                                                                                                                                                                                          |

| Pin<br>Number<br>145                                                                                                                                                                                       | Full Pin Name GD9/EBIBS0/RJ12                                                                                                                                                                                                                                                                                                                                                                                 | <br>Number<br>161                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                               |

| Pin<br>Number<br>145<br>146                                                                                                                                                                                | Full Pin Name           GD9/EBIBS0/RJ12           GD18/EBIBS1/RJ10                                                                                                                                                                                                                                                                                                                                            | <br>Number           161           162                                                                                                                                                                     | SOSCO/RPC14 <sup>(7)</sup> /T1CK/RC14 <sup>(7)</sup><br>SOSCI/RPC13 <sup>(7)</sup> /RC13 <sup>(7)</sup>                                                                                                                                                                                                                       |

| Pin<br>Number<br>145<br>146<br>147                                                                                                                                                                         | Full Pin Name       GD9/EBIBS0/RJ12       GD18/EBIBS1/RJ10       GEN/EBICS3/RJ7                                                                                                                                                                                                                                                                                                                               | Number           161           162           163                                                                                                                                                           | SOSCO/RPC14 <sup>(7)</sup> /T1CK/RC14 <sup>(7)</sup><br>SOSCI/RPC13 <sup>(7)</sup> /RC13 <sup>(7)</sup><br>OSC2/CLKO/RC15                                                                                                                                                                                                     |

| Pin<br>Number<br>145<br>146<br>147<br>148                                                                                                                                                                  | Full Pin Name         GD9/EBIBS0/RJ12         GD18/EBIBS1/RJ10         GEN/EBICS3/RJ7         GCLK/EBICS2/RJ6                                                                                                                                                                                                                                                                                                 | Number           161           162           163           164                                                                                                                                             | SOSCO/RPC14 <sup>(7)</sup> /T1CK/RC14 <sup>(7)</sup><br>SOSCI/RPC13 <sup>(7)</sup> /RC13 <sup>(7)</sup><br>OSC2/CLKO/RC15<br>OSC1/CLKI/RC12                                                                                                                                                                                   |

| Pin<br>Number<br>145<br>146<br>147<br>148<br>149                                                                                                                                                           | Full Pin Name         GD9/EBIBS0/RJ12         GD18/EBIBS1/RJ10         GEN/EBICS3/RJ7         GCLK/EBICS2/RJ6         HSYNC/EBICS1/RJ5                                                                                                                                                                                                                                                                        | Number           161           162           163           164           165                                                                                                                               | SOSCO/RPC14 <sup>(7)</sup> /T1CK/RC14 <sup>(7)</sup><br>SOSCI/RPC13 <sup>(7)</sup> /RC13 <sup>(7)</sup><br>OSC2/CLKO/RC15<br>OSC1/CLKI/RC12<br>VDDIO                                                                                                                                                                          |

| Pin<br>Number<br>145<br>146<br>147<br>148<br>149<br>150                                                                                                                                                    | Full Pin Name         GD9/EBIBS0/RJ12         GD18/EBIBS1/RJ10         GEN/EBICS3/RJ7         GCLK/EBICS2/RJ6         HSYNC/EBICS1/RJ5         VSYNC/EBICS0/RJ4                                                                                                                                                                                                                                               | Number           161           162           163           164           165           166                                                                                                                 | SOSCO/RPC14 <sup>(7)</sup> /T1CK/RC14 <sup>(7)</sup><br>SOSCI/RPC13 <sup>(7)</sup> /RC13 <sup>(7)</sup><br>OSC2/CLKO/RC15<br>OSC1/CLKI/RC12<br>VDDIO<br>VBAT                                                                                                                                                                  |

| Pin<br>Number<br>145<br>146<br>147<br>148<br>149<br>150<br>151                                                                                                                                             | Full Pin Name         GD9/EBIBS0/RJ12         GD18/EBIBS1/RJ10         GEN/EBICS3/RJ7         GCLK/EBICS2/RJ6         HSYNC/EBICS1/RJ5         VSYNC/EBICS0/RJ4         GD20/EBIA22/RJ3                                                                                                                                                                                                                       | Number           161           162           163           164           165           166           167                                                                                                   | SOSCO/RPC14 <sup>(7)</sup> /T1CK/RC14 <sup>(7)</sup><br>SOSCI/RPC13 <sup>(7)</sup> /RC13 <sup>(7)</sup><br>OSC2/CLKO/RC15<br>OSC1/CLKI/RC12<br>VDDIO<br>VBAT<br>AN45/RPB5/RB5                                                                                                                                                 |

| Pin           Number           145           146           147           148           149           150           151                                                                                     | Full Pin Name         GD9/EBIBS0/RJ12         GD18/EBIBS1/RJ10         GEN/EBICS3/RJ7         GCLK/EBICS2/RJ6         HSYNC/EBICS1/RJ5         VSYNC/EBICS0/RJ4         GD20/EBIA22/RJ3         EBIRDY3/AN32/RJ2         Vss         Vss                                                                                                                                                                      | Number           161           162           163           164           165           166           167                                                                                                   | SOSCO/RPC14 <sup>(7)</sup> /T1CK/RC14 <sup>(7)</sup><br>SOSCI/RPC13 <sup>(7)</sup> /RC13 <sup>(7)</sup><br>OSC2/CLKO/RC15<br>OSC1/CLKI/RC12<br>VDDIO<br>VBAT<br>AN45/RPB5/RB5<br>AN5/RPB10/RB10                                                                                                                               |

| Pin<br>Number<br>145<br>146<br>147<br>148<br>149<br>150<br>151<br>152<br>153                                                                                                                               | Full Pin Name         GD9/EBIBS0/RJ12         GD18/EBIBS1/RJ10         GEN/EBICS3/RJ7         GCLK/EBICS2/RJ6         HSYNC/EBICS1/RJ5         VSYNC/EBICS0/RJ4         GD20/EBIA22/RJ3         EBIRDY3/AN32/RJ2         Vss                                                                                                                                                                                  | Number           161           162           163           164           165           166           167           168           169                                                                       | SOSCO/RPC14 <sup>(7)</sup> /T1CK/RC14 <sup>(7)</sup><br>SOSCI/RPC13 <sup>(7)</sup> /RC13 <sup>(7)</sup><br>OSC2/CLKO/RC15<br>OSC1/CLKI/RC12<br>VDDIO<br>VBAT<br>AN45/RPB5/RB5<br>AN5/RPB5/RB5<br>AN5/RPB10/RB10<br>PGED1/AN0/RPB0/CTED2/RB0<br>PGED2/C1INA/AN46/RPB7/RB7<br>AN6/RB12                                          |

| Pin<br>Number<br>145<br>146<br>147<br>148<br>149<br>150<br>151<br>152<br>153<br>154                                                                                                                        | Full Pin Name         GD9/EBIBS0/RJ12         GD18/EBIBS1/RJ10         GEN/EBICS3/RJ7         GCLK/EBICS2/RJ6         HSYNC/EBICS1/RJ5         VSYNC/EBICS0/RJ4         GD20/EBIA22/RJ3         EBIRDY3/AN32/RJ2         Vss         Vss                                                                                                                                                                      | Number           161           162           163           164           165           166           167           168           169           170                                                         | SOSCO/RPC14 <sup>(7)</sup> /T1CK/RC14 <sup>(7)</sup><br>SOSCI/RPC13 <sup>(7)</sup> /RC13 <sup>(7)</sup><br>OSC2/CLKO/RC15<br>OSC1/CLKI/RC12<br>VDDIO<br>VBAT<br>AN45/RPB5/RB5<br>AN5/RPB10/RB10<br>PGED1/AN0/RPB0/CTED2/RB0<br>PGED2/C1INA/AN46/RPB7/RB7                                                                      |

| Pin<br>Number<br>145<br>146<br>147<br>148<br>149<br>150<br>151<br>152<br>153<br>154<br>155                                                                                                                 | Full Pin Name         GD9/EBIBS0/RJ12         GD18/EBIBS1/RJ10         GEN/EBICS3/RJ7         GCLK/EBICS2/RJ6         HSYNC/EBICS1/RJ5         VSYNC/EBICS0/RJ4         GD20/EBIA22/RJ3         EBIRDY3/AN32/RJ2         Vss         Vss         Vodio                                                                                                                                                        | Number           161           162           163           164           165           166           167           168           169           170                                                         | SOSCO/RPC14 <sup>(7)</sup> /T1CK/RC14 <sup>(7)</sup><br>SOSCI/RPC13 <sup>(7)</sup> /RC13 <sup>(7)</sup><br>OSC2/CLKO/RC15<br>OSC1/CLKI/RC12<br>VDDIO<br>VBAT<br>AN45/RPB5/RB5<br>AN5/RPB5/RB5<br>AN5/RPB10/RB10<br>PGED1/AN0/RPB0/CTED2/RB0<br>PGED2/C1INA/AN46/RPB7/RB7<br>AN6/RB12                                          |

| Pin<br>Number<br>145<br>146<br>147<br>148<br>149<br>150<br>151<br>152<br>153<br>154<br>155<br>156<br>157<br>158                                                                                            | Full Pin Name         GD9/EBIBS0/RJ12         GD18/EBIBS1/RJ10         GEN/EBICS3/RJ7         GCLK/EBICS2/RJ6         HSYNC/EBICS2/RJ6         HSYNC/EBICS2/RJ6         GD20/EBIA22/RJ3         EBIRDY3/AN32/RJ2         Vss         VDDIO         VDDIO         AN33/SCK6/RD15         AN22/RPD14/RD14                                                                                                       | Number           161           162           163           164           165           166           167           168           169           170           171           172           173           174 | SOSCO/RPC14 <sup>(7)</sup> /T1CK/RC14 <sup>(7)</sup><br>SOSCI/RPC13 <sup>(7)</sup> /RC13 <sup>(7)</sup><br>OSC2/CLKO/RC15<br>OSC1/CLKI/RC12<br>VDDIO<br>VBAT<br>AN45/RPB5/RB5<br>AN5/RPB10/RB10<br>PGED1/AN0/RPB0/CTED2/RB0<br>PGED2/C1INA/AN46/RPB7/RB7<br>AN6/RB12<br>AN1/C2INB/RPB2/RB2                                    |

| Pin           Number           145           146           147           148           149           150           151           152           153           154           155           156           157 | Full Pin Name         GD9/EBIBS0/RJ12         GD18/EBIBS1/RJ10         GEN/EBICS3/RJ7         GCLK/EBICS2/RJ6         HSYNC/EBICS2/RJ6         HSYNC/EBICS1/RJ5         VSYNC/EBICS0/RJ4         GD20/EBIA22/RJ3         EBIRDY3/AN32/RJ2         Vss         VDIO         VDDIO         AN33/SCK6/RD15                                                                                                       | Number           161           162           163           164           165           166           167           168           169           170           171           172           173               | SOSCO/RPC14 <sup>(7)</sup> /T1CK/RC14 <sup>(7)</sup><br>SOSCI/RPC13 <sup>(7)</sup> /RC13 <sup>(7)</sup><br>OSC2/CLKO/RC15<br>OSC1/CLKI/RC12<br>VDDIO<br>VBAT<br>AN45/RPB5/RB5<br>AN5/RPB10/RB10<br>PGED1/AN0/RPB0/CTED2/RB0<br>PGED2/C1INA/AN46/RPB7/RB7<br>AN6/RB12<br>AN1/C2INB/RPB2/RB2<br>EBIA7/AN47/HLVDIN/RPB9/PMA7/RB9 |

1: The RPn pins can be used by remappable peripherals. See Table 1 and Table 3 for the available peripherals and 12.4 "Peripheral Pin Select (PPS)" for restrictions.

2: Every I/O port pin (RAx-RKx) can be used as a change notification pin (CNAx-CNKx). See 12.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

4: The metal plane at the bottom of the device is internally tied to VSS1V8 and should be connected to 1.8V ground externally.

5: This pin must be tied to Vss through a 20k  $\Omega$  resistor in devices without DDR.

6: This pin is a No Connect in devices without DDR.

7: These pins are restricted to input functions only.

#### TABLE 7:PIN NAMES FOR 288-PIN DEVICES (CONTINUED)

| 288-P                      | PIN LFBGA (BOTTOM V                                                                                                                      | IEW)    |                    |                        |            |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------|------------------------|------------|

|                            |                                                                                                                                          | A1      |                    | V1                     |            |

|                            | IC32MZ1025DAA288                                                                                                                         | F6      |                    | N6                     |            |

| Pi<br>Pi<br>Pi<br>Pi<br>Pi | IC32MZ1025DAB288<br>IC32MZ1064DAA288<br>IC32MZ1064DAB288<br>IC32MZ2025DAA288<br>IC32MZ2025DAB288<br>IC32MZ2064DAA288<br>IC32MZ2064DAB288 | F13     |                    |                        | N13<br>V18 |

|                            |                                                                                                                                          | A18     | 1                  |                        |            |

|                            | Polarity Inc                                                                                                                             | dicator |                    |                        |            |

| Ball/Pin<br>Number         | Full Pin Na                                                                                                                              | me      | Ball/Pin<br>Number | Full Pin Name          |            |

| J10                        | Vddio                                                                                                                                    |         | L12                | VDDIO                  |            |

| J11                        | Vss                                                                                                                                      |         | L13                | Vss                    |            |

| J12                        | Vss                                                                                                                                      |         | L15                | Vss                    |            |

| J13                        | Vss                                                                                                                                      |         | L15                | GEN/EBICS3/RJ7         |            |

| J15                        | VDDIO                                                                                                                                    |         | L10                | GCLK/EBICS2/RJ6        |            |

| J16                        | AN33/SCK6/RD15                                                                                                                           |         |                    | HSYNC/EBICS1/RJ5       |            |

| J10                        |                                                                                                                                          |         | L18                |                        |            |

| -                          | AN29/SCK3/RB14                                                                                                                           |         | M1                 | DDRRAS                 |            |

| J18                        | AN22/RPD14/RD14                                                                                                                          |         | M2                 | DDRBA0                 |            |

| K1                         | DDRCK                                                                                                                                    |         | M3                 | DDRBA1                 |            |

| K2                         | DDRCK                                                                                                                                    |         | M4                 | SCK1/RD1               |            |

| K3                         | EBIA6/RPE5/PMA6/RE5                                                                                                                      |         | M6                 | VSS1V8                 |            |

| K4                         | SDCMD/SQICS0/RPD4/RD4                                                                                                                    |         | M7                 | VSS1V8                 |            |

| K6                         | VDDR1V8 <sup>(4)</sup>                                                                                                                   |         | M8                 | VSS1V8                 |            |

| K7                         | VDDR1V8 <sup>(4)</sup>                                                                                                                   |         | M9                 | VSS1V8                 |            |

| K8                         | VDDR1V8 <sup>(4)</sup>                                                                                                                   |         | M10                | Vss                    |            |

| K9                         | VSS1V8                                                                                                                                   |         | M11                | Vss                    |            |

| K10                        | VDDIO                                                                                                                                    |         | M12                | VDDIO                  |            |

| K11                        | Vss                                                                                                                                      |         | M13                | VDDIO                  |            |

| K12                        | Vss                                                                                                                                      |         | M15                | VDDIO                  |            |

| K13                        | Vss                                                                                                                                      |         | M16                | GD0/EBID13/PMD13/RJ13  |            |

| K15                        | Vss                                                                                                                                      |         | M17                | GD9/EBIBS0/RJ12        |            |

| K16                        | EBIRDY3/AN32/RJ2                                                                                                                         |         | M18                | GD18/EBIBS1/RJ10       |            |

| K17                        | GD20/EBIA22/RJ3                                                                                                                          |         | N1                 | DDRODT                 |            |

| K18                        | VSYNC/EBICS0/RJ4                                                                                                                         |         | N2                 | DDRCS0                 |            |

| L1                         | DDRWE                                                                                                                                    |         | N3                 | DDRA2                  |            |

| L2                         | DDRCKE                                                                                                                                   |         | N4                 | GD22/EBIA13/PMA13/RD13 |            |

| L3                         | DDRA1                                                                                                                                    |         | N6                 | VSS1V8                 |            |

| L3<br>L4                   | SQICS1/RPD5/RD5                                                                                                                          |         | N7                 | VSS1V8                 |            |

| L4<br>L6                   | VDDR1V8 <sup>(4)</sup>                                                                                                                   |         | N8                 | VSS1V8                 |            |

| L0<br>L7                   | VDDR1V8(4)                                                                                                                               |         | N9                 | VSS1V8<br>VSS1V8       |            |

|                            | VDDR1V8 <sup>(4)</sup>                                                                                                                   |         |                    |                        |            |

| L8                         |                                                                                                                                          |         | N10                | Vss                    |            |

| L9                         | VSS1V8                                                                                                                                   |         | N11                | Vss                    |            |

| 1.40                       |                                                                                                                                          |         |                    |                        |            |

| L10<br>L11                 | Vss<br>Vddio                                                                                                                             |         | N12<br>N13         | VDDIO<br>VDDIO         |            |

e 1: The RPn pins can be used by remappable peripherals. See Table 1 and Table 4 for the available peripherals and 12.4 "Peripheral Pi Select (PPS)" for restrictions.

2: Every I/O port pin (RAx-RKx) can be used as a change notification pin (CNAx-CNKx). See 12.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

4: This pin must be tied to Vss through a 20k  $\Omega$  resistor when DDR is not connected in the system.

5: This pin is a No Connect when DDR is not connected in the system.

**6:** These pins are restricted to input functions only.

| TABLE 4-1: A | DDRESS MAPPING TABLE |

|--------------|----------------------|

|--------------|----------------------|

| Memory          | Size                  | Region End<br>Address (KSEG1) | Region End<br>Address (KSEG0) | Region End<br>Address (Physical) |

|-----------------|-----------------------|-------------------------------|-------------------------------|----------------------------------|

| Program Flash   | 2 MB                  | 0xBD1FFFFF                    | 0x9D1FFFFF                    | 0x1D1FFFFF                       |

| FIOGRAFII FIAST | 1 MB                  | 0xBD0FFFFF                    | 0x9D0FFFFF                    | 0x1D0FFFFF                       |

|                 | EXT <sup>(1)</sup>    | 0xAFFFFFFF                    | 0x8FFFFFFF                    | 0x0FFFFFFF                       |

| DDR2 SDRAM      | 32 MB <sup>(5)</sup>  | 0xA9FFFFFF                    | 0x89FFFFFF                    | 0x09FFFFFF                       |

|                 | (2)                   | Reserved                      | Reserved                      | Reserved                         |

| RAM             | 640 KB <sup>(3)</sup> | 0xA009FFFF                    | 0x8009FFFF                    | 0x0009FFFF                       |

| KAIVI           | 256 KB <sup>(4)</sup> | 0xA003FFFF                    | 0x8003FFFF                    | 0x0003FFFF                       |

**Note 1:** External DDR2 SDRAM can be up to 128 MB, EXTDDRSIZE<3:0> bits (DEVCFG3<19:16>) should be set, and the region end address should be scaled accordingly.

2: Devices without the DDR2 option.

3: Devices with 640 KB RAM contain SRAM Bank 1 (256 KB) and SRAM Bank 2 (384 KB).

4: Devices with 256 KB RAM contain SRAM Bank 1 (128 KB) and SRAM Bank 2 (128 KB).

5: Refer to 4.2 "DDR2 SDRAM" for DDR2 SDRAM features, which are applicable to devices with internal DDR2 SDRAM.

#### TABLE 4-19: SYSTEM BUS TARGET PROTECTION GROUP 9 REGISTER MAP

| ess                         |                  | 6         |       |       |                               |        |       |       |       | Bi         | ts     |       |           |      |        |        |          |        |               |

|-----------------------------|------------------|-----------|-------|-------|-------------------------------|--------|-------|-------|-------|------------|--------|-------|-----------|------|--------|--------|----------|--------|---------------|

| Virtual Address<br>(BF90_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13                         | 28/12  | 27/11 | 26/10 | 25/9  | 24/8       | 23/7   | 22/6  | 21/5      | 20/4 | 19/3   | 18/2   | 17/1     | 16/0   | All<br>Resets |

| 8C20                        | SBT9ELOG1        | 31:16     | MULTI |       | —                             | _      |       | CODE  | <3:0> |            |        | —     | —         |      | —      | —      | —        |        | 0000          |

| 0020                        | SBISELOGI        | 15:0      |       |       |                               | INITID | <7:0> |       |       |            |        | REGIO | N<3:0>    |      | —      |        | CMD<2:0> |        | 0000          |

| 8C24                        | SBT9ELOG2        | 31:16     | —     | —     | —                             | —      | _     | —     | —     | —          | _      | —     | —         | —    | —      | —      | —        | -      | 0000          |

| 0024                        | 3B19EE0G2        | 15:0      | —     | —     | —                             | —      | _     | —     | —     | —          | _      | —     | —         | —    | —      | —      | GROU     | P<1:0> | 0000          |

| 8C28                        | SBT9ECON         | 31:16     | —     | —     | —                             | —      | _     | —     | —     | ERRP       | _      | —     | —         | —    | —      | —      | —        | -      | 0000          |

| 0020                        | SBISECON         | 15:0      | _     | —     | —                             | —      | _     | _     | _     | —          | _      | —     | —         | —    |        | —      | —        | _      | 0000          |

| 8C30                        | SBT9ECLRS        | 31:16     | _     | —     | —                             | —      | —     | —     | —     | —          | —      | —     | —         | —    |        | —      | —        | _      | 0000          |

| 0000                        | OBTOLCERO        | 15:0      | _     | —     | —                             | —      | —     | —     | —     | —          | —      | —     | —         | —    |        | —      | —        | CLEAR  | 0000          |

| 8C38                        | SBT9ECLRM        | 31:16     | _     | —     | —                             | —      | —     | —     | —     | —          | —      | —     | —         | —    |        | —      | —        | _      | 0000          |

| 0000                        | OBTOECEI         | 15:0      | _     | —     | —                             |        | —     | —     |       | —          | —      |       | —         | —    | —      |        | —        | CLEAR  | 0000          |

| 8C40                        | SBT9REG0         | 31:16     |       |       |                               |        |       |       | -     | BASE       | <21:6> |       |           |      |        | -      |          |        | xxxx          |

| 00-0                        | OBTOREGO         | 15:0      |       |       | BASE                          | <5:0>  |       |       | PRI   | —          |        | -     | SIZE<4:0> | -    |        | —      | —        | _      | xxxx          |

| 8C50                        | SBT9RD0          | 31:16     | _     | —     | —                             | —      | —     | —     | —     | —          | —      | —     | —         | —    |        | —      | —        | _      | xxxx          |

| 0000                        | 00191000         | 15:0      | _     | —     | —                             | _      | _     | _     | _     | _          | _      | _     | —         | _    | GROUP3 | GROUP2 | GROUP1   | GROUP0 | xxxx          |

| 8C58                        | SBT9WR0          | 31:16     | _     | —     | —                             | _      | _     | _     | _     | _          | _      | _     | —         | _    |        | _      | —        |        | xxxx          |

| 0000                        | 36190010         | 15:0      | _     | _     | —                             | —      | _     | _     | —     | —          | _      | —     | —         | —    | GROUP3 | GROUP2 | GROUP1   | GROUP0 | xxxx          |

| 8C60                        | SBT9REG1         | 31:16     |       |       |                               |        |       |       |       | BASE<21:6> |        |       |           |      |        |        | xxxx     |        |               |

| 0000                        | OBTINEOT         | 15:0      |       |       | BASE<5:0> PRI — SIZE<4:0> — — |        |       |       |       |            | _      | xxxx  |           |      |        |        |          |        |               |

| 8C70                        | SBT9RD1          | 31:16     | _     | —     | _                             | _      | _     | _     | _     | _          | _      | _     | _         | _    |        | _      | _        |        | xxxx          |

| 3070                        | 0010101          | 15:0      | _     | —     | _                             | _      | _     | _     | _     | _          | _      | _     | _         | _    | GROUP3 | GROUP2 | GROUP1   | GROUP0 | xxxx          |

| 8C78                        | SBT9WR1          | 31:16     | _     | —     | _                             | _      | _     | _     | _     | _          | _      | _     | _         | _    |        | _      | —        | _      | xxxx          |

| 5070                        | ODISWITT         | 15:0      | —     | —     | —                             | —      | _     | —     | —     | _          |        | —     | —         | —    | GROUP3 | GROUP2 | GROUP1   | GROUP0 | xxxx          |

© 2015-2018 Microchip Technology Inc.

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note: For reset values listed as 'xxxx', please refer to Table 4-8 for the actual reset values.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6              | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2        | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|--------------------------------|-------------------|-------------------|--------------------|--------------------------|------------------|------------------|

| 04.04        | U-0               | U-0                            | R/W-0             | R/W-0             | R/W-0              | U-0                      | U-0              | R/W-0            |

| 31:24        | _                 | —                              | BYTO              | <1:0>             | WBO <sup>(1)</sup> |                          | —                | BITO             |

| 00.40        | U-0               | U-0                            | U-0               | U-0               | U-0                | U-0                      | U-0              | U-0              |

| 23:16        | —                 | —                              | _                 | —                 | _                  | _                        | —                | _                |

| 45.0         | U-0               | U-0                            | U-0               | R/W-0             | R/W-0              | R/W-0                    | R/W-0            | R/W-0            |

| 15:8         | —                 | _                              | _                 |                   |                    | PLEN<4:0> <sup>(1)</sup> | )                |                  |

| 7.0          | R/W-0             | R/W-0                          | R/W-0             | U-0               | U-0                | R/W-0                    | R/W-0            | R/W-0            |

| 7:0          | CRCEN             | CRCAPP <sup>(1)</sup> CRCTYP — |                   | _                 |                    | (                        | CRCCH<2:0>       | •                |

#### REGISTER 10-4: DCRCCON: DMA CRC CONTROL REGISTER

#### Legend:

| 5                 |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-30 Unimplemented: Read as '0'

- bit 29-28 BYTO<1:0>: CRC Byte Order Selection bits

- 11 = Endian byte swap on half-word boundaries (i.e., source half-word order with reverse source byte order per half-word)

- 10 = Swap half-words on word boundaries (i.e., reverse source half-word order with source byte order per half-word)

- 01 = Endian byte swap on word boundaries (i.e., reverse source byte order)

- 00 = No swapping (i.e., source byte order)

- bit 27 WBO: CRC Write Byte Order Selection bit<sup>(1)</sup>

- 1 = Source data is written to the destination re-ordered as defined by BYTO<1:0>

- 0 = Source data is written to the destination unaltered

- bit 26-25 Unimplemented: Read as '0'

- bit 24 BITO: CRC Bit Order Selection bit

When CRCTYP (DCRCCON<5>) = 1 (CRC module is in IP Header mode):

- 1 = The IP header checksum is calculated Least Significant bit (LSb) first (i.e., reflected)

- 0 = The IP header checksum is calculated Most Significant bit (MSb) first (i.e., not reflected)

When CRCTYP (DCRCCON<5>) = 0 (CRC module is in LFSR mode):

- 1 = The LFSR CRC is calculated Least Significant bit first (i.e., reflected)

- 0 = The LFSR CRC is calculated Most Significant bit first (i.e., not reflected)

- bit 23-13 Unimplemented: Read as '0'

- bit 12-8 **PLEN<4:0>:** Polynomial Length bits<sup>(1)</sup>

<u>When CRCTYP (DCRCCON<5>) = 1</u> (CRC module is in IP Header mode): These bits are unused.

<u>When CRCTYP (DCRCCON<5>) = 0</u> (CRC module is in LFSR mode): Denotes the length of the polynomial -1.

- bit 7 CRCEN: CRC Enable bit

- 1 = CRC module is enabled and channel transfers are routed through the CRC module

- 0 = CRC module is disabled and channel transfers proceed normally

- **Note 1:** When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

| Bit<br>Range | Bit<br>31/23/15/7          | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|----------------------------|-------------------|-------------------|-------------------|----------------------|-------------------|------------------|------------------|--|--|--|

|              | U-0                        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0              | U-0              |  |  |  |

| 31:24        |                            |                   | -                 | -                 | —                    |                   | _                | _                |  |  |  |

| 00.40        | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1                | R/W-1             | R/W-1            | R/W-1            |  |  |  |

| 23:16        | CHAIRQ<7:0> <sup>(1)</sup> |                   |                   |                   |                      |                   |                  |                  |  |  |  |

| 45.0         | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1                | R/W-1             | R/W-1            | R/W-1            |  |  |  |

| 15:8         |                            |                   |                   | CHSIRQ            | <7:0> <sup>(1)</sup> |                   |                  |                  |  |  |  |

| 7:0          | S-0                        | S-0               | R/W-0             | R/W-0             | R/W-0                | U-0               | U-0              | U-0              |  |  |  |

| 7:0          | CFORCE                     | CABORT            | PATEN             | SIRQEN            | AIRQEN               |                   | _                | _                |  |  |  |

#### **REGISTER 10-8: DCHxECON: DMA CHANNEL x EVENT CONTROL REGISTER**

| Legend:           | S = Settable bit |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-24 Unimplemented: Read as '0'

- bit 23-16 CHAIRQ<7:0>: Channel Transfer Abort IRQ bits<sup>(1)</sup>

- 111111111 = Interrupt 255 will abort any transfers in progress and set CHAIF flag

- .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

- - 00000001 = Interrupt 1 will initiate a DMA transfer 00000000 = Interrupt 0 will initiate a DMA transfer

- bit 7 CFORCE: DMA Forced Transfer bit

- 1 = A DMA transfer is forced to begin when this bit is written to a '1'

- 0 = This bit always reads '0'

- bit 6 CABORT: DMA Abort Transfer bit

- 1 = A DMA transfer is aborted when this bit is written to a '1'

- 0 = This bit always reads '0'

#### bit 5 **PATEN:** Channel Pattern Match Abort Enable bit

- 1 = Abort transfer and clear CHEN on pattern match

- 0 = Pattern match is disabled

- bit 4 SIRQEN: Channel Start IRQ Enable bit

- 1 = Start channel cell transfer if an interrupt matching CHSIRQ occurs

- 0 = Interrupt number CHSIRQ is ignored and does not start a transfer

- bit 3 AIRQEN: Channel Abort IRQ Enable bit

- 1 = Channel transfer is aborted if an interrupt matching CHAIRQ occurs

- 0 = Interrupt number CHAIRQ is ignored and does not terminate a transfer

- bit 2-0 Unimplemented: Read as '0'

- Note 1: See Table 7-2: "Interrupt IRQ, Vector and Bit Location" for the list of available interrupt IRQ sources.

|                    |                  |           |       |                   |        |           |          |        |         |        | Bits       |           |           |          |           |          |         |          |            |

|--------------------|------------------|-----------|-------|-------------------|--------|-----------|----------|--------|---------|--------|------------|-----------|-----------|----------|-----------|----------|---------|----------|------------|

| Virtual<br>Address | Register<br>Name | Bit Range | 31/15 | 30/14             | 29/13  | 28/12     | 27/11    | 26/10  | 25/9    | 24/8   | 23/7       | 22/6      | 21/5      | 20/4     | 19/3      | 18/2     | 17/1    | 16/0     | All Resets |

| 2020               | USB              | 31:16     |       |                   |        | I         |          |        |         | L<br>C | ATA<31:16> |           |           |          |           |          |         | <u> </u> | 000        |

| 3028               | FIFO2            | 15:0      |       |                   |        |           |          |        |         | [      | DATA<15:0> |           |           |          |           |          |         |          | 000        |

| 302C               | USB              | 31:16     |       |                   |        |           |          |        |         | D      | ATA<31:16> |           |           |          |           |          |         |          | 000        |

| 3020               | FIFO3            | 15:0      |       |                   |        |           |          |        |         | [      | DATA<15:0> |           |           |          |           |          |         |          | 000        |

| 3030               | USB              | 31:16     |       |                   |        |           |          |        |         | D      | ATA<31:16> |           |           |          |           |          |         |          | 000        |

| 3030               | FIFO4            | 15:0      |       |                   |        |           |          |        |         | [      | DATA<15:0> |           |           |          |           |          |         |          | 000        |

| 3034               | USB              | 31:16     |       |                   |        |           |          |        |         | D      | ATA<31:16> |           |           |          |           |          |         |          | 0000       |

| 0004               | FIFO5            | 15:0      |       |                   |        |           |          |        |         | [      | DATA<15:0> |           |           |          |           |          |         |          | 000        |

| 3038               | USB              | 31:16     |       |                   |        |           |          |        |         |        | ATA<31:16> |           |           |          |           |          |         |          | 0000       |

| 0000               | FIFO6            | 15:0      |       |                   |        |           |          |        |         | [      | DATA<15:0> |           |           |          |           |          |         |          | 0000       |

| 303C               | USB              | 31:16     |       |                   |        |           |          |        |         | D      | ATA<31:16> |           |           |          |           |          |         |          | 0000       |

| 0000               | FIF07            | 15:0      |       |                   |        | -         |          |        |         | [      | DATA<15:0> |           |           |          |           |          |         |          | 0000       |

| 3060               | USBOTG           | 31:16     | -     | —                 | —      | RXDPB     |          | RXFIFC | SZ<3:0> |        | —          | _         | —         | TXDPB    |           | TXFIFOSZ |         |          | 0000       |

|                    | 002010           | 15:0      | -     | _                 | —      | —         | —        | —      | TXEDMA  | RXEDMA | BDEV       | FSDEV     | LSDEV     | VBUS     | <1:0>     | HOSTMODE | HOSTREQ | SESSION  | N 0088     |

| 3064               | USB              | 31:16     | -     | _                 | —      |           |          |        |         |        |            | RXFIFOAD< |           |          |           |          |         |          | 0000       |

|                    | FIFOA            | 15:0      | -     | _                 | —      |           | -        |        |         | -      |            | TXFIFOAD< | 12:0>     |          | -         |          | _       |          | 0000       |

| 306C               | USB              | 31:16     | —     | —                 | —      | —         | —        | —      | —       | —      | —          | _         | —         | _        | —         | —        | —       | —        | 0000       |

|                    | HWVER            | 15:0      | RC    |                   | VEF    | RMAJOR<4: |          |        |         |        | 1          |           | VERMINO   | R<9:0>   |           |          |         |          | 0800       |

| 3078               | USB              | 31:16     |       |                   |        | VPLEN     | <7:0>    |        |         |        |            |           | ON<3:0>   |          |           | WTID<3   |         |          | 3C50       |

|                    | INFO             | 15:0      |       | DMACHAN           | S<3:0> |           |          | RAMBI  | TS<3:0> | r      |            | RXEND     | )PTS<3:0> |          |           | TXENDPT  | S<3:0>  |          | 8C77       |

| 307C               | USB              | 31:16     | -     | -                 | —      | —         | —        | —      | NRSTX   | NRST   |            |           |           | LSEOF<7: |           |          |         |          | 0072       |

|                    | EOFRST           | 15:0      |       |                   |        | FSEOF     |          |        |         |        | <br>       |           |           | HSEOF<7  | -         |          |         |          | 7780       |

| 3080               | USB<br>E0TXA     | 31:16     | -     |                   |        | TX        | HUBPRT<6 | :0>    |         |        | MULTTRAN   |           |           |          | BADD<6:0> |          |         |          | 0000       |

|                    | EUTXA            | 15:0      | -     | —                 | —      | —         | —        | —      | —       | -      | —          |           |           |          | DDR<6:0>  |          |         |          | 0000       |

| 3084               | USB<br>E0RXA     | 31:16     | _     |                   |        |           | HUBPRT<6 | :0>    |         |        | MULTTRAN   |           |           |          | BADD<6:0> |          |         | 1        | 0000       |

|                    |                  | 15:0      | _     | _                 | —      |           |          |        |         | —      | —          | -         | -         | -        |           | -        | -       | -        | 0000       |

| 3088               | USB<br>E1TXA     | 31:16     | _     |                   |        | IX        | HUBPRT<6 | :0>    |         |        | MULTTRAN   |           |           |          | BADD<6:0> |          |         |          | 0000       |

|                    |                  | 15:0      | _     | _                 |        | —         | -        |        |         | —      | -          |           |           |          | DDR<6:0>  |          |         |          | 0000       |

| 308C               | USB<br>E1RXA     | 31:16     | _     |                   | 1      |           | HUBPRT<6 |        |         | 1      | MULTTRAN   |           |           |          | BADD<6:0> |          |         |          | 0000       |

| $\vdash$           |                  | 15:0      | _     | -                 | —      | —<br>—    | -        |        | —       | -      | —          |           |           |          | DDR<6:0>  |          |         |          | 0000       |

| 3090               | USB<br>E2TXA     | 31:16     | _     |                   |        |           | HUBPRT<6 |        |         |        | MULTTRAN   |           |           |          | BADD<6:0> |          |         |          | 0000       |

|                    |                  | 15:0      | _     | -                 | —      |           |          | -      | —       | -      |            |           |           |          | DDR<6:0>  |          |         |          | 0000       |

| 3094               | USB<br>E2RXA     | 31:16     | _     |                   |        |           | HUBPRT<6 |        |         |        | MULTTRAN   |           |           |          | BADD<6:0> |          |         |          | 0000       |

|                    |                  | 15:0      | _     | _                 | —      | —<br>—    | -        |        | —       | —      | —          |           |           |          | DDR<6:0>  |          |         |          | 0000       |

| 3098               | USB              | 31:16     | _     |                   | 1      | i         | HUBPRT<6 | 1      | 1       | 1      | MULTTRAN   |           |           |          | BADD<6:0> |          |         |          | 0000       |

|                    | E3TXA            | 15:0      | -     | —<br>Booot: — uni | —      | _         | —        | -      |         | —      | —          |           |           | TXFA     | DDR<6:0>  |          |         |          | 0000       |

#### TABLE 11\_1. LIGB DECIGTED MAD 1 (CONTINUED)

Legend:  ${\bf x}$  = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Device mode.

Note 1: 2:

Host mode.

Definition for Endpoint 0 (ENDPOINT<3:0> (USBCSR<19:16>) = 0). Definition for Endpoints 1-7 (ENDPOINT<3:0> (USBCSR<19:16>) = 1 through 7). 3: 4:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|---------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | W-0               | W-0               | W-0               | W-0               | W-0                 | W-0               | W-0              | W-0              |  |  |  |

| 31:24        |                   |                   |                   | WDTCLR            | <ey<15:8></ey<15:8> |                   |                  |                  |  |  |  |

| 00.40        | W-0               | W-0               | W-0               | W-0               | W-0                 | W-0               | W-0              | W-0              |  |  |  |

| 23:16        |                   |                   |                   | WDTCLR            | KEY<7:0>            |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | U-0               | U-0               | R-y               | R-y                 | R-y               | R-y              | R-y              |  |  |  |

| 15:8         | 0N <sup>(1)</sup> | —                 | _                 |                   |                     | RUNDIV<4:0        | )>               |                  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0                 | U-0               | U-0              | R/W-0            |  |  |  |

| 7:0          | _                 | —                 |                   | SLPDIV<4:0>       |                     |                   |                  |                  |  |  |  |

#### REGISTER 18-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Legend:           | y = Values set from Configuration bits on POR |                                    |                    |  |  |

|-------------------|-----------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                              | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                              | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-16 WDTCLRKEY<15:0>: Watchdog Timer Clear Key bits To clear the Watchdog Timer to prevent a time-out, software must write the value 0x5743 to these bits using a single 16-bit write.

- bit 15 **ON:** Watchdog Timer Enable bit<sup>(1)</sup>

- 1 = The Watchdog Timer module is enabled

- 0 = The Watchdog Timer module is disabled

- bit 14-13 Unimplemented: Read as '0'

bit 12-8 **RUNDIV<4:0>:** Watchdog Timer Postscaler Value in Run Mode bits In Run mode, these bits are set to the values of the WDTPS<4:0> Configuration bits in DEVCFG1.

- bit 7-6 **Unimplemented:** Read as '0'

- bit 5-1 **SLPDIV<4:0>:** Watchdog Timer Postscaler Value in Sleep Mode bits In Sleep mode, these bits are set to the values of the SWDTPS <4:0> Configuration bits in DEVCFG4.

- bit 0 WDTWINEN: Watchdog Timer Window Enable bit

- 1 = Enable windowed Watchdog Timer

- 0 = Disable windowed Watchdog Timer

- Note 1: This bit only has control when FWDTEN (DEVCFG1<23>) = 0.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------------------|-------------------|------------------|------------------|

|              | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |

| 31:24        |                   | YEAR1             | 0<3:0>            |                   |                                    | YEAR0             | 1<3:0>           |                  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |

| 23:16        |                   | MONTH             | 10<3:0>           |                   | MONTH01<3:0>                       |                   |                  |                  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |

| 15:8         | DAY10<3:0>        |                   |                   |                   | DAY01<3:0>                         |                   |                  |                  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |

| 7:0          | _                 | -                 | _                 |                   | WDAY01<3:0>                        |                   |                  |                  |

|              |                   |                   |                   |                   |                                    |                   |                  |                  |

| Legend:      |                   |                   |                   |                   |                                    |                   |                  |                  |

| R = Read     | able bit          |                   | W = Writable      | e bit             | U = Unimplemented bit, read as '0' |                   |                  |                  |

'0' = Bit is cleared

#### REGISTER 20-4: RTCDATE: REAL-TIME CLOCK DATE VALUE REGISTER

bit 31-28 YEAR10<3:0>: Binary-Coded Decimal Value of Years bits, 10 digits

'1' = Bit is set

bit 27-24 YEAR01<3:0>: Binary-Coded Decimal Value of Years bits, 1 digit

bit 23-20 MONTH10<3:0>: Binary-Coded Decimal Value of Months bits, 10 digits; contains a value from 0 to 1

bit 19-16 **MONTH01<3:0>:** Binary-Coded Decimal Value of Months bits, 1 digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary-Coded Decimal Value of Days bits, 10 digits; contains a value from 0 to 3

bit 11-8 DAY01<3:0>: Binary-Coded Decimal Value of Days bits, 1 digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

-n = Value at POR

bit 3-0 WDAY01<3:0>: Binary-Coded Decimal Value of Weekdays bits,1 digit; contains a value from 0 to 6

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

x = Bit is unknown

| Bit<br>24/16/8/0      | Bit<br>25/17/9/1 | Bit<br>26/18/10/2 | Bit<br>27/19/11/3 | Bit<br>28/20/12/4     | Bit<br>29/21/13/5 | Bit<br>30/22/14/6  | Bit<br>31/23/15/7      | Bit<br>Range |

|-----------------------|------------------|-------------------|-------------------|-----------------------|-------------------|--------------------|------------------------|--------------|

| R/W-0                 | R/W-0            | R/W-0             | R/W-0             | R/W-0                 | R/W-0             | R/W-0              | R/W-0                  | 21.24        |

| FRMCNT<2:0>           |                  |                   | FRMSYPW           | MSSEN                 | FRMPOL            | FRMSYNC            | FRMEN                  | 31:24        |

| R/W-0                 | R/W-0            | U-0               | U-0               | U-0                   | U-0               | U-0                | R/W-0                  | 00.40        |

| ENHBUF <sup>(1)</sup> | SPIFE            | _                 | —                 | —                     | —                 | —                  | MCLKSEL <sup>(1)</sup> | 23:16        |

| R/W-0                 | R/W-0            | R/W-0             | R/W-0             | R/W-0                 | R/W-0             | U-0                | R/W-0                  | 15.0         |

| CKE <sup>(2)</sup>    | SMP              | MODE16            | MODE32            | DISSDO <sup>(4)</sup> | SIDL              | —                  | ON                     | 15:8         |

| R/W-0                 | R/W-0            | R/W-0             | R/W-0             | R/W-0                 | R/W-0             | R/W-0              | R/W-0                  | 7:0          |

| EL<1:0>               | SRXIS            | L<1:0>            | STXISE            | DISSDI <sup>(4)</sup> | MSTEN             | CKP <sup>(3)</sup> | SSEN                   | 7:0          |

|                       |                  |                   |                   |                       | -                 |                    |                        | 7:0          |

#### REGISTER 21-1: SPIxCON: SPI CONTROL REGISTER

#### Legend:

| R = Readable bit  | e bit W = Writable bit |                      | read as '0'        |

|-------------------|------------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set       | '0' = Bit is cleared | x = Bit is unknown |

bit 31 FRMEN: Framed SPI Support bit

- 1 = Framed SPI support is enabled (SSx pin used as FSYNC input/output)

- 0 = Framed SPI support is disabled

- bit 30 **FRMSYNC:** Frame Sync Pulse Direction Control on <u>SSx</u> pin bit (Framed SPI mode only)

- 1 = Frame sync pulse input (Slave mode)

- 0 = Frame sync pulse output (Master mode)

- bit 29 FRMPOL: Frame Sync Polarity bit (Framed SPI mode only)

- 1 = Frame pulse is active-high

- 0 = Frame pulse is active-low

- bit 28 MSSEN: Master Mode Slave Select Enable bit

- 1 = Slave select SPI support enabled. The SS pin is automatically driven during transmission in Master mode. Polarity is determined by the FRMPOL bit.

- 0 = Slave select SPI support is disabled.

- bit 27 FRMSYPW: Frame Sync Pulse Width bit

- 1 = Frame sync pulse is one character wide

- 0 = Frame sync pulse is one clock wide

- bit 26-24 **FRMCNT<2:0>:** Frame Sync Pulse Counter bits. Controls the number of data characters transmitted per pulse. This bit is only valid in Framed mode.

- 111 = Reserved

- 110 = Reserved

- 101 = Generate a frame sync pulse on every 32 data characters

- 100 = Generate a frame sync pulse on every 16 data characters

- 011 = Generate a frame sync pulse on every 8 data characters

- 010 = Generate a frame sync pulse on every 4 data characters

- 001 = Generate a frame sync pulse on every 2 data characters

- 000 = Generate a frame sync pulse on every data character

- bit 23 MCLKSEL: Master Clock Enable bit<sup>(1)</sup> 1 = REFCLKO1 is used by the Baud Rate Generator

- 0 = PBCLK2 is used by the Baud Rate Generator

- bit 22-18 Unimplemented: Read as '0'

- **Note 1:** This bit can only be written when the ON bit = 0. Refer to **Section 44.0** "**Electrical Characteristics**" for maximum clock frequency requirements.

- 2: This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- **3:** When AUDEN = 1, the SPI/I<sup>2</sup>S module functions as if the CKP bit is equal to '1', regardless of the actual value of the CKP bit.

- 4: This bit present for legacy compatibility and is superseded by PPS functionality on these devices (see Section 12.4 "Peripheral Pin Select (PPS)" for more information).

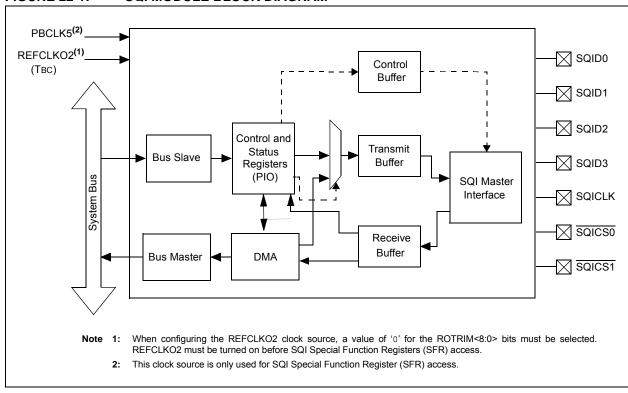

# 22.0 SERIAL QUAD INTERFACE (SQI)

Note: This data sheet summarizes the features of the PIC32MZ Graphics (DA) Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 46. "Serial Quad Interface (SQI)" (DS60001244), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The SQI module is a synchronous serial interface that provides access to serial Flash memories and other serial devices. The SQI module supports Single Lane (identical to SPI), Dual Lane, and Quad Lane modes.

The following are some of the key features of the SQI module:

- · Supports Single, Dual, and Quad Lane modes

- Supports Single Data Rate (SDR) and Double Data Rate (DDR) modes

- Programmable command sequence

- eXecute-In-Place (XIP)

- Data transfer:

- Programmed I/O mode (PIO)

- Buffer descriptor DMA

- Supports SPI Mode 0 and Mode 3

- Programmable Clock Polarity (CPOL) and Clock Phase (CPHA) bits

- Supports up to two Chip Selects

- · Supports up to four bytes of Flash address

- · Programmable interrupt thresholds

- · 32-byte transmit data buffer

- · 32-byte receive data buffer

- 4-word controller buffer

- Note: Once the SQI module is configured, external devices are memory mapped into KSEG2 (see Figure 4-1 through Figure 4-2 in Section 4.0 "Memory Organization" for more information). The MMU must be enabled and the TLB must be set up to access this memory (see Section 50. "CPU for Devices with MIPS32<sup>®</sup> microAptiv<sup>™</sup> and M-Class Cores" (DS60001192) in the "*PIC32* Family Reference Manual" for more information).

#### FIGURE 22-1: SQI MODULE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1          | Bit<br>24/16/8/0 |