Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

ENKEL

| Product Status             | Active                                                                                        |

|----------------------------|-----------------------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                            |

| Speed                      | 200MHz                                                                                        |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, SQI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT                            |

| Number of I/O              | 120                                                                                           |

| Program Memory Size        | 2MB (2M x 8)                                                                                  |

| Program Memory Type        | FLASH                                                                                         |

| EEPROM Size                | -                                                                                             |

| RAM Size                   | 256K x 8                                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                   |

| Data Converters            | A/D 45x12b                                                                                    |

| Oscillator Type            | Internal                                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                             |

| Mounting Type              | Surface Mount                                                                                 |

| Package / Case             | 176-LQFP Exposed Pad                                                                          |

| Supplier Device Package    | 176-LQFP (20x20)                                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2025dah176-i-2j              |

|                            |                                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

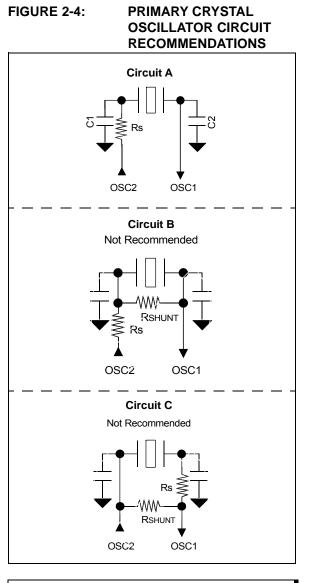

| Note: | For recommended resistor values versus    |

|-------|-------------------------------------------|

|       | crystal/frequency, Refer to the "PIC32MK  |

|       | GP/MC Family Silicon Errata and Data      |

|       | Sheet Clarification" (DS80000737), which  |

|       | is available for download from the Micro- |

|       | chip web site (www.microchip.com).        |

# 2.8 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

#### REGISTER 4-12: SBTxRDy: SYSTEM BUS TARGET 'x' REGION 'y' READ PERMISSIONS REGISTER ('x' = 0-13; 'y' = 0-8)

|              |                   | ,                 | x = • •••,        | , = • •,          |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 |                   | -                 | _                 | _                 | _                 |                  | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 |                   | _                 | _                 | _                 | _                 | _                | _                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-1             | R/W-1            | R/W-1            |

| 7:0          |                   |                   |                   |                   | GROUP3            | GROUP2            | GROUP1           | GROUP0           |

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

|-------------------|------------------|------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

### bit 31-4 Unimplemented: Read as '0'

bit 3 Group3: Group3 Read Permissions bits 1 = Privilege Group 3 has read permission 0 = Privilege Group 3 does not have read permission bit 2 Group2: Group2 Read Permissions bits 1 = Privilege Group 2 has read permission 0 = Privilege Group 2 does not have read permission Group1: Group1 Read Permissions bits bit 1 1 = Privilege Group 1 has read permission 0 = Privilege Group 1 does not have read permission bit 0 Group0: Group0 Read Permissions bits 1 = Privilege Group 0 has read permission 0 = Privilege Group 0 does not have read permission Note 1: Refer to Table 4-8 for the list of available targets and their descriptions.

Refer to rable 4-5 for the list of available targets and their descriptions.

For some target regions, certain bits in this register are read-only with preset values. See Table 4-8 for more information.

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 24.24        | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 31:24        | 31:24 CHPIGN<7:0    |                   |                   |                   |                   |                   |                  |                       |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 23:16        | _                   | _                 | —                 | _                 | —                 | _                 | _                | —                     |

| 45.0         | R/W-0               | U-0               | R/W-0             | U-0               | R/W-0             | U-0               | U-0              | R/W-0                 |

| 15:8         | CHBUSY              | _                 | CHIPGNEN          | —                 | CHPATLEN          | _                 | _                | CHCHNS <sup>(1)</sup> |

| 7.0          | R/W-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R-0               | R/W-0            | R/W-0                 |

| 7:0          | CHEN <sup>(2)</sup> | CHAED             | CHCHN             | CHAEN             | _                 | CHEDET            | CHPF             | RI<1:0>               |

# REGISTER 10-7: DCHxCON: DMA CHANNEL x CONTROL REGISTER

#### Legend:

| Logonan           |                               |                      |                    |

|-------------------|-------------------------------|----------------------|--------------------|

| R = Readable bit  | Readable bit W = Writable bit |                      | read as '0'        |

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared | x = Bit is unknown |

# bit 31-24 CHPIGN<7:0>: Channel Register Data bits

Pattern Terminate mode:

Any byte matching these bits during a pattern match may be ignored during the pattern match determination when the CHPIGNEN bit is set. If a byte is read that is identical to this data byte, the pattern match logic will treat it as a "don't care" when the pattern matching logic is enabled and the CHPIGEN bit is set.

### bit 23-16 Unimplemented: Read as '0'

- bit 15 CHBUSY: Channel Busy bit

- 1 = Channel is active or has been enabled

- 0 = Channel is inactive or has been disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **CHPIGNEN:** Enable Pattern Ignore Byte bit

- 1 = Treat any byte that matches the CHPIGN<7:0> bits as a "don't care" when pattern matching is enabled

0 = Disable this feature

- bit 12 Unimplemented: Read as '0'

- bit 11 CHPATLEN: Pattern Length bit

- 1 = 2 byte length

- 0 = 1 byte length

- bit 10-9 **Unimplemented:** Read as '0'

## bit 8 **CHCHNS:** Chain Channel Selection bit<sup>(1)</sup>

- 1 = Chain to channel lower in natural priority (CH1 will be enabled by CH2 transfer complete)

- 0 = Chain to channel higher in natural priority (CH1 will be enabled by CH0 transfer complete)

- CHEN: Channel Enable bit<sup>(2)</sup>

- 1 = Channel is enabled

bit 7

- 0 = Channel is disabled

- bit 6 CHAED: Channel Allow Events If Disabled bit

- 1 = Channel start/abort events will be registered, even if the channel is disabled

- 0 = Channel start/abort events will be ignored if the channel is disabled

- bit 5 CHCHN: Channel Chain Enable bit

- 1 = Allow channel to be chained

- 0 = Do not allow channel to be chained

- Note 1: The chain selection bit takes effect when chaining is enabled (i.e., CHCHN = 1).

- 2: When the channel is suspended by clearing this bit, the user application should poll the CHBUSY bit (if available on the device variant) to see when the channel is suspended, as it may take some clock cycles to complete a current transaction before the channel is suspended.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                 | _                 | —                 | -                 | _                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | _                 | _                 | -                 | —                 | _                 | -                | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | 15:8 CHPDAT<15:8> |                   |                   |                   |                   |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHPDAT            | [<7:0>            |                   |                  |                  |

# REGISTER 10-18: DCHxDAT: DMA CHANNEL x PATTERN DATA REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 **CHPDAT<15:0>:** Channel Data Register bits <u>Pattern Terminate mode:</u> Data to be matched must be stored in this register to allow terminate on match.

> All other modes: Unused.

# REGISTER 11-7: USBIE0CSR3: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 3 (ENDPOINT 0)

|              |                   |                   | ,                 |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | R-x               | R-x               | R-0               | R-x               | R-x               | R-x               | R-1              | R-0              |

| 31.24        | MPRXEN            | MPTXEN            | BIGEND            | HBRXEN            | HBTXEN            | DYNFIFOS          | SOFTCONE         | UTMIDWID         |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | -                 | -                 |                   | —                 | —                 | —                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         |                   |                   |                   |                   | _                 | _                 | _                | _                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7.0          | _                 | _                 | _                 | _                 | _                 | _                 | —                | _                |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

| bit 31 | MPRXEN: Automatic Amalgamation Option bit |

|--------|-------------------------------------------|

|--------|-------------------------------------------|

- 1 = Automatic amalgamation of bulk packets is done

- 0 = No automatic amalgamation

- bit 30 MPTXEN: Automatic Splitting Option bit

- 1 = Automatic splitting of bulk packets is done

- 0 = No automatic splitting

- bit 29 BIGEND: Byte Ordering Option bit

- 1 = Big Endian ordering

- 0 = Little Endian ordering

- bit 28 HBRXEN: High-bandwidth RX ISO Option bit

1 = High-bandwidth RX ISO endpoint support is selected

0 = No High-bandwidth RX ISO support

- bit 27 **HBTXEN:** High-bandwidth TX ISO Option bit 1 = High-bandwidth TX ISO endpoint support is selected 0 = No High-bandwidth TX ISO support

- bit 26 **DYNFIFOS:** Dynamic FIFO Sizing Option bit

- 1 = Dynamic FIFO sizing is supported

- 0 = No Dynamic FIFO sizing

- bit 25 SOFTCONE: Soft Connect/Disconnect Option bit

- 1 = Soft Connect/Disconnect is supported

- 0 = Soft Connect/Disconnect is not supported

- bit 24 UTMIDWID: UTMI+ Data Width Option bit Always '0', indicating 8-bit UTMI+ data width

- bit 23-0 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | _                 | _                 | _                 | —                 | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | _                 | _                 | _                 | —                 | _                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | —                 | —                 | —                 | —                 | —                 | DMABRS            | STM<1:0>         | DMAERR           |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   | DMAE              | P<3:0>            |                   | DMAIE             | DMAMODE           | DMADIR           | DMAEN            |

#### **REGISTER 11-21: USBDMAxC: USB DMA CHANNEL 'x' CONTROL REGISTER ('x' = 1-8)**

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-11 Unimplemented: Read as '0'

- bit 10-9 DMABRSTM<1:0>: DMA Burst Mode Selection bit

- 11 = Burst Mode 3: INCR16, INCR8, INCR4 or unspecified length

- 10 = Burst Mode 2: INCR8, INCR4 or unspecified length

- 01 = Burst Mode 1: INCR4 or unspecified length

- 00 = Burst Mode 0: Bursts of unspecified length

#### bit 8 DMAERR: Bus Error bit

- 1 = A bus error has been observed on the input

- 0 = The software writes this to clear the error

- bit 7-4 DMAEP<3:0>: DMA Endpoint Assignment bits

These bits hold the endpoint that the DMA channel is assigned to. Valid values are 0-7.

#### bit 3 DMAIE: DMA Interrupt Enable bit

- 1 = Interrupt is enabled for this channel

- 0 = Interrupt is disabled for this channel

- bit 2 DMAMODE: DMA Transfer Mode bit

- 1 = DMA Mode1 Transfers

- 0 = DMA Mode0 Transfers

- bit 1 DMADIR: DMA Transfer Direction bit

- 1 = DMA Read (TX endpoint)

- 0 = DMA Write (RX endpoint)

#### bit 0 DMAEN: DMA Enable bit

- 1 = Enable the DMA transfer and start the transfer

- 0 = Disable the DMA transfer

NOTES:

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24     |                   | _                 |                   | —                 | —                 | -                 | —                | —                |

| 23:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10     |                   | _                 |                   | —                 | —                 | -                 | —                | —                |

| 15:8      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6      |                   | _                 |                   | —                 | —                 | -                 | —                | —                |

| 7.0       | R-0, HC           | R-0, HC           | R-0, HC           | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R-0              |

| 7:0       | BAD1              | BAD2              | DMTEVENT          |                   |                   |                   |                  | WINOPN           |

# REGISTER 17-4: DMTSTAT: DEADMAN TIMER STATUS REGISTER

| Legend:                                     | HC = Cleared by Hardware |                                       |

|---------------------------------------------|--------------------------|---------------------------------------|

| R = Readable bit                            | W = Writable bit         | U = Unimplemented bit                 |

| -n = Bit Value at POR: ('0', '1', x = unkno | own)                     | P = Programmable bit r = Reserved bit |

| bit 31-8 | Unimplemented: Read as '0'                                                                                                          |

|----------|-------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | BAD1: Bad STEP1<7:0> Value Detect bit                                                                                               |

|          | 1 = Incorrect STEP1<7:0> value was detected<br>0 = Incorrect STEP1<7:0> value was not detected                                      |

| bit 6    | BAD2: Bad STEP2<7:0> Value Detect bit                                                                                               |

|          | 1 = Incorrect STEP2<7:0> value was detected                                                                                         |

|          | 0 = Incorrect STEP2<7:0> value was not detected                                                                                     |

| bit 5    | DMTEVENT: Deadman Timer Event bit                                                                                                   |

|          | 1 = Deadman timer event was detected (counter expired or bad STEP1<7:0> or STEP2<7:0> value was entered prior to counter increment) |

|          | 0 = Deadman timer event was not detected                                                                                            |

| bit 4-1  | Unimplemented: Read as '0'                                                                                                          |

| bit 0    | WINOPN: Deadman Timer Clear Window bit                                                                                              |

|          | 1 = Deadman timer clear window is open                                                                                              |

|          | 0 = Deadman timer clear window is not open                                                                                          |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        |                   | _                 | _                 | —                 | —                 | _                 | _                | —                |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 23:16        | MONTH10<3:0>      |                   |                   |                   | MONTH01<3:0>      |                   |                  |                  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 15:8         | DAY10<1:0>        |                   |                   |                   | DAY01<3:0>        |                   |                  |                  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 7:0          | _                 | _                 |                   |                   | WDAY01<3:0>       |                   |                  |                  |  |

# REGISTER 20-6: ALRMDATE: ALARM DATE VALUE REGISTER

# Legend:

| Legenu.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-24 Unimplemented: Read as '0'

bit 23-20 MONTH10<3:0>: Binary Coded Decimal value of months bits, 10 digits; contains a value from 0 to 1

bit 19-16 MONTH01<3:0>: Binary Coded Decimal value of months bits, 1 digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary Coded Decimal value of days bits, 10 digits; contains a value from 0 to 3

bit 11-8 DAY01<3:0>: Binary Coded Decimal value of days bits, 1 digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

bit 3-0 WDAY01<3:0>: Binary Coded Decimal value of weekdays bits, 1 digit; contains a value from 0 to 6

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 04.04        | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 31:24        | _                 | _                 | SDRCMD            | DDRDATA           | DDRDUMMY          | DDRMODE           | DDRADDR          | DDRCMD <sup>(1)</sup> |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 23:16        | DUMMYBYTES<2:0>   |                   |                   | A                 | DDRBYTES<2:       | READOPCODE<7:6>   |                  |                       |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 15:8         | READOPCODE<5:0>   |                   |                   |                   |                   | TYPEDATA<1:0>     |                  |                       |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 7:0          | TYPEDUN           | /IMY<1:0>         | TYPEMO            | DE<1:0>           | TYPEAD            | DR<1:0>           | TYPEC            | MD<1:0>               |

#### REGISTER 22-1: SQI1XCON1: SQI XIP CONTROL REGISTER 1

# Legend:

| Legena.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

### bit 31-30 Unimplemented: Read as '0'

| bit 29    | SDRCMD: SQI Command in SDR Mode bit                                                                                                                                                                                                                                           |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | <ul> <li>1 = SQI command is in SDR mode and SQI data is in DDR mode</li> <li>0 = SQI command is in DDR mode and SQI data is in DDR mode</li> </ul>                                                                                                                            |

| bit 28    | DDRDATA: SQI Data DDR Mode bit                                                                                                                                                                                                                                                |

|           | <ul><li>1 = SQI data bytes are transferred in DDR mode</li><li>0 = SQI data bytes are transferred in SDR mode</li></ul>                                                                                                                                                       |

| bit 27    | DDRDUMMY: SQI Dummy DDR Mode bit                                                                                                                                                                                                                                              |

|           | <ul><li>1 = SQI dummy bytes are transferred in DDR mode</li><li>0 = SQI dummy bytes are transferred in SDR mode</li></ul>                                                                                                                                                     |

| bit 26    | DDRMODE: SQI DDR Mode bit                                                                                                                                                                                                                                                     |

|           | <ul><li>1 = SQI mode bytes are transferred in DDR mode</li><li>0 = SQI mode bytes are transferred in SDR mode</li></ul>                                                                                                                                                       |

| bit 25    | DDRADDR: SQI Address Mode bit                                                                                                                                                                                                                                                 |

|           | <ul><li>1 = SQI address bytes are transferred in DDR mode</li><li>0 = SQI address bytes are transferred in SDR mode</li></ul>                                                                                                                                                 |

| bit 24    | DDRCMD: SQI DDR Command Mode bit <sup>(1)</sup>                                                                                                                                                                                                                               |

|           | <ul> <li>1 = SQI command bytes are transferred in DDR mode</li> <li>0 = SQI command bytes are transferred in SDR mode</li> </ul>                                                                                                                                              |

| bit 23-21 | DUMMYBYTES<2:0>: Transmit Dummy Bytes bits                                                                                                                                                                                                                                    |

|           | 111 = Transmit seven dummy bytes after the address bytes                                                                                                                                                                                                                      |

|           | •                                                                                                                                                                                                                                                                             |

|           | •                                                                                                                                                                                                                                                                             |

|           | <ul> <li>011 = Transmit three dummy bytes after the address bytes</li> <li>010 = Transmit two dummy bytes after the address bytes</li> <li>001 = Transmit one dummy bytes after the address bytes</li> <li>000 = Transmit zero dummy bytes after the address bytes</li> </ul> |

Note 1: When DDRCMD is set to '0', the SQI module will ignore the value in the SDRCMD bit.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | CSADDR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | CSADDR<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 7:0          | —                 | —                 |                   |                   |                   |                   | _                |                  |  |  |

|              |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

# **REGISTER 26-1:** EBICSX: EXTERNAL BUS INTERFACE CHIP SELECT REGISTER ('x' = 0-3)

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-16 CSADDR<15:0>: Base Address for Device bits

Address in physical memory, which will select the external device.

bit 15-0 Unimplemented: Read as '0'

Table 27-12 shows the Security Association control word structure.

The Crypto Engine fetches different structures for different flows and ensures that hardware fetches minimum words from SA required for processing. The structure is ready for hardware optimal data fetches.

| Bit<br>Range | Bit<br>31/23/15/7              | Bit<br>30/22/14/6                                                                                                                                                                                                                                | Bit<br>29/21/13/5             | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31-24        |                                |                                                                                                                                                                                                                                                  | VERIFY                        |                   | NO_RX             | OR_EN             | ICVONLY          | IRFLAG           |  |  |

| 23-16        | LNC                            | LOADIV                                                                                                                                                                                                                                           | FB                            | FLAGS             | _                 |                   | _                | ALGO<6>          |  |  |

| 15-8         |                                |                                                                                                                                                                                                                                                  | ALGO                          | <5:0>             |                   |                   | ENC              | KEY<br>SIZE<1>   |  |  |

| 7-0          | KEY<br>SIZE<0>                 | ML                                                                                                                                                                                                                                               | ILTITASK<2:                   | 0>                |                   | CRYPTOALGO<3:0>   |                  |                  |  |  |

| bit 31-30    | Reserved:                      | Do not use                                                                                                                                                                                                                                       |                               |                   |                   |                   |                  |                  |  |  |

| bit 29       | 1 = NIST pr                    | ERIFY: NIST Procedure Verification Setting<br>= NIST procedures are to be used<br>= Do not use NIST procedures                                                                                                                                   |                               |                   |                   |                   |                  |                  |  |  |

| bit 28       | Reserved:                      | Do not use                                                                                                                                                                                                                                       |                               |                   |                   |                   |                  |                  |  |  |

| bit 27       |                                | ceive DMA C<br>lculate ICV fo<br>processing                                                                                                                                                                                                      | -                             | -                 | ons               |                   |                  |                  |  |  |

| bit 26       |                                | R Register Bits<br>register bits w<br>processing                                                                                                                                                                                                 |                               | -                 | ne CSR regis      | ster              |                  |                  |  |  |

| bit 25       | This affects<br>1 = Only thr   | <b>ICVONLY:</b> Incomplete Check Value Only Flag<br>This affects the SHA-1 algorithm only. It has no effect on the AES algorithm.<br>1 = Only three words of the HMAC result are available<br>0 = All results from the HMAC result are available |                               |                   |                   |                   |                  |                  |  |  |

| bit 24       | This bit is se<br>1 = Save the | nmediate Res<br>et when the in<br>e immediate r<br>save the imme                                                                                                                                                                                 | nmediate res<br>esult for has | ult for hashir    | ng is request     | ed.               |                  |                  |  |  |

| bit 23       | 1 = Load a                     | New Keys Se<br>new set of key<br>oad new keys                                                                                                                                                                                                    | ys for encryp                 | tion and auth     | nentication       |                   |                  |                  |  |  |

| bit 22       | LOADIV: Lo                     | oad IV Setting<br>e IV from this                                                                                                                                                                                                                 |                               | ociation          |                   |                   |                  |                  |  |  |

| bit 21       | This bit indic<br>1 = Indicate | <ul> <li>B: First Block Setting</li> <li>This bit indicates that this is the first block of data to feed the IV value.</li> <li>Indicates this is the first block of data</li> <li>Indicates this is not the first block of data</li> </ul>      |                               |                   |                   |                   |                  |                  |  |  |

| bit 20       | 1 = Security                   | coming/Outgo<br>Association i<br>Association i                                                                                                                                                                                                   | is associated                 | with an outg      |                   |                   |                  |                  |  |  |

| hit 10 17    | Reserved:                      | Do not use                                                                                                                                                                                                                                       |                               |                   |                   |                   |                  |                  |  |  |

# FIGURE 27-12: FORMAT OF SA\_CTRL

## **REGISTER 31-14: ETHIRQ: ETHERNET CONTROLLER INTERRUPT REQUEST REGISTER**

| bit 7   | RXDONE: Receive Done Interrupt bit <sup>(2)</sup>                                                                                                                                                                                                   |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = RX packet was successfully received</li> <li>0 = No interrupt pending</li> </ul>                                                                                                                                                       |

|         | This bit is set whenever an RX packet is successfully received. It is cleared by either a Reset or CPU write of a '1' to the CLR register.                                                                                                          |

| bit 6   | PKTPEND: Packet Pending Interrupt bit <sup>(2)</sup>                                                                                                                                                                                                |

|         | <ul> <li>1 = RX packet pending in memory</li> <li>0 = RX packet is not pending in memory</li> </ul>                                                                                                                                                 |

|         | This bit is set when the BUFCNT counter has a value other than '0'. It is cleared by either a Reset or by writing the BUFCDEC bit to decrement the BUFCNT counter. Writing a '0' or a '1' has no effect.                                            |

| bit 5   | <b>RXACT:</b> Receive Activity Interrupt bit <sup>(2)</sup>                                                                                                                                                                                         |

|         | <ul> <li>1 = RX packet data was successfully received</li> <li>0 = No interrupt pending</li> </ul>                                                                                                                                                  |

|         | This bit is set whenever RX packet data is stored in the RXBM FIFO. It is cleared by either a Reset or CPU write of a '1' to the CLR register.                                                                                                      |

| bit 4   | Unimplemented: Read as '0'                                                                                                                                                                                                                          |

| bit 3   | <b>TXDONE:</b> Transmit Done Interrupt bit <sup>(2)</sup>                                                                                                                                                                                           |

|         | 1 = TX packet was successfully sent<br>0 = No interrupt pending                                                                                                                                                                                     |

|         | This bit is set when the currently transmitted TX packet completes transmission, and the Transmit Status Vector is loaded into the first descriptor used for the packet. It is cleared by either a Reset or CPU write of a '1' to the CLR register. |

| bit 2   | TXABORT: Transmit Abort Condition Interrupt bit <sup>(2)</sup>                                                                                                                                                                                      |

|         | <ul> <li>1 = TX abort condition occurred on the last TX packet</li> <li>0 = No interrupt pending</li> </ul>                                                                                                                                         |

|         | This bit is set when the MAC aborts the transmission of a TX packet for one of the following reasons:                                                                                                                                               |

|         | Jumbo TX packet abort                                                                                                                                                                                                                               |

|         | Underrun abort                                                                                                                                                                                                                                      |

|         | Excessive defer abort                                                                                                                                                                                                                               |

|         | Late collision abort                                                                                                                                                                                                                                |

|         | Excessive collisions abort                                                                                                                                                                                                                          |

|         | This bit is cleared by either a Reset or CPU write of a '1' to the CLR register.                                                                                                                                                                    |

| bit 1   | <b>RXBUFNA:</b> Receive Buffer Not Available Interrupt bit <sup>(2)</sup>                                                                                                                                                                           |

|         | <ul> <li>1 = RX Buffer Descriptor Not Available condition has occurred</li> <li>0 = No interrupt pending</li> </ul>                                                                                                                                 |

|         | This bit is set by a RX Buffer Descriptor Overrun condition. It is cleared by either a Reset or a CPU write of a '1' to the CLR register.                                                                                                           |

| bit 0   | RXOVFLW: Receive FIFO Over Flow Error bit <sup>(2)</sup>                                                                                                                                                                                            |

|         | <ul> <li>1 = RX FIFO Overflow Error condition has occurred</li> <li>0 = No interrupt pending</li> </ul>                                                                                                                                             |

|         | RXOVFLW is set by the RXBM Logic for an RX FIFO Overflow condition. It is cleared by either a Reset or CPU write of a '1' to the CLR register.                                                                                                      |

| Note 1: | This bit is only used for TX operations.                                                                                                                                                                                                            |

| 2:      | This bit is are only used for RX operations.                                                                                                                                                                                                        |

**Note:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | IRQCON            | _                 | _                 | _                 | —                 | _                 | —                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | _                 | —                 | -                 | —                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         |                   | —                 | _                 | _                 | —                 | _                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 | —                 | _                 | HSYNCINT         | VSYNCINT         |

# REGISTER 36-15: GLCDINT: GRAPHICS LCD CONTROLLER INTERRUPT REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

- bit 31 **IRQCON:** IRQ Triggering Control bit 1 = Edge triggering is enabled 0 = Level triggering is enabled

- bit 30-2 Unimplemented: Read as '0'

- bit 1 **HYSNNCINT:** HSYNC Interrupt Enable bit 1 = HSYNC interrupt is enabled

- 0 = HSYNC interrupt is not enabled

- bit 0 VSYNCINT: VSYNC Interrupt Enable bit 1 = VSYNC interrupt is enabled

- 0 = VSYNC interrupt is not enabled

# REGISTER 36-17: GLCDCLUTx: GRAPHICS LCD CONTROLLER GLOBAL COLOR LOOKUP TABLE REGISTER x ('x'=0-255)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        |                   | _                 | _                 | _                 | _                 | -                 | —                | _                |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | RED<7:0>          |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | GREEN<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | BLUE<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |   |  |  |

|-------------------|------------------|------------------------------------|--------------------|---|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown | l |  |  |

bit 31-24 Unimplemented: Read as '0'

bit 23-16 **RED<7:0>:** Global Color Lookup Table Red Component bits

bit 15-8 GREEN<7:0>: Global Color Lookup Table Green Component bits

bit 7-0 BLUE<7:0>: Global Color Lookup Table Blue Component bits

# TABLE 38-1: DDR SDRAM CONTROLLER REGISTER SUMMARY (CONTINUED)

|                             | SLE 38-1:        | Bits          |                               |            |       |               |             |         |               |      | 1                       |         |         |         |               |               |           |               |            |

|-----------------------------|------------------|---------------|-------------------------------|------------|-------|---------------|-------------|---------|---------------|------|-------------------------|---------|---------|---------|---------------|---------------|-----------|---------------|------------|

| Virtual Address<br>(BF8E_#) | Register<br>Name | Bit Range     | 31/15                         | 30/14      | 29/13 | 28/12         | 27/11       | 26/10   | 25/9          | 24/8 | 23/7                    | 22/6    | 21/5    | 20/4    | 19/3          | 18/2          | 17/1      | 16/0          | All Resets |

| 8048                        | DDR<br>CMDISSUE  | 31:16         |                               | —          | —     | -             | —           | —       | —             |      |                         | —       | —       | -       |               | —             | —         |               | 0000       |

|                             | DDR              | 15:0<br>31:16 | _                             |            |       |               |             |         |               |      | —                       | _       |         | VALID   | _             | NUMHOS I      | CMDS<3:0> | ODTWEN        | 0000       |

| 804C                        | ODTENCFG         | 15:0          |                               |            |       |               |             |         | _             |      |                         |         |         |         |               |               |           | ODTWEN        | 0000       |

|                             | DDR              | 31:16         | —                             | —          | —     | —             | —           | —       | —             | —    | —                       | —       | —       | _       | —             | —             | —         | —             | 0000       |

| 8050                        | MEMWIDTH         | 15:0          | —                             | -          | —     | —             | -           | -       | —             | —    | -                       | —       | —       | —       | HALF<br>RATE  | —             | -         | —             | 0000       |

|                             | DDR              | 31:16         |                               | •          |       | MDALC         | MD<7:0>     |         |               |      | WEN<br>CMD2             | CASCMD2 | RASCMD2 |         | . (           | CSCMD2<7:     | 3>        | •             | 0000       |

| 8080                        | DDR<br>CMD10     | 15:0          | (                             | CSCMD2<2:  | 0>    | CLKEN<br>CMD2 | WEN<br>CMD1 | CASCMD1 | RASCMD1       |      |                         |         | CSCME   | )1<7:0> |               |               |           | CLKEN<br>CMD1 | 0000       |

|                             | DDR              | 31:16         |                               |            |       | MDALC         | MD<7:0>     |         |               |      | WEN<br>CMD2             | CASCMD2 | RASCMD2 |         | (             | CSCMD2<7:     | }>        |               | 0000       |

| 8084                        | DDR<br>CMD11     | 15:0          | C                             | CSCMD2<2:  | 0>    | CLKEN<br>CMD2 | WEN<br>CMD1 | CASCMD1 | RASCMD1       |      | CSCMD1<7:0>             |         |         |         | CLKEN<br>CMD1 |               |           |               |            |

|                             | DDR              | 31:16         |                               |            |       | MDALC         | MD<7:0>     |         |               |      | WEN<br>CMD2             | CASCMD2 | RASCMD2 |         | (             | CSCMD2<7:     | }>        |               | 0000       |

| 8088                        | DDR<br>CMD12     | 15:0          |                               |            |       |               |             |         | CLKEN<br>CMD1 | 0000 |                         |         |         |         |               |               |           |               |            |

|                             | DDR              | 31:16         |                               |            |       | MDALC         | MD<7:0>     |         | 1             |      | WEN<br>CMD2             | CASCMD2 | RASCMD2 |         | (             | CSCMD2<7:     | 3>        | -             | 0000       |

| 808C                        | DDR<br>CMD13     | 15:0          | CSCMD2<2:0> CLKEN WEN CASCMD1 |            |       |               |             | RASCMD1 |               |      |                         |         |         |         |               | CLKEN<br>CMD1 | 0000      |               |            |

|                             | DDR              | 31:16         |                               |            |       | MDALC         | MD<7:0>     |         |               |      | WEN<br>CMD2             | CASCMD2 | RASCMD2 |         | (             | CSCMD2<7:     | 3>        |               | 0000       |

| 8090                        | DDR<br>CMD14     | 15:0          | C                             | CSCMD2<2:  | 0>    | CLKEN<br>CMD2 | WEN<br>CMD1 | CASCMD1 | RASCMD1       |      | CSCMD1<7:0> CLKE<br>CME |         |         |         |               | CLKEN<br>CMD1 | 0000      |               |            |

|                             | DDR              | 31:16         |                               |            |       |               | MD<7:0>     | I       |               |      | WEN<br>CMD2             | CASCMD2 | RASCMD2 |         | (             | CSCMD2<7:     | }>        |               | 0000       |

| 8094                        | DDR<br>CMD15     | 15:0          | C                             | CSCMD2<2:  | 0>    | CLKEN<br>CMD2 | WEN<br>CMD1 | CASCMD1 | RASCMD1       |      |                         |         | CSCME   | )1<7:0> |               |               |           | CLKEN<br>CMD1 | 0000       |

|                             | DDR              | 31:16         |                               |            |       | MDALC         | MD<7:0>     |         |               |      | WEN<br>CMD2             | CASCMD2 | RASCMD2 |         | (             | CSCMD<27:     | }>        |               | 0000       |

| 8098                        | DDR<br>CMD16     | 15:0          | C                             | CSCMD2<2:  | 0>    | CLKEN<br>CMD2 | WEN<br>CMD1 | CASCMD1 | RASCMD1       |      |                         |         | CSCME   | )1<7:0> |               |               |           | CLKEN<br>CMD1 | 0000       |

|                             | DDR              | 31:16         |                               |            |       | MDALC         | MD<7:0>     |         |               |      | WEN<br>CMD2             | CASCMD2 | RASCMD2 |         | (             | CSCMD2<7:     | }>        |               | 0000       |

| 809C                        | DDR<br>CMD17     | 15:0          | (                             | CSCMD2<2:0 | 0>    | CLKEN<br>CMD2 | WEN<br>CMD1 | CASCMD1 | RASCMD1       |      | 1                       |         | CSCME   | )1<7:0> |               |               |           | CLKEN<br>CMD1 | 0000       |

| 00.4.0                      | DDR              | 31:16         |                               |            |       | MDALC         | MD<7:0>     | 1       | 11            |      | WEN<br>CMD2             | CASCMD2 | RASCMD2 |         | (             | CSCMD2<7:     | 3>        |               | 0000       |

| 80A0                        | DDR<br>CMD18     | 15:0          | C                             | CSCMD2<2:0 | 0>    | CLKEN<br>CMD2 | WEN<br>CMD1 | CASCMD1 | RASCMD1       |      |                         |         | CSCME   | 01<7:0> |               |               |           | CLKEN<br>CMD1 | 0000       |

|                             | DDR              | 31:16         |                               |            |       | MDALC         | MD<7:0>     | 1       | 11            |      | WEN<br>CMD2             | CASCMD2 | RASCMD2 |         | (             | CSCMD2<7:     | 3>        |               | 0000       |

| 80A4                        | DDR<br>CMD19     | 15:0          | C                             | CSCMD2<2:0 | 0>    | CLKEN<br>CMD2 | WEN<br>CMD1 | CASCMD1 | RASCMD1       |      |                         |         | CSCME   | 01<7:0> |               |               |           | CLKEN<br>CMD1 | 0000       |

© 2015-2018 Microchip Technology Inc.

DS60001361F-page 615

## REGISTER 41-3: DEVCFG0/ADEVCFG0: DEVICE/ALTERNATE DEVICE CONFIGURATION WORD 0 (CONTINUED)

- bit 10 **FSLEEP:** Flash Sleep Mode bit

- 1 = Flash is powered down when the device is in Sleep mode

- 0 = Flash power down is controlled by the VREGS bit (PWRCON<0>)

- bit 9-8 FECCCON<1:0>: Dynamic Flash ECC Configuration bits

- 11 = ECC and dynamic ECC are disabled (ECCCON<1:0> bits are writable)

- 10 = ECC and dynamic ECC are disabled (ECCCON<1:0> bits are locked)

- 01 = Dynamic Flash ECC is enabled (ECCCON<1:0> bits are locked)

- 00 = Flash ECC is enabled (ECCCON<1:0> bits are locked; disables word Flash writes)

- **Note:** Upon a device POR, the value of these bits are copied by hardware into CFGCON<5:4> bits, (i.e. ECCCON<1:0>.

- bit 7 Reserved: Write as '1'

- bit 6 BOOTISA: Boot ISA Selection bit

- 1 = Boot code and Exception code is MIPS32

- (ISAONEXC bit is set to '0' and the ISA<1:0> bits are set to '10' in the CP0 Config3 register) 0 = Boot code and Exception code is microMIPS

- (ISAONEXC bit is set to '1' and the ISA<1:0> bits are set to '11' in the CP0 Config3 register)

- bit 5 TRCEN: Trace Enable bit

- 1 = Trace features in the CPU are enabled

- 0 = Trace features in the CPU are disabled

- bit 4-3 ICESEL<1:0>: In-Circuit Emulator/Debugger Communication Channel Select bits

- 11 = PGEC1/PGED1 pair is used

- 10 = PGEC2/PGED2 pair is used

- 01 = PGEC3/PGED3 pair is used

- 00 = Reserved

- bit 2 JTAGEN: JTAG Enable bit

- 1 = JTAG is enabled

- 0 = JTAG is disabled

- Note 1: On Reset, this Configuration bit is copied into JTAGEN (CFGCON<3>). If JTAGEN (DEVCFG0<2>) = 0, the JTAGEN bit cannot be set to '1' by the user application at run-time, as JTAG is always disabled. However, if JTAGEN (DEVCFG0<2>) = 1, the user application may enable/disable JTAG at run-time by simply writing JTAGEN (CFGCON<3> as required.

- 2: This bit sets the value of the JTAGEN bit in the CFGCON register.

- bit 1-0 **DEBUG<1:0>:** Background Debugger Enable bits (forced to '11' if code-protect is enabled)

- 11 = 4-wire JTAG Enabled PGECx/PGEDx Disabled ICD module Disabled

- 10 = 4-wire JTAG Enabled PGECx/PGEDx Disabled ICD module Enabled

- 01 = PGECx/PGEDx Enabled 4-wire JTAG I/F Disabled ICD module Disabled

- 00 = PGECx/PGEDx Enabled 4-wire JTAG I/F Disabled ICD module Enabled

- **Note:** When the FJTAGEN or JTAGEN bits are equal to '0', this prevents 4-wire JTAG debugging, but not PGECx/PGEDx debugging.

| DC CHAR                   | RACTERIS | TICS                                                 | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |      |       |            |  |  |  |

|---------------------------|----------|------------------------------------------------------|-------------------------------------------------------|------|------|-------|------------|--|--|--|

| Param.<br>No.<br>(Note 1) | Symbol   | Characteristics                                      | Min.                                                  | Тур. | Max. | Units | Conditions |  |  |  |

| DDRM12                    | Iddo     | Operating Current, One Bank<br>Active Precharge      |                                                       |      | 90   | mA    | Note 2     |  |  |  |

| DDRM13                    | IDD1     | Operating Current, One Back<br>Active-Read Precharge |                                                       |      | 100  | mA    | Note 2     |  |  |  |

| DDRM14                    | IDD2     | Precharge Power-Down Current                         |                                                       |      | 8    | mA    | Note 3     |  |  |  |

| DDRM15                    | Idd3     | Precharge Stand-by Current                           |                                                       |      | 45   | mA    | Note 2     |  |  |  |

| DDRM16                    | IDD4     | Precharge Quiet Stand-by Current                     |                                                       |      | 35   | mA    | Note 4     |  |  |  |

| DDRM17                    | Idd5     | Active Power-Down Current                            |                                                       |      | 12   | mA    | Note 3     |  |  |  |

| DDRM18                    | IDD6     | Active Stand-by Current                              |                                                       |      | 65   | mA    | Note 2     |  |  |  |

| DDRM19                    | Idd7     | Operating Burst Read Current                         |                                                       |      | 140  | mA    | Note 2     |  |  |  |

| DDRM20                    | IDD8     | Operating Burst Write Current                        | _                                                     | _    | 165  | mA    | Note 2     |  |  |  |

| DDRM21                    | IDD9     | Burst Refresh Current                                | _                                                     | _    | 95   | mA    | Note 2     |  |  |  |

| DDRM22                    | IDD10    | Self-Refresh Current                                 | _                                                     | _    | 6    | mA    | Note 5     |  |  |  |

| DDRM23                    | IDD11    | Operating Bank Interleave Read<br>Current            |                                                       |      | 200  | mA    | Note 6     |  |  |  |

## TABLE 44-17: DC CHARACTERISTICS: DDR2 SDRAM MEMORY

**Note 1:** These parameters are characterized, but not tested in manufacturing. The specifications are only valid after the memory is initialized.

2: DDRCKE is high, DDRCS0 is high between valid commands. Address, control, and data bus inputs are switching.

- 3: DDRCKE is low. Other control and address inputs are stable. Data bus inputs are floating.

- 4: DDRCKE is high and DDRCS0 is high. Other control and address inputs are stable. Data bus inputs are floating.

- 5: DDRCKE is low and DDRCK/DDRCK are low. Other control and address inputs are floating. Data bus inputs are floating.

**6:** DDRCKE is high and DDRCS0 is high between valid commands. Address bus inputs are stable. Data bus inputs are switching.

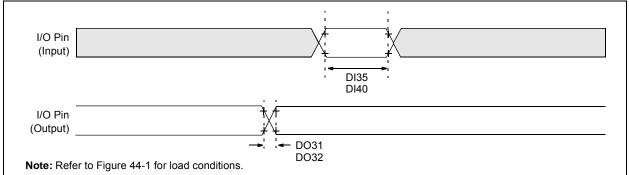

## TABLE 44-30: I/O TIMING REQUIREMENTS

| AC CHAI       | RACTERIS                                                                                                                                                                                                                   | STICS                                                                                                                            | Standard Operating Conditions: VDDIO = 2.2V to 3.6V,VDDCORE = 1.7V to 1.9V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |   |   |      |       |               |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|------|-------|---------------|--|--|

| Param.<br>No. | Symbol                                                                                                                                                                                                                     | Characteris                                                                                                                      | Characteristics <sup>(2)</sup>                                                                                                                                                  |   |   | Max. | Units | Conditions    |  |  |

| DO31          | TIOR                                                                                                                                                                                                                       | Port Output Rise T<br>I/O Pins:<br>4x Source Driver Pir<br>RA3, RA9, RA10, R<br>RB0-7, RB11, RB13<br>RC12-RC15<br>RD0 RD6-RD7 RD | ns -<br>A14, RA15                                                                                                                                                               | _ | _ | 9.5  | ns    | Cload = 50 pF |  |  |

|               |                                                                                                                                                                                                                            | RD0, RD6-RD7, RD11<br>RE8, RE9<br>RF2, RF3, RF8<br>RG15<br>RH0, RH1, RH4-RH6,<br>RJ0-RJ2, RJ8, RJ9, R                            | 6, RH8-RH13                                                                                                                                                                     | _ | _ | 6    | ns    | Cload = 20 pF |  |  |