Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

ENSE

| Product Status             | Active                                                                                        |

|----------------------------|-----------------------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                            |

| Speed                      | 200MHz                                                                                        |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, SQI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT                            |

| Number of I/O              | 120                                                                                           |

| Program Memory Size        | 2MB (2M x 8)                                                                                  |

| Program Memory Type        | FLASH                                                                                         |

| EEPROM Size                | -                                                                                             |

| RAM Size                   | 640K x 8                                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                   |

| Data Converters            | A/D 45x12b                                                                                    |

| Oscillator Type            | Internal                                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                             |

| Mounting Type              | Surface Mount                                                                                 |

| Package / Case             | 176-LQFP Exposed Pad                                                                          |

| Supplier Device Package    | 176-LQFP (20x20)                                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2064dab176-i-2j              |

|                            |                                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 7:PIN NAMES FOR 288-PIN DEVICES

| 288-P              | VIN LFBGA (BOTTOM V                                                                              | IEW)    |                    |                            |

|--------------------|--------------------------------------------------------------------------------------------------|---------|--------------------|----------------------------|

|                    |                                                                                                  | A1      |                    | V1                         |

|                    |                                                                                                  |         |                    | N6                         |

| PI                 | IC32MZ1025DAA288<br>IC32MZ1025DAB288<br>IC32MZ1064DAA288                                         | F6      |                    |                            |

| PI<br>PI<br>PI     | IC32MZ1064DAB288<br>IC32MZ2025DAA288<br>IC32MZ2025DAB288<br>IC32MZ2064DAA288<br>IC32MZ2064DAB288 | F13     |                    | N13<br>V18                 |

|                    |                                                                                                  | A18     |                    |                            |

|                    | Polarity Inc                                                                                     | licator |                    |                            |

| Ball/Pin<br>Number | Full Pin Na                                                                                      | ne      | Ball/Pin<br>Number | Full Pin Name              |

| A1                 | No Connect                                                                                       |         | B17                | AN2/C1INB/RB4              |

| A2                 | DDRUDQS                                                                                          |         | B18                | EBIA5/AN7/PMA5/RA5         |

| A3                 | DDRDM1                                                                                           |         | C1                 | DDRDQ8                     |

| A4                 | D-                                                                                               |         | C2                 | DDRDQ15                    |

| A5                 | Vss                                                                                              |         | C3                 | DDRDQ9                     |

| A6                 | INT0/RH14                                                                                        |         | C4                 | VUSB3V3                    |

| A7                 | RPF2/SDA3/RF2                                                                                    |         | C5                 | VBUS                       |

| A8                 | AN21/RG15                                                                                        |         | C6                 | USBID                      |

| A9                 | AN14/C1IND/SCK2/RG6                                                                              |         | C7                 | Vss                        |

| A10                | TDI/AN17/SCK5/RF13                                                                               |         | C8                 | No Connect                 |

| A11                | TDO/AN31/RPF12/RF12                                                                              |         | C9                 | AN30/C2IND/RPG8/SCL4/RG8   |

| A12                | EBID5/AN12/RPC1/PMD5/RC1                                                                         |         | C10                | AN25/RPE8/RE8              |

| A13                | EBIOE/AN19/RPC4/PMRD/RC4                                                                         |         | C11                | EBID6/AN16/PMD6/RE6        |

| A14                | PGEC1/AN9/RPB1/CTED1/RB1                                                                         |         | C12                | No Connect                 |

| A15                | EBID10/AN4/RPB8/PMD10/RB8                                                                        |         | C13                | EBID12/AN10/RPC2/PMD12/RC2 |

| A16                | AN8/RPB3/RB3                                                                                     |         | C14                | AN49/RB11                  |

| A17                | VREF-/CVREF-/AN27/RA9                                                                            |         | C15                | VREF+/CVREF+/AN28/RA10     |

| A18                | No Connect                                                                                       |         | C16                | VDDIO                      |

| B1                 | No Connect                                                                                       |         | C17                | AN1/C2INB/RPB2/RB2         |

| B2                 | DDRUDQS                                                                                          |         | C18                | AN6/RB12                   |

| B3                 | DDRDQ14                                                                                          |         | D1                 | DDRDQ13                    |

| B4                 | D+                                                                                               |         | D2                 | DDRDQ10                    |

| B5                 | Vss                                                                                              |         | D3                 | VSS1V8                     |

| B6                 | EBID4/AN18/PMD4/RE4                                                                              |         | D4                 | TMS/SDCD/RA0               |

| B7                 | EBID0/PMD0/RE0                                                                                   |         | D5                 | VUSB3V3                    |

| B8                 | AN20/RH4                                                                                         |         | D6                 | No Connect                 |

| B9                 | EBIA2/AN23/C2INC/RPG9/PMA2                                                                       | /RG9    | D7                 | VDDCORE                    |

| B10                | AN26/RPE9/RE9                                                                                    |         | D8                 | EBID1/AN39/PMD1/RE1        |

| B11                | EBID7/AN15/PMD7/RE7                                                                              |         | D9                 | AN13/C1INC/RPG7/SDA4/RG7   |

| B12                | No Connect                                                                                       |         | D10                | Vss                        |

| B13                | EBIWE/AN34/RPC3/PMWR/RC3                                                                         |         | D11                | Vss                        |

|                    |                                                                                                  |         | D40                | Vss                        |

| B14                | PGEC2/RPB6/RB6                                                                                   |         | D12                | V33                        |

| B14<br>B15         | AN48/CTPLS/RB13                                                                                  |         | D12<br>D13         | Vss                        |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 and Table 4 for the available peripherals and 12.4 "Peripheral Pin Select (PPS)" for restrictions.

2: Every I/O port pin (RAx-RKx) can be used as a change notification pin (CNAx-CNKx). See 12.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

4: This pin must be tied to Vss through a 20k  $\Omega$  resistor when DDR is not connected in the system.

5: This pin is a No Connect when DDR is not connected in the system.

6: These pins are restricted to input functions only.

|          |                  | Pin Number        |                  |             | 5.4            |                                                  |

|----------|------------------|-------------------|------------------|-------------|----------------|--------------------------------------------------|

| Pin Name | 169-pin<br>LFBGA | 176-pin<br>LQFP   | 288-pin<br>LFBGA | Pin<br>Type | Buffer<br>Type | Description                                      |

|          |                  |                   | DDR2 S           | SDRAM Co    | ntroller       |                                                  |

| DDRCK    | DDR Internal     | DDR Internal      | K2               | 0           | SSTL           | Differential Clocks                              |

| DDRCK    | to the Package   | to the Package    | K1               | 0           | SSTL           |                                                  |

| DDRCKE   |                  |                   | L2               | 0           | SSTL           | Clock Enable                                     |

| DDRCS0   |                  |                   | N2               | 0           | SSTL           | Chip Select 0                                    |

| DDRRAS   |                  |                   | M1               | 0           | SSTL           | Row Address Strobe                               |

| DDRCAS   |                  |                   | P2               | 0           | SSTL           | Column Address Strobe                            |

| DDRWE    |                  |                   | L1               | 0           | SSTL           | Write Enable Strobe                              |

| DDRLDM   |                  |                   | G3               | 0           | SSTL           | Lower Data Byte Mask                             |

| DDRUDM   |                  |                   | A3               | 0           | SSTL           | Upper Data Byte Mask                             |

| DDRODT   |                  |                   | N1               | 0           | SSTL           | On-Die Termination                               |

| DDRLDQS  |                  |                   | E1               | I/O         | SSTL           | Lower Data Byte Qualifier Strobes (Differential) |

| DDRLDQS  |                  |                   | E2               | I/O         | SSTL           |                                                  |

| DDRUDQS  |                  |                   | B2               | I/O         | SSTL           | Upper Data Byte Qualifier Strobes (Differential) |

| DDRUDQS  |                  |                   | A2               | I/O         | SSTL           |                                                  |

| DDRBA0   |                  |                   | M2               | 0           | SSTL           | Bank Address Select 0                            |

| DDRBA1   |                  |                   | M3               | 0           | SSTL           | Bank Address Select 1                            |

| DDRBA2   |                  |                   | U4               | 0           | SSTL           | Bank Address Select 2                            |

| DDRA0    |                  |                   | R1               | 0           | SSTL           | DDR2 Address Bus                                 |

| DDRA1    |                  |                   | L3               | 0           | SSTL           | -                                                |

| DDRA2    |                  |                   | N3               | 0           | SSTL           |                                                  |

| DDRA3    |                  |                   | R2               | 0           | SSTL           | -                                                |

| DDRA4    |                  |                   | P3               | 0           | SSTL           |                                                  |

| DDRA5    |                  |                   | T1               | 0           | SSTL           |                                                  |

| DDRA6    |                  |                   | U1               | 0           | SSTL           |                                                  |

| DDRA7    |                  |                   | T2               | 0           | SSTL           |                                                  |

| DDRA8    |                  |                   | U2               | 0           | SSTL           |                                                  |

| DDRA9    |                  |                   | R3               | 0           | SSTL           |                                                  |

| DDRA10   | ]                |                   | P1               | 0           | SSTL           |                                                  |

| DDRA11   | ]                |                   | V2               | 0           | SSTL           |                                                  |

| DDRA12   |                  |                   | Т3               | 0           | SSTL           |                                                  |

| DDRA13   |                  |                   | U3               | 0           | SSTL           |                                                  |

| DDRA14   | ]                | ļ [               | T4               | 0           | SSTL           |                                                  |

| DDRA15   |                  | <b>_</b>          | V3               | 0           | SSTL           | ]                                                |

| Legend:  | CMOS = CMOS      | -compatible input | or output        | Analog = A  | nalog input    | P = Power                                        |

#### **TABLE 1-22:** DDR2 SDRAM CONTROLLER PINOUT I/O DESCRIPTIONS

ST = Schmitt Trigger input with CMOS levels O = Output

9.....

I = Input

TTL = Transistor-transistor Logic input buffer PPS = Peripheral Pin Select SSTL = Stub Series Terminated Logic

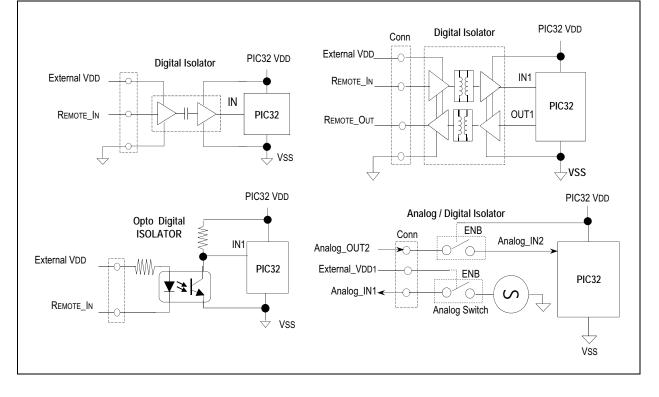

#### TABLE 2-1: EXAMPLES OF DIGITAL/ ANALOG ISOLATORS WITH OPTIONAL LEVEL TRANSLATION

| Example Digital/Analog<br>Signal Isolation Circuits | Inductive Coupling | Capacitive Coupling | Opto Coupling | Analog/Digital Switch |

|-----------------------------------------------------|--------------------|---------------------|---------------|-----------------------|

| ADuM7241 / 40 ARZ (1 Mbps)                          | Х                  |                     |               | _                     |

| ADuM7241 / 40 CRZ (25 Mbps)                         | Х                  | _                   | _             | —                     |

| ISO721                                              | _                  | Х                   | _             | —                     |

| LTV-829S (2 Channel)                                | _                  |                     | Х             | —                     |

| LTV-849S (4 Channel)                                | _                  |                     | Х             | —                     |

| FSA266 / NC7WB66                                    | —                  | —                   | _             | Х                     |

#### FIGURE 2-6:

## EXAMPLE DIGITAL/ANALOG SIGNAL ISOLATION CIRCUITS

## 3.2 Architecture Overview

The MIPS32 microAptiv Microprocessor core in PIC32MZ DA family devices contains several logic blocks working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- Execution unit

- General Purpose Register (GPR)

- Multiply/Divide Unit (MDU)

- System control coprocessor (CP0)

- Memory Management Unit (MMU)

- · Instruction/Data cache controllers

- · Power Management

- Instructions and data caches

- microMIPS support

- Enhanced JTAG (EJTAG) controller

## 3.2.1 EXECUTION UNIT

The processor core execution unit implements a load/ store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation. Seven additional register file shadow sets (containing thirty-two registers) are added to minimize context switching overhead during interrupt/exception processing. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- Load aligner

- Trap condition comparator

- Bypass multiplexers used to avoid stalls when executing instruction streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing arithmetic and bitwise logical operations

- · Shifter and store aligner

- DSP ALU and logic block for performing DSP instructions, such as arithmetic/shift/compare operations

#### 3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

The processor core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations, and DSP ASE multiply instructions. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows MDU operations to be partially masked by system stalls and/or other integer unit instructions.

The high-performance MDU consists of a 32x32 booth recoded multiplier, four pairs of result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x32) represents the *rs* operand. The second number ('32' of 32x32) represents the *rt* operand.

The MDU supports execution of one multiply or multiply-accumulate operation every clock cycle.

Divide operations are implemented with a simple 1-bitper-clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If *rs* is 8 bits wide, 23 iterations are skipped. For a 16-bit wide *rs*, 15 iterations are skipped and for a 24-bit wide *rs*, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation has completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the processor core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

| <b>TABLE 3-1:</b> | MIPS32 microAptiv MICROPROCESSOR CORE HIGH-PERFORMANCE INTEGER |

|-------------------|----------------------------------------------------------------|

|                   | MULTIPLY/DIVIDE UNIT LATENCIES AND REPEAT RATES                |

| Opcode                         | Operand Size (mul <i>rt</i> ) (div <i>rs</i> ) | Latency | Repeat Rate |

|--------------------------------|------------------------------------------------|---------|-------------|

| MULT/MULTU, MADD/MADDU,        | 16 bits                                        | 5       | 1           |

| MSUB/MSUBU (HI/LO destination) | 32 bits                                        | 5       | 1           |

| MUL (GPR destination)          | 16 bits                                        | 5       | 1           |

|                                | 32 bits                                        | 5       | 1           |

| DIV/DIVU                       | 8 bits                                         | 12/14   | 12/14       |

|                                | 16 bits                                        | 20/22   | 20/22       |

|                                | 24 bits                                        | 28/30   | 28/30       |

|                                | 32 bits                                        | 36/38   | 36/38       |

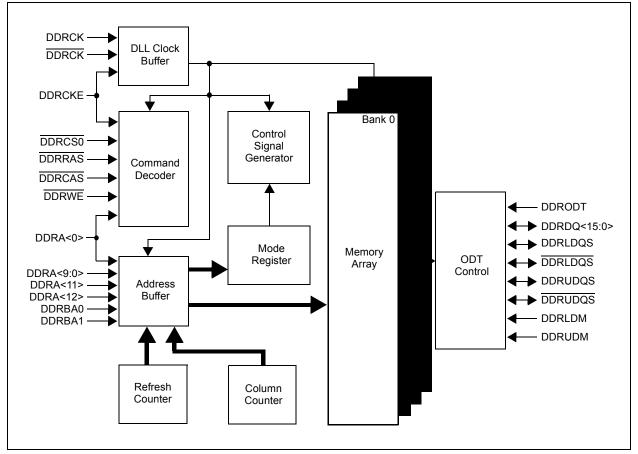

## 4.2 DDR2 SDRAM

Stacked DDR2 SDRAM memory devices support 32 MB of DDR2 SDRAM. Memory in these devices is organized as 4,194,304 x 4 banks x 16 bits. Refer to Figure 4-1 and Table 4-1 for the DDR2 SDRAM address ranges.

#### 4.2.1 FEATURES

The DDR2 SDRAM includes the following features:

- Double Data Rate architecture: two data transfers per clock cycle

- · CAS Latency: 3 and 4

- Burst Length: 8

- Bi-directional, differential data strobes (DDRUDQS, DDRLDQS and DDRUDQS, DDRLDQS) are transmitted / received with data

- Edge-aligned with Read data and center-aligned with Write data

- DLL aligns Data (DDRDQx) and Data Qualifier Strobe (DDRxDQS, DDRxDQS) transitions with clock

- Differential clock inputs (DDRCK and /DDRCK)

- · Data masks (DDRUDM, DDRLDM) for write data

- Commands entered on each positive DDRCK edge, data and data mask are referenced to both edges of DDRxDQS

- Posted CAS programmable additive latency supported to make command and data bus efficiency

- Read Latency = Additive Latency plus CAS Latency (RL = AL + CL)

- Off-Chip-Driver impedance adjustment (OCD) and On-Die-Termination (ODT) for better signal quality

- Auto-precharge operation for read and write bursts

- · Auto Refresh and Self Refresh modes

- Precharged Power Down and Active Power Down

- Write Latency = Read Latency 1 (WL = RL 1)

Figure 4-3 provides a block diagram of the DDR2 SDRAM.

#### FIGURE 4-3: DDR2 SDRAM BLOCK DIAGRAM

## 4.3 Timing Parameters

Table 4-5 only applies to device variants with internal 32 MB DDR2 SDRAM. For device variants supporting external DDR2 SDRAM memory, refer to the vendor data sheet for timing parameters.

| TABLE 4-5: | TIMING PARAMETERS |

|------------|-------------------|

|            |                   |

| Parameter | Description                                          | Value | Units           |

|-----------|------------------------------------------------------|-------|-----------------|

| tRFC      | Auto-refresh Cycle Time                              | 130   | ns              |

| tWR       | Write Recovery Time                                  | 25    | ns              |

| tRP       | Precharge-to-Active<br>Command Delay Time            | 20    | ns              |

| tRCD      | Active to Read/Write<br>Command Delay Time           | 20    | ns              |

| tRRD      | Row-to-Row (RAS to<br>RAS) Command Delay<br>Time     | 7.5   | ns              |

| tWTR      | Write-to-Read Command<br>Delay Time                  | 15    | ns              |

| tRTP      | Read-to-Precharge<br>Command Delay Time              | 20    | ns              |

| tDLLK     | DLL Lock Delay Time                                  | 200   | Clock<br>cycles |

| tRAS      | Active to Precharge<br>Minimum Command<br>Delay Time | 40    | ns              |

| tRC       | Row Cycle Time                                       | 110   | ns              |

| tFAW      | Four Bank Activation<br>Window                       | 35    | ns              |

| tMRD      | Mode Register Set<br>Command Cycle Delay             | 4     | Clock<br>cycles |

| tXP       | Power Down Exit Delay                                | 6     | Clock<br>cycles |

| tCKE      | Power Down Minimum<br>Delay                          | 6     | Clock<br>cycles |

| RL        | CAS Latency                                          | 4     | Clock<br>cycles |

| tRFI      | Average Periodic<br>Refresh Interval                 | 7.8   | μs              |

| WL        | Write Latency                                        | 3     | Clock<br>cycles |

| BL        | Burst Length (in cycles)                             | 8     | Clock<br>cycles |

## 4.4 System Bus Arbitration

Note: The System Bus interconnect implements one or more instantiations of the SonicsSX<sup>®</sup> interconnect from Sonics, Inc. This document contains materials that are (c) 2003-2015 Sonics, Inc., and that constitute proprietary information of Sonics, Inc. SonicsSX is a registered trademark of Sonics, Inc. All such materials and trademarks are used under license from Sonics, Inc.

As shown in the PIC32MZ DA Family Block Diagram (see Figure 1-1), there are multiple initiator modules (I1 through I14) in the system that can access various target modules (T1 through T23). Table 4-6 illustrates which initiator can access which target. The System Bus supports simultaneous access to targets by initiators, so long as the initiators are accessing different targets. The System Bus will perform arbitration if multiple initiators attempt to access the same target.

| Bit<br>Range | Bit Bit 31/23/15/7 30/22/14/6 |     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |  |

|--------------|-------------------------------|-----|-------------------|-------------------|-------------------|-------------------|-----------------------|------------------|--|

| 31:24        | U-0                           | U-0 | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0              |  |

| 31.24        | —                             |     | _                 | —                 | _                 | _                 | _                     | -                |  |

| 23:16        | U-0                           | U-0 | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0              |  |

| 23.10        | —                             |     | _                 | —                 | _                 | _                 | _                     | -                |  |

| 15:8         | U-0                           | U-0 | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0              |  |

| 15.0         | —                             |     | _                 | —                 | _                 | _                 | _                     | -                |  |

| 7.0          | U-0                           | U-0 | U-0               | U-0               | U-0               | U-0               | R/W-0                 | R/W-0            |  |

| 7:0          | _                             |     | _                 | _                 |                   |                   | T0PGV3 <sup>(1)</sup> | T16PGV           |  |

#### REGISTER 4-5: SBFLAG3: SYSTEM BUS STATUS FLAG REGISTER 3

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

|-------------------|------------------|------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

bit 31-2 Unimplemented: Read as '0'

- bit 1 **TOPGV3:** Target 0 (System Bus 3) Permission Group Violation Status bit<sup>(1)</sup>

- 1 = Target 0 (System Bus 3) is reporting a Permission Group (PG) violation

- 0 = Target 0 (System Bus 3) is not reporting a PG violation

- bit 0 T16PGV: Target 16 (DDR2 Target 3 and Target 4) Permission Group Violation Status bit

- 1 = Target 16 is reporting a Permission Group (PG) violation

- 0 = Target 16 is not reporting a PG violation

- **Note 1:** System Bus 3 represents an internal sub-system element and should be treated as a general System Bus violation.

# Note: All errors are cleared at the source (i.e., SBTxELOG1, SBTxELOG2, SBTxECLRS, or SBTxECLRM registers).

## TABLE 11-1: USB REGISTER MAP 1 (CONTINUED)

|                    |                  |           |       |                 |       |       |           |       |           |           | Bits      |        |                       |                       |        |          |          |       |            |

|--------------------|------------------|-----------|-------|-----------------|-------|-------|-----------|-------|-----------|-----------|-----------|--------|-----------------------|-----------------------|--------|----------|----------|-------|------------|

| Virtual<br>Address | Register<br>Name | Bit Range | 31/15 | 30/14           | 29/13 | 28/12 | 27/11     | 26/10 | 25/9      | 24/8      | 23/7      | 22/6   | 21/5                  | 20/4                  | 19/3   | 18/2     | 17/1     | 16/0  | All Resets |

| 3340               |                  | 31:16     | _     | -               | —     | _     | —         | _     | -         | —         | EP7TXD    | EP6TXD | EP5TXD                | EP4TXD                | EP3TXD | EP2TXD   | EP1TXD   | _     | 0000       |

| 3340               | DPBFD            | 15:0      | -     | -               | -     |       | —         | _     | -         | _         | EP7RXD    | EP6RXD | EP5RXD                | EP4RXD                | EP3RXD | EP2RXD   | EP1RXD   |       | 0000       |

| 3344               | 000              | 31:16     |       | THHSRTN<15:0> 0 |       |       |           |       |           |           |           |        |                       |                       |        | 05E6     |          |       |            |

| 3344               | TMCON1           | 15:0      |       |                 |       |       |           |       |           | T         | UCH<15:0> |        |                       |                       |        |          |          |       |            |

| 3348               | 000              |           |       |                 |       |       |           |       | _         |           | 0000      |        |                       |                       |        |          |          |       |            |

| 3340               | TMCON2           | 15:0      | _     |                 | _     |       | _         | —     |           | —         |           | —      | —                     | -                     |        | THSBT<3  | 8:0>     |       | 0000       |

|                    | 1105             | 31:16     |       | -               | LPM   | LPM   | LPMACKIE  |       | LPMSTIE   | LPMTOIE   |           | _      |                       | LPMNAK <sup>(1)</sup> | LPME   | N<1:0>   | LPMRES   |       | 0000       |

| 3360               | USB<br>LPMR1     | 31.10     | _     |                 | ERRIE | RESIE |           |       | LEIVISTIE | LFINITUIE |           | _      | —                     | _(2)                  | (2)    | (2)      | LFINIRES |       | 0000       |

|                    | 2                | 15:0      |       | ENDPOINT        | <3:0> |       | —         |       | -         | RMTWAK    |           | HIRI   | D<3:0>                |                       |        | LNKSTATE | <3:0>    |       | 0000       |

|                    |                  | 31:16     | -     | _               | _     | -     | —         | _     | -         | —         | -         | —      | _                     |                       | -      | _        | -        |       | 0000       |

| 3364               | USB<br>LMPR2     | 15:0      | _     |                 |       | LPI   | MFADDR<6: | 0>    |           |           | _         | _      | LPMERR <sup>(1)</sup> | LPMRES                | LPMNC  | LPMACK   | LPMNY    | LPMST | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Device mode.

2: Host mode.

3:

Definition for Endpoint 0 (ENDPOINT<3:0> (USBCSR<19:16>) = 0). Definition for Endpoints 1-7 (ENDPOINT<3:0> (USBCSR<19:16>) = 1 through 7). 4:

### TABLE 11-2: USB REGISTER MAP 2

|                    |                  | Bits      |       |       |       |       |       |       |               |              |         |               |                |                |               |       |        |               |            |

|--------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|---------------|--------------|---------|---------------|----------------|----------------|---------------|-------|--------|---------------|------------|

| Virtual<br>Address | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9          | 24/8         | 23/7    | 22/6          | 21/5           | 20/4           | 19/3          | 18/2  | 17/1   | 16/0          | All Resets |

|                    |                  | 31:16     | _     | _     | _     | _     | -     | USBIF | USBRF         | USBWKUP      | _       | _             | _              | _              | _             | _     | _      | _             | 0000       |

| 4000               | USB<br>CRCON     | 15:0      | _     | _     | _     | -     | _     | _     | USB<br>IDOVEN | USB<br>IDVAL | PHYIDEN | VBUS<br>MONEN | ASVAL<br>MONEN | BSVAL<br>MONEN | SEND<br>MONEN | USBIE | USBRIE | USB<br>WKUPEN | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

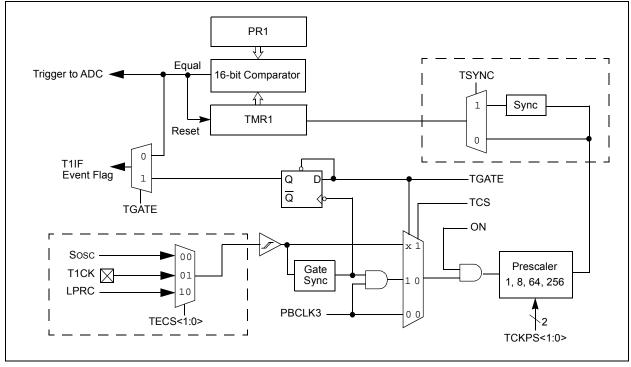

## 13.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MZ Graphics (DA) Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MZ DA devices feature one synchronous/asynchronous 16-bit timer that can operate as a free-running interval timer for various timing applications and counting external events. This timer can also be used with the lowpower Secondary Oscillator (Sosc) for real-time clock applications.

## FIGURE 13-1: TIMER1 BLOCK DIAGRAM

The following modes are supported by Timer1:

- Synchronous Internal Timer

- Synchronous Internal Gated Timer

- Synchronous External Timer

- Asynchronous External Timer

## 13.1 Additional Supported Features

- Selectable clock prescaler

- Timer operation during Sleep and Idle modes

- Fast bit manipulation using CLR, SET and INV registers

- Asynchronous mode can be used with the Sosc to function as a real-time clock

- · ADC event trigger

## 22.1 SQI Control Registers

## TABLE 22-1: SERIAL QUADRATURE INTERFACE (SQI) REGISTER MAP

| SSS                         |                   |               |       |       |         |          |              |               |              |              | Bits           |               |             |              |               |             |              |               |            |

|-----------------------------|-------------------|---------------|-------|-------|---------|----------|--------------|---------------|--------------|--------------|----------------|---------------|-------------|--------------|---------------|-------------|--------------|---------------|------------|

| Virtual Address<br>(BF8E_#) | Register<br>Name  | Bit Range     | 31/15 | 30/14 | 29/13   | 28/12    | 27/11        | 26/10         | 25/9         | 24/8         | 23/7           | 22/6          | 21/5        | 20/4         | 19/3          | 18/2        | 17/1         | 16/0          | All Resets |

| 2000                        | SQI1              | 31:16         | -     | _     | SDRCMD  | DDRDATA  | DDR<br>DUMMY | DDR<br>MODE   | DDR<br>ADDR  | DDRCMD       | DUN            | /MYBYTES<     | 2:0>        | AD           | DRBYTES<2     | :0>         | READOPC      | ODE<7:6>      | 0000       |

|                             | XCON1             | 15:0          |       |       | READOPC | ODE<5:0> |              |               | TYPEDA       | ATA<1:0>     | TYPEDU         | /MY<1:0>      | TYPEMC      | DE<1:0>      | TYPEAD        | DR<1:0>     | TYPEC        | /ID<1:0>      | 0000       |

| 2004                        | SQI1              | 31:16         | _     | -     | _       | _        | -            | _             | _            | _            | -              | _             |             |              | —             |             | _            | _             | 0000       |

| 2004                        | XCON2             | 15:0          | _     | _     | _       | _        | DEVSE        | EL<1:0>       | MODEBY       | TES<1:0>     |                |               |             | MODECO       | DDE<7:0>      |             |              |               | 0000       |

| 2008                        | SQI1CFG           | 31:16         | —     | _     | —       | _        | _            | _             | CSEN         | I<1:0>       | SQIEN          | _             | DATAE       | N<1:0>       | CON<br>BUFRST | RXBUFST     | TXBUFST      | RESET         | 0000       |

|                             |                   | 15:0          | _     | _     | _       | BURSTEN  | _            | HOLD          | WP           | —            |                | —             | LSBF        | CPOL         | CPHA          |             | MODE<2:0>    |               | 0000       |

| 200C                        | SQI1CON           | 31:16         | —     | —     | —       | —        | —            | —             | —            | SCHECK       | DDRMODE        | DASSERT       | DEVSE       | L<1:0>       | LANEMC        | DE<1:0>     | CMDIN        | IT<1:0>       | 0000       |

| 2000                        | ognoon            | 15:0          |       |       |         |          |              |               |              | TXF          | RXCOUNT<1      | 5:0>          |             |              |               |             |              |               | 0000       |

| 2010                        | SQI1              | 31:16         | _     | —     | —       | <u> </u> | —            |               |              | —            | _              | _             |             |              | —             | (           | CLKDIV<10:8  |               | 0000       |

|                             | CLKCON            | 15:0          |       |       |         | CLKDIV   | <7:0>        |               |              |              | —              | —             | _           |              | —             | _           | STABLE       | EN            | 0000       |

| 2014                        | SQI1              | 31:16         | —     | _     | —       | —        | —            | —             | —            | _            |                | _             | —           | —            | —             | —           | —            | —             | 0000       |

|                             | CMDTHR            | 15:0          | _     |       |         |          |              | THR<5:0>      |              |              |                |               |             |              | RXCMDT        |             |              |               | 0000       |

| 2018                        | SQI1<br>INTTHR    | 31:16         | _     |       | _       | —        | -            | —             | —            | _            |                |               | _           | _            |               | -           | —            | _             | 0000       |

|                             |                   | 15:0<br>31:16 | _     | _     |         |          | TXINTT       | HR<5:0>       |              | _            | _              | _             |             |              | RXINTTI       | HR<5:0>     |              |               | 0000       |

| 201C                        | SQI1<br>INTEN     | 15:0          | _     |       |         |          | <br>DMAEIE   | PKT           | BD           | CON          | CON            | CON           | RX          | RX           | RX            | TX          | TX           | —<br>TX       | 0000       |

|                             |                   |               |       |       |         |          | DMAEIE       | COMPIE        | DONEIE       | THRIE        | EMPTYIE        | FULLIE        | THRIE       | FULLIE       | EMPTYIE       | THRIE       | FULLIE       | EMPTYIE       | 0000       |

| 2020                        | SQI1              | 31:16         | _     | _     |         | _        | _            | —<br>DI(T     | -            | -            | -              | -             | -           | -            | -             | —<br>       | —<br>        | —<br>         | 0000       |

| 2020                        | INTSTAT           | 15:0          | —     | —     | —       | —        | DMAEIF       | PKT<br>COMPIF | BD<br>DONEIF | CON<br>THRIF | CON<br>EMPTYIF | CON<br>FULLIF | RX<br>THRIF | RX<br>FULLIF | RX<br>EMPTYIF | TX<br>THRIF | TX<br>FULLIF | TX<br>EMPTYIF | 0000       |

| 2024                        | SQI1              | 31:16         |       |       |         |          |              |               |              | T.           | XDATA<31:1     | 6>            |             |              |               |             |              |               | 0000       |

| 2024                        | TXDATA            | 15:0          |       |       |         |          |              |               |              | Т            | XDATA<15:0     | )>            |             |              |               |             |              |               | 0000       |

| 2028                        | SQI1              | 31:16         |       |       |         |          |              |               |              |              | XDATA<31:1     |               |             |              |               |             |              |               | 0000       |

|                             | RXDATA            | 15:0          |       |       |         |          |              |               |              | F            | XDATA<15:0     | )>            |             |              |               |             |              |               | 0000       |

| 202C                        | SQI1              | 31:16         | _     |       | —       | —        |              | —             |              |              | _              |               |             |              | TXBUFFF       |             |              |               | 0000       |

|                             | STAT1             | 15:0          | —     | —     | —       | —        | —            | —             | —            | —            | —              | —             |             |              | RXBUFC        | NT<5:0>     |              |               | 0000       |

| 2030                        | SQI1<br>STAT2     | 31:16         | _     |       | —       | —        | _            | —             | -            | -            | —              | -             | -           | -            | -             | —           | CMDST        |               | 0000       |

|                             | -                 | 15:0          |       |       |         |          |              |               |              |              | 00x0           |               |             |              |               |             |              |               |            |

| 2034                        | SQI1<br>BDCON     | 31:16<br>15:0 |       |       |         |          |              |               |              |              |                |               |             |              |               |             |              |               |            |

|                             |                   | 31:16         | _     | _     | —       | _        | _            |               | _            | - BDCI       | <br>JRRADDR<3  |               | _           | _            |               | START       | POLLEN       | DMAEN         | 0000       |

| 2038                        | SQI1BD<br>CURADD  | 15:0          |       |       |         |          |              |               |              |              | URRADDR<3      |               |             |              |               |             |              |               | 0000       |

|                             |                   | 31:16         |       |       |         |          |              |               |              |              | DADDR<31:1     |               |             |              |               |             |              |               | 0000       |

| 2040                        | SQI1BD<br>BASEADD | 15:0          |       |       |         |          |              |               |              |              | DADDR<31.1     |               |             |              |               |             |              |               | 0000       |

| L                           |                   | 10.0          |       |       |         |          |              |               |              | D            | 2              | •             |             |              |               |             |              |               | 3000       |

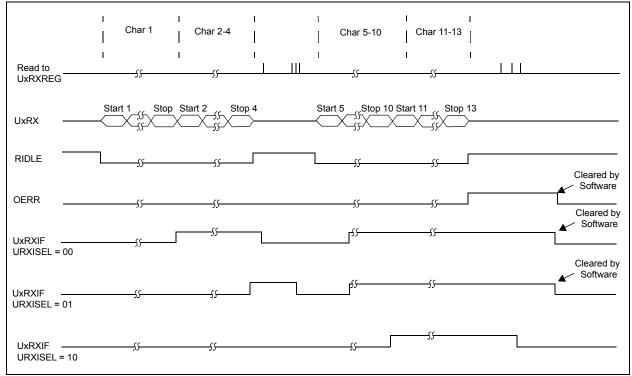

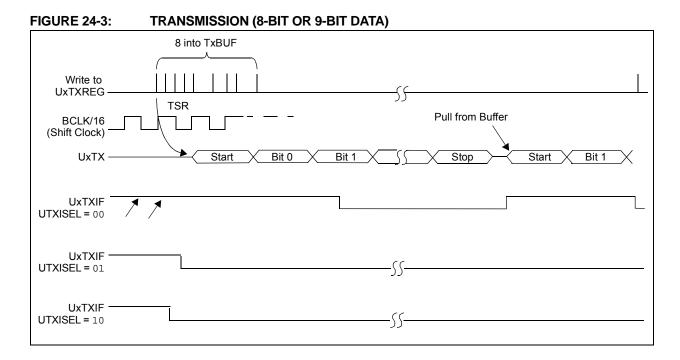

Figure 24-2 and Figure 24-3 illustrate typical receive and transmit timing for the UART module.

## FIGURE 24-2: UART RECEPTION

#### REGISTER 26-5: EBISMCON: EXTERNAL BUS INTERFACE STATIC MEMORY CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 31:24        | —                 | _                 | -                 | —                 | _                 | _                 | _                | _                    |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 23:16        | —                 | _                 | _                 | —                 | _                 | _                 | _                | _                    |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-1            | R/W-0                |

| 15:8         | SMDV              | VIDTH2<2:0>       |                   | SM                | DWIDTH1<2         | :0>               | SMDWID           | <sup>-</sup> H0<2:1> |

| 7.0          | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-1                |

| 7:0          | SMDWIDTH0<0>      | _                 | _                 |                   | _                 | _                 | _                | SMRP                 |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |  |

|-------------------|------------------|----------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

#### bit 15-13 SMDWIDTH2<2:0>: Static Memory Width for Register EBISMT2 bits

- 111 = Reserved

- 110 = Reserved

- 101 = Reserved

- 100 = 8 bits

- 011 = Reserved

- 010 = Reserved

- 001 = Reserved 000 = 16 bits

#### bit 12-10 SMDWIDTH1<2:0>: Static Memory Width for Register EBISMT1 bits

- 111 = Reserved

- 110 = Reserved

- 101 = Reserved

- 100 **= 8 bits**

- 011 = Reserved

- 010 = Reserved

- 001 = Reserved

- 000 **= 16 bits**

#### bit 9-7 SMDWIDTH0<2:0>: Static Memory Width for Register EBISMT0 bits

- 111 = Reserved

- 110 = Reserved

- 101 = Reserved

- 100 = 8 bits

- 011 = Reserved

- 010 = Reserved

- 001 = Reserved

- 000 = 16 bits

- bit 6-1 Unimplemented: Read as '0'

#### bit 0 SMRP: Flash Reset/Power-down mode Select bit

After a Reset, the controller internally performs a power-down for Flash, and then sets this bit to '1'.

- 1 = Flash is taken out of Power-down mode

- 0 = Flash is forced into Power-down mode

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                 | _                 | —                 | -                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | _                 | —                 | -                 | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | —                 | _                 | _                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | HDRLEN            | N<7:0>            |                   |                  |                  |

## REGISTER 27-9: CEHDLEN: CRYPTO ENGINE HEADER LENGTH REGISTER

## Legend:

| =ogona.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 **HDRLEN<7:0>:** DMA Header Length bits For every packet, skip this length of locations and start filling the data.

## REGISTER 27-10: CETRLLEN: CRYPTO ENGINE TRAILER LENGTH REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         |                   | —                 | _                 | _                 | _                 |                   | _                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | TRLRLE            | N<7:0>            |                   |                  |                  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

## bit 31-8 **Unimplemented:** Read as '0'

bit 7-0 **TRLRLEN<7:0>:** DMA Trailer Length bits For every packet, skip this length of locations at the end of the current packet and start putting the next packet.

## FIGURE 27-3: FORMAT OF BD\_SADDR

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31-24        |                   |                   |                   | BD_SAADD          | )R<31:24>         |                   |                  |                  |

| 23-16        |                   |                   |                   | BD_SAADD          | )R<23:16>         |                   |                  |                  |

| 15-8         |                   |                   |                   | BD_SAAD           | DR<15:8>          |                   |                  |                  |

| 7-0          |                   |                   |                   | BD_SAAD           | DR<7:0>           |                   |                  |                  |

bit 31-0 **BD\_SAADDR<31:0>:** Security Association IP Session Address The sessions' SA pointer has the keys and IV values.

#### FIGURE 27-4: FORMAT OF BD\_SADDR

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31-24        |                   |                   |                   | BD_SAADD          | )R<31:24>         |                   |                  |                  |

| 23-16        |                   | BD_SAADDR<23:16>  |                   |                   |                   |                   |                  |                  |

| 15-8         |                   |                   |                   | BD_SAAD           | DR<15:8>          |                   |                  |                  |

| 7-0          |                   | BD_SAADDR<7:0>    |                   |                   |                   |                   |                  |                  |

bit 31-0 **BD\_SAADDR<31:0>:** Security Association IP Session Address The sessions' SA pointer has the keys and IV values.

## FIGURE 27-5: FORMAT OF BD\_SRCADDR

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31-24        |                   | BD_SCRADDR<31:24> |                   |                   |                   |                   |                  |                  |

| 23-16        |                   | BD_SCRADDR<23:16> |                   |                   |                   |                   |                  |                  |

| 15-8         |                   | BD_SCRADDR<15:8>  |                   |                   |                   |                   |                  |                  |

| 7-0          |                   | BD_SCRADDR<7:0>   |                   |                   |                   |                   |                  |                  |

#### bit 31-0 BD\_SCRADDR: Buffer Source Address

The source address of the buffer that needs to be passed through the PE-CRDMA for encryption or authentication. This address must be on a 32-bit boundary.

**IVRIE:** Invalid Message Received Interrupt Enable bit

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-----------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0              | U-0              |

| 31:24        | IVRIE             | WAKIE             | CERRIE            | SERRIE                | RBOVIE            | _                 | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        |                   | _                 | _                 | _                     | MODIE             | CTMRIE            | RBIE             | TBIE             |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0              | U-0              |

| 15:8         | IVRIF             | WAKIF             | CERRIF            | SERRIF <sup>(1)</sup> | RBOVIF            | _                 | —                | _                |

| 7:0          | U-0               | U-0               | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | _                 | _                 | _                 |                       | MODIF             | CTMRIF            | RBIF             | TBIF             |

## REGISTER 30-3: CIINT: CAN INTERRUPT REGISTER

#### Legend:

bit 31

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

|           | 1 = Interrupt request enabled<br>0 = Interrupt request not enabled                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30    | WAKIE: CAN Bus Activity Wake-up Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled                                       |

| bit 29    | <b>CERRIE:</b> CAN Bus Error Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled                                          |

| bit 28    | SERRIE: System Error Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled                                                  |

| bit 27    | <b>RBOVIE:</b> Receive Buffer Overflow Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled                                |

| bit 26-20 | Unimplemented: Read as '0'                                                                                                                                       |

| bit 19    | MODIE: Mode Change Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled                                                    |

| bit 18    | <b>CTMRIE:</b> CAN Timestamp Timer Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled                                    |

| bit 17    | <b>RBIE:</b> Receive Buffer Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled                                           |

| bit 16    | <b>TBIE:</b> Transmit Buffer Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled                                          |

| bit 15    | <b>IVRIF:</b> Invalid Message Received Interrupt Flag bit<br>1 = An invalid messages interrupt has occurred<br>0 = An invalid message interrupt has not occurred |

|           |                                                                                                                                                                  |

Note 1: This bit can only be cleared by turning the CAN module Off and On by clearing or setting the ON bit (CiCON<15>).

## REGISTER 30-20: CiFIFOCONn: CAN FIFO CONTROL REGISTER (n = 0 THROUGH 31)

- TXABAT: Message Aborted bit<sup>(2)</sup> bit 6 1 = Message was aborted 0 = Message completed successfully bit 5 TXLARB: Message Lost Arbitration bit<sup>(3)</sup> 1 = Message lost arbitration while being sent 0 = Message did not loose arbitration while being sent TXERR: Error Detected During Transmission bit<sup>(3)</sup> bit 4 1 = A bus error occured while the message was being sent 0 = A bus error did not occur while the message was being sent bit 3 **TXREQ:** Message Send Request TXEN = 1: (FIFO configured as a Transmit FIFO) Setting this bit to '1' requests sending a message. The bit will automatically clear when all the messages queued in the FIFO are successfully sent Clearing the bit to '0' while set ('1') will request a message abort. TXEN = 0: (FIFO configured as a Receive FIFO) This bit has no effect. bit 2 RTREN: Auto RTR Enable bit 1 = When a remote transmit is received, TXREQ will be set 0 = When a remote transmit is received, TXREQ will be unaffected bit 1-0 TXPR<1:0>: Message Transmit Priority bits 11 = Highest Message Priority 10 = High Intermediate Message Priority 01 = Low Intermediate Message Priority 00 = Lowest Message Priority Note 1: These bits can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> bits (CiCON<23:21>) = 100).

- 2: This bit is updated when a message completes (or aborts) or when the FIFO is reset.

- 3: This bit is reset on any read of this register or when the FIFO is reset.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 | —                 | —                 | —                 | _                 | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              |                   | _                 | —                 | —                 | —                 | _                 | —                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              |                   | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

|              | _                 |                   |                   |                   |                   | _                 | INITDN           | STINIT           |

## REGISTER 38-5: DDRMEMCON: DDR MEMORY CONTROL REGISTER

#### Legend:

| =ogona.           |                  |                        |                    |  |

|-------------------|------------------|------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

#### bit 31-2 Unimplemented: Read as '0'

bit 1 **INITDN:** Memory Initialize Done bit

Set by software after memory initialization is completed to enable controller for regular operation.

- 1 = All commands have been issued; the controller is enabled for regular operation

- 0 = Controller not enabled for regular operation

- bit 0 STINIT: Memory Initialize Start bit

Set by software after the memory initialization commands are loaded into the DDRCMD registers to start memory initialization.

1 = Start memory initialization

0 = Do not start memory initialization

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1             | Bit<br>24/16/8/0             |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------------------|------------------------------|

|              | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | W-0               | U-0                          | R/W-0                        |

| 31:24        | —                 | —                 | SCL<br>PHCAL      | SCL<br>START      | —                 | SCLEN             | —                            | —                            |

| 22:16        | U-0                          | U-0                          |

| 23:16        | —                 | —                 |                   | —                 | —                 | —                 | —                            | —                            |

| 15:8         | U-0                          | U-0                          |

| 10.0         | —                 | —                 | _                 | —                 | —                 | —                 | —                            | —                            |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0               | R-0                          | R-0                          |

|              | _                 | —                 | _                 | —                 | —                 | —                 | SCLUB<br>PASS <sup>(1)</sup> | SCLLB<br>PASS <sup>(1)</sup> |

#### REGISTER 38-24: DDRSCLSTART: DDL SELF CALIBRATION LOGIC START REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

|-------------------|------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

- bit 31-30 Unimplemented: Write as '0'

- bit 29 SCLPHCAL: Start Phase Self-calibration Logic bit

- 1 = Phase calibration is enabled

- 0 = Phase calibration is disabled

- bit 28 SCLSTART: Start Self Calibration Logic bit

- 1 = Start self calibration

- 0 = Do not start self calibration

- bit 27 Unimplemented: Write as '0'

- bit 26 SCLEN: Self Calibration Logic Enable bit

- 1 = Enable dynamic self calibration logic

- 0 = Disable dynamic self calibration logic

Note: Enabling dynamic self calibration may impact performance.

- bit 25-2 Unimplemented: Write as '0'

- bit 1 SCLUBPASS: Self Calibration Logic Upper Data Byte Status bit<sup>(1)</sup>

- 1 = Self calibration logic for upper data byte passed

- 0 = Self calibration logic for upper data byte failed

- bit 0 SCLLBPASS: Self Calibration Logic Lower Data Byte Status bit<sup>(1)</sup>

- 1 = Self calibration logic for lower data byte passed

- 0 = Self calibration logic for lower data byte failed

- Note 1: This bit is set by hardware when the SCL process has passed and is complete.

## 44.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MZ DA electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC32MZ DA devices are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions, above the parameters indicated in the operation listings of this specification, is not implied.

#### **ABSOLUTE MAXIMUM RATINGS**

#### (see Note1)

| Ambient temperature under bias                                                    |                          |

|-----------------------------------------------------------------------------------|--------------------------|

| Storage temperature                                                               | 65°C to +150°C           |

| Voltage on VDDIO, VDDCORE, and VBAT with respect to Vss                           | 0.3V to +4.0V            |

| Voltage on VDDR1V8 pin with respect to VSS1V8                                     | 0.5V to +1.98V           |

| Voltage on DDR2 pins with respect to Vss1v8                                       | 0.3V to (VDDR1V8 + 0.3V) |

| Voltage on any pin that is not 5V tolerant, with respect to Vss (Note 3)          | 0.3V to (VDDIO + 0.3V)   |

| Voltage on any 5V tolerant pin with respect to Vss when VDDIO $\ge 2.2V$ (Note 3) | 0.3V to +5.5V            |

| Voltage on any 5V tolerant pin with respect to Vss when VDDIO < 2.2V (Note 3)     | 0.3V to +3.6V            |

| Voltage on D+ or D- pin with respect to VUSB3V3                                   | 0.3V to (VUSB3V3 + 0.3V) |

| Voltage on VBUS with respect to VSS                                               | 0.3V to +5.5V            |

| Maximum current out of Vss pin(s)                                                 | 200 mA                   |

| Maximum current into VDDIO pin(s) (Note 2)                                        | 200 mA                   |

| Maximum current sunk/sourced by DDR2 pin                                          | 22 mA                    |

| Maximum current sunk/sourced by any 4x I/O pin (Note 4)                           | 15 mA                    |

| Maximum current sunk/sourced by any 8x I/O pin (Note 4)                           | 25 mA                    |

| Maximum current sunk/sourced by any 12x I/O pin (Note 4)                          |                          |

| Maximum current sunk by all ports (Note 5)                                        | 150 mA                   |

| Maximum current sourced by all ports (Note 2, Note 5)                             | 150 mA                   |

**Note 1:** Stresses above those listed under "**Absolute Maximum Ratings**" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 44-2).

- **3:** See the pin name tables (Table 5 through Table 7) for the 5V tolerant pins.

- 4: Characterized, but not tested. Refer to parameters DO10, DO20, and DO20a for the 4x, 8x, and 12x I/O pin lists.

- 5: Excludes DDR2 pins.

|               |         |                                                        |                        | Standard Operating Conditions:VDDIO = 2.2V to 3.6V,VDDCORE = 1.7V to 1.9V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |      |       |                                        |  |

|---------------|---------|--------------------------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----------------------------------------|--|