Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                                        |

|----------------------------|-----------------------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                            |

| Speed                      | 200MHz                                                                                        |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, SQI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT                            |

| Number of I/O              | 120                                                                                           |

| Program Memory Size        | 2MB (2M x 8)                                                                                  |

| Program Memory Type        | FLASH                                                                                         |

| EEPROM Size                | -                                                                                             |

| RAM Size                   | 640K x 8                                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                   |

| Data Converters            | A/D 45x12b                                                                                    |

| Oscillator Type            | Internal                                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                             |

| Mounting Type              | Surface Mount                                                                                 |

| Package / Case             | 169-LFBGA                                                                                     |

| Supplier Device Package    | 169-LFBGA (11x11)                                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2064dah169-i-6j              |

|                            |                                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          | I                             | Pin Numbe | r                | Din Duffer  |                |                                     |  |  |

|----------|-------------------------------|-----------|------------------|-------------|----------------|-------------------------------------|--|--|

| Pin Name | 169-pin 176-pin<br>LFBGA LQFP |           | 288-pin<br>LFBGA | Pin<br>Type | Buffer<br>Type | Description                         |  |  |

|          |                               |           |                  | Ex          | ternal Bus     | s Interface                         |  |  |

| EBIA0    | H13                           | 142       | N17              | 0           | _              | External Bus Interface Address Bus  |  |  |

| EBIA1    | J11                           | 136       | R18              | 0           |                |                                     |  |  |

| EBIA2    | C5                            | 33        | В9               | 0           |                |                                     |  |  |

| EBIA3    | H11                           | 135       | R17              | 0           | —              | 1                                   |  |  |

| EBIA4    | J12                           | 139       | N15              | 0           | —              | 1                                   |  |  |

| EBIA5    | A11                           | 174       | B18              | 0           | —              |                                     |  |  |

| EBIA6    | F3                            | 69        | К3               | 0           | —              |                                     |  |  |

| EBIA7    | B12                           | 173       | E16              | 0           | —              | 1                                   |  |  |

| EBIA8    | N2                            | 96        | V9               | 0           | —              | 1                                   |  |  |

| EBIA9    | M2                            | 95        | Т8               | 0           | —              | 1                                   |  |  |

| EBIA10   | K3                            | 90        | U7               | 0           | —              |                                     |  |  |

| EBIA11   | L1                            | 91        | V7               | 0           | —              |                                     |  |  |

| EBIA12   | J1                            | 80        | U5               | 0           | _              |                                     |  |  |

| EBIA13   | J2                            | 81        | N4               | 0           | _              |                                     |  |  |

| EBIA14   | G2                            | 74        | R6               | 0           | _              |                                     |  |  |

| EBIA15   | G3                            | 75        | Т6               | 0           | _              |                                     |  |  |

| EBIA16   | K12                           | 137       | P16              | 0           | _              |                                     |  |  |

| EBIA17   | L13                           | 134       | R16              | 0           | _              |                                     |  |  |

| EBIA18   | H10                           | 133       | P15              | 0           | —              | 1                                   |  |  |

| EBIA19   | J10                           | 132       | R15              | 0           | —              | 1                                   |  |  |

| EBIA20   | M13                           | 131       | T18              | 0           | —              | 1                                   |  |  |

| EBIA21   | M12                           | 130       | T17              | 0           | —              | 1                                   |  |  |

| EBIA22   | E8                            | 151       | K17              | 0           | —              |                                     |  |  |

| EBIA23   | L2                            | 92        | V8               | 0           | —              |                                     |  |  |

| EBID0    | C4                            | 40        | B7               | I/O         | ST             | External Bus Interface Data I/O Bus |  |  |

| EBID1    | A4                            | 40        | D8               | I/O         | ST             |                                     |  |  |

| EBID2    | N3                            | 36        | V10              | I/O         | ST             | 1                                   |  |  |

| EBID3    | M3                            | 99        | Т9               | I/O         | ST             | 1                                   |  |  |

| EBID4    | B3                            | 98        | B6               | I/O         | ST             | ]                                   |  |  |

| EBID5    | B7                            | 43        | A12              | I/O         | ST             | 1                                   |  |  |

| EBID6    | F6                            | 17        | C11              | I/O         | ST             | 1                                   |  |  |

| EBID7    | C7                            | 23        | B11              | I/O         | ST             | 1                                   |  |  |

| EBID8    | K2                            | 24        | T7               | I/O         | ST             | 1                                   |  |  |

| EBID9    | L3                            | 89        | U9               | I/O         | ST             | 1                                   |  |  |

| EBID10   | A9                            | 97        | A15              | I/O         | ST             | 1                                   |  |  |

| EBID11   | G10                           | 10        | N18              | I/O         | ST             | 1                                   |  |  |

| EBID12   | A8                            | 143       | C13              | I/O         | ST             | 1                                   |  |  |

| EBID13   | G12                           | 14        | M16              | I/O         | ST             | 1                                   |  |  |

| EBID14   | L11                           | 144       | V17              | I/O         | ST             | 1                                   |  |  |

| EBID15   | H1                            | 127       | U6               | I/O         | ST             | 1                                   |  |  |

## TABLE 1-13: EBI PINOUT I/O DESCRIPTIONS

ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

O = Output PPS = Peripheral Pin Select

#### **TABLE 1-18: SQI1 PINOUT I/O DESCRIPTIONS**

| Pin Name                                       | Pin Number            |    |                  | Dim                       | Buffer                       |                                     |  |  |  |

|------------------------------------------------|-----------------------|----|------------------|---------------------------|------------------------------|-------------------------------------|--|--|--|

|                                                | 109-pin 170-pin 200   |    | 288-pin<br>LFBGA | – Pin Buffer<br>Type Type |                              | Description                         |  |  |  |

|                                                | Serial Quad Interface |    |                  |                           |                              |                                     |  |  |  |

| SQICLK                                         | E4                    | 54 | E4               | 0                         | _                            | Serial Quad Interface Clock         |  |  |  |

| SQICS0                                         | F1                    | 70 | K4               | 0                         | _                            | Serial Quad Interface Chip Select 0 |  |  |  |

| SQICS1                                         | F2                    | 71 | L4               | 0                         | _                            | Serial Quad Interface Chip Select 1 |  |  |  |

| SQID0                                          | E2                    | 64 | H4               | I/O                       | ST                           | Serial Quad Interface Data 0        |  |  |  |

| SQID1                                          | E3                    | 56 | G4               | I/O                       | ST                           | Serial Quad Interface Data 1        |  |  |  |

| SQID2                                          | E1                    | 65 | J4               | I/O                       | ST                           | Serial Quad Interface Data 2        |  |  |  |

| SQID3                                          | D1                    | 55 | F4               | I/O                       | ST                           | Serial Quad Interface Data 3        |  |  |  |

| Legend: CMOS = CMOS-compatible input or output |                       |    | or output        | Ana                       | log = Analog input P = Power |                                     |  |  |  |

ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

O = Output PPS = Peripheral Pin Select

I = Input

## TABLE 1-19: SDHC PINOUT I/O DESCRIPTIONS

| Pin Name | Pin Number       |                             |                  | Pin  | Buffer |                              |                        |

|----------|------------------|-----------------------------|------------------|------|--------|------------------------------|------------------------|

|          | 169-pin<br>LFBGA | 176-pin<br>LQFP             | 288-pin<br>LFBGA | Туре | Туре   | Description                  |                        |

|          |                  |                             |                  |      | SDHC   |                              |                        |

| SDCK     | E4               | 54                          | E4               | 0    | —      | SD Serial Clock              |                        |

| SDCMD    | F1               | 70                          | K4               | 0    | _      | SD Command/Response          |                        |

| SDDATA0  | E2               | 64                          | H4               | I/O  | ST     | SD Serial Data 0             |                        |

| SDDATA1  | E3               | 56                          | G4               | I/O  | ST     | SD Serial Data 1             |                        |

| SDDATA2  | E1               | 65                          | J4               | I/O  | ST     | SD Serial Data 2             |                        |

| SDDATA3  | D1               | 55                          | F4               | I/O  | ST     | SD Serial Data 3/Card Detect |                        |

| SDCD     | D2               | 53                          | D4               | I    | ST     | SD Mechanical Card Detect    |                        |

| SDWP     | H12              | 141                         | N16              | I    | ST     | SD Write Protect             |                        |

| Legend:  |                  | MOS-compa<br>itt Trigger in | •                | •    |        | log = Analog input<br>Output | P = Power<br>I = Input |

ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

O = Output PPS = Peripheral Pin Select

TABLE 1-20: CTMU PINOUT I/O DESCRIPTIONS

| Pin Name | Pin Number                             |                 |                  | Din                                  | Buffer             |                           |           |  |  |

|----------|----------------------------------------|-----------------|------------------|--------------------------------------|--------------------|---------------------------|-----------|--|--|

|          | 169-pin<br>LFBGA                       | 176-pin<br>LQFP | 288-pin<br>LFBGA | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                    | Description               |           |  |  |

|          | Charge Time Measurement Unit           |                 |                  |                                      |                    |                           |           |  |  |

| CTED1    | B9                                     | 11              | A14              | I                                    | ST                 | CTMU External Edge Input  | t 1       |  |  |

| CTED2    | C12                                    | 169             | D18              | I                                    | ST                 | CTMU External Edge Input  | t 2       |  |  |

| CTPLS    | F7                                     | 9               | B15              | 0                                    |                    | CTMU Output Pulse         |           |  |  |

| Legend:  | CMOS = CMOS-compatible input or output |                 |                  | Ana                                  | log = Analog input | P = Power                 |           |  |  |

|          | ST = Schm                              | itt Trigger in  | put with CM      | IOS levels                           | O =                | Output                    | I = Input |  |  |

|          | TTL = Tran                             | sistor-transi   | stor Logic in    | put buffer                           | PPS                | S = Peripheral Pin Select |           |  |  |

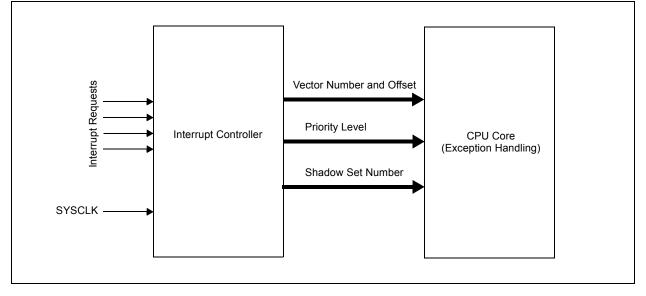

# 7.0 CPU EXCEPTIONS AND INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the PIC32MZ Graphics (DA) Family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Interrupt Controller" (DS60001108) and Section 50. "CPU for Devices with MIPS32<sup>®</sup> microAptiv<sup>™</sup> and M-Class Cores" (DS60001192), which are available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MZ DA devices generate interrupt requests in response to interrupt events from peripheral modules. The Interrupt Controller module exists outside of the CPU and prioritizes the interrupt events before presenting them to the CPU.

The CPU handles interrupt events as part of the exception handling mechanism, which is described in **Section 7.1 "CPU Exceptions"**.

The Interrupt Controller module includes the following features:

- Up to 210 interrupt sources and vectors with dedicated programmable offsets, eliminating the need for redirection

- · Single and multi-vector mode operations

- · Five external interrupts with edge polarity control

- · Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable sub-priority levels within each priority

- Seven shadow register sets that can be used for any priority level, eliminating software context switch and reducing interrupt latency

- Software can generate any interrupt

Figure 7-1 shows the block diagram for the Interrupt Controller and CPU exceptions.

## FIGURE 7-1: CPU EXCEPTIONS AND INTERRUPT CONTROLLER MODULE BLOCK DIAGRAM

# 8.1 Fail-Safe Clock Monitor (FSCM)

The PIC32MZ DA oscillator system includes a Fail-safe Clock Monitor (FSCM). The FSCM monitors the SYSCLK for continuous operation. If it detects that the SYSCLK has failed, it switches the SYSCLK over to the BFRC oscillator and triggers a NMI. The BFRC is an untuned 8 MHz oscillator that will drive the SYSCLK during FSCM event. When the NMI is executed, software can attempt to restart the main oscillator or shut down the system.

In Sleep mode both the SYSCLK and the FSCM halt, which prevents FSCM detection.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.04     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24     |                   |                   |                   | CHSSA<            | 31:24>            |                   |                  |                  |  |  |

| 00.40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16     |                   | CHSSA<23:16>      |                   |                   |                   |                   |                  |                  |  |  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8      |                   |                   |                   | CHSSA             | <15:8>            |                   |                  |                  |  |  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0       |                   |                   |                   | CHSSA             | <7:0>             |                   |                  |                  |  |  |

# REGISTER 10-10: DCHxSSA: DMA CHANNEL x SOURCE START ADDRESS REGISTER

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-0 CHSSA<31:0> Channel Source Start Address bits Channel source start address. Note: This must be the physical address of the source.

#### REGISTER 10-11: DCHxDSA: DMA CHANNEL x DESTINATION START ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | CHDSA<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | CHDSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | CHDSA<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              |                   |                   |                   | CHDSA             | <7:0>             |                   |                  |                  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 CHDSA<31:0>: Channel Destination Start Address bits Channel destination start address.

Note: This must be the physical address of the destination.

| REGIST   | ER 20-1: RTCCON: REAL-TIME CLOCK AND CALENDAR CONTROL REGISTER                                                                                                                                                                 |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10-9 | RTCCLKSEL<1:0>: RTCC Clock Select bits                                                                                                                                                                                         |

|          | When a new value is written to these bits, the Seconds Value register should also be written to properly reset the clock prescalers in the RTCC.                                                                               |

|          | 11 = Reserved                                                                                                                                                                                                                  |

|          | 10 = Reserved                                                                                                                                                                                                                  |

|          | <ul><li>01 = RTCC uses the external 32.768 kHz Secondary Oscillator (SOSC)</li><li>00 = RTCC uses the internal 32 kHz oscillator (LPRC)</li></ul>                                                                              |

| bit 8-7  | RTCOUTSEL<1:0>: RTCC Output Data Select bits <sup>(2)</sup>                                                                                                                                                                    |

|          | 11 = Reserved                                                                                                                                                                                                                  |

|          | 10 = RTCC Clock is presented on the RTCC pin                                                                                                                                                                                   |

|          | 01 = Seconds Clock is presented on the RTCC pin                                                                                                                                                                                |

|          | 00 = Alarm Pulse is presented on the RTCC pin when the alarm interrupt is triggered                                                                                                                                            |

| bit 6    | RTCCLKON: RTCC Clock Enable Status bit                                                                                                                                                                                         |

|          | 1 = RTCC Clock is actively running                                                                                                                                                                                             |

|          | 0 = RTCC Clock is not running                                                                                                                                                                                                  |

| bit 5-4  | Unimplemented: Read as '0'                                                                                                                                                                                                     |

| bit 3    | RTCWREN: Real-Time Clock Value Registers Write Enable bit <sup>(3)</sup>                                                                                                                                                       |

|          | 1 = Real-Time Clock Value registers can be written to by the user                                                                                                                                                              |

|          | 0 = Real-Time Clock Value registers are locked out from being written to by the user                                                                                                                                           |

| bit 2    | RTCSYNC: Real-Time Clock Value Registers Read Synchronization bit                                                                                                                                                              |

|          | 1 = Real-time clock value registers can change while reading (due to a rollover ripple that results in an invalid data read). If the register is read twice and results in the same data, the data can be assumed to be valid. |

|          | 0 = Real-time clock value registers can be read without concern about a rollover ripple                                                                                                                                        |

| bit 1    | HALFSEC: Half-Second Status bit <sup>(4)</sup>                                                                                                                                                                                 |

|          | 1 = Second half period of a second                                                                                                                                                                                             |

|          | 0 = First half period of a second                                                                                                                                                                                              |

| bit 0    | RTCOE: RTCC Output Enable bit                                                                                                                                                                                                  |

|          |                                                                                                                                                                                                                                |

- 1 = RTCC output is enabled

- 0 = RTCC output is not enabled

- **Note 1:** The ON bit is only writable when RTCWREN = 1.

- **2:** Requires RTCOE = 1 (RTCCON<0>) for the output to be active.

- 3: The RTCWREN bit can be set only when the write sequence is enabled.

- 4: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

Note: This register is reset only on a Power-on Reset (POR).

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-----------------------|-----------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                     | _                     | _                 | _                 | _                 | _                 | _                | _                |  |  |

| 00.40        | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                     | —                     | _                 | _                 | —                 | —                 | —                | —                |  |  |

|              | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | CS2 <sup>(1)</sup>    | CS1 <sup>(3)</sup>    |                   |                   |                   |                   |                  |                  |  |  |

|              | ADDR15 <sup>(2)</sup> | ADDR14 <sup>(4)</sup> |                   | ADDR<13:8>        |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              | ADDR<7:0>             |                       |                   |                   |                   |                   |                  |                  |  |  |

#### REGISTER 25-3: PMADDR: PARALLEL PORT ADDRESS REGISTER

## Legend:

| Logona.           |                  |                                         |  |

|-------------------|------------------|-----------------------------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |  |

#### bit 31-16 **Unimplemented:** Read as '0'

- bit 15 **CS2:** Chip Select 2 bit<sup>(1)</sup>

- 1 = Chip Select 2 is active

- 0 = Chip Select 2 is inactive

- bit 15 ADDR<15>: Target Address bit 15<sup>(2)</sup>

- bit 14 CS1: Chip Select 1 bit<sup>(3)</sup>

- 1 = Chip Select 1 is active 0 = Chip Select 1 is inactive

- bit 14 ADDR<14>: Target Address bit 14<sup>(4)</sup>

- bit 13-0 ADDR<13:0>: Address bits

- **Note 1:** When the CSF<1:0> bits (PMCON<7:6>) = 10 or 01.

- **2:** When the CSF<1:0> bits (PMCON<7:6>) = 00.

- **3:** When the CSF<1:0> bits (PMCON<7:6>) = 10.

- **4:** When the CSF<1:0> bits (PMCON<7:6>) = 00 or 01.

**Note:** If the DUALBUF bit (PMCON<17>) = 0, the bits in this register control both read and write target addressing. If the DUALBUF bit = 1, the bits in this register are not used. In this instance, use the PMRADDR register for Read operations and the PMWADDR register for Write operations.

Table 27-12 shows the Security Association control word structure.

The Crypto Engine fetches different structures for different flows and ensures that hardware fetches minimum words from SA required for processing. The structure is ready for hardware optimal data fetches.

| Bit<br>Range | Bit<br>31/23/15/7              | Bit<br>30/22/14/6                                                                                                                                                                                                                                | Bit<br>29/21/13/5              | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31-24        |                                |                                                                                                                                                                                                                                                  | VERIFY                         |                   | NO_RX             | OR_EN             | ICVONLY          | IRFLAG           |  |  |  |

| 23-16        | LNC                            | LOADIV                                                                                                                                                                                                                                           | FB                             | FLAGS             | —                 | —                 |                  | ALGO<6>          |  |  |  |

| 15-8         |                                |                                                                                                                                                                                                                                                  | ALGO                           | <5:0>             |                   |                   | ENC              | KEY<br>SIZE<1>   |  |  |  |

| 7-0          | KEY<br>SIZE<0>                 | MU                                                                                                                                                                                                                                               | ILTITASK<2:                    | 0>                |                   | CRYPTOA           | LGO<3:0>         |                  |  |  |  |

| bit 31-30    | Reserved:                      | Do not use                                                                                                                                                                                                                                       |                                |                   |                   |                   |                  |                  |  |  |  |

| bit 29       | 1 = NIST pr                    | ERIFY: NIST Procedure Verification Setting<br>= NIST procedures are to be used<br>= Do not use NIST procedures                                                                                                                                   |                                |                   |                   |                   |                  |                  |  |  |  |

| bit 28       | Reserved:                      | Do not use                                                                                                                                                                                                                                       |                                |                   |                   |                   |                  |                  |  |  |  |

| bit 27       | 1 = Only ca                    | D_RX: Receive DMA Control Setting<br>= Only calculate ICV for authentication calculations<br>= Normal processing                                                                                                                                 |                                |                   |                   |                   |                  |                  |  |  |  |

| bit 26       | 1 = OR the                     | <b>DR_EN:</b> OR Register Bits Enable Setting<br>= OR the register bits with the internal value of the CSR register<br>= Normal processing                                                                                                       |                                |                   |                   |                   |                  |                  |  |  |  |

| bit 25       | This affects<br>1 = Only thr   | <b>ICVONLY:</b> Incomplete Check Value Only Flag<br>This affects the SHA-1 algorithm only. It has no effect on the AES algorithm.<br>1 = Only three words of the HMAC result are available<br>0 = All results from the HMAC result are available |                                |                   |                   |                   |                  |                  |  |  |  |

| bit 24       | This bit is se<br>1 = Save the | nmediate Res<br>et when the in<br>e immediate r<br>save the imme                                                                                                                                                                                 | nmediate res<br>result for has | ult for hashir    | ng is request     | ed.               |                  |                  |  |  |  |

| bit 23       | 1 = Load a                     | New Keys Se<br>new set of key<br>oad new keys                                                                                                                                                                                                    | ys for encryp                  | tion and auth     | nentication       |                   |                  |                  |  |  |  |

| bit 22       |                                | oad IV Setting<br>e IV from this<br>next IV                                                                                                                                                                                                      |                                | ociation          |                   |                   |                  |                  |  |  |  |

| bit 21       | This bit indic<br>1 = Indicate | <ul> <li>B: First Block Setting</li> <li>his bit indicates that this is the first block of data to feed the IV value.</li> <li>Indicates this is the first block of data</li> <li>Indicates this is not the first block of data</li> </ul>       |                                |                   |                   |                   |                  |                  |  |  |  |

| bit 20       | 1 = Security                   | coming/Outgo<br>Association i<br>Association i                                                                                                                                                                                                   | s associated                   | with an outg      |                   |                   |                  |                  |  |  |  |

| bit 19-17    | Reserved:                      | Do not use                                                                                                                                                                                                                                       |                                |                   |                   |                   |                  |                  |  |  |  |

## FIGURE 27-12: FORMAT OF SA\_CTRL

#### REGISTER 28-5: RNGSEEDx: TRUE RANDOM NUMBER GENERATOR SEED REGISTER 'x'

|              | ('2               | x' = 1 OR 2)      |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04.04        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 31:24        |                   |                   |                   | SEED<3            | 31:24>            |                   |                  |                  |

| 00.40        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 23:16        |                   |                   |                   | SEED<2            | 23:16>            |                   |                  |                  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         |                   |                   |                   | SEED<             | 15:8>             |                   |                  |                  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | SEED<             | <7:0>             |                   |                  |                  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 **SEED<31:0>:** TRNG MSb/LSb Value bits (RNGSEED1 = LSb, RNGSEED2 = MSb)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 |           |       | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-----------|-------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0       | U-0   | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | _                 | —         | —     | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0       | U-0   | U-0              | U-0              |

| 23:16        | _                 | —                 | _                 | _                 | _         | —     | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0       | U-0   | U-0              | U-0              |

| 15:8         | —                 | —                 | _                 | _                 | —         | _     | _                | _                |

| 7.0          | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0     | R/W-0 | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   |                   | RCNT<6:0> |       |                  |                  |

#### REGISTER 28-6: RNGCNT: TRUE RANDOM NUMBER GENERATOR COUNT REGISTER

| Legend:           |                  |                          |                    |  |

|-------------------|------------------|--------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

bit 31-7 Unimplemented: Read as '0'

bit 6-0 RCNT<6:0>: Number of Valid TRNG MSB 32 bits

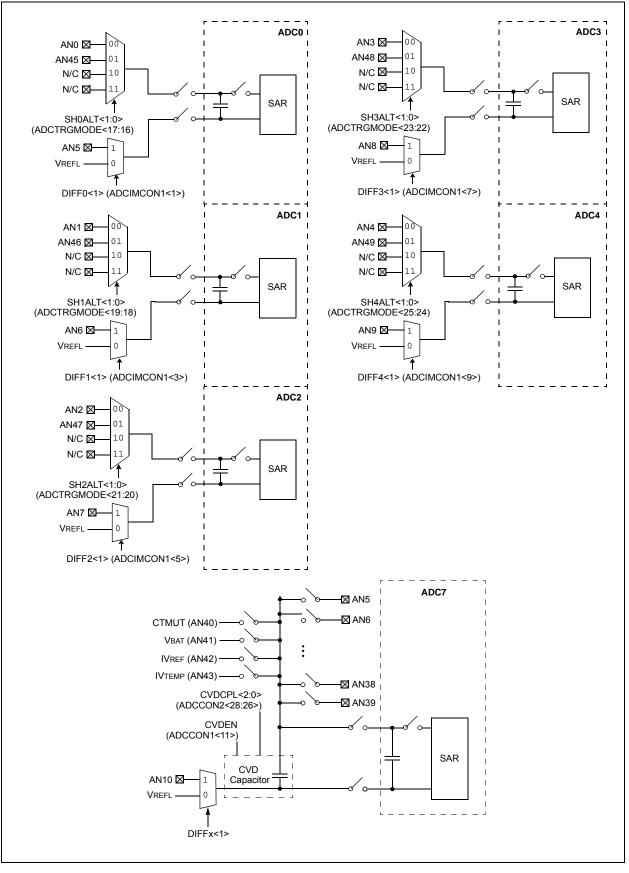

# FIGURE 29-2: S&H BLOCK DIAGRAM

# **PIC32MZ Graphics (DA) Family**

## REGISTER 29-3: ADCCON3: ADC CONTROL REGISTER 3 (CONTINUED)

bit 18 **DIGEN2:** ADC2 Digital Enable bit 1 = ADC2 is digital enabled

|             | 0       |          |

|-------------|---------|----------|

| 0 = ADC2 is | digital | disabled |

bit 17 DIGEN1: ADC1 Digital Enable bit

1 = ADC1 is digital enabled

0 = ADC1 is digital disabled

- bit 16 **DIGEN0:** ADC0 Digital Enable bit 1 = ADC0 is digital enabled

- 0 = ADC0 is digital disabled

- bit 15-13 VREFSEL<2:0>: Voltage Reference (VREF) Input Selection bits

| VREFSEL<2:0> | ADREF+         | ADREF-         |  |  |

|--------------|----------------|----------------|--|--|

| 111          | AVDD           | Internal VREFL |  |  |

| 110          | Internal VREFH | AVss           |  |  |

| 101          | Internal VREFH | External VREFL |  |  |

| 100          | Internal VREFH | Internal VREFL |  |  |

| 011          | Internal VREFH | External VREFL |  |  |

| 010          | AVdd           | External VREFL |  |  |

| 001          | External VREFH | AVss           |  |  |

| 000          | AVdd           | AVss           |  |  |

bit 12 TRGSUSP: Trigger Suspend bit

1 = Triggers are blocked from starting a new analog-to-digital conversion, but the ADC module is not disabled

0 = Triggers are not blocked

- bit 11 UPDIEN: Update Ready Interrupt Enable bit

- 1 = Interrupt will be generated when the UPDRDY bit is set by hardware

- 0 = No interrupt is generated

- bit 10 **UPDRDY:** ADC Update Ready Status bit

1 = ADC SFRs can be updated

- 0 = ADC SFRs cannot be updated

- **Note:** This bit is only active while the TRGSUSP bit is set and there are no more running conversions of any ADC modules.

- bit 9 SAMP: Class 2 and Class 3 Analog Input Sampling Enable bit<sup>(1,2,3,4)</sup>

- 1 = The ADC S&H amplifier is sampling

- 0 = The ADC S&H amplifier is holding

- bit 8 RQCNVRT: Individual ADC Input Conversion Request bit

This bit and its associated ADINSEL<5:0> bits enable the user to individually request an analog-to-digital conversion of an analog input through software.

1 = Trigger the conversion of the selected ADC input as specified by the ADINSEL<5:0> bits

0 = Do not trigger the conversion

**Note:** This bit is automatically cleared in the next ADC clock cycle.

- **Note 1:** The SAMP bit has the highest priority and setting this bit will keep the S&H circuit in Sample mode until the bit is cleared. Also, usage of the SAMP bit will cause settings of SAMC<9:0> bits (ADCCON2<25:16>) to be ignored.

- 2: The SAMP bit only connects Class 2 and Class 3 analog inputs to the shared ADC, ADC7. All Class 1 analog inputs are not affected by the SAMP bit.

- **3:** The SAMP bit is not a self-clearing bit and it is the responsibility of application software to first clear this bit and only after setting the RQCNVRT bit to start the analog-to-digital conversion.

- 4: Normally, when the SAMP and RQCNVRT bits are used by software routines, all TRGSRCx<4:0> bits and STRGSRC<4:0> bits should be set to '00000' to disable all external hardware triggers and prevent them from interfering with the software-controlled sampling command signal SAMP and with the software-controlled trigger RQCNVRT.

#### 30.1 **CAN Control Registers**

The 'i' shown in register names denotes Note: CAN1 or CAN2.

#### TABLE 30-1: CAN1 REGISTER SUMMARY FOR PIC32MZXXXXECF AND PIC32MZXXXXECH DEVICES

| ess                         |                                 |           |          |                                                                                                                                               |                      |           |          |            |           | Bit       | s        |          |          |          |           |            |           |          |            |

|-----------------------------|---------------------------------|-----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------|----------|------------|-----------|-----------|----------|----------|----------|----------|-----------|------------|-----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15    | 30/14                                                                                                                                         | 29/13                | 28/12     | 27/11    | 26/10      | 25/9      | 24/8      | 23/7     | 22/6     | 21/5     | 20/4     | 19/3      | 18/2       | 17/1      | 16/0     | All Resets |

| 0000                        | C1CON                           | 31:16     |          | —                                                                                                                                             | —                    | -         | ABAT     |            | REQOP<2:0 | >         | (        | PMOD<2:0 | >        | CANCAP   | _         | —          | _         | —        | 0480       |

| 0000                        | 01001                           | 15:0      | ON       | _                                                                                                                                             | SIDLE                | _         | CANBUSY  | _          | —         | _         | —        | —        | —        |          | D         | NCNT<4:0>  | >         |          | 0000       |

| 0010                        | C1CFG                           | 31:16     | _        |                                                                                                                                               | _                    | —         | _        |            | —         | _         |          | WAKFIL   | —        | _        | _         | S          | EG2PH<2:0 | >        | 0000       |

| 0010                        | CICEG                           | 15:0      | SEG2PHTS | SAM                                                                                                                                           | S                    | EG1PH<2:0 | >        |            | PRSEG<2:0 | >         | SJW      | <1:0>    |          |          | BRP<      | :5:0>      |           |          | 0000       |

| 0020                        | C1INT                           | 31:16     | IVRIE    | WAKIE                                                                                                                                         | CERRIE               | SERRIE    | RBOVIE   |            | -         |           | _        | _        | —        |          | MODIE     | CTMRIE     | RBIE      | TBIE     | 0000       |

| 0020                        | CHINT                           | 15:0      | IVRIF    | WAKIF                                                                                                                                         | CERRIF               | SERRIF    | RBOVIF   |            |           |           | _        | _        | _        |          | MODIF     | CTMRIF     | RBIF      | TBIF     | 0000       |

| 0030                        | C1VEC                           | 31:16     |          | _                                                                                                                                             | _                    |           | -        | -          | _         |           | -        | _        | _        | -        | -         | _          | _         | _        | 0000       |

| 0030                        | CIVEC                           | 15:0      | _        | _                                                                                                                                             | _                    |           |          | FILHIT<4:0 | >         |           | —        |          |          | 10       | CODE<6:0> |            |           |          | 0040       |

| 0040                        |                                 | 31:16     | _        |                                                                                                                                               | _                    | —         | _        | _          | —         | _         | _        |          | TXBO     | TXBP     | RXBP      | TXWARN     | RXWARN    | EWARN    | 0000       |

| 0040                        | C1TREC                          | 15:0      |          |                                                                                                                                               |                      | TERRC     | NT<7:0>  |            |           |           |          |          |          | RERRCN   | T<7:0>    |            |           |          | 0000       |

| 0050                        | 0450747                         | 31:16     | FIFOIP31 | FIFOIP30                                                                                                                                      | FIFOIP29             | FIFOIP28  | FIFOIP27 | FIFOIP26   | FIFOIP25  | FIFOIP24  | FIFOIP23 | FIFOIP22 | FIFOIP21 | FIFOIP20 | FIFOIP19  | FIFOIP18   | FIFOIP17  | FIFOIP16 | ; 0000     |

| 0050 C1FSTA                 | C1FSTAT                         | 15:0      | FIFOIP15 | FIFOIP14                                                                                                                                      | FIFOIP13             | FIFOIP12  | FIFOIP11 | FIFOIP10   | FIFOIP9   | FIFOIP8   | FIFOIP7  | FIFOIP6  | FIFOIP5  | FIFOIP4  | FIFOIP3   | FIFOIP2    | FIFOIP1   | FIFOIP0  | 0000       |

|                             | 0.001/01/5                      | 31:16     | RXOVF31  | RXOVF30                                                                                                                                       | RXOVF29              | RXOVF28   | RXOVF27  | RXOVF26    | RXOVF25   | RXOVF24   | RXOVF23  | RXOVF22  | RXOVF21  | RXOVF20  | RXOVF19   | RXOVF18    | RXOVF17   | RXOVF16  | 3 0000     |

| 0060                        | C1RXOVF                         | 15:0      | RXOVF15  | RXOVF14                                                                                                                                       | RXOVF13              | RXOVF12   | RXOVF11  | RXOVF10    | RXOVF9    | RXOVF8    | RXOVF7   | RXOVF6   | RXOVF5   | RXOVF4   | RXOVF3    | RXOVF2     | RXOVF1    | RXOVF0   | 0000       |

|                             |                                 | 31:16     |          |                                                                                                                                               |                      |           |          |            |           | CANTS<    | <15:0>   |          |          |          |           |            |           |          | 0000       |

| 0070                        | C1TMR                           | 15:0      |          |                                                                                                                                               |                      |           |          |            | CA        | NTSPRE<15 | :0>      |          |          |          |           |            |           |          | 0000       |

|                             |                                 | 31:16     |          |                                                                                                                                               |                      |           |          | SID<10:0>  |           |           |          |          |          |          | MIDE      | _          | EID<1     | 7:16>    | xxxx       |

| 0080                        | C1RXM0                          | 15:0      |          |                                                                                                                                               |                      |           |          |            |           | EID<1     | 5:0>     |          |          |          |           |            |           |          | xxxx       |

|                             |                                 | 31:16     |          |                                                                                                                                               |                      |           |          | SID<10:0>  |           |           |          |          |          |          | MIDE      | _          | EID<1     | 7:16>    | xxxx       |

| 0090                        | C1RXM1                          | 15:0      |          |                                                                                                                                               |                      |           |          |            |           | EID<1     | 5.0>     |          |          |          |           |            |           |          | XXXX       |

|                             |                                 | 31:16     |          |                                                                                                                                               |                      |           |          | SID<10:0>  |           | 2.0       | 0.0      |          |          |          | MIDE      | _          | EID<1     | 7.16>    | xxxx       |

| 00A0                        | C1RXM2                          | 15:0      |          |                                                                                                                                               |                      |           |          | 010 410.04 |           | EID<1     | 5.0>     |          |          |          | NIIDE     |            |           | 1.10-    | XXXX       |

|                             |                                 | 31:16     |          |                                                                                                                                               |                      |           |          | SID<10:0>  |           | LIDYI     | 5.02     |          |          |          | MIDE      | _          | EID<1     | 7:16>    |            |

| 00B0                        | C1RXM3                          | 15:0      |          |                                                                                                                                               |                      |           |          | 510~10.02  |           |           |          |          |          |          | IVIIDE    |            | EID       | 7.10-    | XXXX       |

|                             |                                 |           |          | EID<15:0>         xxxx           TEN3         MSEL3<1:0>         FSEL3<4:0>         FLTEN2         MSEL2<1:0>         FSEL2<4:0>         0000 |                      |           |          |            |           |           |          | -        |          |          |           |            |           |          |            |

| 00C0                        | C1FLTCON0                       | 31:16     | FLTEN3   | -                                                                                                                                             |                      |           |          | FSEL3<4:0  |           |           | FLTEN2   |          |          |          |           | SEL2<4:0>  |           |          | 0000       |

|                             |                                 | 15:0      | FLTEN1   | MSEL                                                                                                                                          |                      |           |          | FSEL1<4:0  |           |           | FLTEN0   | -        | 0<1:0>   |          |           | SEL0<4:0>  |           |          | 0000       |

| 00D0                        | C1FLTCON1                       | 31:16     | FLTEN7   | -                                                                                                                                             | 7<1:0>               |           |          | FSEL7<4:0  |           |           | FLTEN6   |          | 6<1:0>   |          |           | SEL6<4:0>  |           |          | 0000       |

|                             | <u> </u>                        | 15:0      | FLTEN5   | MSEL                                                                                                                                          |                      |           |          | FSEL5<4:0  |           |           | FLTEN4   |          | 4<1:0>   |          |           | SEL4<4:0>  |           |          | 0000       |

| 00E0                        | C1FLTCON2                       | 31:16     |          |                                                                                                                                               | 11<1:0>              |           |          | FSEL11<4:0 |           |           | FLTEN10  |          | 10<1:0>  |          |           | SEL10<4:0> |           |          | 0000       |

|                             |                                 | 15:0      | FLTEN9   | MSEL                                                                                                                                          | 9<1:0><br>mplemented |           |          | FSEL9<4:0  |           |           | FLTEN8   | MSEL     | 8<1:0>   |          | F         | SEL8<4:0>  |           |          | 0000       |

DS60001361F-page 492

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information. Note 1:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | S/HC-0            | R/W-1             | R/W-0            | R/W-0            |

| 31:24        | —                 | —                 | _                 | _                 | ABAT              | F                 | REQOP<2:0>       | <b>`</b>         |

| 00.40        | R-1               | R-0               | R-0               | R/W-0             | U-0               | U-0               | U-0              | U-0              |

| 23:16        | C                 | OPMOD<2:0>        |                   | CANCAP            | —                 | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | R-0               | U-0               | U-0              | U-0              |

| 15:8         | 0N <sup>(1)</sup> | —                 | SIDLE             | -                 | CANBUSY           | _                 | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | _                 |                   |                   |                   | DNCNT<4:0>        |                  |                  |

#### REGISTER 30-1: CICON: CAN MODULE CONTROL REGISTER

| Legend:              | HC = Hardware Clear          | S = Settable bit      |                  |

|----------------------|------------------------------|-----------------------|------------------|

| R = Readable bit     | W = Writable bit             | P = Programmable bit  | r = Reserved bit |

| U = Unimplemented bi | t  -n = Bit Value at POR: (' | 0', '1', x = Unknown) |                  |

#### bit 31-28 Unimplemented: Read as '0'

#### bit 27 **ABAT:** Abort All Pending Transmissions bit

- 1 = Signal all transmit buffers to abort transmission

- 0 = Module will clear this bit when all transmissions aborted

#### bit 26-24 REQOP<2:0>: Request Operation Mode bits

- 111 = Set Listen All Messages mode

- 110 = Reserved Do not use

- 101 = Reserved Do not use

- 100 = Set Configuration mode

- 011 = Set Listen Only mode

- 010 = Set Loopback mode

- 001 = Set Disable mode

- 000 = Set Normal Operation mode

#### bit 23-21 OPMOD<2:0>: Operation Mode Status bits

- 111 = Module is in Listen All Messages mode

- 110 = Reserved

- 101 = Reserved

- 100 = Module is in Configuration mode

- 011 = Module is in Listen Only mode

- 010 = Module is in Loopback mode

- 001 = Module is in Disable mode

- 000 = Module is in Normal Operation mode

#### bit 20 CANCAP: CAN Message Receive Time Stamp Timer Capture Enable bit

- 1 = CANTMR value is stored on valid message reception and is stored with the message

- 0 = Disable CAN message receive time stamp timer capture and stop CANTMR to conserve power

- bit 19-16 Unimplemented: Read as '0'

- bit 15 **ON:** CAN On bit<sup>(1)</sup>

- 1 = CAN module is enabled

- 0 = CAN module is disabled

- bit 14 Unimplemented: Read as '0'

- **Note 1:** If the user application clears this bit, it may take a number of cycles before the CAN module completes the current transaction and responds to this request. The user application should poll the CANBUSY bit to verify that the request has been honored.

#### REGISTER 30-20: CiFIFOCONn: CAN FIFO CONTROL REGISTER (n = 0 THROUGH 31)

- TXABAT: Message Aborted bit<sup>(2)</sup> bit 6 1 = Message was aborted 0 = Message completed successfully bit 5 TXLARB: Message Lost Arbitration bit<sup>(3)</sup> 1 = Message lost arbitration while being sent 0 = Message did not loose arbitration while being sent TXERR: Error Detected During Transmission bit<sup>(3)</sup> bit 4 1 = A bus error occured while the message was being sent 0 = A bus error did not occur while the message was being sent bit 3 **TXREQ:** Message Send Request TXEN = 1: (FIFO configured as a Transmit FIFO) Setting this bit to '1' requests sending a message. The bit will automatically clear when all the messages queued in the FIFO are successfully sent Clearing the bit to '0' while set ('1') will request a message abort. TXEN = 0: (FIFO configured as a Receive FIFO) This bit has no effect. bit 2 RTREN: Auto RTR Enable bit 1 = When a remote transmit is received, TXREQ will be set 0 = When a remote transmit is received, TXREQ will be unaffected bit 1-0 TXPR<1:0>: Message Transmit Priority bits 11 = Highest Message Priority 10 = High Intermediate Message Priority 01 = Low Intermediate Message Priority 00 = Lowest Message Priority Note 1: These bits can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> bits (CiCON<23:21>) = 100).

- 2: This bit is updated when a message completes (or aborts) or when the FIFO is reset.

- 3: This bit is reset on any read of this register or when the FIFO is reset.

# 35.1 CTMU Control Registers

# TABLE 35-1: CTMU REGISTER MAP

| dress<br>#)              |                                 | е         |         |         |          |       |         |          |          | Bits     |         |         |        |       |          |      |      |       | s         |

|--------------------------|---------------------------------|-----------|---------|---------|----------|-------|---------|----------|----------|----------|---------|---------|--------|-------|----------|------|------|-------|-----------|

| Virtual Addr<br>(BF84_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13    | 28/12 | 27/11   | 26/10    | 25/9     | 24/8     | 23/7    | 22/6    | 21/5   | 20/4  | 19/3     | 18/2 | 17/1 | 16/0  | All Reset |

| <u></u>                  | CTMUCON                         | 31:16     | EDG1MOD | EDG1POL |          | EDG1S | EL<3:0> |          | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL |        | EDG2S | SEL<3:0> |      |      |       | 0000      |

| C200                     | CTWOCON                         | 15:0      | ON      | _       | CTMUSIDL | TGEN  | EDGEN   | EDGSEQEN | IDISSEN  | CTTRIG   |         |         | ITRIM• | <5:0> |          |      | IRNG | <1:0> | 0000      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 11.2 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-1             | R/W-0            | R/W-0            |  |  |

| 31.24        | BIGENDIAN         | _                 | —                 | —                 |                   | MAXBUR            | RST<3:0>         |                  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23.10        | —                 | _                 | —                 | – <u> </u>        |                   | RDATENI           | ATENDLY<3:0>     |                  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15.0         | —                 | _                 | —                 | —                 | —                 | —                 | _                | —                |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   | NXTDATAV          | /DLY<3:0>         |                   |                   | NXTDATRO          | QDLY<3:0>        |                  |  |  |

#### **REGISTER 38-18: DDRXFERCFG: DDR TRANSFER CONFIGURATION REGISTER**

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

- bit 31 BIGENDIAN: Big Endian bit

- 1 = Data is big endian format

- 0 = Data is little endian format

- bit 30-28 Unimplemented: Read as '0'

- bit 27-24 **MAXBURST<3:0>:** Maximum Command Burst Count bits These bits specify the maximum number of commands that can be written to the DDR controller in Burst

- bit 23-20 **Unimplemented:** Read as '0'

mode.

bit 19-16 **RDATENDLY<3:0>:** PHY Read Data Enable Delay bits

These bits specify the minimum number of clocks Required between issuing a Read command to the PHY and when the "read data enable" signal to the PHY is asserted.

- bit 15-8 **Unimplemented:** Read as '0'

- bit 7-4 NXTDATAVDLY<3:0>: Next Data Available Delay bits

These bits specify the minimum number of clock cycles required between issuing a Read command and the read data being received.

#### bit 3-0 NXTDATRQDLY<3:0>: Next Data Request Delay bits

These bits specify the minimum number of clock cycles required between issuing a Write command and the write data transfer handshake signal "next data request".

# 43.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

# 43.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

## 43.8 MPLAB ICD 3 In-Circuit Debugger System