Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Petails                   |                                                                                               |

|---------------------------|-----------------------------------------------------------------------------------------------|

| roduct Status             | Active                                                                                        |

| Core Processor            | MIPS32® microAptiv™                                                                           |

| Core Size                 | 32-Bit Single-Core                                                                            |

| peed                      | 200MHz                                                                                        |

| Connectivity              | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, SQI, UART/USART, USB OTG |

| eripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT                            |

| lumber of I/O             | 120                                                                                           |

| rogram Memory Size        | 2MB (2M x 8)                                                                                  |

| rogram Memory Type        | FLASH                                                                                         |

| EPROM Size                | -                                                                                             |

| AM Size                   | 640K x 8                                                                                      |

| oltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                   |

| ata Converters            | A/D 45x12b                                                                                    |

| scillator Type            | Internal                                                                                      |

| perating Temperature      | -40°C ~ 85°C (TA)                                                                             |

| lounting Type             | Surface Mount                                                                                 |

| ackage / Case             | 176-LQFP Exposed Pad                                                                          |

| upplier Device Package    | 176-LQFP (20x20)                                                                              |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz2064dah176t-i-2              |

TABLE 1-22: DDR2 SDRAM CONTROLLER PINOUT I/O DESCRIPTIONS (CONTINUED)

|          |                  | Pin Number      |                  | D:          | Doffee         |               |

|----------|------------------|-----------------|------------------|-------------|----------------|---------------|

| Pin Name | 169-pin<br>LFBGA | 176-pin<br>LQFP | 288-pin<br>LFBGA | Pin<br>Type | Buffer<br>Type | Description   |

| DDRDQ0   | DDR Internal     | DDR Internal    | F1               | I/O         | SSTL           | DDR2 Data Bus |

| DDRDQ1   | to the Package   | to the Package  | J3               | I/O         | SSTL           |               |

| DDRDQ2   |                  |                 | H1               | I/O         | SSTL           |               |

| DDRDQ3   |                  |                 | G1               | I/O         | SSTL           |               |

| DDRDQ4   |                  |                 | G2               | I/O         | SSTL           |               |

| DDRDQ5   |                  |                 | H2               | I/O         | SSTL           |               |

| DDRDQ6   |                  |                 | НЗ               | I/O         | SSTL           |               |

| DDRDQ7   |                  |                 | F2               | I/O         | SSTL           |               |

| DDRDQ8   |                  |                 | C1               | I/O         | SSTL           | DDR2 Data Bus |

| DDRDQ9   |                  |                 | C3               | I/O         | SSTL           |               |

| DDRDQ10  |                  |                 | D2               | I/O         | SSTL           |               |

| DDRDQ11  |                  |                 | F3               | I/O         | SSTL           |               |

| DDRDQ12  |                  |                 | E3               | I/O         | SSTL           |               |

| DDRDQ13  |                  |                 | D1               | I/O         | SSTL           |               |

| DDRDQ14  |                  |                 | В3               | I/O         | SSTL           |               |

| DDRDQ15  |                  |                 | C2               | I/O         | SSTL           |               |

**Legend:** CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels

Analog = Analog input

O = Output

P = Power I = Input

TTL = Transistor-transistor Logic input buffer

PPS = Peripheral Pin Select

SSTL = Stub Series Terminated Logic

TABLE 4-1: ADDRESS MAPPING TABLE

| Memory        | Size                  | Region End<br>Address (KSEG1) | Region End<br>Address (KSEG0) | Region End<br>Address (Physical) |

|---------------|-----------------------|-------------------------------|-------------------------------|----------------------------------|

| Program Flash | 2 MB                  | 0xBD1FFFFF                    | 0x9D1FFFFF                    | 0x1D1FFFFF                       |

| Program Plasm | 1 MB                  | 0xBD0FFFFF                    | 0x9D0FFFFF                    | 0x1D0FFFFF                       |

|               | EXT <sup>(1)</sup>    | 0xAFFFFFF                     | 0x8FFFFFF                     | 0x0FFFFFF                        |

| DDR2 SDRAM    | 32 MB <sup>(5)</sup>  | 0xA9FFFFF                     | 0x89FFFFF                     | 0x09FFFFFF                       |

|               | (2)                   | Reserved                      | Reserved                      | Reserved                         |

| RAM           | 640 KB <sup>(3)</sup> | 0xA009FFFF                    | 0x8009FFFF                    | 0x0009FFFF                       |

| KAW           | 256 KB <sup>(4)</sup> | 0xA003FFFF                    | 0x8003FFFF                    | 0x0003FFFF                       |

- **Note 1:** External DDR2 SDRAM can be up to 128 MB, EXTDDRSIZE<3:0> bits (DEVCFG3<19:16>) should be set, and the region end address should be scaled accordingly.

- 2: Devices without the DDR2 option.

- 3: Devices with 640 KB RAM contain SRAM Bank 1 (256 KB) and SRAM Bank 2 (384 KB).

- 4: Devices with 256 KB RAM contain SRAM Bank 1 (128 KB) and SRAM Bank 2 (128 KB).

- 5: Refer to 4.2 "DDR2 SDRAM" for DDR2 SDRAM features, which are applicable to devices with internal DDR2 SDRAM.

#### **REGISTER 4-11:** SBTxREGy: SYSTEM BUS TARGET 'x' REGION 'y' REGISTER ('x' = 0-13; 'v' = 0-8)

|              |                   | ,                 | <del>, ,</del> ,  |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | R/W0              | R/W-0             | R/W0              | R/W-0             | R/W0              | R/W-0             | R/W0             | R/W-0            |

| 31:24        |                   |                   |                   | BASE              | <21:14>           |                   |                  |                  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        |                   |                   |                   | BASE              | E<13:6>           |                   |                  |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | U-0              |

| 15:8         |                   |                   | BAS               | E<5:0>            |                   |                   | PRI              | _                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |

| 7:0          |                   |                   | SIZE<4:0>         |                   |                   | _                 | _                | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared

bit 31-10 BASE<21:0>: Region Base Address bits

bit 9 PRI: Region Priority Level bit

> 1 = Level 2 0 = Level 1

bit 8 Unimplemented: Read as '0'

bit 7-3 SIZE<4:0>: Region Size bits

Permissions for a region are only active is the SIZE is non-zero. 11111 = Region size =  $2^{(SIZE-1)}$  x 1024 (bytes)

00001 = Region size =  $2^{(SIZE - 1)} \times 1024$  (bytes)

00000 = Region is not present

bit 2-0 Unimplemented: Read as '0'

Note 1: Refer to Table 4-8 for the list of available targets and their descriptions.

2: For some target regions, certain bits in this register are read-only with preset values. See Table 4-8 for more information.

#### REGISTER 8-8: CLKSTAT: OSCILLATOR CLOCK STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | -                 | _                 | _                 | -                 |                  | _                |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | -                 | _                | _                |

| 7.0          | R-0               | U-0               | R-0               | R-0               | U-0               | R-0               | U-0              | R-0              |

| 7:0          | SPLLRDY           | _                 | LPRCRDY           | SOSCRDY           | _                 | POSCRDY           | _                | FRCRDY           |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 SPLLRDY: System PLL (SPLL) Ready Status bit

1 = SPLL is ready0 = SPLL is not ready

bit 6 Unimplemented: Read as '0'

bit 5 LPRCRDY: Low-Power RC (LPRC) Oscillator Ready Status bit

1 = LPRC is stable and ready

0 = LPRC is disabled or not operating

bit 4 SOSCRDY: Secondary Oscillator (Sosc) Ready Status bit

1 = Sosc is stable and ready

0 = Sosc is disabled or not operating

bit 3 Unimplemented: Read as '0'

bit 2 POSCRDY: Primary Oscillator (Posc) Ready Status bit

1 = Posc is stable and ready

0 = Posc is disabled or not operating

bit 1 Unimplemented: Read as '0'

bit 0 FRCRDY: Fast RC (FRC) Oscillator Ready Status bit

1 = FRC is stable and ready

0 = FRC is disabled for not operating

# REGISTER 11-9: USBIENCSR1: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 1 (ENDPOINT 1-7)

|              |                   | (=::::::::::::::::::::::::::::::::::::: |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-----------------------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6                       | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|              | R/W-0             | R/W-0                                   | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R-0              | R/W-0            |

| 31:24        | AUTOCLR           | ISO                                     | DMAREQEN          | DISNYET           | DMAREQMD          | ı                 | I                | INCOMPRX         |

|              | AUTOCLK           | AUTORQ                                  | DIVIAREQEN        | PIDERR            | DIMAREQIND        | DATATWEN          | DATATGGL         | INCOMPRA         |

|              | R/W-0, HC         | R/W-0, HS                               | R/W-0             | R/W-0, HC         | R-0, HS           | R/W-0, HS         | R-0, HS, HC      | R/W-0, HS        |

| 23:16        | CLRDT             | SENTSTALL                               | SENDSTALL         | FLUSH             | DATAERR           | OVERRUN           | FIFOFULL         | RXPKTRDY         |

|              | CLNDT             | RXSTALL                                 | REQPKT            | PLUSIT            | DERRNAKT          | ERROR             | FIFOFULL         | KAFKIKDI         |

| 15:8         | R/W-0             | R/W-0                                   | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.6         |                   |                                         | MULT<4:0>         |                   |                   | R                 | XMAXP<10:8       | >                |

| 7:0          | R/W-0             | R/W-0                                   | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   |                                         |                   | RXMA              | XP<7:0>           |                   |                  |                  |

**Legend:** HC = Hardware Cleared HS = Hardware Set

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31 AUTOCLR: RXPKTRDY Automatic Clear Control bit

- 1 = RXPKTRDY will be automatically cleared when a packet of RXMAXP bytes has been unloaded from the RX FIFO. When packets of less than the maximum packet size are unloaded, RXPKTRDY will have to be cleared manually. When using a DMA to unload the RX FIFO, data is read from the RX FIFO in 4-byte chunks regardless of the RXMAXP.

- 0 = No automatic clearing of RXPKTRDY

This bit should not be set for high-bandwidth Isochronous endpoints.

- bit 30 ISO: Isochronous Endpoint Control bit (Device mode)

- 1 = Enable the RX endpoint for Isochronous transfers

- 0 = Enable the RX endpoint for Bulk/Interrupt transfers

#### **AUTORQ:** Automatic Packet Request Control bit (*Host mode*)

- 1 = REQPKT will be automatically set when RXPKTRDY bit is cleared.

- 0 = No automatic packet request

This bit is automatically cleared when a short packet is received.

- bit 29 DMAREQEN: DMA Request Enable Control bit

- 1 = Enable DMA requests for the RX endpoint.

- 0 = Disable DMA requests for the RX endpoint.

- bit 28 **DISNYET:** Disable NYET Handshakes Control/PID Error Status bit (*Device mode*)

- 1 = In Bulk/Interrupt transactions, disables the sending of NYET handshakes. All successfully received RX packets are ACKed including at the point at which the FIFO becomes full.

- 0 = Normal operation.

In Bulk/Interrupt transactions, this bit only has any effect in Hi-Speed mode, in which mode it should be set for all Interrupt endpoints.

#### **PIDERR:** PID Error Status bit (*Host mode*)

- 1 = In ISO transactions, this indicates a PID error in the received packet.

- 0 = No error

- bit 27 DMAREQMD: DMA Request Mode Selection bit

- 1 = DMA Request Mode 1

- 0 = DMA Request Mode 0

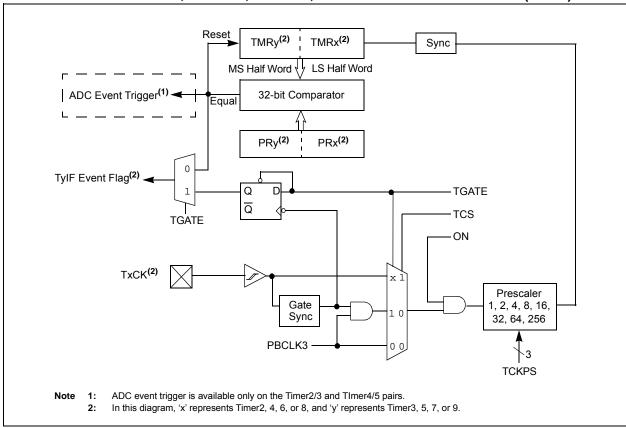

FIGURE 14-2: TIMER2/3, TIMER4/5, TIMER6/7, AND TIMER8/9 BLOCK DIAGRAM (32-BIT)

TABLE 16-2: OUTPUT COMPARE 1 THROUGH OUTPUT COMPARE 9 REGISTER MAP (CONTINUED)

| ess                         |                                 | 0             |       |                       |       |       |       |          |          | Bi    |        | ·    |      | •     |        |      |          |      |            |

|-----------------------------|---------------------------------|---------------|-------|-----------------------|-------|-------|-------|----------|----------|-------|--------|------|------|-------|--------|------|----------|------|------------|

| Virtual Address<br>(BF84_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14                 | 29/13 | 28/12 | 27/11 | 26/10    | 25/9     | 24/8  | 23/7   | 22/6 | 21/5 | 20/4  | 19/3   | 18/2 | 17/1     | 16/0 | All Resets |

| 4A00                        | OC6CON                          | 31:16         | _     | -                     |       | _     | 1     |          | _        | _     | -      | 1    | _    | _     | _      | _    | _        | _    | 0000       |

| 17100                       |                                 |               | ON    | _                     | SIDL  | _     | _     | _        | _        | _     | _      | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000       |

| 4A10                        | OC6R                            | 31:16         |       |                       |       |       |       |          |          | OC6R  | <31:0> |      |      |       |        |      |          |      | xxxx       |

|                             |                                 | 15:0          |       |                       |       |       |       |          |          |       |        |      |      |       |        |      |          |      | XXXX       |

| 4A20                        | OC6RS                           | 31:16<br>15:0 |       | OC6RS<31:0> XXXX XXXX |       |       |       |          |          |       |        |      |      |       |        |      |          |      |            |

|                             |                                 | 31:16         | _     | _                     | _     | _     | _     | _        | _        |       | _      | _    | _    | _     |        |      |          |      | 0000       |

| 4C00                        | OC7CON                          | 15:0          | ON    |                       | SIDL  |       |       | _        |          |       |        |      | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000       |

|                             |                                 | 31:16         | OIT   |                       | OIDE  |       |       |          |          |       |        |      | 0002 | OOLE  | OUTOLL |      | 00M -2.0 |      | xxxx       |

| 4C10                        | OC7R                            | 15:0          |       |                       |       |       |       |          |          | OC7R  | <31:0> |      |      |       |        |      |          |      | xxxx       |

| 4000                        | 00700                           | 31:16         |       |                       |       |       |       |          |          | OC7RS |        |      |      |       |        |      |          |      | xxxx       |

| 4020                        | OC7RS                           | 15:0          |       |                       |       |       |       |          |          | UC/RS | <31:0> |      |      |       |        |      |          |      | xxxx       |

| 4F00                        | OC8CON                          | 31:16         | -     |                       | _     | _     | _     | _        | _        | _     |        | _    | _    | _     | _      | _    | _        | _    | 0000       |

| 7200                        |                                 | 15:0          | ON    | _                     | SIDL  | _     | _     | _        | _        |       | _      | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000       |

| 4E10                        | OC8R                            | 31:16         |       |                       |       |       |       |          |          | OC8R  | <31:0> |      |      |       |        |      |          |      | XXXX       |

|                             |                                 | 15:0          |       |                       |       |       |       |          |          |       |        |      |      |       |        |      |          |      | XXXX       |

| 4E20                        | OC8RS                           | 31:16<br>15:0 |       |                       |       |       |       |          |          | OC8RS | <31:0> |      |      |       |        |      |          |      | XXXX       |

|                             |                                 | 31:16         |       |                       |       |       | _     |          |          |       |        |      |      |       |        |      |          |      | xxxx       |

| 5000                        | OC9CON                          | 15:0          | ON    |                       | SIDL  |       |       |          |          |       |        |      | OC32 | OCFLT | OCTSEL |      | OCM<2:0> |      | 0000       |

|                             |                                 | 31:16         | OIV   |                       | SIDL  |       |       | <u>—</u> | <u> </u> |       |        |      | 0032 | OCILI | OCTOLL |      | OOW-2.02 |      | xxxx       |

| 5010                        | OC9R                            | 15:0          |       |                       |       |       |       |          |          | OC9R  | <31:0> |      |      |       |        |      |          |      | xxxx       |

| 5020                        | OC9RS                           | 31:16<br>15:0 |       |                       |       |       |       |          |          | OC9RS | <31:0> |      |      |       |        |      |          |      | xxxx       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

### 17.1 Deadman Timer Control Registers

### TABLE 17-1: DEADMAN TIMER REGISTER MAP

| ess                         |                  |           |       |       |       |       |        |       |      |      | Bits       |      |          |      |        |      |      |        | ·0         |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|--------|-------|------|------|------------|------|----------|------|--------|------|------|--------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8 | 23/7       | 22/6 | 21/5     | 20/4 | 19/3   | 18/2 | 17/1 | 16/0   | All Resets |

| 0A00                        | DMTCON           | 31:16     | -     | _     | _     | _     | _      | _     | _    | _    |            | _    | _        | _    | _      | _    | _    | _      | 0000       |

| 07100                       | Biiii Goil       | 15:0      | ON    | _     | _     | _     | _      | _     | _    | _    | _          | _    | _        | _    | _      | _    | _    | _      | 0000       |

| 0A10                        | DMTPRECLR        | 31:16     | _     | _     | _     | _     | _      | _     | _    | _    | _          |      | _        |      | _      | _    | _    |        | 0000       |

| OATO                        | DIVITI RECER     | 15:0      |       |       |       | STEP  | 1<7:0> |       |      |      | _          | _    | _        | _    | _      | _    | _    | _      | 0000       |

| 0A20                        | DMTCLR           | 31:16     | _     | _     | _     | _     | _      | _     | _    | _    | _          | _    | _        |      | _      | _    | _    | _      | 0000       |

| UAZU                        | DIVITOLIX        | 15:0      | ı     | _     | _     | _     | _      | _     | _    | _    |            | •    |          | STEP | 2<7:0> | •    |      | •      | 0000       |

| 0A30                        | DMTSTAT          | 31:16     | ı     | _     | _     | _     | _      | _     | _    | _    |            | _    | _        | _    | _      | _    | _    | _      | 0000       |

| UASU                        | DIVITOTAL        | 15:0      | ı     | _     | _     | _     | _      | _     | _    | -    | BAD1       | BAD2 | DMTEVENT | _    | _      | _    | _    | WINOPN | 0000       |

| 0A40                        | DMTCNT           | 31:16     |       |       |       |       |        |       |      | COLI | NTER<31:0  | 1    |          |      |        |      |      |        | 0000       |

| 0/40                        | DIVITORT         | 15:0      |       |       |       |       |        |       |      | COU  | VILK-51.   | J-   |          |      |        |      |      |        | 0000       |

| 0A60                        | DMTPSCNT         | 31:16     |       |       |       |       |        |       |      | Dec  | CNT<31:0>  |      |          |      |        |      |      |        | 0000       |

| UAGU                        | DIVITESCINT      | 15:0      |       |       |       |       |        |       |      | F30  | JN1 \31.02 |      |          |      |        |      |      |        | 0000       |

| 0A70                        | DMTPSINTV        | 31:16     |       |       |       |       |        |       |      | Dell | NTV<31:0>  |      |          |      | ·      |      |      | -      | 0000       |

| UATU                        | אווונידוואוע     | 15:0      |       |       |       |       |        |       |      | FSI  | NIV-31.02  | -    |          |      |        |      |      |        | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### REGISTER 22-2: SQI1XCON2: SQI XIP CONTROL REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | -                 | -                 | -                 | _                 | _                | _                |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | _                 | _                 | _                 | DEVSE             | EL<1:0>           | MODEBY           | TES<1:0>         |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | MODECO            | DE<7:0>           |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-12 Unimplemented: Read as '0'

bit 11-10 DEVSEL<1:0>: Device Select bits

11 = Reserved

10 = Reserved

01 = Device 1 is selected

00 = Device 0 is selected

bit 9-8 MODEBYTES<1:0>: Mode Byte Cycle Enable bits

11 = Three cycles

10 = Two cycles

01 = One cycle

00 = Zero cycles

bit 7-0 MODECODE<7:0>: Mode Code Value bits

These bits contain the 8-bit code value for the mode bits.

#### REGISTER 22-3: SQI1CFG: SQI CONFIGURATION REGISTER (CONTINUED)

bit 12 **BURSTEN:** Burst Configuration bit<sup>(1)</sup>

1 = Burst is enabled

0 = Burst is not enabled

bit 11 Reserved: Must be programmed as '0'

bit 10 HOLD: Hold bit

In Single Lane or Dual Lane mode, this bit is used to drive the SQID3 pin, which can be used for devices with a HOLD input pin. The meaning of the values for this bit will depend on the device to which SQID3 is connected.

bit 9 WP: Write Protect bit

In Single Lane or Dual Lane mode, this bit is used to drive the SQID2 pin, which can be used with devices with a write-protect pin. The meaning of the values for this bit will depend on the device to which SQID2 is connected.

bit 8-6 **Unimplemented:** Read as '0'

bit 5 LSBF: Data Format Select bit

1 = LSB is sent or received first

0 = MSB is sent or received first

bit 4 CPOL: Clock Polarity Select bit

1 = Active-low SQICLK (SQICLK high is the Idle state)

0 = Active-high SQICLK (SQICLK low is the Idle state)

bit 3 CPHA: Clock Phase Select bit

1 = SQICLK starts toggling at the start of the first data bit

0 = SQICLK starts toggling at the middle of the first data bit

bit 2-0 MODE<2:0>: Mode Select bits

111 = Reserved

•

100 = Reserved

011 = XIP mode is selected (when this mode is entered, the module behaves as if executing in place (XIP), but uses the register data to control timing)

010 = DMA mode is selected

001 = CPU mode is selected (the module is controlled by the CPU in PIO mode. This mode is entered when leaving Boot or XIP mode)

000 = Reserved

**Note 1:** This bit must be programmed as '1'.

### 26.1 EBI Control Registers

### TABLE 26-1: EBI REGISTER MAP

|                             | LE 20-1.         |               | I ILC  | SIEKI    | 117 (1 |             |          |         |         |              |                  |          |          |       |          |           |            |         |              |

|-----------------------------|------------------|---------------|--------|----------|--------|-------------|----------|---------|---------|--------------|------------------|----------|----------|-------|----------|-----------|------------|---------|--------------|

| ess                         | -                |               |        |          |        |             |          |         |         |              | Bits             |          |          |       |          |           |            |         | "            |

| Virtual Address<br>(BF8E_#) | Register<br>Name | Bit Range     | 31/15  | 30/14    | 29/13  | 28/12       | 27/11    | 26/10   | 25/9    | 24/8         | 23/7             | 22/6     | 21/5     | 20/4  | 19/3     | 18/2      | 17/1       | 16/0    | All Resets   |

| 1014                        | EBICS0           | 31:16         |        |          |        |             |          |         |         | С            | SADDR<15:0       | >        |          |       |          |           |            |         | 2000         |

| 1014                        | ЕВІСО            | 15:0          | _      | _        | _      | _           | -        | -       | _       | _            | _                | _        | _        | _     | _        | _         | _          | _       | 0000         |

| 1018                        | EBICS1           | 31:16         |        |          |        |             |          |         |         | С            | SADDR<15:0       | >        |          |       |          |           |            |         | 1000         |

| 1010                        | LDICOT           | 15:0          |        | _        | _      | _           | _        | _       | _       | _            | _                | _        | _        | _     | _        | _         | _          | _       | 0000         |

| 101C                        | EBICS2           | 31:16         |        |          |        |             |          |         |         | С            | SADDR<15:0       | >        |          |       |          |           |            |         | 2040         |

| 1010                        | LDICOZ           | 15:0          | _      | _        | _      | _           | _        | _       | _       | _            | _                | _        | _        | _     | _        | _         | _          | _       | 0000         |

| 1020                        | EBICS3           | 31:16         |        |          |        |             | 1        |         |         | С            | SADDR<15:0       | >        |          |       |          |           |            |         | 1040         |

| 1020                        | LDIOO            | 15:0          | _      | _        | _      | _           | _        | _       | _       | _            | _                | _        | _        | _     | _        | _         | _          | _       | 0000         |

| 1054                        | EBIMSK0          | 31:16         |        | _        |        | _           |          | _       | _       | _            | _                | _        | _        | _     | _        | _         | _          | _       | 0000         |

|                             |                  | 15:0          |        | _        |        |             |          | REC     | SEL<2:0 | <b> &gt;</b> | М                | EMTYPE<2 | 2:0>     |       | M        | EMSIZE<4: | 0>         | 1       | 0020         |

| 1058                        | EBIMSK1          | 31:16         |        | _        |        |             |          | _       | _       | _            | _                | _        | _        |       | _        | _         | _          | _       | 0000         |

|                             |                  | 15:0          |        | _        | _      | _           |          | REC     | SEL<2:0 | >            | М                | EMTYPE<2 | 2:0>     |       | M        | EMSIZE<4: | 0>         | 1       | 0020         |

| 105C                        | EBIMSK2          | 31:16         |        | _        | _      | _           | _        | _       | _       | _            | _                | _        | _        |       | _        | _         | _          | _       | 0000         |

|                             |                  | 15:0          |        | _        | _      |             | _        | REC     | SEL<2:0 | <b> &gt;</b> |                  | EMTYPE<2 |          |       | M        | EMSIZE<4  |            |         | 0120         |

| 1060                        | EBIMSK3          | 31:16         |        | _        |        | _           |          |         |         | _            |                  |          | _        | _     | <u> </u> |           | _          | _       | 0000         |

|                             |                  | 15:0          |        |          |        |             |          |         | SEL<2:0 |              |                  | EMTYPE<2 |          |       | M        | EMSIZE<4: |            |         | 0120         |

| 1094                        | EBISMT0          | 31:16         |        | _        |        |             | _        | RDYMODE |         |              | PAGEMODE         |          | TPRC<    | <3:0> | TDO :    |           | TBTA<2:0>  |         | 041C         |

|                             |                  | 15:0          |        |          | I VVI  | P<5:0>      |          | DDVMODE | TWR     |              | TAS<             |          | TDDO     | ٠٥.٥٠ | TRC<     |           | TDTA 40.05 |         | 2D4B         |

| 1098                        | EBISMT1          | 31:16<br>15:0 |        | _        |        | —<br>P<5:0> | _        | RDYMODE | TWR     |              | PAGEMODE<br>TAS< |          | TPRC<    | 3:0>  | TDO 4    |           | TBTA<2:0>  |         | 041C         |

|                             |                  |               |        |          | I VVI  | P<5:0>      |          | DDVMODE |         |              | PAGEMODE         |          | TPRC<    | 2.05  | TRC<     |           | TBTA<2:0>  |         | 2D4B<br>041C |

| 109C                        | EBISMT2          | 31:16<br>15:0 |        | _        |        | P<5:0>      | _        | RUTWODE | TWR     |              | TAS<             | L        | IPRU     | ·3.U> | TRC<     |           | 1B1A\2.0>  |         | 2D4B         |

|                             |                  | 31:16         |        |          | I      | P<5.0>      |          |         | IVVR    | < 1.U>       | IASS             | 1.0>     |          | _     |          | 5.0>      |            |         | 0000         |

| 10A0                        | EBIFTRPD         | 15:0          |        |          | _      |             | _        | _       |         | _            | _                |          | PD<11:0> | _     |          | _         | _          | _       | 00C8         |

|                             |                  | 31:16         |        |          |        |             |          |         |         |              |                  |          | PD<11.0> | l –   | _        | _         | _          | _       | 0000         |

| 10A4                        | EBISMCON         | 15:0          |        | WIDTH2<2 |        |             | DWIDTH1< | 2:0>    | - 51    | I <u> </u>   |                  | _        |          |       |          |           |            | SMRP    | 0201         |

| L                           |                  |               | الالال |          |        |             |          | -2.0-   | 1       |              |                  |          | _        |       |          |           |            | CIVILLE | 0201         |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Table 27-12 shows the Security Association control word structure.

The Crypto Engine fetches different structures for different flows and ensures that hardware fetches minimum words from SA required for processing. The structure is ready for hardware optimal data fetches.

#### FIGURE 27-12: FORMAT OF SA\_CTRL

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6              | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|--------------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31-24        | _                 | _                              | VERIFY            | _                 | NO_RX             | OR_EN             | ICVONLY          | IRFLAG           |

| 23-16        | LNC               | LOADIV                         | FB                | FLAGS             | _                 | _                 | _                | ALGO<6>          |

| 15-8         |                   |                                | ALGO              | <5:0>             |                   |                   | ENC              | KEY<br>SIZE<1>   |

| 7-0          | KEY<br>SIZE<0>    | MULTITASK<2:0> CRYPTOALGO<3:0> |                   |                   |                   |                   |                  |                  |

bit 31-30 Reserved: Do not use

bit 29 VERIFY: NIST Procedure Verification Setting

1 = NIST procedures are to be used 0 = Do not use NIST procedures

bit 28 Reserved: Do not use

bit 27 NO\_RX: Receive DMA Control Setting

1 = Only calculate ICV for authentication calculations

0 = Normal processing

bit 26 OR\_EN: OR Register Bits Enable Setting

1 = OR the register bits with the internal value of the CSR register

0 = Normal processing

bit 25 ICVONLY: Incomplete Check Value Only Flag

This affects the SHA-1 algorithm only. It has no effect on the AES algorithm.

1 = Only three words of the HMAC result are available

0 = All results from the HMAC result are available

bit 24 IRFLAG: Immediate Result of Hash Setting

This bit is set when the immediate result for hashing is requested.

1 = Save the immediate result for hashing

0 = Do not save the immediate result

bit 23 LNC: Load New Keys Setting

1 = Load a new set of keys for encryption and authentication

0 = Do not load new keys

bit 22 LOADIV: Load IV Setting

1 = Load the IV from this Security Association

0 = Use the next IV

bit 21 FB: First Block Setting

This bit indicates that this is the first block of data to feed the IV value.

1 = Indicates this is the first block of data

0 = Indicates this is not the first block of data

bit 20 FLAGS: Incoming/Outgoing Flow Setting

1 = Security Association is associated with an outgoing flow

0 = Security Association is associated with an incoming flow

bit 19-17 Reserved: Do not use

#### **REGISTER 29-22: ADCFSTAT: ADC FIFO STATUS REGISTER**

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24     | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24     | FEN               | -                 |                   | ADC4EN            | ADC3EN            | ADC2EN            | ADC1EN           | ADC0EN           |

| 00:46     | R/W-0             | R-0, HS, HC       | R-0, HS, HC       | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | FIEN              | FRDY              | FWROVERR          |                   | _                 | -                 | 1                | -                |

| 45.0      | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8      |                   |                   |                   | FCNT              | <7:0>             |                   |                  |                  |

| 7.0       | R-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |

| 7:0       | FSIGN             | _                 | _                 | _                 | _                 |                   | ADCID<2:0>       |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 FEN: FIFO Enable bit

1 = FIFO is enabled

0 = FIFO is disabled; no data is being saved into the FIFO

bit 30-29 Unimplemented: Read as '0'

bit 28-24 ADC4EN: ADC0EN: ADCx Enable bits ('x' = 0 through 4)

1 = Converted output data of ADCx is stored in the FIFO

0 = Converted output data of ADCx is not stored in the FIFO

Note: While using FIFO, the output data is additionally stored in the respective output data register

(ADCDATAx).

bit 23 FIEN: FIFO Interrupt Enable bit

1 = FIFO interrupts are enabled; an interrupt is generated once the FRDY bit is set

0 = FIFO interrupts are disabled

bit 22 FRDY: FIFO Data Ready Interrupt Status bit

1 = FIFO has data to be read

0 = No data is available in the FIFO

Note: This bit is cleared when the FIFO output data in ADCFIFO has been read and there is no

additional data ready in the FIFO (that is, the FIFO is empty).

bit 21 **FWROVERR:** FIFO Write Overflow Error Status bit

1 = A write overflow error in the FIFO has occurred (circular FIFO)

0 = A write overflow error in the FIFO has not occurred

**Note:** This bit is cleared after ADCFSTAT<23:16> are read by software.

bit 15-8 FCNT<7:0>: FIFO Data Entry Count Status bit

The value in these bits indicates the number of data entries in the FIFO.

bit 7 FSIGN: FIFO Sign Setting bit

This bit reflects the sign of data stored in the ADCFIFO register.

bit 6-3 Unimplemented: Read as '0'

bit 2-0 **ADCID<2:0>:** ADCx Identifier bits ('x' = 0 through 6)

These bits specify the ADC module whose data is stored in the FIFO.

111 = Reserved

110 = Reserved

100 = Converted data of ADC4 is store in FIFO

•

.

000 = Converted data of ADC0 is stored in FIFO

#### REGISTER 30-2: CICFG: CAN BAUD RATE CONFIGURATION REGISTER

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2            | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------------|--------------------|-------------------|-------------------|-------------------|------------------------------|------------------|------------------|

| 24.04        | U-0                     | U-0                | U-0               | U-0               | U-0               | U-0                          | U-0              | U-0              |

| 31:24        | _                       | _                  | _                 | -                 | -                 | _                            | _                | _                |

| 00:40        | U-0                     | R/W-0              | U-0               | U-0               | U-0               | R/W-0                        | R/W-0            | R/W-0            |

| 23:16        | _                       | WAKFIL             | _                 | _                 | _                 | SEG2PH<2:0> <sup>(1,4)</sup> |                  |                  |

| 15:8         | R/W-0                   | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0                        | R/W-0            | R/W-0            |

|              | SEG2PHTS <sup>(1)</sup> | SAM <sup>(2)</sup> | SEG1PH<2:0>       |                   |                   | Р                            | PRSEG<2:0>       |                  |

| 7:0          | R/W-0                   | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0                        | R/W-0            | R/W-0            |

|              | SJW<1:0> <sup>(3)</sup> |                    | BRP<5:0>          |                   |                   |                              |                  |                  |

**Legend:** HC = Hardware Clear S = Settable bit

R = Readable bit W = Writable bit P = Programmable bit r = Reserved bit

U = Unimplemented bit -n = Bit Value at POR: ('0', '1', x = Unknown)

bit 31-23 Unimplemented: Read as '0'

bit 22 WAKFIL: CAN Bus Line Filter Enable bit

1 = Use CAN bus line filter for wake-up

0 = CAN bus line filter is not used for wake-up

bit 21-19 Unimplemented: Read as '0'

bit 18-16 **SEG2PH<2:0>:** Phase Buffer Segment 2 bits<sup>(1,4)</sup>

111 = Length is 8 x TQ

•

•

000 = Length is 1 x TQ

bit 15 **SEG2PHTS:** Phase Segment 2 Time Select bit<sup>(1)</sup>

1 = Freely programmable

0 = Maximum of SEG1PH or Information Processing Time, whichever is greater

bit 14 SAM: Sample of the CAN Bus Line bit (2)

1 = Bus line is sampled three times at the sample point

0 = Bus line is sampled once at the sample point

bit 13-11 **SEG1PH<2:0>:** Phase Buffer Segment 1 bits<sup>(4)</sup>

111 = Length is 8 x TQ

\_

$000 = \text{Length is } 1 \times \text{TQ}$

**Note 1:** SEG2PH ≤ SEG1PH. If SEG2PHTS is clear, SEG2PH will be set automatically.

2: 3 Time bit sampling is not allowed for BRP < 2.

3:  $SJW \leq SEG2PH$ .

4: The Time Quanta per bit must be greater than 7 (that is, TQBIT > 7).

**Note:** This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (CiCON<23:21>) = 100).

#### REGISTER 31-2: ETHCON2: ETHERNET CONTROLLER CONTROL REGISTER 2

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24     | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 23:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10     | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8      | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

|           | _                 | _                 | _                 | _                 | _                 | RXBUFSZ<6:4>      |                  |                  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0               | U-0              | U-0              |

|           |                   | RXBUF             | SZ<3:0>           |                   |                   | _                 |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-11 Unimplemented: Read as '0'

bit 10-4 RXBUFSZ<6:0>: RX Data Buffer Size for All RX Descriptors (in 16-byte increments) bits

1111111 = RX data Buffer size for descriptors is 2032 bytes

•

•

1100000 = RX data Buffer size for descriptors is 1536 bytes

•

•

.

0000011 = RX data Buffer size for descriptors is 48 bytes

0000010 = RX data Buffer size for descriptors is 32 bytes

0000001 = RX data Buffer size for descriptors is 16 bytes

0000000 = Reserved

bit 3-0 **Unimplemented:** Read as '0'

Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0.

# REGISTER 36-9: GLCDLxMODE: GRAPHICS LCD CONTROLLER LAYER 'x' MODE REGISTER ('x' = 0-2)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0               | U-0              | U-0              |  |  |

|              | LAYEREN           | DISABIFIL         | FORCE<br>ALPHA    | MUL<br>ALPHA      | -                 | _                 | _                | _                |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | ALPHA<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | DESTBLEND<3:0>    |                   |                   |                   |                   | SRCBLE            | ND<3:0>          | U-0 — R/W-0      |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              | _                 | _                 | _                 | _                 | COLORMODE<3:0>    |                   |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 LAYEREN: Layer Enable bit

1 = Layer is enabled

0 = Layer is not enabled

bit 30 DISABIFIL: Disable Bilinear Filtering bit

1 = Bilinear filtering is enabled

0 = Bilinear filtering is not enabled

bit 29 FORCEALPHA: Force Alpha with Global Alpha bit

1 = Force alpha with global alpha is enabled

0 = Force alpha with global alpha is not enabled

bit 28 MULALPHA: Premultiply Image Alpha bit

1 = Premultiply image alpha is enabled

0 = Premultiply image alpha is not enabled

bit 27-24 Unimplemented: Read as '0'

bit 23-16 ALPHA<7:0>: Layer Alpha bits

These bits contain the Layer Alpha value ranging from 0 to 0xFF.

bit 15-12 **DESTBLEND<3:0>:** Destinary Blending Function bits

1111 = Reserved

1110 = Reserved

1101 = Blend inverted destination

1100 = Reserved

1011 = Reserved

1010 = Blend alpha destination

1001 = Reserved

1000 = Reserved

0111 = Blend inverted source and inverted global

0110 = Blend inverted global

0101 = Blend inverted source

0100 = Blend alpha source and alpha global

0011 = Blend alpha global

0010 = Blend alpha source

0001 = Blend white

0000 = Blend black

#### REGISTER 38-28: DDRPHYPADCON: DDR PHY PAD CONTROL REGISTER (CONTINUED) bit 9 **NOEXTDLL:** No External DLL bit 1 = Use internal digital DLL. 0 = Use external DLL. bit 8 **EOENCLKCYC:** Extra Output Enable bit 1 = Drive pad output enables for an extra clock cycle after a write burst 0 = Do not drive pad output enables for an extra clock cycle after a write burst ODTPUCAL<1:0>: On-Die Termination Pull-up Calibration bits bit 7-6 11 = Maximum ODT impedance 00 = Minimum ODT impedance bit 5-4 ODTPFDCAL<1:0>: On-Die Termination Pull-down Calibration bits 11 = Maximum ODT impedance 00 = Minimum ODT impedance bit 3 ADDCDRVSEL: Address and Control Pads Drive Strength Select bit 1 = Full drive strength 0 = 60% driver strength **DATDRVSEL:** Data Pad Drive Strength Select bit bit 2 1 = Full Drive Strength 0 = 60% Drive Strength bit 1 **ODTEN:** On-Die Termination Enable bit 1 = ODT Enabled 0 = ODT Disabled bit 0 **ODTSEL:** On-Die Termination Select bit 1 = 150 ohm On-Die Termination 0 = 75 ohm On-Die Termination

#### bit 2-0 CLKDLYDELTA<2:0>: DDR Clock Delay Delta bits

These bits indicate the SCL latency setting programmed per byte lane.

```

111 = 7 DDR clocks

110 = 6 DDR clocks

.

.

000 = 0 DDR clocks

```

These bits are automatically programmed by the SCL logic and can also be programmed by the user, and are specifically useful for SCL retires.

Note 1: These bits indicate the same status as the SCLLBPASS (DDRSCLSTART<0>) and SCLUBPASS (DDRSCLSTART<0>) bits.

#### 43.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDF

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility

#### 43.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel® standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

### 43.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 43.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility

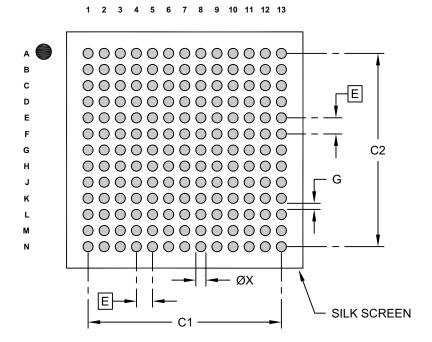

#### 169-Ball Low Profile Ball Grid Array (6JX) - 11x11 mm Body [LFBGA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                             | N   | MILLIMETERS MIN NOM MAX |      |      |  |

|-----------------------------|-----|-------------------------|------|------|--|

| Dimension                   | MIN | NOM                     | MAX  |      |  |

| Contact Pitch               | Е   | 0.80 BSC                |      |      |  |

| Overall Contact Pad Spacing | C1  |                         | 9.60 |      |  |

| Overall Contact Pad Spacing | C2  |                         | 9.60 |      |  |

| Contact Pad Width (X169)    | X1  |                         |      | 0.50 |  |

| Contact Pad to Contact Pad  | G   | 0.30                    |      |      |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2439A