Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                  |

|----------------------------|------------------------------------------------------------------|

| Product Status             | Active                                                           |

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | LINbus, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT               |

| Number of I/O              | 6                                                                |

| Program Memory Size        | 8KB (8K x 8)                                                     |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 256 x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.25V                                                       |

| Data Converters            | A/D 6x12b                                                        |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                               |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 10-VFDFN Exposed Pad                                             |

| Supplier Device Package    | 10-DFN (3x3)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f520-c-im |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## List of Figures

| Figure 1.1. C8051F53xA/F53x-C Block Diagram                          | . 16 |

|----------------------------------------------------------------------|------|

| Figure 1.2. C8051F52xA/F52x-C Block Diagram                          | . 16 |

| Figure 1.3. C8051F53x Block Diagram (Silicon Revision A)             | . 17 |

| Figure 1.4. C8051F52x Block Diagram (Silicon Revision A)             | . 17 |

| Figure 1.5. Development/In-System Debug Diagram                      |      |

| Figure 1.6. Memory Map                                               |      |

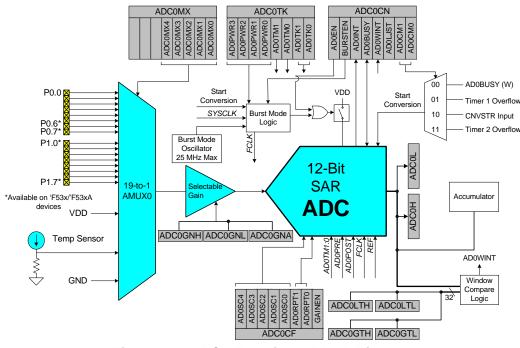

| Figure 1.7. 12-Bit ADC Block Diagram                                 | . 22 |

| Figure 1.8. Comparator Block Diagram                                 |      |

| Figure 1.9. Port I/O Functional Block Diagram                        |      |

| Figure 3.1. DFN-10 Pinout Diagram (Top View)                         | . 35 |

| Figure 3.2. DFN-10 Package Diagram                                   |      |

| Figure 3.3. DFN-10 Landing Diagram                                   | . 39 |

| Figure 3.4. TSSOP-20 Pinout Diagram (Top View)                       | . 40 |

| Figure 3.5. TSSOP-20 Package Diagram                                 |      |

| Figure 3.6. TSSOP-20 Landing Diagram                                 | . 44 |

| Figure 3.7. QFN-20 Pinout Diagram (Top View)                         | . 45 |

| Figure 3.8. QFN-20 Package Diagram*                                  |      |

| Figure 3.9. QFN-20 Landing Diagram*                                  | . 50 |

| Figure 4.1. ADC0 Functional Block Diagram                            |      |

| Figure 4.2. Typical Temperature Sensor Transfer Function             | . 53 |

| Figure 4.3. ADC0 Tracking Modes                                      |      |

| Figure 4.4. 12-Bit ADC Tracking Mode Example                         |      |

| Figure 4.5. 12-Bit ADC Burst Mode Example with Repeat Count Set to 4 | . 58 |

| Figure 4.6. ADC0 Equivalent Input Circuits                           | . 60 |

| Figure 4.7. ADC Window Compare Example:                              |      |

| Right-Justified Single-Ended Data                                    | . 71 |

| Figure 4.8. ADC Window Compare Example:                              |      |

| Left-Justified Single-Ended Data                                     |      |

| Figure 5.1. Voltage Reference Functional Block Diagram               |      |

| Figure 6.1. External Capacitors for Voltage Regulator Input/Output   |      |

| Figure 7.1. Comparator Functional Block Diagram                      |      |

| Figure 7.2. Comparator Hysteresis Plot                               | . 77 |

| Figure 8.1. CIP-51 Block Diagram                                     |      |

| Figure 9.1. Memory Map                                               |      |

| Figure 11.1. Reset Sources                                           |      |

| Figure 11.2. Power-On and V <sub>DD</sub> Monitor Reset Timing       |      |

| Figure 12.1. Flash Program Memory Map                                | 117  |

| Figure 13.1. Port I/O Functional Block Diagram                       |      |

| Figure 13.2. Port I/O Cell Block Diagram                             | 121  |

| Figure 13.3. Crossbar Priority Decoder with No Pins Skipped          |      |

| (TSSOP 20 and QFN 20)                                                | 122  |

| Figure 13.4. Crossbar Priority Decoder with Crystal Pins Skipped     |      |

| (TSSOP 20 and QFN 20)                                                | 123  |

## 2. Electrical Characteristics

## 2.1. Absolute Maximum Ratings

### Table 2.1. Absolute Maximum Ratings

| Parameter                                                                                                                                                                                                                                 | Conditions        | Min       | Тур     | Мах                      | Units   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------|---------|--------------------------|---------|

| Ambient temperature under Bias                                                                                                                                                                                                            |                   | -55       | —       | 135                      | °C      |

| Storage Temperature                                                                                                                                                                                                                       |                   | -65       | —       | 150                      | °C      |

| Voltage on V <sub>REGIN</sub> with Respect to GND                                                                                                                                                                                         |                   | -0.3      | —       | 5.5                      | V       |

| Voltage on V <sub>DD</sub> with Respect to GND                                                                                                                                                                                            |                   | -0.3      | —       | 2.8                      | V       |

| Voltage on XTAL1 with Respect to GND                                                                                                                                                                                                      |                   | -0.3      | —       | $V_{REGIN} + 0.3$        | V       |

| Voltage on XTAL2 with Respect to GND                                                                                                                                                                                                      |                   | -0.3      | —       | V <sub>REGIN</sub> + 0.3 | V       |

| Voltage on any Port I/O Pin or RST with Respect to GND                                                                                                                                                                                    |                   | -0.3      | —       | V <sub>REGIN</sub> + 0.3 | V       |

| Maximum Output Current Sunk by any Port Pin                                                                                                                                                                                               |                   | _         | —       | 100                      | mA      |

| Maximum Output Current Sourced by any Port Pin                                                                                                                                                                                            |                   | _         | —       | 100                      | mA      |

| Maximum Total Current through V <sub>REGIN</sub> , and GND                                                                                                                                                                                |                   |           | —       | 500                      | mA      |

| <b>Note:</b> Stresses above those listed under "Absolute Maximum This is a stress rating only and functional operation of th indicated in the operation listings of this specification is extended periods may affect device reliability. | ne devices at the | ose or ar | y other | conditions above         | e those |

#### **Table 2.7. Comparator Electrical Characteristics**

$V_{\text{REGIN}} = 2.7-5.25$  V, -40 to +125 °C unless otherwise noted.

All specifications apply to both Comparator0 and Comparator1 unless otherwise noted.

| Parameter                                                      | Conditions            | Min   | Тур  | Max                    | Units |

|----------------------------------------------------------------|-----------------------|-------|------|------------------------|-------|

| Response Time:                                                 | CP0+ - CP0- = 100 mV  |       | 780  | —                      | ns    |

| Mode 0, Vcm <sup>1</sup> = 1.5 V                               | CP0+ - CP0- = -100 mV |       | 980  | _                      | ns    |

| Response Time:                                                 | CP0+ - CP0- = 100 mV  |       | 850  | _                      | ns    |

| Mode 1, Vcm <sup>1</sup> = 1.5 V                               | CP0+ - CP0- = -100 mV | —     | 1120 | —                      | ns    |

| Response Time:                                                 | CP0+ - CP0- = 100 mV  | —     | 870  | —                      | ns    |

| Mode 2, Vcm <sup>1</sup> = 1.5 V                               | CP0+ - CP0- = -100 mV |       | 1310 | —                      | ns    |

| Response Time:                                                 | CP0+ - CP0- = 100 mV  |       | 1980 | —                      | ns    |

| Mode 3, Vcm <sup>1</sup> = 1.5 V                               | CP0+ - CP0- = -100 mV |       | 4770 | —                      | ns    |

| Common-Mode Rejection<br>Ratio                                 |                       |       | 3    | 9                      | mV/V  |

| Positive Hysteresis 1                                          | CP0HYP1-0 = 00        |       | 0.7  | 2                      | mV    |

| Positive Hysteresis 2                                          | CP0HYP1-0 = 01        | 2     | 5    | 10                     | mV    |

| Positive Hysteresis 3                                          | CP0HYP1-0 = 10        | 5     | 10   | 20                     | mV    |

| Positive Hysteresis 4                                          | CP0HYP1-0 = 11        | 13    | 20   | 40                     | mV    |

| Negative Hysteresis 1                                          | CP0HYN1-0 = 00        |       | 0.7  | 2                      | mV    |

| Negative Hysteresis 2                                          | CP0HYN1-0 = 01        | 2     | 5    | 10                     | mV    |

| Negative Hysteresis 3                                          | CP0HYN1-0 = 10        | 5     | 10   | 20                     | mV    |

| Negative Hysteresis 4                                          | CP0HYN1-0 = 11        | 13    | 20   | 40                     | mV    |

| Inverting or Non-Inverting<br>Input Voltage Range <sup>2</sup> |                       | -0.25 |      | V <sub>DD</sub> + 0.25 | V     |

| Input Capacitance <sup>2</sup>                                 |                       | —     | 4    | —                      | pF    |

| Input Bias Current                                             |                       |       | 0.5  | —                      | nA    |

| Input Offset Voltage                                           |                       | -15   | —    | 15                     | mV    |

| Input Impedance                                                |                       |       | 1.5  | _                      | kΩ    |

| Power Supply                                                   |                       |       |      |                        |       |

| Power Supply Rejection <sup>2</sup>                            |                       | _     | 0.2  | 4                      | mV/V  |

| Power-up Time                                                  |                       | — —   | 2.3  | —                      | μs    |

|                                                                | Mode 0                | — —   | 6    | 30                     | μA    |

| Supply Current at DC                                           | Mode 1                |       | 3    | 15                     | μA    |

| Supply Current at DC                                           | Mode 2                | — —   | 2    | 7.5                    | μA    |

|                                                                | Mode 3                |       | 0.3  | 3.8                    | μA    |

1. Vcm is the common-mode voltage on CP0+ and CP0-.

2. Guaranteed by design and/or characterization.

| Name     | Pin Nur           | nbers | Туре             | Description                                                                                                                                                                                                                      |

|----------|-------------------|-------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | ʻF53xA<br>ʻF53x-C |       |                  |                                                                                                                                                                                                                                  |

| P1.0/    | 13                | 13    | D I/O or<br>A In | Port 1.0. See Port I/O Section for a complete description.                                                                                                                                                                       |

| XTAL2    |                   |       | D I/O            | External Clock Output. For an external crystal or resonator, this pin is the excitation driver. This pin is the external clock input fo CMOS, capacitor, or RC oscillator configurations. Section "14. Oscillators" on page 135. |

| P0.7/    | 14                | 14    | D I/O or         | Port 0.7. See Port I/O Section for a complete description.                                                                                                                                                                       |

| XTAL1    |                   |       | A In             | External Clock Input. This pin is the external oscillator return for a crystal or resonator. See Oscillator Section.                                                                                                             |

| P0.6/    | 15                | 15    | D I/O or<br>A In | Port 0.6. See Port I/O Section for a complete description.                                                                                                                                                                       |

| C2D      |                   |       | D I/O            | Bi-directional data signal for the C2 Debug Interface.                                                                                                                                                                           |

| P0.5/RX* | 16                | —     | D I/O or<br>A In | Port 0.5. See Port I/O Section for a complete description.                                                                                                                                                                       |

| P0.5     |                   | 16    | D I/O or<br>A In | Port 0.5. See Port I/O Section for a complete description.                                                                                                                                                                       |

| P0.4/TX* | 17                | —     | D I/O or<br>A In | Port 0.4. See Port I/O Section for a complete description.                                                                                                                                                                       |

| P0.4/RX* | _                 | 17    | D I/O or<br>A In | Port 0.4. See Port I/O Section for a complete description.                                                                                                                                                                       |

| P0.3     | 18                |       | D I/O or<br>A In | Port 0.3. See Port I/O Section for a complete description.                                                                                                                                                                       |

| P0.3/TX* | —                 | 18    | D I/O or<br>A In | Port 0.3. See Port I/O Section for a complete description.                                                                                                                                                                       |

| P0.2     | 19                | 19    | D I/O or<br>A In | Port 0.2. See Port I/O Section for a complete description.                                                                                                                                                                       |

| P0.1     | 20                | 20    | D I/O or<br>A In | Port 0.1. See Port I/O Section for a complete description.                                                                                                                                                                       |

### Table 3.7. Pin Definitions for the C8051F53x and C805153xA (QFN 20) (Continued)

## 4. 12-Bit ADC (ADC0)

The ADC0 on the C8051F52x/F52xA/F53x/F53xA Family consists of an analog multiplexer (AMUX0) with 16/6 total input selections, and a 200 ksps, 12-bit successive-approximation-register (SAR) ADC with integrated track-and-hold, programmable window detector, programmable gain, and hardware accumulator. The ADC0 subsystem has a special Burst Mode which can automatically enable ADC0, capture and accumulate samples, then place ADC0 in a low power shutdown mode without CPU intervention. The AMUX0, data conversion modes, and window detector are all configurable under software control via the Special Function Registers shown in Figure 4.1. ADC0 inputs are single-ended and may be configured to measure P0.0-P1.7, the Temperature Sensor output,  $V_{DD}$ , or GND with respect to GND. The voltage reference for the ADC is selected as described in Section "5. Voltage Reference" on page 72. ADC0 is enabled when the AD0EN bit in the ADC0 Control register (ADC0CN) is set to logic 1, or when performing conversions in Burst Mode. ADC0 is in low power shutdown when AD0EN is logic 0 and no Burst Mode conversions are taking place.

Figure 4.1. ADC0 Functional Block Diagram

### 4.1. Analog Multiplexer

AMUX0 selects the input channel to the ADC. Any of the following may be selected as an input: P0.0–P1.7, the on-chip temperature sensor, the core power supply ( $V_{DD}$ ), or ground (GND). **ADC0 is single-ended and all signals measured are with respect to GND.** The ADC0 input channels are selected using the ADC0MX register as described in SFR Definition 4.4.

**Important Note About ADC0 Input Configuration:** Port pins selected as ADC0 inputs should be configured as analog inputs, and should be skipped by the Digital Crossbar. To configure a Port pin for analog input, set to 0 the corresponding bit in register PnMDIN (for n = 0,1). To force the Crossbar to skip a Port pin, set to 1 the corresponding bit in register PnSKIP (for n = 0,1). See Section "13. Port Input/Output" on page 120 for more Port I/O configuration details.

#### 4.3. ADC0 Operation

In a typical system, ADC0 is configured using the following steps:

- 1. If a gain adjustment is required, refer to Section "4.4. Selectable Gain" on page 60.

- 2. Choose the start of conversion source.

- 3. Choose Normal Mode or Burst Mode operation.

- 4. If Burst Mode, choose the ADC0 Idle Power State and set the Power-Up Time.

- 5. Choose the tracking mode. Note that Pre-Tracking Mode can only be used with Normal Mode.

- 6. Calculate required settling time and set the post convert-start tracking time using the AD0TK bits.

- 7. Choose the repeat count.

- 8. Choose the output word justification (Right-Justified or Left-Justified).

- 9. Enable or disable the End of Conversion and Window Comparator Interrupts.

#### 4.3.1. Starting a Conversion

A conversion can be initiated in one of four ways, depending on the programmed states of the ADC0 Start of Conversion Mode bits (AD0CM1–0) in register ADC0CN. Conversions may be initiated by one of the following:

- Writing a 1 to the AD0BUSY bit of register ADC0CN

- A rising edge on the CNVSTR input signal (pin P0.6)

- A Timer 1 overflow (i.e., timed continuous conversions)

- A Timer 2 overflow (i.e., timed continuous conversions)

Writing a 1 to AD0BUSY provides software control of ADC0 whereby conversions are performed "ondemand." During conversion, the AD0BUSY bit is set to logic 1 and reset to logic 0 when the conversion is complete. The falling edge of AD0BUSY triggers an interrupt (when enabled) and sets the ADC0 interrupt flag (AD0INT). Note: When polling for ADC conversion completions, the ADC0 interrupt flag (AD0INT) should be used. Converted data is available in the ADC0 data registers, ADC0H:ADC0L, when bit AD0INT is logic 1. Note that when Timer 2 overflows are used as the conversion source, Low Byte overflows are used if Timer2 is in 8-bit mode; High byte overflows are used if Timer 2 is in 16-bit mode. See Section "18. Timers" on page 182 for timer configuration.

**Important Note:** The CNVSTR input pin also functions as Port pin P0.5 on C8051F52x/52xA devices and P1.2 on C8051F53x/53xA devices. When the CNVSTR input is used as the ADC0 conversion source, Port pin P0.5 or P1.2 should be skipped by the Digital Crossbar. To configure the Crossbar to skip P0.5 or P1.2, set to 1 to the appropriate bit in the PnSKIP register. See Section "13. Port Input/Output" on page 120 for details on Port I/O configuration.

#### 4.3.2. Tracking Modes

Each ADC0 conversion must be preceded by a minimum tracking time for the converted result to be accurate, as shown in Table 2.3 on page 28. ADC0 has three tracking modes: Pre-Tracking, Post-Tracking, and Dual-Tracking. Pre-Tracking Mode provides the minimum delay between the convert start signal and end of conversion by tracking continuously before the convert start signal. This mode requires software management in order to meet minimum tracking requirements. In Post-Tracking Mode, a programmable tracking time starts after the convert start signal and is managed by hardware. Dual-Tracking Mode maximizes tracking time by tracking before and after the convert start signal. Figure 4.3 shows examples of the three tracking modes.

Pre-Tracking Mode is selected when AD0TM is set to 10b. Conversions are started immediately following the convert start signal. ADC0 is tracking continuously when not performing a conversion. Software must allow at least the minimum tracking time between each end of conversion and the next convert start signal. The minimum tracking time must also be met prior to the first convert start signal after ADC0 is enabled.

| Co        | nvert Start — | ≻ |    |        |         |      |      |        |          |        |         |        |      |     |  |

|-----------|---------------|---|----|--------|---------|------|------|--------|----------|--------|---------|--------|------|-----|--|

|           |               |   |    |        |         |      |      | Pre    | -Tracki  | ng Moo | de      |        |      |     |  |

| (         | Time          |   | F  | S1     | S2      | ] .  | [    | S12    | S13      | F      |         |        |      |     |  |

| ł         | ADC0 State    |   |    |        |         | Con  | ver  | t      |          |        |         |        |      |     |  |

|           | AD0INT Flag   |   |    |        |         |      |      |        |          |        |         |        |      |     |  |

|           |               |   |    | F      | Post-Tr | acki | ng d | or Dua | Il-Track | ing Mc | odes (A | D0TK = | = '0 | 0') |  |

| ſ         | Time          |   | F  | S1     | S2      | F    | F    | S1     | S2       | ]      | S12     | S13    | F    |     |  |

| $\langle$ | ADC0 State    |   |    | Tra    | ack     |      |      |        |          | Convei | rt      |        |      |     |  |

| Ĺ         | AD0INT Flag   |   |    |        |         |      |      |        |          |        |         |        |      |     |  |

|           |               |   | Ke | y<br>] | Equal   | to c | one  | period | of FCL   | _K.    |         |        |      |     |  |

F

Sn

Each Sn is equal to one period of the SAR clock.

Figure 4.4. 12-Bit ADC Tracking Mode Example

## SFR Definition 6.1. REG0CN: Regulator Control

| R/W      | R/W                                    | R                                                | R/W           | R            | R       | R    | R            | Reset Value |  |  |  |  |  |  |

|----------|----------------------------------------|--------------------------------------------------|---------------|--------------|---------|------|--------------|-------------|--|--|--|--|--|--|

| REGDIS   | 8 Reserved                             |                                                  | REG0MD        |              |         |      | DROPOUT      | 01010000    |  |  |  |  |  |  |

| Bit7     | Bit6                                   | Bit5                                             | Bit4          | Bit3         | Bit2    | Bit1 | Bit0         |             |  |  |  |  |  |  |

|          |                                        |                                                  |               |              |         |      | SFR Address: | 0xC9        |  |  |  |  |  |  |

|          |                                        |                                                  |               |              |         |      |              |             |  |  |  |  |  |  |

| Bit7:    | REGDIS: Voltage Regulator Disable Bit. |                                                  |               |              |         |      |              |             |  |  |  |  |  |  |

|          | This bit disat                         | This bit disables/enables the Voltage Regulator. |               |              |         |      |              |             |  |  |  |  |  |  |

|          | 0: Voltage R                           | ): Voltage Regulator Enabled.                    |               |              |         |      |              |             |  |  |  |  |  |  |

|          | 1: Voltage Re                          | 1: Voltage Regulator Disabled.                   |               |              |         |      |              |             |  |  |  |  |  |  |

| Bit6:    | RESERVED                               | . Read = 11                                      | o. Must write | e 1b.        |         |      |              |             |  |  |  |  |  |  |

| Bit5:    | UNUSED. R                              | ead = 0b. V                                      | Vrite = don't | care.        |         |      |              |             |  |  |  |  |  |  |

| Bit4:    | REGOMD: V                              | oltage Reg                                       | ulator Mode   | Select Bit.  |         |      |              |             |  |  |  |  |  |  |

|          | This bit selec                         | cts the Volt                                     | age Regulat   | or output vo | oltage. |      |              |             |  |  |  |  |  |  |

|          | 0: Voltage R                           | egulator ou                                      | tput is 2.1 V |              |         |      |              |             |  |  |  |  |  |  |

|          | 1: Voltage R                           | egulator ou                                      | tput is 2.6 V | ' (default). |         |      |              |             |  |  |  |  |  |  |

| Bits3–1: | UNUSED. R                              | ead = 000b                                       | o. Write = do | n't care.    |         |      |              |             |  |  |  |  |  |  |

| Bit0:    | DROPOUT:                               | Voltage Re                                       | gulator Drop  | out Indicat  | or Bit. |      |              |             |  |  |  |  |  |  |

|          | 0: Voltage R                           | egulator is                                      | not in dropo  | ut.          |         |      |              |             |  |  |  |  |  |  |

|          | 1: Voltage R                           | egulator is                                      | in or near dı | ropout.      |         |      |              |             |  |  |  |  |  |  |

|          |                                        |                                                  |               |              |         |      |              |             |  |  |  |  |  |  |

#### Notes on Registers, Operands and Addressing Modes:

**Rn** - Register R0–R7 of the currently selected register bank.

@Ri - Data RAM location addressed indirectly through R0 or R1.

**rel** - 8-bit, signed (two's complement) offset relative to the first byte of the following instruction. Used by SJMP and all conditional jumps.

**direct** - 8-bit internal data location's address. This could be a direct-access Data RAM location (0x00– 0x7F) or an SFR (0x80–0xFF).

#data - 8-bit constant

#data16 - 16-bit constant

**bit** - Direct-accessed bit in Data RAM or SFR

**addr11** - 11-bit destination address used by ACALL and AJMP. The destination must be within the same 2 kB page of program memory as the first byte of the following instruction.

**addr16** - 16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 7680 bytes of program memory space.

There is one unused opcode (0xA5) that performs the same function as NOP. All mnemonics copyrighted © Intel Corporation 1980.

#### 8.2. Register Descriptions

Following are descriptions of SFRs related to the operation of the CIP-51 System Controller. Reserved bits should not be set to logic 1. Future product versions may use these bits to implement new features in which case the reset value of the bit will be logic 0, selecting the feature's default state. Detailed descriptions of the remaining SFRs are included in the sections of the datasheet associated with their corresponding system function.

## SFR Definition 8.7. PCON: Power Control

| R/W                  | R/W            | R/W                                                                                                                           | R/W           | R/W           | R/W           | R/W            | R/W           | Reset Value |  |  |  |  |  |

|----------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|---------------|----------------|---------------|-------------|--|--|--|--|--|

| Reserved             | d Reserved     | Reserved                                                                                                                      | Reserved      | Reserved      | Reserved      | STOP           | IDLE          | 00000000    |  |  |  |  |  |

| Bit7                 | Bit6           | Bit5                                                                                                                          | Bit4          | Bit3          | Bit2          | Bit1           | Bit0          | _           |  |  |  |  |  |

|                      |                |                                                                                                                               |               |               |               |                | SFR Address   | : 0x87      |  |  |  |  |  |

| Rits7_2 <sup>.</sup> | RESERVED       |                                                                                                                               |               |               |               |                |               |             |  |  |  |  |  |

|                      |                | •                                                                                                                             | oot           |               |               |                |               |             |  |  |  |  |  |

| DILI.                |                | <b>STOP</b> : STOP Mode Select.<br>Vriting a 1 to this bit will place the CIP-51 into STOP mode. This bit will always read 0. |               |               |               |                |               |             |  |  |  |  |  |

|                      | •              |                                                                                                                               | •             |               |               |                |               | ead 0.      |  |  |  |  |  |

|                      | 1: CIP-51 for  | ced into po                                                                                                                   | wer-down r    | node. (Turn   | s off interna | al oscillator) | ).            |             |  |  |  |  |  |

| Bit0:                | IDLE: IDLE I   | Mode Selec                                                                                                                    | :t.           |               |               | ,              |               |             |  |  |  |  |  |

|                      | Writing a 1 to | thic bit wil                                                                                                                  | l placa tha ( | CID 51 into   |               | Thic bit w     | ill always ro | ad 0        |  |  |  |  |  |

|                      | •              |                                                                                                                               | •             |               |               |                | •             |             |  |  |  |  |  |

|                      | 1: CIP-51 for  |                                                                                                                               | `             | Shuts off clo | ock to CPU,   | but clock t    | o Timers, In  | iterrupts,  |  |  |  |  |  |

|                      | and all perip  | herals rema                                                                                                                   | ain active.)  |               |               |                |               |             |  |  |  |  |  |

|                      |                |                                                                                                                               | ,             |               |               |                |               |             |  |  |  |  |  |

|                      |                |                                                                                                                               |               |               |               |                |               |             |  |  |  |  |  |

### SFR Definition 10.3. EIE1: Extended Interrupt Enable 1

| EMAT         EREGO         ELIN         ECPR         ECPF         EPCA0         EADC0         EWADC0         00000000           Bit7         Bit6         Bit5         Bit4         Bit3         Bit2         Bit1         Bit0         SFR Address:         0xE6           Bit7:         EMAT: Enable Port Match Interrupt.         This bit sets the masking of the Port Match interrupt.         Bit3         Bit2         Bit1         Bit0         SFR Address:         0xE6           Bit7:         EMAT: Enable Port Match Interrupt.         This bit sets the masking of the Voltage Regulator Dropout interrupt.         Disable the Port Match Interrupt.         This bit sets the masking of the Voltage Regulator Dropout Interrupt.         0. Disable the Voltage Regulator Dropout Interrupt.         1: Enable the Voltage Regulator Dropout Interrupt.         1: Enable the Voltage Regulator Dropout Interrupt.         0. Disable LIN Interrupt.         1: Enable LIN Interrupt.         1: Enable LIN Interrupt.         1: Enable COP Rising Edge Interrupt.         1: Enable COP Rising Edge Interrupt.         1: Enable COP Rising Edge Interrupt.         1: Enable CPO Rising Edge Interrupt.         1: Enable CPO Falling Edge Interrupt.         1: Enable COP Falling Edge Interrupt.         1: Enable CPO Falling Edge Interrupt.         1: Enable C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W   | R/W                                                                                                                                                                                | R/W         | R/W          | R/W           | R/W          | R/W          | R/W          | Reset Value |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|---------------|--------------|--------------|--------------|-------------|--|--|--|--|--|--|

| <ul> <li>SFR Address: 0xE6</li> <li>Bit7: EMAT: Enable Port Match Interrupt.<br/>This bit sets the masking of the Port Match interrupt.<br/>Disable the Port Match interrupt.<br/>1: Enable the Port Match interrupt.<br/>1: Enable the Port Match interrupt.<br/>This bit sets the masking of the Voltage Regulator Dropout interrupt.<br/>Disable the Voltage Regulator Dropout interrupt.<br/>1: Enable the Voltage Regulator Dropout interrupt.<br/>Disable the Voltage Regulator Dropout interrupt.<br/>1: Enable the Voltage Regulator Dropout interrupt.<br/>1: Enable the Voltage Regulator Dropout interrupt.<br/>Bit5: ELIN: Enable LIN Interrupt.<br/>This bit sets the masking of the LIN interrupt.<br/>Disable LIN interrupts.<br/>1: Enable LIN interrupts.<br/>1: Enable LIN interrupts.<br/>1: Enable COP Rising Edge Interrupt<br/>This bit sets the masking of the CPO Rising Edge interrupt.<br/>Disable CPO Rising Edge Interrupt.<br/>1: Enable CPO Rising Edge Interrupt.<br/>3: Enable CPO Falling Edge Interrupt.<br/>1: Enable CPO Falling Edge Interrupt.<br/>3: Enable CPO Falling Edge Interrupt.<br/>1: Enable CPO Falling Edge Interrupt.<br/>3: Enable ADCO Conversion Complete Interrupt.<br/>3: Enable all PCA0 interrupts.<br/>3: Enable ADCO Conversion Complete Interrupt.<br/>3: Enable ADCO Window Comparison Interrupt.<br/>3: Enable ADCO Window Comparison Interrupt.<br/>3: Disable ADCO Window Comparison</li></ul> | EMAT  | EREG0                                                                                                                                                                              | ELIN        | ECPR         | ECPF          | EPCA0        | EADC0        | EWADC0       | 00000000    |  |  |  |  |  |  |

| <ul> <li>Bit7: EMAT: Enable Port Match Interrupt.<br/>This bit sets the masking of the Port Match interrupt.<br/>O Disable the Port Match interrupt.<br/>1: Enable the Port Match interrupt.<br/>Bit6: EREGO: Enable Voltage Regulator Interrupt.<br/>This bit sets the masking of the Voltage Regulator Dropout interrupt.<br/>O: Disable the Voltage Regulator Dropout interrupt.<br/>1: Enable the Voltage Regulator Dropout interrupt.<br/>Disable the Voltage Regulator Dropout interrupt.<br/>1: Enable the Voltage Regulator Dropout interrupt.<br/>Disable the Voltage Regulator Dropout interrupt.<br/>Bit5: ELIN: Enable LIN Interrupt.<br/>This bit sets the masking of the LIN interrupt.<br/>0: Disable LIN interrupts.<br/>1: Enable LIN interrupts.<br/>1: Enable COP Rising Edge Interrupt<br/>This bit sets the masking of the CPO Rising Edge interrupt.<br/>0: Disable CPO Rising Edge Interrupt.<br/>1: Enable CPO Rising Edge Interrupt.<br/>1: Enable CPO Rising Edge Interrupt.<br/>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt<br/>This bit sets the masking of the CPO Falling Edge Interrupt.<br/>1: Enable CPO Falling Edge Interrupt.<br/>Bit4: ECPR: Enable Comparator 0 Falling Edge Interrupt.<br/>1: Enable CPO Falling Edge Interrupt.<br/>Bit5: ECPF: Enable Comparator 0 Falling Edge Interrupt.<br/>1: Enable CPO Falling Edge Interrupt.<br/>Bit6: EPCA0: Enable Programmable Counter Array (PCA0) Interrupt.<br/>This bit sets the masking of the PCA0 interrupts.<br/>1: Enable interrupt requests generated by PCA0.<br/>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.<br/>1: Enable interrupt requests generated by PCA0.<br/>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.<br/>1: Enable interrupt requests generated by the AD0INT flag.<br/>Bit0: EWADC0: Enable ADC0 Window Comparison Interrupt.<br/>This bit sets the masking of the ADC0 Window Comparison interrupt.<br/>0: Disable ADC0 Window Comparison Interrupt</li></ul>                | Bit7  | Bit6                                                                                                                                                                               | Bit5        | Bit4         | Bit3          | Bit2         | Bit1         | Bit0         | •           |  |  |  |  |  |  |

| <ul> <li>This bit sets the masking of the Port Match interrupt.</li> <li>0: Disable the Port Match interrupt.</li> <li>1: Enable the Port Match interrupt.</li> <li>1: Enable the Port Match interrupt.</li> <li>Bit6: EREG0: Enable Voltage Regulator Interrupt.</li> <li>This bit sets the masking of the Voltage Regulator Dropout interrupt.</li> <li>0: Disable the Voltage Regulator Dropout interrupt.</li> <li>1: Enable the Voltage Regulator Dropout interrupt.</li> <li>1: Enable LIN Interrupt.</li> <li>This bit sets the masking of the LIN interrupt.</li> <li>0: Disable LIN Interrupt.</li> <li>This bit sets the masking of the LIN interrupt.</li> <li>0: Disable LIN interrupts.</li> <li>1: Enable LIN interrupt requests.</li> <li>Bit4: ECPR: Enable Comparator 0 Rising Edge Interrupt</li> <li>This bit sets the masking of the CPO Rising Edge interrupt.</li> <li>0: Disable CPO Rising Edge Interrupt.</li> <li>1: Enable CPO Rising Edge Interrupt.</li> <li>1: Enable CPO Rising Edge Interrupt.</li> <li>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt.</li> <li>0: Disable CPO Ralling Edge Interrupt.</li> <li>Bit4: ECPR: Enable Comparator 0 Falling Edge Interrupt.</li> <li>0: Disable CPO Falling Edge Interrupt.</li> <li>1: Enable Programmable Counter Array (PCA0) Interrupt.</li> <li>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable ADCO Conversion Complete Interrupt.</li> <li>1: Enable ADCO Window Comparison Interrupt.</li> <li>1: Enable ADCO Window Comparison Interrupt.</li> <li>1: Disable ADCO Window Comp</li></ul>                                                                                                                                           |       |                                                                                                                                                                                    |             |              |               |              |              | SFR Address: | 0xE6        |  |  |  |  |  |  |

| <ul> <li>This bit sets the masking of the Port Match interrupt.</li> <li>0: Disable the Port Match interrupt.</li> <li>1: Enable the Port Match interrupt.</li> <li>1: Enable the Port Match interrupt.</li> <li>Bit6: EREG0: Enable Voltage Regulator Interrupt.</li> <li>This bit sets the masking of the Voltage Regulator Dropout interrupt.</li> <li>0: Disable the Voltage Regulator Dropout interrupt.</li> <li>1: Enable the Voltage Regulator Dropout interrupt.</li> <li>1: Enable LIN Interrupt.</li> <li>This bit sets the masking of the LIN interrupt.</li> <li>0: Disable LIN Interrupt.</li> <li>This bit sets the masking of the LIN interrupt.</li> <li>0: Disable LIN interrupts.</li> <li>1: Enable LIN interrupt requests.</li> <li>Bit4: ECPR: Enable Comparator 0 Rising Edge Interrupt</li> <li>This bit sets the masking of the CPO Rising Edge interrupt.</li> <li>0: Disable CPO Rising Edge Interrupt.</li> <li>1: Enable CPO Rising Edge Interrupt.</li> <li>1: Enable CPO Rising Edge Interrupt.</li> <li>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt.</li> <li>0: Disable CPO Ralling Edge Interrupt.</li> <li>Bit4: ECPR: Enable Comparator 0 Falling Edge Interrupt.</li> <li>0: Disable CPO Falling Edge Interrupt.</li> <li>1: Enable Programmable Counter Array (PCA0) Interrupt.</li> <li>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable ADCO Conversion Complete Interrupt.</li> <li>1: Enable ADCO Window Comparison Interrupt.</li> <li>1: Enable ADCO Window Comparison Interrupt.</li> <li>1: Disable ADCO Window Comp</li></ul>                                                                                                                                           |       |                                                                                                                                                                                    |             |              |               |              |              |              |             |  |  |  |  |  |  |

| <ul> <li>0: Disable the Port Match interrupt.</li> <li>1: Enable the Port Match interrupt.</li> <li>Bit6: EREG0: Enable Voltage Regulator Interrupt.<br/>This bit sets the masking of the Voltage Regulator Dropout interrupt.</li> <li>0: Disable the Voltage Regulator Dropout interrupt.</li> <li>1: Enable the Voltage Regulator Dropout interrupt.</li> <li>1: Enable the Voltage Regulator Dropout interrupt.</li> <li>Bit5: ELIN: Enable LIN Interrupt.<br/>This bit sets the masking of the LIN interrupt.</li> <li>0: Disable LIN interrupt requests.</li> <li>Bit4: ECPR: Enable Comparator 0 Rising Edge Interrupt<br/>This bit sets the masking of the CP0 Rising Edge interrupt.</li> <li>0: Disable CP0 Rising Edge Interrupt.</li> <li>1: Enable CP0 Rising Edge Interrupt.</li> <li>1: Enable CP0 Rising Edge Interrupt.</li> <li>1: Enable CP0 Rising Edge Interrupt.</li> <li>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>Bit2: EPCA0: Enable Programmable Counter Array (PCA0) Interrupt.</li> <li>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable ADC0 Conversion Complete Interrupt.</li> <li>1: Enable ADC0 Window Comparison Interrupt.</li> <li>1: Bit sets the masking of the ADC0 Window Comparison Interrupt.</li> <li>1: Disable ADC0 Window Comparison Interrupt.<th>Bit7:</th><th>EMAT: Enab</th><th>le Port Mat</th><th>ch Interrupt</th><th></th><th></th><th></th><th></th><th></th></li></ul>           | Bit7: | EMAT: Enab                                                                                                                                                                         | le Port Mat | ch Interrupt |               |              |              |              |             |  |  |  |  |  |  |

| <ul> <li>1: Enable the Port Match interrupt.</li> <li>Bit6: EREG0: Enable Voltage Regulator Interrupt.<br/>This bit sets the masking of the Voltage Regulator Dropout interrupt.<br/>0: Disable the Voltage Regulator Dropout interrupt.</li> <li>1: Enable the Voltage Regulator Dropout interrupt.</li> <li>Bit5: ELIN: Enable LIN Interrupt.<br/>This bit sets the masking of the LIN interrupt.<br/>0: Disable LIN interrupts.</li> <li>Bit4: ECPR: Enable Comparator 0 Rising Edge Interrupt<br/>This bit sets the masking of the CP0 Rising Edge interrupt.</li> <li>0: Disable CP0 Rising Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>1: Enable PCA0 interrupts.</li> <li>0: Disable ADC0 Conversion Complete Interrupt.</li> <li>1: Enable interrupt requests generated by PCA0.</li> <li>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.</li> <li>1: Enable interrupt requests generated by the AD0INT flag.</li> <li>Bit0: EWADC0: Enable ADC0 Window Comparison Interrupt.</li> <li>1: Sisable ADC0 Window Comparison Interrupt.</li> <li>1: Sisable ADC0 Window Comparison Interrupt.</li> <li>1: Sisable ADC0 Window Comparison Interrupt.</li> <li>1: Disable ADC0 Window Comparison Interrupt.</li> </ul>                                                                                                                                                                                              |       |                                                                                                                                                                                    |             |              |               | errupt.      |              |              |             |  |  |  |  |  |  |

| <ul> <li>Bit6: EREG0: Enable Voltage Regulator Interrupt.<br/>This bit sets the masking of the Voltage Regulator Dropout interrupt.<br/>0: Disable the Voltage Regulator Dropout interrupt.<br/>1: Enable the Voltage Regulator Dropout interrupt.<br/>1: Enable LIN Interrupt.<br/>This bit sets the masking of the LIN interrupt.<br/>0: Disable LIN interrupt.<br/>This bit sets the masking of the LIN interrupt<br/>0: Disable LIN interrupt requests.<br/>Bit4: ECPR: Enable Comparator 0 Rising Edge Interrupt<br/>This bit sets the masking of the CP0 Rising Edge interrupt.<br/>0: Disable CP0 Rising Edge Interrupt.<br/>1: Enable CP0 Rising Edge Interrupt.<br/>1: Enable CP0 Rising Edge Interrupt.<br/>1: Enable CP0 Rising Edge Interrupt.<br/>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt.<br/>Di Disable CP0 Falling Edge Interrupt.<br/>Bit4: ECPR: Enable Comparator 0 Falling Edge Interrupt.<br/>Bit5: ECPF: Enable Comparator 0 Falling Edge Interrupt.<br/>Bit6: ECPF: Enable Comparator 0 Falling Edge Interrupt.<br/>Bit6: ECPC Falling Edge Interrupt.<br/>Bit2: EPCA0: Enable Programmable Counter Array (PCA0) Interrupt.<br/>This bit sets the masking of the PCA0 interrupts.<br/>0: Disable all PCA0 interrupts.<br/>1: Enable interrupt requests generated by PCA0.<br/>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.<br/>This bit sets the masking of the ADC0 Conversion Complete interrupt.<br/>0: Disable ADC0 Conversion Complete Interrupt.<br/>Bit0: EWADC0: Enable ADC0 Window Comparison Interrupt.<br/>This bit sets the masking of the ADC0 Window Comparison interrupt.<br/>0: Disable ADC0 Window Comparison interrupt.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                          |       | 0: Disable the Port Match interrupt.                                                                                                                                               |             |              |               |              |              |              |             |  |  |  |  |  |  |

| <ul> <li>This bit sets the masking of the Voltage Regulator Dropout interrupt.</li> <li>0: Disable the Voltage Regulator Dropout interrupt.</li> <li>1: Enable the Voltage Regulator Dropout interrupt.</li> <li>Bit5: ELIN: Enable LIN Interrupt.</li> <li>This bit sets the masking of the LIN interrupt.</li> <li>0: Disable LIN interrupts.</li> <li>1: Enable LIN interrupt requests.</li> <li>Bit4: ECPR: Enable Comparator 0 Rising Edge Interrupt</li> <li>This bit sets the masking of the CP0 Rising Edge Interrupt.</li> <li>0: Disable CP0 Rising Edge Interrupt.</li> <li>1: Enable CP0 Rising Edge Interrupt.</li> <li>0: Disable CP0 Rising Edge Interrupt.</li> <li>1: Enable COMparator 0 Falling Edge Interrupt.</li> <li>0: Disable CP0 Rising Edge Interrupt.</li> <li>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt.</li> <li>0: Disable CP0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>0: Disable CP0 Falling Edge Interrupt.</li> <li>1: Enable Interrupt requests generated by PCA0.</li> <li>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.</li> <li>1: Enable Interrupt requests generated by PCA0.</li> <li>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.</li> <li>1: Enable Interrupt requests generated by the ADOINT flag.</li> <li>Bit0: EWADC0: Enable ADC0 Window Comparison Interrupt.</li> <li>1: Enable ADC0 Window Comparison Interrupt.</li> <li>1: Disable ADC0 Window Comparison Interrupt.</li> <li>1: Disable ADC0 Window Comparison Interrupt.</li> <li>1: Disable ADC0 Window Comparison Interrupt.</li> </ul>                                                                                                                                                                                                                 |       |                                                                                                                                                                                    |             |              |               |              |              |              |             |  |  |  |  |  |  |

| <ul> <li>0: Disable the Voltage Regulator Dropout interrupt.</li> <li>1: Enable the Voltage Regulator Dropout interrupt.</li> <li>Bit5: ELIN: Enable LIN Interrupt.<br/>This bit sets the masking of the LIN interrupt.</li> <li>0: Disable LIN interrupts.</li> <li>1: Enable LIN interrupts.</li> <li>1: Enable Comparator 0 Rising Edge Interrupt</li> <li>This bit sets the masking of the CP0 Rising Edge interrupt.</li> <li>0: Disable CP0 Rising Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>3: ECPF: Enable Comparator 0 Falling Edge Interrupt.</li> <li>0: Disable CP0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>3: Enable CP0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>3: Enable CP0 Falling Edge Interrupt.</li> <li>3: Enable CP0 Falling Edge Interrupt.</li> <li>3: Enable CP0 Falling Edge Interrupt.</li> <li>4: Enable Programmable Counter Array (PCA0) Interrupt.</li> <li>5: Disable all PCA0 interrupts.</li> <li>1: Enable Interrupt requests generated by PCA0.</li> <li>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.</li> <li>3: Disable ADC0 Conversion Complete Interrupt.</li> <li>4: Enable ADC0 Conversion Complete Interrupt.</li> <li>4: Enable ADC0 Conversion Complete Interrupt.</li> <li>4: Enable ADC0 Conversion Complete Interrupt.</li> <li>5: Enable ADC0 Conversion Complete Interrupt.</li> <li>5: Enable ADC0 Enable ADC0 Window Comparison Interrupt.</li> <li>5: Disable ADC0 Window Comparison Interrupt.</li> </ul>                                                                                                                                                                              | Bit6: | <b>EREG0</b> : Enable Voltage Regulator Interrupt.<br>This bit sets the masking of the Voltage Regulator Dropout interrupt.<br>0: Disable the Voltage Regulator Dropout interrupt. |             |              |               |              |              |              |             |  |  |  |  |  |  |

| <ul> <li>1: Enable the Voltage Regulator Dropout interrupt.</li> <li>Bit5: ELIN: Enable LIN Interrupt.<br/>This bit sets the masking of the LIN interrupt.<br/>0: Disable LIN interrupts.<br/>1: Enable LIN interrupts.<br/>1: Enable LIN interrupts.</li> <li>Bit4: ECPR: Enable Comparator 0 Rising Edge Interrupt<br/>This bit sets the masking of the CP0 Rising Edge interrupt.<br/>0: Disable CP0 Rising Edge Interrupt.<br/>1: Enable CP0 Rising Edge Interrupt.<br/>1: Enable CP0 Rising Edge Interrupt.</li> <li>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt<br/>This bit sets the masking of the CP0 Falling Edge interrupt.<br/>0: Disable CP0 Falling Edge Interrupt.<br/>1: Enable CP0 Falling Edge Interrupt.<br/>1: Enable CP0 Falling Edge Interrupt.<br/>1: Enable CP0 Falling Edge Interrupt.</li> <li>Bit2: EPCA0: Enable Programmable Counter Array (PCA0) Interrupt.<br/>This bit sets the masking of the PCA0 interrupts.<br/>0: Disable all PCA0 interrupts.<br/>1: Enable interrupt requests generated by PCA0.</li> <li>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.<br/>This bit sets the masking of the ADC0 Conversion Complete interrupt.<br/>0: Disable ADC0 Conversion Complete Interrupt.<br/>1: Enable interrupt requests generated by the AD0INT flag.</li> <li>Bit0: EWADC0: Enable ADC0 Window Comparison Interrupt.<br/>This bit sets the masking of the ADC0 Window Comparison interrupt.<br/>0: Disable ADC0 Window Comparison Interrupt.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |                                                                                                                                                                                    |             |              |               |              |              |              |             |  |  |  |  |  |  |

| <ul> <li>Bit5: ELIN: Enable LIN Interrupt.<br/>This bit sets the masking of the LIN interrupt.<br/>0: Disable LIN interrupts.<br/>1: Enable LIN interrupt requests.</li> <li>Bit4: ECPR: Enable Comparator 0 Rising Edge Interrupt<br/>This bit sets the masking of the CP0 Rising Edge interrupt.<br/>0: Disable CP0 Rising Edge Interrupt.<br/>1: Enable COP Rising Edge Interrupt.<br/>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt<br/>This bit sets the masking of the CP0 Falling Edge interrupt.<br/>0: Disable CP0 Falling Edge Interrupt.<br/>1: Enable CP0 Falling Edge Interrupt.<br/>0: Disable CP0 Falling Edge Interrupt.<br/>1: Enable CP0 Falling Edge Interrupt.<br/>Bit2: EPCA0: Enable Programmable Counter Array (PCA0) Interrupt.<br/>This bit sets the masking of the PCA0 interrupts.<br/>0: Disable all PCA0 interrupts.<br/>1: Enable interrupt requests generated by PCA0.<br/>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.<br/>This bit sets the masking of the ADC0 Conversion Complete interrupt.<br/>0: Disable ADC0 Conversion Complete Interrupt.<br/>1: Enable interrupt requests generated by the AD0INT flag.<br/>Bit0: EWADC0: Enable ADC0 Window Comparison Interrupt.<br/>This bit sets the masking of the ADC0 Window Comparison interrupt.<br/>0: Disable ADC0 Window Comparison interrupt.</li> </ul>                                                                                                                                                                                                                                                   |       |                                                                                                                                                                                    |             |              |               |              |              |              |             |  |  |  |  |  |  |

| <ul> <li>This bit sets the masking of the LIN interrupt.</li> <li>0: Disable LIN interrupts.</li> <li>1: Enable LIN interrupt requests.</li> <li>Bit4: ECPR: Enable Comparator 0 Rising Edge Interrupt</li> <li>This bit sets the masking of the CP0 Rising Edge interrupt.</li> <li>0: Disable CP0 Rising Edge Interrupt.</li> <li>1: Enable Comparator 0 Falling Edge Interrupt</li> <li>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt.</li> <li>0: Disable CP0 Falling Edge Interrupt.</li> <li>Bit4: ECPR: Enable Comparator 0 Falling Edge Interrupt.</li> <li>0: Disable CP0 Falling Edge Interrupt.</li> <li>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt.</li> <li>0: Disable CP0 Falling Edge Interrupt.</li> <li>Bit2: EPCA0: Enable Programmable Counter Array (PCA0) Interrupt.</li> <li>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable interrupt requests generated by PCA0.</li> <li>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.</li> <li>This bit sets the masking of the ADC0 Conversion Complete interrupt.</li> <li>0: Disable ADC0 Conversion Complete Interrupt.</li> <li>1: Enable interrupt requests generated by the AD0INT flag.</li> <li>Bit0: EWADC0: Enable ADC0 Window Comparison Interrupt.</li> <li>This bit sets the masking of the ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison Interrupt.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | 1: Enable the Voltage Regulator Dropout interrupt.                                                                                                                                 |             |              |               |              |              |              |             |  |  |  |  |  |  |

| <ul> <li>0: Disable LIN interrupts.</li> <li>1: Enable LIN interrupt requests.</li> <li>Bit4: ECPR: Enable Comparator 0 Rising Edge Interrupt<br/>This bit sets the masking of the CP0 Rising Edge interrupt.</li> <li>0: Disable CP0 Rising Edge Interrupt.</li> <li>1: Enable CP0 Rising Edge Interrupt.</li> <li>1: Enable CP0 Rising Edge Interrupt.</li> <li>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt<br/>This bit sets the masking of the CP0 Falling Edge interrupt.</li> <li>0: Disable CP0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>Bit2: EPCA0: Enable Programmable Counter Array (PCA0) Interrupt.<br/>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable interrupt requests generated by PCA0.</li> <li>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.</li> <li>This bit sets the masking of the ADC0 conversion Complete interrupt.</li> <li>0: Disable ADC0 Conversion Complete Interrupt.</li> <li>1: Enable interrupt requests generated by the AD0INT flag.</li> <li>Bit0: EWADC0: Enable ADC0 Window Comparison Interrupt.</li> <li>This bit sets the masking of the ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison Interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Bit5: |                                                                                                                                                                                    |             |              |               |              |              |              |             |  |  |  |  |  |  |

| <ul> <li>1: Enable LIN interrupt requests.</li> <li>Bit4: ECPR: Enable Comparator 0 Rising Edge Interrupt<br/>This bit sets the masking of the CP0 Rising Edge interrupt.</li> <li>0: Disable CP0 Rising Edge Interrupt.</li> <li>1: Enable CP0 Rising Edge Interrupt.</li> <li>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt<br/>This bit sets the masking of the CP0 Falling Edge interrupt.</li> <li>0: Disable CP0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>Bit2: EPCA0: Enable Programmable Counter Array (PCA0) Interrupt.<br/>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable interrupt requests generated by PCA0.</li> <li>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.<br/>This bit sets the masking of the ADC0 Conversion Complete interrupt.</li> <li>0: Disable ADC0 Conversion Complete Interrupt.</li> <li>1: Enable interrupt requests generated by the ADOINT flag.</li> <li>Bit0: EWADC0: Enable ADC0 Window Comparison Interrupt.</li> <li>This bit sets the masking of the ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |                                                                                                                                                                                    |             |              | I interrupt.  |              |              |              |             |  |  |  |  |  |  |

| <ul> <li>Bit4: ECPR: Enable Comparator 0 Rising Edge Interrupt<br/>This bit sets the masking of the CP0 Rising Edge interrupt.</li> <li>0: Disable CP0 Rising Edge Interrupt.</li> <li>1: Enable CP0 Rising Edge Interrupt.</li> <li>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt<br/>This bit sets the masking of the CP0 Falling Edge interrupt.</li> <li>0: Disable CP0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>Bit2: EPCA0: Enable Programmable Counter Array (PCA0) Interrupt.<br/>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable interrupt requests generated by PCA0.</li> <li>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.</li> <li>0: Disable ADC0 Conversion Complete Interrupt.</li> <li>1: Enable interrupt requests generated by the AD0INT flag.</li> <li>Bit0: EWADC0: Enable ADC0 Window Comparison Interrupt.</li> <li>0: Disable ADC0 Window Comparison Interrupt.</li> <li>0: Disable ADC0 Window Comparison Interrupt.</li> <li>0: Disable ADC0 Window Comparison Interrupt.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |                                                                                                                                                                                    |             |              |               |              |              |              |             |  |  |  |  |  |  |

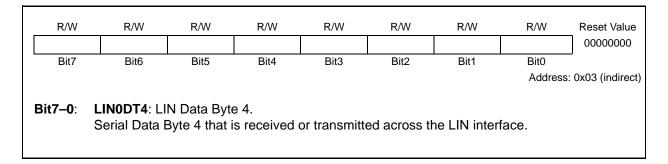

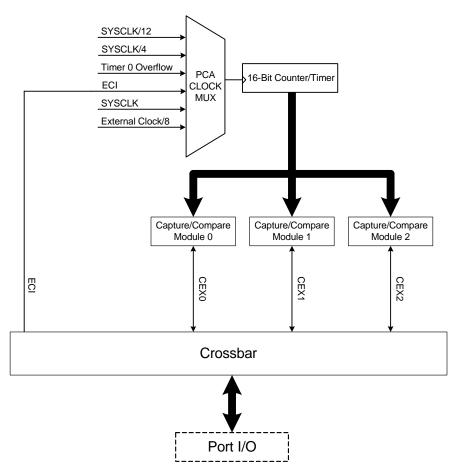

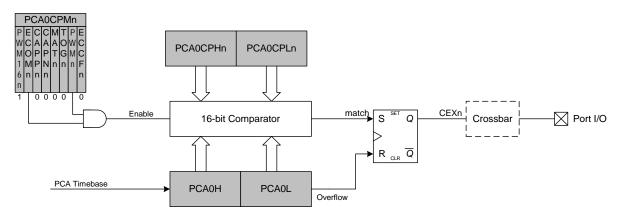

| <ul> <li>This bit sets the masking of the CPO Rising Edge interrupt.</li> <li>0: Disable CPO Rising Edge Interrupt.</li> <li>1: Enable CPO Rising Edge Interrupt.</li> <li>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt</li> <li>This bit sets the masking of the CPO Falling Edge interrupt.</li> <li>0: Disable CPO Falling Edge Interrupt.</li> <li>1: Enable CPO Falling Edge Interrupt.</li> <li>1: Enable CPO Falling Edge Interrupt.</li> <li>Bit2: EPCA0: Enable Programmable Counter Array (PCA0) Interrupt.</li> <li>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable interrupt requests generated by PCA0.</li> <li>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.</li> <li>This bit sets the masking of the ADC0 Conversion Complete interrupt.</li> <li>0: Disable ADC0 Conversion Complete Interrupt.</li> <li>1: Enable interrupt requests generated by the AD0INT flag.</li> <li>Bit0: EWADC0: Enable ADC0 Window Comparison Interrupt.</li> <li>This bit sets the masking of the ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | D:44  |                                                                                                                                                                                    |             | •            | a Edao Into   | *****        |              |              |             |  |  |  |  |  |  |