Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                   |

|----------------------------|-------------------------------------------------------------------|

| Product Status             | Active                                                            |

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | LINbus, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                |

| Number of I/O              | 6                                                                 |

| Program Memory Size        | 8KB (8K x 8)                                                      |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 256 x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.25V                                                        |

| Data Converters            | A/D 6x12b                                                         |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 10-VFDFN Exposed Pad                                              |

| Supplier Device Package    | 10-DFN (3x3)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f520-c-imr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name         | Pin Nur           | nbers     | Туре             | Description                                                                                                                                                                                                                           |

|--------------|-------------------|-----------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | 'F52xA<br>'F52x-C | 'F52x     |                  |                                                                                                                                                                                                                                       |

| P0.3/TX*/    | —                 | 8         | D I/O or<br>A In | Port 0.3. See Port I/O Section for a complete description.                                                                                                                                                                            |

| XTAL2        |                   |           | D I/O            | External Clock Output. For an external crystal or resonator, this pin is the excitation driver. This pin is the external clock input for CMOS, capacitor, or RC oscillator configurations. See Section "14. Oscillators" on page 135. |

| P0.2         | 9                 | 9         | D I/O or         | Port 0.2. See Port I/O Section for a complete description.                                                                                                                                                                            |

| XTAL1        |                   |           | A In             | External Clock Input. This pin is the external oscillator return for a crystal or resonator. Section "14. Oscillators" on page 135.                                                                                                   |

| P0.1/        | 10                | 10        | D I/O or<br>A In | Port 0.1. See Port I/O Section for a complete description.                                                                                                                                                                            |

|              |                   |           |                  |                                                                                                                                                                                                                                       |

| C2D          |                   |           | D I/O            | Bi-directional data signal for the C2 Debug Interface                                                                                                                                                                                 |

| lote: Please | refer to Se       | ection "2 | 0. Device S      | Specific Behavior" on page 210.                                                                                                                                                                                                       |

### Table 3.1. Pin Definitions for the C8051F52x and C8051F52xA (DFN 10) (Continued)

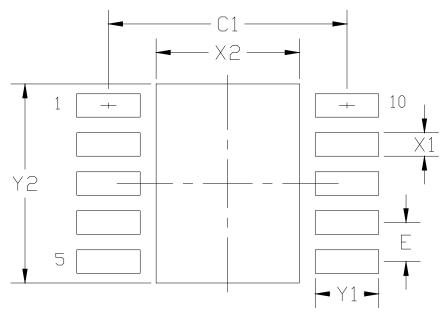

Figure 3.3. DFN-10 Landing Diagram

|                   | Dimension                                                                                                                                                                                                                                                                                                                                                             | Min                           | Max                                          |  |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------|--|--|--|--|--|

|                   | C1                                                                                                                                                                                                                                                                                                                                                                    | 2.90                          | 3.00                                         |  |  |  |  |  |

|                   | E                                                                                                                                                                                                                                                                                                                                                                     | 0.50                          | BSC.                                         |  |  |  |  |  |

|                   | X1                                                                                                                                                                                                                                                                                                                                                                    | 0.20                          | 0.30                                         |  |  |  |  |  |

|                   | X2                                                                                                                                                                                                                                                                                                                                                                    | 1.70                          | 1.80                                         |  |  |  |  |  |

|                   | Y1                                                                                                                                                                                                                                                                                                                                                                    | 0.70                          | 0.80                                         |  |  |  |  |  |

|                   | Y2                                                                                                                                                                                                                                                                                                                                                                    | 2.45                          | 2.55                                         |  |  |  |  |  |

| 2.                | <ol> <li>All dimensions shown are in millimeters (mm) unless otherwise noted.</li> <li>This land pattern design is based on the IPC-7351 guidelines.</li> <li>Solder Mask Design</li> <li>All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 μm minimum, all the way around the pad.</li> </ol> |                               |                                              |  |  |  |  |  |

| 3.<br><u>Sten</u> | All metal pads are to be<br>between the solder ma<br>way around the pad.<br>cil Design                                                                                                                                                                                                                                                                                | be non-solder mask defined (N | NSMD). Clearance<br>ε 60 μm minimum, all the |  |  |  |  |  |

**9.** The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

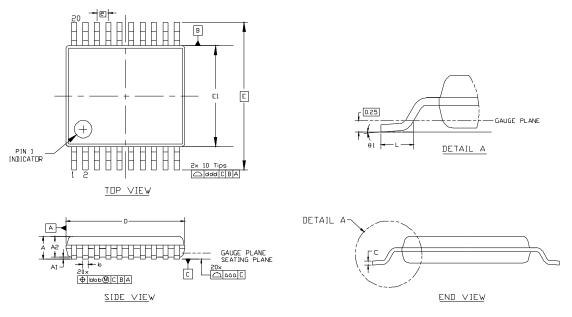

### Figure 3.5. TSSOP-20 Package Diagram

| Symbol | Min       | Nom       | Мах  |  |  |  |  |  |

|--------|-----------|-----------|------|--|--|--|--|--|

| A      |           |           | 1.20 |  |  |  |  |  |

| A1     | 0.05      | 0.05 —    |      |  |  |  |  |  |

| A2     | 0.80      | 1.00      | 1.05 |  |  |  |  |  |

| b      | 0.19      |           | 0.30 |  |  |  |  |  |

| С      | 0.09      | —         | 0.20 |  |  |  |  |  |

| D      | 6.40      | 6.60      |      |  |  |  |  |  |

| е      | 0.65 BSC. |           |      |  |  |  |  |  |

| E      |           | 6.40 BSC. |      |  |  |  |  |  |

| E1     | 4.30      | 4.40      | 4.50 |  |  |  |  |  |

| L      | 0.45      | 0.60      | 0.75 |  |  |  |  |  |

| θ1     | 0°        | —         | 8°   |  |  |  |  |  |

| aaa    |           | 0.10      |      |  |  |  |  |  |

| bbb    |           | 0.10      |      |  |  |  |  |  |

| ddd    | 0.20      |           |      |  |  |  |  |  |

| otes:  |           |           |      |  |  |  |  |  |

### Table 3.5. TSSOP-20 Package Diagram Dimensions

1. All dimensions shown are in millimeters (mm).

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This drawing conforms to JEDEC outline MO-153, variation AC.

**4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

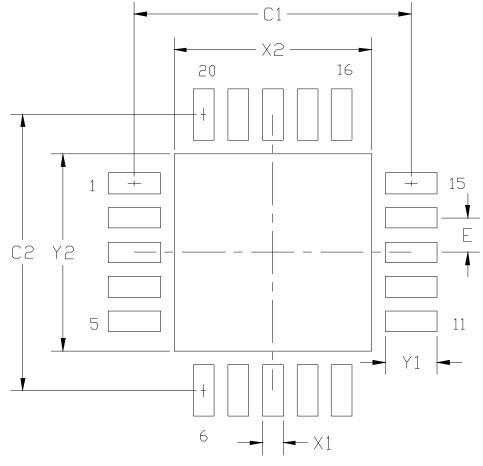

Figure 3.9. QFN-20 Landing Diagram\*

Note: The Landing Dimensions are given in Table 3.9, "QFN-20 Landing Diagram Dimensions," on page 51.

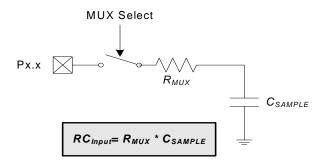

#### 4.3.6. Settling Time Requirements

A minimum tracking time is required before an accurate conversion can be performed. This tracking time is determined by the AMUX0 resistance, the ADC0 sampling capacitance, any external source resistance, and the accuracy required for the conversion.

Figure 4.6 shows the equivalent ADC0 input circuit. The required ADC0 settling time for a given settling accuracy (SA) may be approximated by Equation 4.1. When measuring the Temperature Sensor output, use the settling time specified in Table 2.3 on page 28. See Table 2.3 on page 28 for ADC0 minimum settling time requirements.

$$t = \ln\left(\frac{2^n}{SA}\right) \times R_{TOTAL} C_{SAMPLE}$$

### **Equation 4.1. ADC0 Settling Time Requirements**

Where:

SA is the settling accuracy, given as a fraction of an LSB (for example, 0.25 to settle within 1/4 LSB) *t* is the required settling time in seconds

$R_{TOTAL}$  is the sum of the AMUX0 resistance and any external source resistance.

*n* is the ADC resolution in bits (12).

Figure 4.6. ADC0 Equivalent Input Circuits

### 4.4. Selectable Gain

ADC0 on the C8051F52x/52xA/53x/53xA family of devices implements a selectable gain adjustment option. By writing a value to the gain adjust address range, the user can select gain values between 0 and 1.016.

For example, three analog sources to be measured have full-scale outputs of 5.0 V, 4.0 V, and 3.0 V, respectively. Each ADC measurement would ideally use the full dynamic range of the ADC with an internal voltage reference of 1.5 V or 2.2 V (set to 2.2 V for this example). When selecting signal one (5.0 V full-scale), a gain value of 0.44 (5 V full scale \* 0.44 = 2.2 V full scale) provides a full-scale signal of 2.2 V when the input signal is 5.0 V. Likewise, a gain value of 0.55 (4 V full scale \* 0.55 = 2.2 V full scale) for the second source and 0.73 (3 V full scale \* 0.73 = 2.2 V full scale) for the third source provide full-scale ADCO measurements when the input signal is full-scale.

Additionally, some sensors or other input sources have small part-to-part variations that must be accounted for to achieve accurate results. In this case, the programmable gain value could be used as a calibration value to eliminate these part-to-part variations.

### Gain Register Definition 4.1. ADC0GNH: ADC0 Selectable Gain High Byte

| R/W        | R/W                                         | R/W  | R/W<br>GAIN | R/W<br>H[7:0] | R/W  | R/W  | R/W  | Reset Value      |  |  |  |

|------------|---------------------------------------------|------|-------------|---------------|------|------|------|------------------|--|--|--|

| Bit7       | Bit6                                        | Bit5 | Bit4        | Bit3          | Bit2 | Bit1 | Bit0 | Address:<br>0x04 |  |  |  |

| Bits7–0: I | Bits7–0: High byte of Selectable Gain Word. |      |             |               |      |      |      |                  |  |  |  |

## Gain Register Definition 4.2. ADC0GNL: ADC0 Selectable Gain Low Byte

|    | R/W                                                        | R/W   | R/W   | R/W  | R/W      | R/W      | R/W      | R/W      | Reset Value |  |  |  |

|----|------------------------------------------------------------|-------|-------|------|----------|----------|----------|----------|-------------|--|--|--|

|    |                                                            | GAINL | [3:0] |      | Reserved | Reserved | Reserved | Reserved | 0000000     |  |  |  |

|    | Bit7                                                       | Bit6  | Bit5  | Bit4 | Bit3     | Bit2     | Bit1     | Bit0     | Address:    |  |  |  |

|    |                                                            |       |       |      |          |          |          |          | 0x07        |  |  |  |

| Bi | <b>Bits7–4</b> : Lower 4 bits of the Selectable Gain Word. |       |       |      |          |          |          |          |             |  |  |  |

| Bi | Bits3–0: Reserved. Must Write 0000b.                       |       |       |      |          |          |          |          |             |  |  |  |

|    |                                                            |       |       |      |          |          |          |          |             |  |  |  |

## Gain Register Definition 4.3. ADC0GNA: ADC0 Additional Selectable Gain

| R/W      | R/W      | R/W          | R/W       | R/W           | R/W          | R/W        | R/W        | Reset Value |

|----------|----------|--------------|-----------|---------------|--------------|------------|------------|-------------|

| Reserved | Reserved | Reserved     | Reserved  | Reserved      | Reserved     | Reserved   | GAINADD    | 00000001    |

| Bit7     | Bit6     | Bit5         | Bit4      | Bit3          | Bit2         | Bit1       | Bit0       | Address:    |

|          |          |              |           |               |              |            |            | 0x08        |

| 5        | SAINADD: | Additional ( | Gain Bit. | gain to the g | gain value i | n the ADC( | )GNH and A | ADC0GNL     |

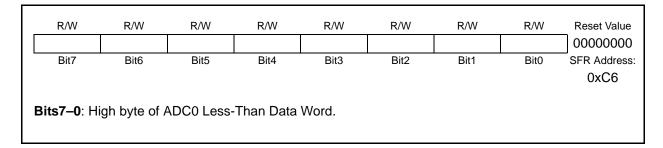

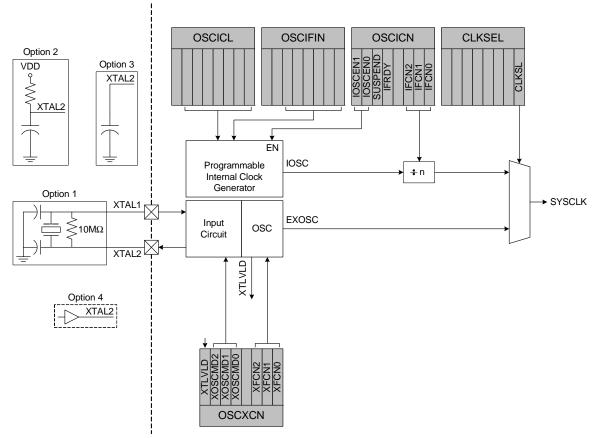

### SFR Definition 4.12. ADC0LTH: ADC0 Less-Than Data High Byte

## SFR Definition 4.13. ADC0LTL: ADC0 Less-Than Data Low Byte

**Important Note About the V<sub>REF</sub> Pin:** Port pin P0.0 is used as the external V<sub>REF</sub> input and as an output for the internal V<sub>REF</sub>. When using either an external voltage reference or the internal reference circuitry, P0.0 should be configured as an analog pin, and skipped by the Digital Crossbar. To configure P0.0 as an analog pin, clear Bit 0 in register P0MDIN to 0. To configure the Crossbar to skip P0.0, set Bit 0 in register P0SKIP to 1. Refer to Section "13. Port Input/Output" on page 120 for complete Port I/O configuration details.

The TEMPE bit in register REF0CN enables/disables the temperature sensor. While disabled, the temperature sensor defaults to a high impedance state and any ADC0 measurements performed on the sensor result in meaningless data.

| R/W          | R/W                                                         | R/W           | R/W           | R/W         | R/W          | R/W           | R/W                | Reset Value |  |  |  |  |

|--------------|-------------------------------------------------------------|---------------|---------------|-------------|--------------|---------------|--------------------|-------------|--|--|--|--|

| Reserve      |                                                             | ZTCEN         | REFLV         | REFSL       | TEMPE        | BIASE         | REFBE              |             |  |  |  |  |

| Bit7         | Bit6                                                        | Bit5          | Bit4          | Bit3        | Bit2         | Bit1          | Bit0               | SFR Address |  |  |  |  |

|              |                                                             |               |               |             |              |               |                    | 0xD1        |  |  |  |  |

|              |                                                             |               |               |             |              |               |                    |             |  |  |  |  |

| Bits7–6:     | RESERVED                                                    | . Read = 00   | )b. Must wr   | ite 00b.    |              |               |                    |             |  |  |  |  |

| Bit5:        | ZTCEN: Zero                                                 | o-TempCol     | Bias Enable   | e Bit*.     |              |               |                    |             |  |  |  |  |

|              | 0: ZeroTC Bias Generator automatically enabled when needed. |               |               |             |              |               |                    |             |  |  |  |  |

|              | 1: ZeroTC Bias Generator forced on.                         |               |               |             |              |               |                    |             |  |  |  |  |

| Bit4:        |                                                             |               |               |             |              |               |                    |             |  |  |  |  |

|              | This bit seled                                              |               | •             |             | internal vol | tage referei  | nce.               |             |  |  |  |  |

|              | 0: Internal vo                                              | •             |               |             |              |               |                    |             |  |  |  |  |

|              | 1: Internal vo                                              | -             |               |             |              |               |                    |             |  |  |  |  |

| Bit3:        | REFSL: Volt                                                 | •             |               |             |              |               |                    |             |  |  |  |  |

|              | This bit selec                                              |               |               |             | ige referenc | ce.           |                    |             |  |  |  |  |

|              | 0: V <sub>REF</sub> pin ι                                   |               | -             | nce.        |              |               |                    |             |  |  |  |  |

|              | 1: V <sub>DD</sub> used                                     |               |               |             |              |               |                    |             |  |  |  |  |

| Bit2:        | TEMPE: Ten                                                  |               |               |             |              |               |                    |             |  |  |  |  |

|              | 0: Internal Te                                              | •             |               |             |              |               |                    |             |  |  |  |  |

| <b>B</b> 144 | 1: Internal Te                                              | •             |               |             | D.'.         |               |                    |             |  |  |  |  |

| Bit1:        | BIASE: Inter                                                | •             |               |             |              | 1 1.          |                    |             |  |  |  |  |

|              | 0: Internal A                                               |               |               |             | y enabled v  | vnen neede    | ed.                |             |  |  |  |  |

| Bit0:        | 1: Internal A<br>REFBE: Inte                                | •             |               |             |              |               |                    |             |  |  |  |  |

| DITU.        | 0: Internal R                                               |               |               |             |              |               |                    |             |  |  |  |  |

|              | 1: Internal R                                               |               |               |             | voltago rofo | ronco drivo   | $n$ on the $V_{-}$ | nin         |  |  |  |  |

|              |                                                             |               |               |             | illaye rele  |               |                    | REF PIII.   |  |  |  |  |

| *Note: Sa    | e Section "20.7                                             | / Internal ∩o | cillator Sucr | end Mode" o | n nage 212 f | or a note rel | ated to the 7      | TCEN hit in |  |  |  |  |

| 14010.00     | older silicon re                                            |               | onator ousp   |             | 11 page 2121 |               |                    |             |  |  |  |  |

|              |                                                             |               |               |             |              |               |                    |             |  |  |  |  |

|              |                                                             |               |               |             |              |               |                    |             |  |  |  |  |

## SFR Definition 5.1. REF0CN: Reference Control

### Table 8.1. CIP-51 Instruction Set Summary (Continued)

| Mnemonic           | Description                                | Bytes | Clock<br>Cycles |

|--------------------|--------------------------------------------|-------|-----------------|

| ORL direct, #data  | OR immediate to direct byte                | 3     | 3               |

| XRL A, Rn          | Exclusive-OR Register to A                 | 1     | 1               |

| XRL A, direct      | Exclusive-OR direct byte to A              | 2     | 2               |

| XRL A, @Ri         | Exclusive-OR indirect RAM to A             | 1     | 2               |

| XRL A, #data       | Exclusive-OR immediate to A                | 2     | 2               |

| XRL direct, A      | Exclusive-OR A to direct byte              | 2     | 2               |

| XRL direct, #data  | Exclusive-OR immediate to direct byte      | 3     | 3               |

| CLR A              | Clear A                                    | 1     | 1               |

| CPL A              | Complement A                               | 1     | 2               |

| RL A               | Rotate A left                              | 1     | 1               |

| RLC A              | Rotate A left through Carry                | 1     | 1               |

| RR A               | Rotate A right                             | 1     | 1               |

| RRC A              | Rotate A right through Carry               | 1     | 1               |

| SWAP A             | Swap nibbles of A                          | 1     | 1               |

| Data Transfer      |                                            |       |                 |

| MOV A, Rn          | Move Register to A                         | 1     | 1               |

| MOV A, direct      | Move direct byte to A                      | 2     | 2               |

| MOV A, @Ri         | Move indirect RAM to A                     | 1     | 2               |

| MOV A, #data       | Move immediate to A                        | 2     | 2               |

| MOV Rn, A          | Move A to Register                         | 1     | 1               |

| MOV Rn, direct     | Move direct byte to Register               | 2     | 2               |

| MOV Rn, #data      | Move immediate to Register                 | 2     | 2               |

| MOV direct, A      | Move A to direct byte                      | 2     | 2               |

| MOV direct, Rn     | Move Register to direct byte               | 2     | 2               |

| MOV direct, direct | Move direct byte to direct byte            | 3     | 3               |

| MOV direct, @Ri    | Move indirect RAM to direct byte           | 2     | 2               |

| MOV direct, #data  | Move immediate to direct byte              | 3     | 3               |

| MOV @Ri, A         | Move A to indirect RAM                     | 1     | 2               |

| MOV @Ri, direct    | Move direct byte to indirect RAM           | 2     | 2               |

| MOV @Ri, #data     | Move immediate to indirect RAM             | 2     | 2               |

| MOV DPTR, #data16  | Load DPTR with 16-bit constant             | 3     | 3               |

| MOVC A, @A+DPTR    | Move code byte relative DPTR to A          | 1     | 3               |

| MOVC A, @A+PC      | Move code byte relative PC to A            | 1     | 3               |

| MOVX A, @Ri        | Move external data (8-bit address) to A    | 1     | 3               |

| MOVX @Ri, A        | Move A to external data (8-bit address)    | 1     | 3               |

| MOVX A, @DPTR      | Move external data (16-bit address) to A   | 1     | 3               |

| MOVX @DPTR, A      | Move A to external data (16-bit address)   | 1     | 3               |

| PUSH direct        | Push direct byte onto stack                | 2     | 2               |

| POP direct         | Pop direct byte from stack                 | 2     | 2               |

| XCH A, Rn          | Exchange Register with A                   | 1     | 1               |

| XCH A, direct      | Exchange direct byte with A                | 2     | 2               |

| XCH A, @Ri         | Exchange indirect RAM with A               | 1     | 2               |

| XCHD A, @Ri        | Exchange low nibble of indirect RAM with A | 1     | 2               |

### 11.2. Power-Fail Reset / V<sub>DD</sub> Monitors (VDDMON0 and VDDMON1)

C8051F52x-C/F53x-C devices include two V<sub>DD</sub> monitors: a standard V<sub>DD</sub> monitor (VDDMON0) and a level-sensitive V<sub>DD</sub> monitor (VDDMON1). VDDMON0 is primarily intended for setting a higher threshold to allow safe erase or write of Flash memory from firmware. VDDMON1 is used to hold the device in a reset state during power-up and brownout conditions.

**Note:** VDDMON1 is not present in older silicon revisions A and B. Please refer to Section "20.4. VDD Monitors and VDD Ramp Time" on page 211 for more details.

When a power-down transition or power irregularity causes  $V_{DD}$  to drop below  $V_{RST}$ , the power supply monitors (VDDMON0 and VDDMON1) will drive the RST pin low and hold the CIP-51 in a reset state (see Figure 11.2). When  $V_{DD}$  returns to a level above  $V_{RST}$ , the CIP-51 will be released from the reset state. Note that even though internal data memory contents are not altered by the power-fail reset, it is impossible to determine if  $V_{DD}$  dropped below the level required for data retention. If the PORSF flag reads 1, the data may no longer be valid.

VDDMON0 is enabled and is selected as a reset source after power-on resets; however its defined state (enabled/disabled) is not altered by any other reset source. For example, if VDDMON0 is disabled by software, and a software reset is performed, VDDMON0 will still be disabled after that reset.

VDDMON1 is enabled and is selected as a reset source after power-on reset and any other type of reset. There is no register setting that can disable this level-sensitive VDD monitor as a reset source.

To protect the integrity of Flash contents, the  $V_{DD}$  monitor (VDDMON0) must be enabled to the higher setting (VDMLVL = '1') and selected as a reset source if software contains routines which erase or write Flash memory. If the  $V_{DD}$  monitor is not enabled and set to the higher setting, any erase or write performed on Flash memory will cause a Flash Error device reset.

**Note:** Please refer to Section "20.5. VDD Monitor (VDDMON0) High Threshold Setting" on page 212 for important notes related to the VDD Monitor high threshold setting in older silicon revisions A and B.

The V<sub>DD</sub> monitor (VDDMON0) must be enabled before it is selected as a reset source. Selecting the VDDMON0 as a reset source before it is enabled and stabilized may cause a system reset. The procedure for re-enabling the  $V_{DD}$  monitor and configuring the  $V_{DD}$  monitor as a reset source is shown below:

- 1. Enable the  $V_{DD}$  monitor (VDMEN bit in VDDMON = 1).

- Wait for the V<sub>DD</sub> monitor to stabilize (see Table 2.8 on page 32 for the V<sub>DD</sub> Monitor turn-on time). Note: This delay should be omitted if software contains routines which write or erase Flash memory.

- 3. Select the  $V_{DD}$  monitor as a reset source (PORSF bit in RSTSRC = 1).

See Figure 11.2 for  $V_{DD}$  monitor timing; note that the reset delay is not incurred after a  $V_{DD}$  monitor reset. See Table 2.8 on page 32 for complete electrical characteristics of the  $V_{DD}$  monitor.

**Note:** Software should take care not to inadvertently disable the V<sub>DD</sub> Monitor (VDDMON0) as a reset source when writing to RSTSRC to enable other reset sources or to trigger a software reset. All writes to RSTSRC should explicitly set PORSF to '1' to keep the V<sub>DD</sub> Monitor enabled as a reset source.

#### 11.2.1. VDD Monitor Thresholds and Minimum VDD

The minimum operating digital supply voltage ( $V_{DD}$ ) is specified as 2.0 V in Table 2.2 on page 26. The voltage at which the MCU is released from reset ( $V_{RST}$ ) can be as low as 1.65 V based on the  $V_{DD}$  Monitor thresholds that are specified in Table 2.8 on page 32. This could allow code execution during the power-up

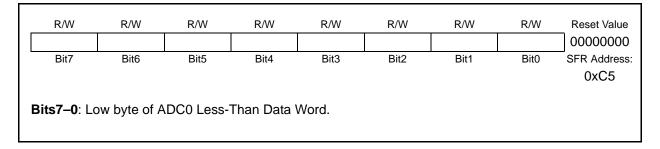

Figure 13.2. Port I/O Cell Block Diagram

**Important Note:** The SPI can be operated in either 3-wire or 4-wire modes, depending on the state of the NSSMD1–NSSMD0 bits in register SPI0CN. According to the SPI mode, the NSS signal may or may not be routed to a Port pin.

### 13.2. Port I/O Initialization

Port I/O initialization consists of the following steps:

- 1. Select the input mode (analog or digital) for all Port pins, using the Port Input Mode register (PnMDIN).

- 2. Select the output mode (open-drain or push-pull) for all Port pins, using the Port Output Mode register (PnMDOUT).

- 3. Select any pins to be skipped by the I/O Crossbar using the Port Skip registers (PnSKIP).

- 4. Assign Port pins to desired peripherals using the XBRn registers.

- 5. Enable the Crossbar (XBARE = 1).

All Port pins must be configured as either analog or digital inputs. Any pins to be used as Comparator or ADC inputs should be configured as an analog inputs. When a pin is configured as an analog input, its weak pullup, digital driver, and digital receiver are disabled. This process saves power and reduces noise on the analog input. Pins configured as digital inputs may still be used by analog peripherals; however, this practice is not recommended.

Additionally, all analog input pins should be configured to be skipped by the Crossbar (accomplished by setting the associated bits in PnSKIP). Port input mode is set in the PnMDIN register, where a 1 indicates a digital input, and a 0 indicates an analog input. All pins default to digital inputs on reset. See SFR Definition 13.4 for the PnMDIN register details.

Important Note: Port 0 and Port 1 pins are 5.25 V tolerant across the operating range of V<sub>REGIN</sub>.

The output driver characteristics of the I/O pins are defined using the Port Output Mode registers (PnMD-OUT). Each Port Output driver can be configured as either open drain or push-pull. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. When the WEAKPUD bit in XBR1 is 0, a weak pullup is enabled for all Port I/O configured as open-drain. WEAKPUD does not affect the push-pull Port I/O. Furthermore, the weak pullup is turned off on an output that is driving a 0 and for pins configured for analog input mode to avoid unnecessary power dissipation.

Registers XBR0 and XBR1 must be loaded with the appropriate values to select the digital I/O functions required by the design. Setting the XBARE bit in XBR1 to 1 enables the Crossbar. Until the Crossbar is enabled, the external pins remain as standard Port I/O (in input mode), regardless of the XBRn Register settings. For given XBRn Register settings, one can determine the I/O pin-out using the Priority Decode Table.

The Crossbar must be enabled to use Port pins as standard Port I/O in output mode. **Port output drivers** are disabled while the Crossbar is disabled.

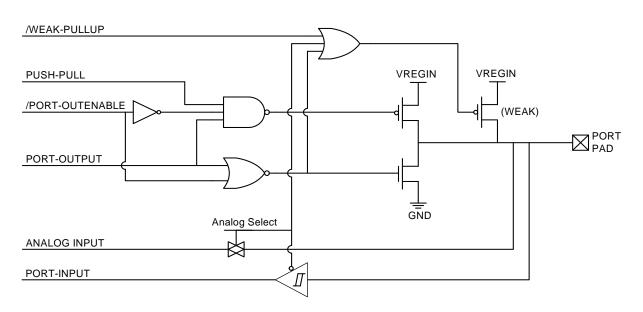

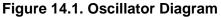

## 14. Oscillators

C8051F52x/F52xA/F53x/F53xA devices include a programmable internal oscillator, an external oscillator drive circuit. The internal oscillator can be enabled/disabled and calibrated using the OSCICN and OSCICL registers, as shown in Figure 14.1. The system clock (SYSCLK) can be derived from the internal oscillator, external oscillator circuit. Oscillator electrical specifications are given in Table 2.11 on page 34.

### 14.1. Programmable Internal Oscillator

All C8051F52x/53x devices include a programmable internal oscillator that defaults as the system clock after a system reset. The internal oscillator period can be programmed via the OSCICL and OSCIFIN registers, shown in SFR Definition 14.2 and SFR Definition 14.3. On C8051F52x/53x devices, OSCICL and OSCIFIN are factory calibrated to obtain a 24.5 MHz frequency.

Electrical specifications for the precision internal oscillator are given in Table 2.11 on page 34. Note that the system clock may be derived from the programmed internal oscillator divided by 1, 2, 4, 8, 16, 32, 64, or 128 as defined by the IFCN bits in register OSCICN. The divide value defaults to 128 following a reset.

### 14.1.1. Internal Oscillator Suspend Mode

When software writes a logic 1 to SUSPEND (OSCICN.5), the internal oscillator is suspended. If the system clock is derived from the internal oscillator, the input clock to the peripheral or CIP-51 will be stopped until one of the following events occur:

- Port 0 Match Event.

- Port 1 Match Event.

- Comparator 0 enabled and output is logic 0.

When one of the internal oscillator awakening events occur, the internal oscillator, CIP-51, and affected peripherals resume normal operation, regardless of whether the event also causes an interrupt. The CPU resumes execution at the instruction following the write to SUSPEND.

**Note:** Please refer to Section "20.7. Internal Oscillator Suspend Mode" on page 212 for a note about suspend mode in older silicon revisions.

### 14.2.3. External RC Example

If an RC network is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 14.1, Option 2. The capacitor should be no greater than 100 pF; however for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, first select the RC network value to produce the desired frequency of oscillation. If the frequency desired is 100 kHz, let R = 246 k $\Omega$  and C = 50 pF:

$f = 1.23(10^3) / RC = 1.23(10^3) / [246 \times 50] = 0.1 MHz = 100 kHz$

Referring to the table in SFR Definition 14.4, the required XFCN setting is 010b. Programming XFCN to a higher setting in RC mode will improve frequency accuracy at a slightly increased external oscillator supply current.

#### 14.2.4. External Capacitor Example

If a capacitor is used as an external oscillator for the MCU, the circuit should be configured as shown in Figure 14.1, Option 3. The capacitor should be no greater than 100 pF; however for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, select the frequency of oscillation and calculate the capacitance to be used from the equations below. Assume  $V_{DD} = 2.1 \text{ V}$  and f = 75 kHz:

$f = KF / (C \times V_{DD})$

0.075 MHz = KF / (C x 2.1)

Since the frequency of roughly 75 kHz is desired, select the K Factor from the table in SFR Definition 14.4 as KF = 7.7:

0.075 MHz = 7.7 / (C x 2.1)

C x 2.1 = 7.7 / 0.075 MHz

C = 102.6 / 2.0 pF = 51.3 pF

Therefore, the XFCN value to use in this example is 010b.

### 16.1. Signal Descriptions

The four signals used by SPI0 (MOSI, MISO, SCK, NSS) are described below.

### 16.1.1. Master Out, Slave In (MOSI)

The master-out, slave-in (MOSI) signal is an output from a master device and an input to slave devices. It is used to serially transfer data from the master to the slave. This signal is an output when SPI0 is operating as a master and an input when SPI0 is operating as a slave. Data is transferred most-significant bit first. When configured as a master, MOSI is driven by the MSB of the shift register in both 3- and 4-wire mode.

#### 16.1.2. Master In, Slave Out (MISO)

The master-in, slave-out (MISO) signal is an output from a slave device and an input to the master device. It is used to serially transfer data from the slave to the master. This signal is an input when SPI0 is operating as a master and an output when SPI0 is operating as a slave. Data is transferred most-significant bit first. The MISO pin is placed in a high-impedance state when the SPI module is disabled and when the SPI operates in 4-wire mode as a slave that is not selected. When acting as a slave in 3-wire mode, MISO is always driven by the MSB of the shift register.

#### 16.1.3. Serial Clock (SCK)

The serial clock (SCK) signal is an output from the master device and an input to slave devices. It is used to synchronize the transfer of data between the master and slave on the MOSI and MISO lines. SPI0 generates this signal when operating as a master. The SCK signal is ignored by a SPI slave when the slave is not selected (NSS = 1) in 4-wire slave mode.

#### 16.1.4. Slave Select (NSS)

The function of the slave-select (NSS) signal is dependent on the setting of the NSSMD1 and NSSMD0 bits in the SPI0CN register. There are three possible modes that can be selected with these bits:

- 1. NSSMD[1:0] = 00: 3-Wire Master or 3-Wire Slave Mode: SPI0 operates in 3-wire mode, and NSS is disabled. When operating as a slave device, SPI0 is always selected in 3-wire mode. Since no select signal is present, SPI0 must be the only slave on the bus in 3-wire mode. This is intended for point-to-point communication between a master and one slave.

- NSSMD[1:0] = 01: 4-Wire Slave or Multi-Master Mode: SPI0 operates in 4-wire mode, and NSS is enabled as an input. When operating as a slave, NSS selects the SPI0 device. When operating as a master, a 1-to-0 transition of the NSS signal disables the master function of SPI0 so that multiple master devices can be used on the same SPI bus.

- 3. NSSMD[1:0] = 1x: 4-Wire Master Mode: SPI0 operates in 4-wire mode, and NSS is enabled as an output. The setting of NSSMD0 determines what logic level the NSS pin will output. This configuration should only be used when operating SPI0 as a master device.

See Figure 16.2, Figure 16.3, and Figure 16.4 for typical connection diagrams of the various operational modes. **Note that the setting of NSSMD bits affects the pinout of the device.** When in 3-wire master or 3-wire slave mode, the NSS pin will not be mapped by the crossbar. In all other modes, the NSS signal will be mapped to a pin on the device. See Section "13. Port Input/Output" on page 120 for general purpose port I/O and crossbar information.

The following code programs the interface in Master mode, using the Enhanced Checksum and enables the interface to operate at 19200 bits/sec using a 24 MHz system clock.

```

LINOCF = 0x80;// Activate the interface

LINOCF |= 0x40;// Set the node as a Master

LINADDR = 0x0D;// Point to the LINOMUL register

// Initialize the register (prescaler, multiplier and bit 8 of divider)

LINDATA = ( 0x01 << 6 ) + ( 0x00 << 1 ) + ( ( 0x13F & 0x0100 ) >> 8 );

LINADDR = 0x0C;// Point to the LINODIV register

LINDATA = (unsigned char)_0x13F;// Initialize LINODIV

LINADDR = 0x0B;// Point to the LINOSIZE register

LINDATA |= 0x80;// Initialize the checksum as Enhanced

LINADDR = 0x08;// Point to LINOCTRL register

LINDATA = 0x0C;// Reset any error and the interrupt

```

Table 17.2 includes the configuration values required for the typical system clocks and baud rates:

|                 |       | Baud (bits / sec) |      |       |              |      |       |       |      |       |       |      |       |       |      |

|-----------------|-------|-------------------|------|-------|--------------|------|-------|-------|------|-------|-------|------|-------|-------|------|

|                 |       | 20 K              |      |       | 19.2 K 9.6 K |      |       | 4.8 K |      |       | 1 K   |      |       |       |      |

| SYSCLK<br>(MHz) | Mult. | Pres.             | Div. | Mult. | Pres.        | Div. | Mult. | Pres. | Div. | Mult. | Pres. | Div. | Mult. | Pres. | Div. |

| 25              | 0     | 1                 | 312  | 0     | 1            | 325  | 1     | 1     | 325  | 3     | 1     | 325  | 19    | 1     | 312  |

| 24.5            | 0     | 1                 | 306  | 0     | 1            | 319  | 1     | 1     | 319  | 3     | 1     | 319  | 19    | 1     | 306  |

| 24              | 0     | 1                 | 300  | 0     | 1            | 312  | 1     | 1     | 312  | 3     | 1     | 312  | 19    | 1     | 300  |

| 22.1184         | 0     | 1                 | 276  | 0     | 1            | 288  | 1     | 1     | 288  | 3     | 1     | 288  | 19    | 1     | 276  |

| 16              | 0     | 1                 | 200  | 0     | 1            | 208  | 1     | 1     | 208  | 3     | 1     | 208  | 19    | 1     | 200  |

| 12.25           | 0     | 0                 | 306  | 0     | 0            | 319  | 1     | 0     | 319  | 3     | 0     | 319  | 19    | 0     | 306  |

| 12              | 0     | 0                 | 300  | 0     | 0            | 312  | 1     | 0     | 312  | 3     | 0     | 312  | 19    | 0     | 300  |

| 11.0592         | 0     | 0                 | 276  | 0     | 0            | 288  | 1     | 0     | 288  | 3     | 0     | 288  | 19    | 0     | 276  |

| 8               | 0     | 0                 | 200  | 0     | 0            | 208  | 1     | 0     | 208  | 3     | 0     | 208  | 19    | 0     | 200  |

Table 17.2. Manual Baud Rate Parameters Examples

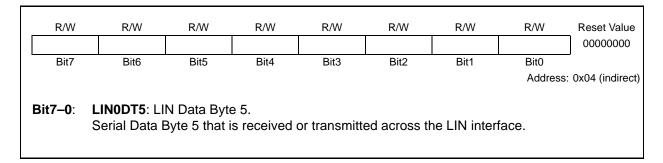

### SFR Definition 17.8. LIN0DT5: LIN0 Data Byte 5

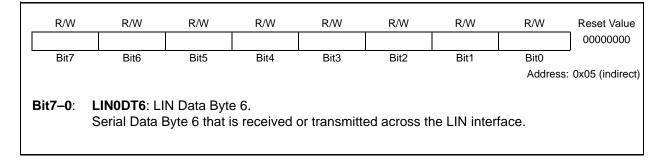

### SFR Definition 17.9. LIN0DT6: LIN0 Data Byte 6

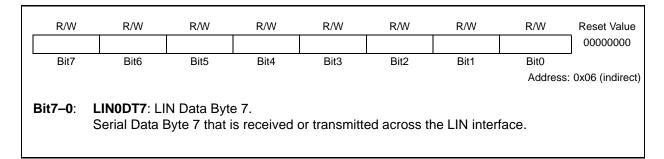

### SFR Definition 17.10. LIN0DT7: LIN0 Data Byte 7

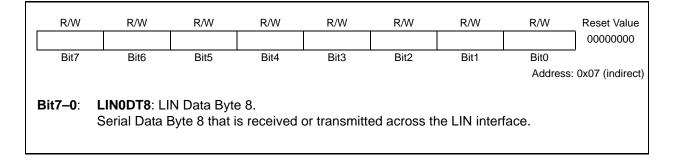

### SFR Definition 17.11. LIN0DT8: LIN0 Data Byte 8

| SFR Defi | nition 18.8                                                                                                                                                                    | . TMR2C      | N: Timer    | 2 Contro      |                |              |                |                       |  |  |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------|---------------|----------------|--------------|----------------|-----------------------|--|--|--|--|--|

| R/W      | R/W                                                                                                                                                                            | R/W          | R/W         | R/W           | R/W            | R/W          | R/W            | Reset Value           |  |  |  |  |  |

| TF2H     | TF2L                                                                                                                                                                           | TF2LEN       | TF2CEN      | T2SPLIT       | TR2            | _            | T2XCLK         | 00000000              |  |  |  |  |  |

| Bit7     | Bit6                                                                                                                                                                           | Bit5         | Bit4        | Bit3          | Bit2           | Bit1         | Bit0           | Bit                   |  |  |  |  |  |

|          |                                                                                                                                                                                |              |             |               |                |              | SFR Address    | Addressable<br>: 0xC8 |  |  |  |  |  |

|          |                                                                                                                                                                                |              |             |               |                |              | SI IT Address  | . 0700                |  |  |  |  |  |

| Bit7:    | TF2H: Timer                                                                                                                                                                    | r 2 High Byt | e Overflow  | Flag.         |                |              |                |                       |  |  |  |  |  |

|          | Set by hardw                                                                                                                                                                   |              |             |               |                |              |                |                       |  |  |  |  |  |

|          | this will occur when Timer 2 overflows from 0xFFFF to 0x0000. When the Timer 2 interrupt is                                                                                    |              |             |               |                |              |                |                       |  |  |  |  |  |

|          | enabled, setting this bit causes the CPU to vector to the Timer 2 interrupt service routine.<br>TF2H is not automatically cleared by hardware and must be cleared by software. |              |             |               |                |              |                |                       |  |  |  |  |  |

| Bit6:    | <b>TF2L</b> : Timer 2 Low Byte Overflow Flag.                                                                                                                                  |              |             |               |                |              |                |                       |  |  |  |  |  |

|          | Set by hardv                                                                                                                                                                   |              |             |               |                |              |                |                       |  |  |  |  |  |

|          | set, an interr                                                                                                                                                                 |              |             |               |                |              | •              |                       |  |  |  |  |  |

|          | will set wher<br>ically cleared                                                                                                                                                |              |             | s regardless  | of the Time    | er 2 mode.   | i nis dit is n | iot automat-          |  |  |  |  |  |

| Bit5:    | TF2LEN: Tir                                                                                                                                                                    |              |             | ot Enable.    |                |              |                |                       |  |  |  |  |  |

|          | This bit enab                                                                                                                                                                  |              | •           |               | errupts. If Th | F2LEN is s   | set and Time   | er 2 inter-           |  |  |  |  |  |

|          | rupts are en                                                                                                                                                                   |              |             |               |                |              | of Timer 2 ov  | verflows.             |  |  |  |  |  |

|          | This bit shou<br>0: Timer 2 Lo                                                                                                                                                 |              |             | •             | er 2 in 16-bi  | it mode.     |                |                       |  |  |  |  |  |

|          | 1: Timer 2 Lo                                                                                                                                                                  | •            |             |               |                |              |                |                       |  |  |  |  |  |

| Bit4:    | TF2CEN. Tir                                                                                                                                                                    | •            | •           | Jiou.         |                |              |                |                       |  |  |  |  |  |

|          | 0: Timer 2 ca                                                                                                                                                                  | •            |             |               |                |              |                |                       |  |  |  |  |  |

| D:40.    | 1: Timer 2 ca                                                                                                                                                                  | •            |             | 1.            |                |              |                |                       |  |  |  |  |  |

| Bit3:    | T2SPLIT: Tir<br>When this bi                                                                                                                                                   | •            |             |               | hit timers w   | /ith auto-re | aload          |                       |  |  |  |  |  |

|          | 0: Timer 2 of                                                                                                                                                                  |              | •           |               |                |              | 1000.          |                       |  |  |  |  |  |

|          | 1: Timer 2 of                                                                                                                                                                  | perates as t | wo 8-bit au |               |                |              |                |                       |  |  |  |  |  |

| Bit2:    | TR2: Timer 2                                                                                                                                                                   |              |             |               |                |              |                |                       |  |  |  |  |  |

|          | This bit enab                                                                                                                                                                  |              |             |               | e, this bit er | ables/disa   | ables IMR2     | H only;               |  |  |  |  |  |

|          | TMR2L is al<br>0: Timer 2 di                                                                                                                                                   | •            |             | oue.          |                |              |                |                       |  |  |  |  |  |

|          | 1: Timer 2 ei                                                                                                                                                                  |              |             |               |                |              |                |                       |  |  |  |  |  |

| Bit1:    | Unused. Re                                                                                                                                                                     |              |             |               |                |              |                |                       |  |  |  |  |  |

| Bit0:    | T2XCLK: Tir                                                                                                                                                                    |              |             |               | mar O. If Tin  | oor 2 io in  | 0 hit mada     | thia hit              |  |  |  |  |  |

|          | This bit selects the e                                                                                                                                                         |              |             |               |                |              |                |                       |  |  |  |  |  |

|          | Select bits (                                                                                                                                                                  |              |             |               |                | •            |                |                       |  |  |  |  |  |

|          | external cloc                                                                                                                                                                  |              | •           |               |                |              |                |                       |  |  |  |  |  |

|          | 0: Timer 2 ex                                                                                                                                                                  |              |             |               |                |              |                |                       |  |  |  |  |  |

|          | 1: Timer 2 ex                                                                                                                                                                  | xternal cloc | K SEIECTION | is the extern | Iai Ciock div  | ided by 8.   |                |                       |  |  |  |  |  |

|          |                                                                                                                                                                                |              |             |               |                |              |                |                       |  |  |  |  |  |

|          |                                                                                                                                                                                |              |             |               |                |              |                |                       |  |  |  |  |  |

|          |                                                                                                                                                                                |              |             |               |                |              |                |                       |  |  |  |  |  |

|          |                                                                                                                                                                                |              |             |               |                |              |                |                       |  |  |  |  |  |

|          |                                                                                                                                                                                |              |             |               |                |              |                |                       |  |  |  |  |  |

### **19.2. Capture/Compare Modules**

Each module can be configured to operate independently in one of six operation modes: Edge-triggered Capture, Software Timer, High Speed Output, Frequency Output, 8-Bit Pulse Width Modulator, or 16-Bit Pulse Width Modulator. Each module has Special Function Registers (SFRs) associated with it in the CIP-51 system controller. These registers are used to exchange data with a module and configure the module's mode of operation.

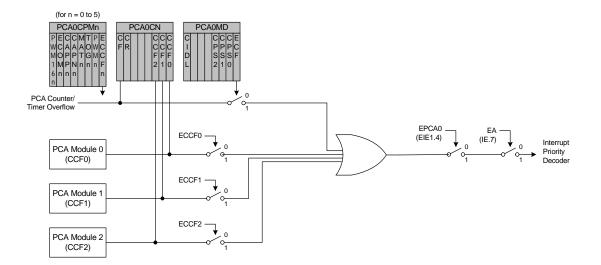

Table 19.2 summarizes the bit settings in the PCA0CPMn registers used to select the PCA capture/compare module's operating modes. Setting the ECCFn bit in a PCA0CPMn register enables the module's CCFn interrupt. Note that PCA0 interrupts must be globally enabled before individual CCFn interrupts are recognized. PCA0 interrupts are globally enabled by setting the EA bit and the EPCA0 bit to logic 1. See Figure 19.3 for details on the PCA interrupt configuration.

| PWM16    | ECOM   | CAPP | CAPN | MAT | TOG | PWM | ECCF | Operation Mode                             |  |  |

|----------|--------|------|------|-----|-----|-----|------|--------------------------------------------|--|--|

| Х        | Х      | 1    | 0    | 0   | 0   | 0   | Х    | Capture triggered by positive edge on CEXn |  |  |

| Х        | Х      | 0    | 1    | 0   | 0   | 0   | Х    | Capture triggered by negative edge on CEXn |  |  |

| Х        | Х      | 1    | 1    | 0   | 0   | 0   | Х    | Capture triggered by transition on CEXn    |  |  |

| Х        | 1      | 0    | 0    | 1   | 0   | 0   | Х    | Software Timer                             |  |  |

| Х        | 1      | 0    | 0    | 1   | 1   | 0   | Х    | High Speed Output                          |  |  |

| Х        | 1      | 0    | 0    | Х   | 1   | 1   | Х    | Frequency Output                           |  |  |

| 0        | 1      | 0    | 0    | Х   | 0   | 1   | Х    | 8-Bit Pulse Width Modulator                |  |  |

| 1        | 1      | 0    | 0    | Х   | 0   | 1   | Х    | 16-Bit Pulse Width Modulator               |  |  |

| X = Don' | t Care | •    |      |     |     | •   | •    |                                            |  |  |

Table 19.2. PCA0CPM Register Settings for PCA Capture/Compare Modules

Figure 19.3. PCA Interrupt Block Diagram