Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                 |

|----------------------------|-----------------------------------------------------------------|

| Product Status             | Active                                                          |

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | LINbus, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT              |

| Number of I/O              | 6                                                               |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 256 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                    |

| Data Converters            | A/D 6x12b                                                       |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                              |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 10-VFDFN Exposed Pad                                            |

| Supplier Device Package    | 10-DFN (3x3)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f520a-im |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## List of Registers

| SFR | Definition | 4.4. ADC0MX: ADC0 Channel Select                | 64 |

|-----|------------|-------------------------------------------------|----|

| SFR | Definition | 4.5. ADC0CF: ADC0 Configuration                 | 65 |

| SFR | Definition | 4.6. ADC0H: ADC0 Data Word MSB                  | 66 |

| SFR | Definition | 4.7. ADC0L: ADC0 Data Word LSB                  | 66 |

| SFR | Definition | 4.8. ADC0CN: ADC0 Control                       | 67 |

| SFR | Definition | 4.9. ADC0TK: ADC0 Tracking Mode Select          | 68 |

|     |            | 4.10. ADC0GTH: ADC0 Greater-Than Data High Byte |    |

| SFR | Definition | 4.11. ADC0GTL: ADC0 Greater-Than Data Low Byte  | 69 |

|     |            | 4.12. ADC0LTH: ADC0 Less-Than Data High Byte    |    |

| SFR | Definition | 4.13. ADC0LTL: ADC0 Less-Than Data Low Byte     | 70 |

| SFR | Definition | 5.1. REF0CN: Reference Control                  | 73 |

| SFR | Definition | 6.1. REG0CN: Regulator Control                  | 75 |

| SFR | Definition | 7.1. CPT0CN: Comparator0 Control                | 78 |

| SFR | Definition | 7.2. CPT0MX: Comparator0 MUX Selection          | 79 |

|     |            | 7.3. CPT0MD: Comparator0 Mode Selection         |    |

| SFR | Definition | 8.1. SP: Stack Pointer                          | 87 |

| SFR | Definition | 8.2. DPL: Data Pointer Low Byte                 | 87 |

| SFR | Definition | 8.3. DPH: Data Pointer High Byte                | 87 |

| SFR | Definition | 8.4. PSW: Program Status Word                   | 88 |

| SFR | Definition | 8.5. ACC: Accumulator                           | 89 |

|     |            | 8.6. B: B Register                              |    |

| SFR | Definition | 8.7. PCON: Power Control                        | 91 |

| SFR | Definition | 10.1. IE: Interrupt Enable 1                    | 00 |

|     |            | 10.2. IP: Interrupt Priority 1                  |    |

|     |            | 10.3. EIE1: Extended Interrupt Enable 1 1       |    |

| SFR | Definition | 10.4. EIP1: Extended Interrupt Priority 1 1     | 03 |

| SFR | Definition | 10.5. IT01CF: INT0/INT1 Configuration 1         | 05 |

|     |            | 11.1. VDDMON: VDD Monitor Control 1             |    |

|     |            | 11.2. RSTSRC: Reset Source 1                    |    |

|     |            | 12.1. PSCTL: Program Store R/W Control 1        |    |

|     |            | 12.2. FLKEY: Flash Lock and Key 1               |    |

|     |            | 13.1. XBR0: Port I/O Crossbar Register 0 1      |    |

|     |            | 13.2. XBR1: Port I/O Crossbar Register 1 1      |    |

|     |            | 13.3. P0: Port0 1                               |    |

|     |            | 13.4. POMDIN: Port0 Input Mode 1                |    |

|     |            | 13.5. P0MDOUT: Port0 Output Mode 1              |    |

|     |            | 13.6. P0SKIP: Port0 Skip 1                      |    |

|     |            | 13.7. POMAT: Port0 Match 1                      |    |

|     |            | 13.8. P0MASK: Port0 Mask 1                      |    |

|     |            | 13.9. P1: Port1 1                               |    |

| SFR | Definition | 13.10. P1MDIN: Port1 Input Mode 1               | 32 |

|     |            | 13.11. P1MDOUT: Port1 Output Mode 1             |    |

| SFR | Definition | 13.12. P1SKIP: Port1 Skip 1                     | 33 |

#### **Table 2.4. Temperature Sensor Electrical Characteristics**

$V_{DD}$  = 2.1 V,  $V_{REF}$  = 1.5 V (REFSL=0), -40 to +125 °C unless otherwise specified.

| Parameter                           | Conditions  | Min | Тур  | Max | Units |  |  |  |  |

|-------------------------------------|-------------|-----|------|-----|-------|--|--|--|--|

| Linearity <sup>1</sup>              |             | —   | 0.1  |     | °C    |  |  |  |  |

| Gain <sup>1</sup>                   |             | —   | 3.33 | —   | mV/°C |  |  |  |  |

| Gain Error <sup>2</sup>             |             | _   | ±100 | —   | µV/°C |  |  |  |  |

| Offset <sup>1</sup>                 | Temp = 0 °C | —   | 890  | —   | mV    |  |  |  |  |

| Offset Error <sup>2</sup>           | Temp = 0 °C | —   | ±15  | —   | mV    |  |  |  |  |

| Tracking Time                       |             | 12  |      |     | μs    |  |  |  |  |

| Power Supply Current                |             | —   | 17   |     | μA    |  |  |  |  |

| Notes:<br>1. Includes ADC offset. g | Notes:      |     |      |     |       |  |  |  |  |

Includes ADC offset, gain, and linearity variations.

Performance and standard deviation from the mean

2. Represents one standard deviation from the mean.

#### Table 2.5. Voltage Reference Electrical Characteristics

$V_{DD} = 2.1 \text{ V}; -40 \text{ to } +125 \text{ °C}$  unless otherwise specified.

| Parameter                                | Parameter Conditions                                                            |              |            |                 | Units  |  |  |  |  |

|------------------------------------------|---------------------------------------------------------------------------------|--------------|------------|-----------------|--------|--|--|--|--|

| Internal Reference (REFBE = 1)           |                                                                                 |              |            |                 |        |  |  |  |  |

| Output Voltage                           | $I_{DD} \approx$ 1 mA; No load on VREF pin and all other GPIO pins.             |              |            |                 |        |  |  |  |  |

|                                          | 25 °C ambient (REFLV = 0)<br>25 °C ambient (REFLV = 1), V <sub>DD</sub> = 2.6 V | 1.45<br>2.15 | 1.5<br>2.2 | 1.55<br>2.25    | V      |  |  |  |  |

| V <sub>REF</sub> Short-Circuit Current   |                                                                                 |              | 2.5        |                 | mA     |  |  |  |  |

| V <sub>REF</sub> Temperature Coefficient |                                                                                 |              | 33         |                 | ppm/°C |  |  |  |  |

| Load Regulation                          | Load = 0 to 200 µA to GND                                                       | —            | 10         | —               | ppm/µA |  |  |  |  |

| V <sub>REF</sub> Turn-on Time 1          | 4.7 μF, 0.1 μF bypass                                                           | —            | 21         |                 | ms     |  |  |  |  |

| V <sub>REF</sub> Turn-on Time 2          | 0.1 μF bypass                                                                   |              | 230        |                 | μs     |  |  |  |  |

| Power Supply Rejection                   |                                                                                 | —            | 2.1        | —               | mV/V   |  |  |  |  |

| External Reference (REFBE =              | = 0)                                                                            |              |            |                 |        |  |  |  |  |

| Input Voltage Range                      |                                                                                 | 0            | —          | V <sub>DD</sub> | V      |  |  |  |  |

| Input Current                            | Sample Rate = 200 ksps; V <sub>REF</sub> = 1.5 V                                |              | 2.4        |                 | μA     |  |  |  |  |

| Bias Generators                          |                                                                                 |              | -          |                 |        |  |  |  |  |

| ADC Bias Generator                       | BIASE = 1                                                                       |              | 22         |                 | μA     |  |  |  |  |

| Power Consumption (Internal)             |                                                                                 | —            | 35         | —               | μA     |  |  |  |  |

#### Table 2.11. Internal Oscillator Electrical Characteristics

$V_{DD}$  = 1.8 to 2.75 V, -40 to +125 °C unless otherwise specified; Using factory-calibrated settings.

| Parameter                            | Conditions                                                                                   | Min         | Тур               | Max         | Units                 |

|--------------------------------------|----------------------------------------------------------------------------------------------|-------------|-------------------|-------------|-----------------------|

| Oscillator Frequency <sup>1</sup>    | $\begin{array}{l} \text{IFCN} = 111\text{b} \\ \text{VDD} \geq \text{VREGMIN}^2 \end{array}$ | 24.5 – 0.5% | 24.5 <sup>3</sup> | 24.5 + 0.5% | MHz                   |

|                                      | IFCN = 111b<br>VDD < VREGMIN <sup>2</sup>                                                    | 24.5 – 1.0% | 24.5 <sup>3</sup> | 24.5 + 1.0% |                       |

|                                      | Oscillator On<br>OSCICN[7:6] = 11b                                                           | —           | 800               | 1100        | μA                    |

|                                      | Oscillator Suspend<br>OSCICN[7:6] = 00b<br>ZTCEN = 1                                         |             |                   |             |                       |

|                                      | T = 25 °C                                                                                    | _           | 67                | _           | μA                    |

| Oscillator Supply Current            | T = 85 °C                                                                                    | _           | 77                | —           | μA                    |

| (from V <sub>DD</sub> )              | T = 125 °C                                                                                   | _           | 117               | 300         | μA                    |

|                                      | Oscillator Suspend<br>OSCICN[7:6] = 00b<br>ZTCEN = 0                                         |             |                   |             |                       |

|                                      | T = 25 °C                                                                                    | _           | 2                 | _           | μA                    |

|                                      | T = 85 °C                                                                                    | _           | 3                 | _           | μA                    |

|                                      | T = 125 °C                                                                                   | _           | 50                | _           | μA                    |

| Wake-Up Time From Sus-<br>pend       | $\frac{\text{OSCICN[7:6]} = 00b}{\text{ZTCEN} = 0^4}$                                        | —           | _                 | 1           | μs                    |

|                                      | OSCICN[7:6] = 00b<br>ZTCEN = 1                                                               | —           | 5                 | _           | Instruction<br>Cycles |

| Power Supply Sensitivity             | Constant Temperature                                                                         |             | 0.10              |             | %/V                   |

| Temperature Sensitivity <sup>5</sup> | Constant Supply<br>TC <sub>1</sub>                                                           | _           | 5.0               | _           | ppm/°C                |

|                                      | TC <sub>2</sub>                                                                              | —           | -0.65             | —           | ppm/°C <sup>2</sup>   |

Notes:

1. See Section "11.2.1. VDD Monitor Thresholds and Minimum VDD" on page 108 for minimum  $V_{DD}$  requirements.

- VREGMIN is the minimum output of the voltage regulator for its low setting (REG0CN: REG0MD = 0b). See Table 2.6, "Voltage Regulator Electrical Specifications," on page 30.

- 3. This is the average frequency across the operating temperature range.

- 4. See "20.7. Internal Oscillator Suspend Mode" on page 212 for ZTCEN setting in older silicon revisions.

- 5. Use temperature coefficients  $TC_1$  and  $TC_2$  to calculate the new internal oscillator frequency using the following equation:

$$f(T) = f0 x (1 + TC_1 x (T - T0) + TC_2 x (T - T0)^2)$$

where f0 is the internal oscillator frequency at 25 °C and T0 is 25 °C.

### Table 3.1. Pin Definitions for the C8051F52x and C8051F52xA (DFN 10)

| Name               | Pin Nun           | nbers     | Туре             | Description                                                                                                                                                                                                                                                                                                                                                                   |  |

|--------------------|-------------------|-----------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                    | 'F52xA<br>'F52x-C | 'F52x     |                  |                                                                                                                                                                                                                                                                                                                                                                               |  |

| RST/<br>C2CK       | 1                 | 1         | D I/O<br>D I/O   | Device Reset. Open-drain output of internal POR or $V_{DD}$ monitor.<br>An external source can initiate a system reset by driving this pin<br>low for at least the minimum RST low time to generate a system<br>reset, as defined in Table 2.8 on page 32. A 1 k $\Omega$ pullup to<br>$V_{REGIN}$ is recommended. See Reset Sources Section for a com-<br>plete description. |  |

|                    |                   |           |                  | Clock signal for the C2 Debug Interface.                                                                                                                                                                                                                                                                                                                                      |  |

| P0.0/              | 2                 | 2         | D I/O or<br>A In | Port 0.0. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                    |  |

| V <sub>REF</sub>   |                   |           | A O or<br>D In   |                                                                                                                                                                                                                                                                                                                                                                               |  |

| GND                | 3                 | 3         |                  | Ground.                                                                                                                                                                                                                                                                                                                                                                       |  |

| V <sub>DD</sub>    | 4                 | 4         |                  | Core Supply Voltage.                                                                                                                                                                                                                                                                                                                                                          |  |

| V <sub>REGIN</sub> | 5                 | 5         |                  | On-Chip Voltage Regulator Input.                                                                                                                                                                                                                                                                                                                                              |  |

| P0.5/RX*/          | 6                 |           | D I/O or<br>A In | Port 0.5. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                    |  |

| CNVSTR             |                   |           | D In             | External Converter start input for the ADC0, see Section "4. 12-<br>Bit ADC (ADC0)" on page 52 for a complete description.                                                                                                                                                                                                                                                    |  |

| P0.5/              |                   | 6         | D I/O or<br>A In | Port 0.5. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                    |  |

| CNVSTR             |                   |           | D In             | External Converter start input for the ADC0, see Section "4. 12-<br>Bit ADC (ADC0)" on page 52 for a complete description.                                                                                                                                                                                                                                                    |  |

| P0.4/TX*           | 7                 |           | D I/O or<br>A In | Port 0.4. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                    |  |

| P0.4/RX*           | —                 | 7         | D I/O or<br>A In | Port 0.4. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                    |  |

| P0.3               | 8                 |           | D I/O or<br>A In | r Port 0.3. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                  |  |

| XTAL2              |                   |           | D I/O            | External Clock Output. For an external crystal or resonator, this pin is the excitation driver. This pin is the external clock input for CMOS, capacitor, or RC oscillator configurations. See Section "14. Oscillators" on page 135.                                                                                                                                         |  |

| Note: Please       | refer to Se       | ection "2 | 0. Device S      | Specific Behavior" on page 210.                                                                                                                                                                                                                                                                                                                                               |  |

### Table 3.7. Pin Definitions for the C8051F53x and C805153xA (QFN 20)

| Name               | Pin Numbers       |       | Туре             | Description                                                                                                                                                                                                                                                                                                                                                                 |  |

|--------------------|-------------------|-------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                    | ʻF53xA<br>ʻF53x-C | 'F53x |                  |                                                                                                                                                                                                                                                                                                                                                                             |  |

| RST/<br>C2CK       | 1                 | 1     | D I/O<br>D I/O   | Device Reset. Open-drain output of internal POR or $V_{DD}$ monitor<br>An external source can initiate a system reset by driving this pin<br>low for at least the minimum RST low time to generate a system<br>reset, as defined in Table 2.8 on page 32. A 1 k $\Omega$ pullup to<br>$V_{REGIN}$ is recommended. See Reset Sources Section for a com<br>plete description. |  |

|                    |                   |       |                  | Clock signal for the C2 Debug Interface.                                                                                                                                                                                                                                                                                                                                    |  |

| P0.0/              | 2                 | 2     | D I/O or<br>A In | r Port 0.0. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                |  |

| $V_{REF}$          |                   |       | A O or<br>D In   | External V <sub>REF</sub> Input. See V <sub>REF</sub> Section.                                                                                                                                                                                                                                                                                                              |  |

| GND                | 3                 | 3     |                  | Ground.                                                                                                                                                                                                                                                                                                                                                                     |  |

| V <sub>DD</sub>    | 4                 | 4     |                  | Core Supply Voltage.                                                                                                                                                                                                                                                                                                                                                        |  |

| V <sub>REGIN</sub> | 5                 | 5     |                  | On-Chip Voltage Regulator Input.                                                                                                                                                                                                                                                                                                                                            |  |

| P1.7               | 6                 | 6     | D I/O or<br>A In | Port 1.7. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                  |  |

| P1.6               | 7                 | 7     | D I/O or<br>A In | Port 1.6. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                  |  |

| P1.5               | 8                 | 8     | D I/O or<br>A In | Port 1.5. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                  |  |

| P1.4               | 9                 | 9     | D I/O or<br>A In | Port 1.4. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                  |  |

| P1.3               | 10                | 10    | D I/O or<br>A In | Port 1.3. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                  |  |

| P1.2/              | 11                | 11    | D I/O or<br>A In | Port 1.2. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                  |  |

| CNVSTR             |                   |       | D In             | External Converter start input for the ADC0, see Section "4. 12-<br>Bit ADC (ADC0)" on page 52 for a complete description.                                                                                                                                                                                                                                                  |  |

| P1.1               | 12                | 12    | D I/O or<br>A In | Port 1.1. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                  |  |

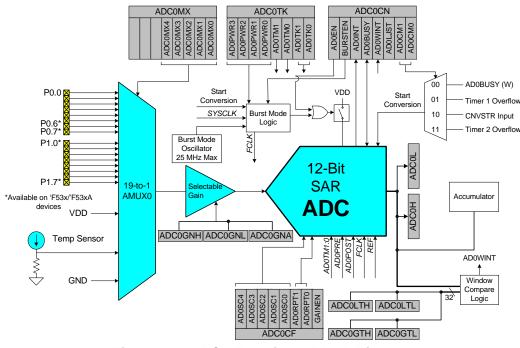

## 4. 12-Bit ADC (ADC0)

The ADC0 on the C8051F52x/F52xA/F53x/F53xA Family consists of an analog multiplexer (AMUX0) with 16/6 total input selections, and a 200 ksps, 12-bit successive-approximation-register (SAR) ADC with integrated track-and-hold, programmable window detector, programmable gain, and hardware accumulator. The ADC0 subsystem has a special Burst Mode which can automatically enable ADC0, capture and accumulate samples, then place ADC0 in a low power shutdown mode without CPU intervention. The AMUX0, data conversion modes, and window detector are all configurable under software control via the Special Function Registers shown in Figure 4.1. ADC0 inputs are single-ended and may be configured to measure P0.0-P1.7, the Temperature Sensor output,  $V_{DD}$ , or GND with respect to GND. The voltage reference for the ADC is selected as described in Section "5. Voltage Reference" on page 72. ADC0 is enabled when the AD0EN bit in the ADC0 Control register (ADC0CN) is set to logic 1, or when performing conversions in Burst Mode. ADC0 is in low power shutdown when AD0EN is logic 0 and no Burst Mode conversions are taking place.

Figure 4.1. ADC0 Functional Block Diagram

## 4.1. Analog Multiplexer

AMUX0 selects the input channel to the ADC. Any of the following may be selected as an input: P0.0–P1.7, the on-chip temperature sensor, the core power supply ( $V_{DD}$ ), or ground (GND). **ADC0 is single-ended and all signals measured are with respect to GND.** The ADC0 input channels are selected using the ADC0MX register as described in SFR Definition 4.4.

**Important Note About ADC0 Input Configuration:** Port pins selected as ADC0 inputs should be configured as analog inputs, and should be skipped by the Digital Crossbar. To configure a Port pin for analog input, set to 0 the corresponding bit in register PnMDIN (for n = 0,1). To force the Crossbar to skip a Port pin, set to 1 the corresponding bit in register PnSKIP (for n = 0,1). See Section "13. Port Input/Output" on page 120 for more Port I/O configuration details.

## 4.3. ADC0 Operation

In a typical system, ADC0 is configured using the following steps:

- 1. If a gain adjustment is required, refer to Section "4.4. Selectable Gain" on page 60.

- 2. Choose the start of conversion source.

- 3. Choose Normal Mode or Burst Mode operation.

- 4. If Burst Mode, choose the ADC0 Idle Power State and set the Power-Up Time.

- 5. Choose the tracking mode. Note that Pre-Tracking Mode can only be used with Normal Mode.

- 6. Calculate required settling time and set the post convert-start tracking time using the AD0TK bits.

- 7. Choose the repeat count.

- 8. Choose the output word justification (Right-Justified or Left-Justified).

- 9. Enable or disable the End of Conversion and Window Comparator Interrupts.

#### 4.3.1. Starting a Conversion

A conversion can be initiated in one of four ways, depending on the programmed states of the ADC0 Start of Conversion Mode bits (AD0CM1–0) in register ADC0CN. Conversions may be initiated by one of the following:

- Writing a 1 to the AD0BUSY bit of register ADC0CN

- A rising edge on the CNVSTR input signal (pin P0.6)

- A Timer 1 overflow (i.e., timed continuous conversions)

- A Timer 2 overflow (i.e., timed continuous conversions)

Writing a 1 to AD0BUSY provides software control of ADC0 whereby conversions are performed "ondemand." During conversion, the AD0BUSY bit is set to logic 1 and reset to logic 0 when the conversion is complete. The falling edge of AD0BUSY triggers an interrupt (when enabled) and sets the ADC0 interrupt flag (AD0INT). Note: When polling for ADC conversion completions, the ADC0 interrupt flag (AD0INT) should be used. Converted data is available in the ADC0 data registers, ADC0H:ADC0L, when bit AD0INT is logic 1. Note that when Timer 2 overflows are used as the conversion source, Low Byte overflows are used if Timer2 is in 8-bit mode; High byte overflows are used if Timer 2 is in 16-bit mode. See Section "18. Timers" on page 182 for timer configuration.

**Important Note:** The CNVSTR input pin also functions as Port pin P0.5 on C8051F52x/52xA devices and P1.2 on C8051F53x/53xA devices. When the CNVSTR input is used as the ADC0 conversion source, Port pin P0.5 or P1.2 should be skipped by the Digital Crossbar. To configure the Crossbar to skip P0.5 or P1.2, set to 1 to the appropriate bit in the PnSKIP register. See Section "13. Port Input/Output" on page 120 for details on Port I/O configuration.

#### 4.3.2. Tracking Modes

Each ADC0 conversion must be preceded by a minimum tracking time for the converted result to be accurate, as shown in Table 2.3 on page 28. ADC0 has three tracking modes: Pre-Tracking, Post-Tracking, and Dual-Tracking. Pre-Tracking Mode provides the minimum delay between the convert start signal and end of conversion by tracking continuously before the convert start signal. This mode requires software management in order to meet minimum tracking requirements. In Post-Tracking Mode, a programmable tracking time starts after the convert start signal and is managed by hardware. Dual-Tracking Mode maximizes tracking time by tracking before and after the convert start signal. Figure 4.3 shows examples of the three tracking modes.

Pre-Tracking Mode is selected when AD0TM is set to 10b. Conversions are started immediately following the convert start signal. ADC0 is tracking continuously when not performing a conversion. Software must allow at least the minimum tracking time between each end of conversion and the next convert start signal. The minimum tracking time must also be met prior to the first convert start signal after ADC0 is enabled.

## SFR Definition 4.4. ADC0MX: ADC0 Channel Select

| R/W     | R/W                       | R/W     | R/W             | R/W     | R/W      | R/W  | R/W  | Reset Value |  |

|---------|---------------------------|---------|-----------------|---------|----------|------|------|-------------|--|

| -       | -                         | -       | AD0MX 00011     |         |          |      |      |             |  |

| Bit7    | Bit6                      | Bit5    | Bit4            | Bit3    | Bit2     | Bit1 | Bit0 | SFR Address |  |

|         |                           |         |                 |         |          |      |      | 0xBB        |  |

| 107 E.  |                           |         |                 |         |          |      |      |             |  |

|         | UNUSED. Re<br>AD0MX4–0: / |         |                 |         | <b>`</b> |      |      |             |  |

| 1154-0. |                           | AIVIOAU | rosilive inpi   |         | 1        |      |      |             |  |

|         | AD0MX4-0                  |         | ADC0 Input      | Channel |          |      |      |             |  |

|         | 00000                     |         | P0.0            |         |          |      |      |             |  |

|         | 00001                     |         | P0.1            |         |          |      |      |             |  |

|         | 00010                     |         | P0.2            |         |          |      |      |             |  |

|         | 00011                     |         | P0.3            |         |          |      |      |             |  |

|         | 00100                     |         | P0.4            |         |          |      |      |             |  |

|         | 00101                     |         | P0.5            |         |          |      |      |             |  |

|         | 00110                     |         | P0.6*           |         |          |      |      |             |  |

|         | 00111                     |         | P0.7*           |         |          |      |      |             |  |

|         | 01000                     |         | P1.0*           |         |          |      |      |             |  |

|         | 01001                     |         | P1.1*           |         |          |      |      |             |  |

|         | 01010                     |         | P1.2*           |         |          |      |      |             |  |

|         | 01011                     |         | P1.3*           |         |          |      |      |             |  |

|         | 01100                     |         | P1.4*           |         |          |      |      |             |  |

|         | 01101                     |         | P1.5*           |         |          |      |      |             |  |

|         | 01110                     |         | P1.6*           |         |          |      |      |             |  |

|         | 01111                     |         | P1.7*           |         |          |      |      |             |  |

|         | 11000                     |         | Temp Senso      | or      |          |      |      |             |  |

|         | 11001                     |         | V <sub>DD</sub> |         |          |      |      |             |  |

|         | 11010 - 1111              |         | GND             |         |          |      |      |             |  |

Note that false rising edges and falling edges can be detected when the comparator is first powered-on or if changes are made to the hysteresis or response time control bits. Therefore, it is recommended that the rising-edge and falling-edge flags be explicitly cleared to logic 0 a short time after the comparator is enabled or its mode bits have been changed. This Power Up Time is specified in Table 2.7 on page 31.

## SFR Definition 7.1. CPT0CN: Comparator0 Control

| R/W      | R                                                                   | R/W           | R/W      | R/W       | R/W            | R/W          | R/W      | Reset Value  |  |

|----------|---------------------------------------------------------------------|---------------|----------|-----------|----------------|--------------|----------|--------------|--|

| CP0EN    | CP0OUT                                                              | <b>CP0RIF</b> | CP0FIF   | CP0HYP1   | CP0HYP0        | CP0HYN1      | CP0HYN0  | 00000000     |  |

| Bit7     | Bit6                                                                | Bit5          | Bit4     | Bit3      | Bit2           | Bit1         | Bit0     | SFR Address: |  |

|          |                                                                     |               |          |           |                |              |          | 0x9B         |  |

|          |                                                                     |               |          |           |                |              |          |              |  |

| Bit7:    | CP0EN: Cor                                                          |               |          |           |                |              |          |              |  |

|          | 0: Comparat                                                         |               |          |           |                |              |          |              |  |

|          | 1: Comparat                                                         |               |          |           |                |              |          |              |  |

| Bit6:    | CPOOUT: Co                                                          | •             | •        | ate Flag. |                |              |          |              |  |

|          | 0: Voltage or                                                       |               |          |           |                |              |          |              |  |

| D.16     | 1: Voltage or                                                       |               |          |           |                |              |          |              |  |

| Bit5:    | CPORIF: Col                                                         | •             |          | •         | ainaa thia fl  | og woo loot  | alaarad  |              |  |

|          | 0: No Comparat                                                      |               |          |           | since this h   | ag was last  | cleared. |              |  |

| Bit4:    | CP0FIF: Cor                                                         | -             | -        |           |                |              |          |              |  |

| Bit4.    | 0: No Compa                                                         |               |          |           | d since this f | lad was last | cleared  |              |  |

|          | 1: Comparat                                                         |               |          |           |                | lag had lad  | cicalcal |              |  |

| Bits3-2: | CP0HYP1-0                                                           |               |          |           | is Control Bi  | ts.          |          |              |  |

|          | 00: Positive                                                        |               |          |           |                |              |          |              |  |

|          | 01: Positive                                                        | Hysteresis    | = 5 mV.  |           |                |              |          |              |  |

|          | 10: Positive                                                        | Hysteresis    | = 10 mV. |           |                |              |          |              |  |

|          | 11: Positive                                                        |               |          |           |                |              |          |              |  |

| Bits1–0: | CP0HYN1–0: Comparator0 Negative Hysteresis Control Bits.            |               |          |           |                |              |          |              |  |

|          | 00: Negative Hysteresis Disabled.                                   |               |          |           |                |              |          |              |  |

|          | 01: Negative Hysteresis = 5 mV.<br>10: Negative Hysteresis = 10 mV. |               |          |           |                |              |          |              |  |

|          | •                                                                   |               |          |           |                |              |          |              |  |

|          | 11: Negative                                                        | Hysteresis    | = 20 mV. |           |                |              |          |              |  |

|          |                                                                     |               |          |           |                |              |          |              |  |

| FR Defi               | nition 10.5. IT01C                                 | F: INT0/INT1 Configurat               | ion                                                 |  |  |  |  |  |  |  |

|-----------------------|----------------------------------------------------|---------------------------------------|-----------------------------------------------------|--|--|--|--|--|--|--|

| R/W                   | R/W R/W                                            | R/W R/W R                             | W R/W R/W Reset Value                               |  |  |  |  |  |  |  |

| IN1PL                 | IN1SL2 IN1SL1                                      | IN1SLO INOPL INO                      | SL2 IN0SL1 IN0SL0 0000001                           |  |  |  |  |  |  |  |

| Bit7                  | Bit6 Bit5                                          | Bit4 Bit3 B                           | it2 Bit1 Bit0                                       |  |  |  |  |  |  |  |

|                       |                                                    |                                       | SFR Address: 0xE4                                   |  |  |  |  |  |  |  |

| Note: Refer           | to SFR Definition 18.1. "TO                        | CON: Timer Control" on page 186 for I | NT0/1 edge- or level-sensitive interrupt selection. |  |  |  |  |  |  |  |

|                       |                                                    |                                       |                                                     |  |  |  |  |  |  |  |

| Bit 7:                | INTPL: INTO Polarity                               |                                       |                                                     |  |  |  |  |  |  |  |

|                       | 0: INTO input is active<br>1: INTO input is active |                                       |                                                     |  |  |  |  |  |  |  |

| Bits 6–4 <sup>.</sup> | IN1SL2–0: INTO Port                                |                                       |                                                     |  |  |  |  |  |  |  |

|                       |                                                    |                                       | . Note that this pin assignment is inde-            |  |  |  |  |  |  |  |

|                       |                                                    |                                       | ned Port pin without disturbing the                 |  |  |  |  |  |  |  |

|                       |                                                    |                                       | ne Crossbar. The Crossbar will not                  |  |  |  |  |  |  |  |

|                       |                                                    |                                       | skip the selected pin (accomplished by              |  |  |  |  |  |  |  |

|                       |                                                    | ponding bit in register P0SKIP        | ').<br>_                                            |  |  |  |  |  |  |  |

|                       | IN1SL2-0                                           | INT1 Port Pin                         |                                                     |  |  |  |  |  |  |  |

|                       | 000                                                | P0.0                                  |                                                     |  |  |  |  |  |  |  |

|                       | 001                                                | P0.1                                  | _                                                   |  |  |  |  |  |  |  |

|                       | 010                                                | P0.2                                  | _                                                   |  |  |  |  |  |  |  |

|                       | 011                                                | P0.3                                  | _                                                   |  |  |  |  |  |  |  |

|                       | 100                                                | P0.4                                  | _                                                   |  |  |  |  |  |  |  |

|                       | 101                                                | P0.5                                  | _                                                   |  |  |  |  |  |  |  |

|                       | 110                                                | P0.6*                                 | _                                                   |  |  |  |  |  |  |  |

|                       | 111                                                | P0.7*                                 | _                                                   |  |  |  |  |  |  |  |

|                       | Note: Available in the                             | C80151F53x/C8051F53xA parts.          |                                                     |  |  |  |  |  |  |  |

| Bit 3:                | INOPL: INTO Polarity                               |                                       |                                                     |  |  |  |  |  |  |  |

|                       | 0: INTO interrupt is ac                            |                                       |                                                     |  |  |  |  |  |  |  |

| D:40 0 0.             | 1: INT0 interrupt is ac<br>INT0SL2-0: INT0 Po      |                                       |                                                     |  |  |  |  |  |  |  |

| BITS Z-U              |                                                    |                                       | . Note that this pin assignment is inde-            |  |  |  |  |  |  |  |

|                       |                                                    | ¥                                     | ned Port pin without disturbing the                 |  |  |  |  |  |  |  |

|                       |                                                    |                                       | ne Crossbar. The Crossbar will not                  |  |  |  |  |  |  |  |

|                       | <b>e</b> .                                         |                                       | skip the selected pin (accomplished by              |  |  |  |  |  |  |  |

|                       | setting to 1 the corres                            | ponding bit in register P0SKIP        | ).                                                  |  |  |  |  |  |  |  |

|                       | IN0SL2-0                                           | INT0 Port Pin                         |                                                     |  |  |  |  |  |  |  |

|                       | 000                                                | P0.0                                  |                                                     |  |  |  |  |  |  |  |

|                       | 001                                                | P0.1                                  |                                                     |  |  |  |  |  |  |  |

|                       | 010                                                | P0.2                                  |                                                     |  |  |  |  |  |  |  |

|                       | 011                                                | P0.3                                  |                                                     |  |  |  |  |  |  |  |

|                       | 100                                                | P0.4                                  |                                                     |  |  |  |  |  |  |  |

|                       | 101                                                | P0.5                                  |                                                     |  |  |  |  |  |  |  |

|                       | 110                                                | P0.6*                                 |                                                     |  |  |  |  |  |  |  |

|                       | 111                                                | P0.7*                                 |                                                     |  |  |  |  |  |  |  |

|                       | Note: Available in the                             | C80151F53x/C8051F53xA parts.          |                                                     |  |  |  |  |  |  |  |

### 11.3. External Reset

The external RST pin provides a means for external circuitry to force the device into a reset state. Asserting an active-low signal on the RST pin generates a reset; an external pullup and/or decoupling of the RST pin may be necessary to avoid erroneous noise-induced resets. See Table 2.8 on page 32 for complete RST pin specifications. The PINRSF flag (RSTSRC.0) is set on exit from an external reset.

### **11.4. Missing Clock Detector Reset**

The Missing Clock Detector (MCD) is a one-shot circuit that is triggered by the system clock. If the system clock remains high or low for more than 100  $\mu$ s, the one-shot will time out and generate a reset. After a MCD reset, the MCDRSF flag (RSTSRC.2) will read 1, signifying the MCD as the reset source; otherwise, this bit reads 0. Writing a 1 to the MCDRSF bit enables the Missing Clock Detector; writing a 0 disables it. The state of the RST pin is unaffected by this reset.

#### 11.5. Comparator Reset

Comparator0 can be configured as a reset source by writing a 1 to the CORSEF flag (RSTSRC.5). Comparator0 should be enabled and allowed to settle prior to writing to CORSEF to prevent any turn-on chatter on the output from generating an unwanted reset. The Comparator0 reset is active-low: if the non-inverting input voltage (on CP0+) is less than the inverting input voltage (on CP0-), the device is put into the reset state. After a Comparator0 reset, the CORSEF flag (RSTSRC.5) will read 1 signifying Comparator0 as the reset source; otherwise, this bit reads 0. The state of the RST pin is unaffected by this reset.

#### 11.6. PCA Watchdog Timer Reset

The programmable Watchdog Timer (WDT) function of the Programmable Counter Array (PCA) can be used to prevent software from running out of control during a system malfunction. The PCA WDT function can be enabled or disabled by software as described in Section "19.3. Watchdog Timer Mode" on page 203; the WDT is enabled and clocked by SYSCLK / 12 following any reset. If a system malfunction prevents user software from updating the WDT, a reset is generated and the WDTRSF bit (RSTSRC.5) is set to 1. The state of the RST pin is unaffected by this reset.

#### 11.7. Flash Error Reset

If a Flash read/write/erase or program read targets an illegal address, a system reset is generated. This may occur due to any of the following:

- A Flash write or erase is attempted above user code space. This occurs when PSWE is set to 1 and a MOVX write operation targets an address above the Lock Byte address.

- A Flash read is attempted above user code space. This occurs when a MOVC operation targets an address above the Lock Byte address.

- A program read is attempted above user code space. This occurs when user code attempts to branch to an address above the Lock Byte address.

- A Flash read, write or erase attempt is restricted due to a Flash security setting (see Section "12.4. Security Options" on page 117).

- A Flash write or erase is attempted while the V<sub>DD</sub> Monitor (VDDMON0) is disabled or not set to its high threshold setting.

The FERROR bit (RSTSRC.6) is set following a Flash error reset. The state of the  $\overrightarrow{RST}$  pin is unaffected by this reset.

**Note:** Please refer to Section "20.6. Reset Low Time" on page 212 for restrictions on reset low time in older silicon revisions A and B.

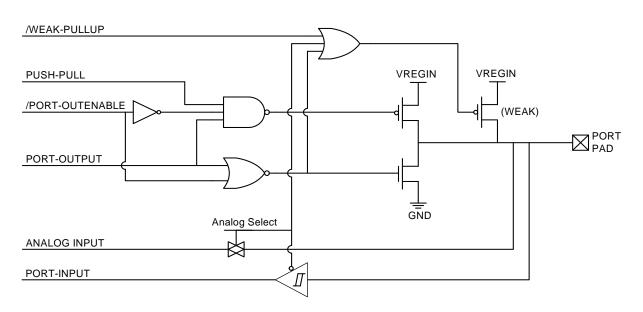

Figure 13.2. Port I/O Cell Block Diagram

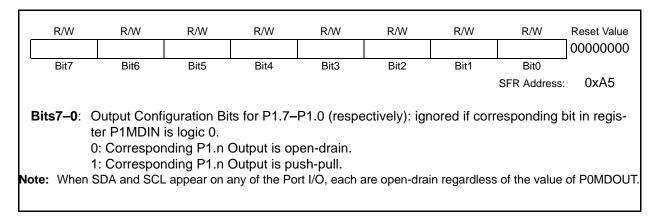

## SFR Definition 13.11. P1MDOUT: Port1 Output Mode

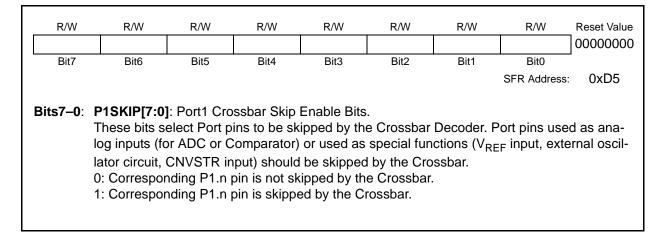

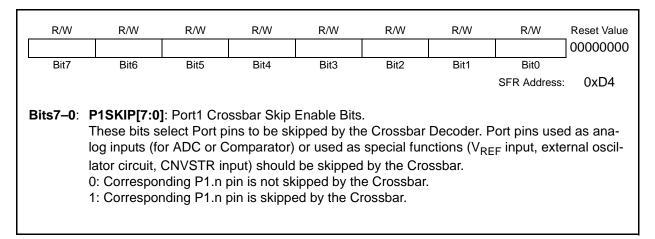

## SFR Definition 13.12. P1SKIP: Port1 Skip

### SFR Definition 13.13. P0SKIP: Port0 Skip

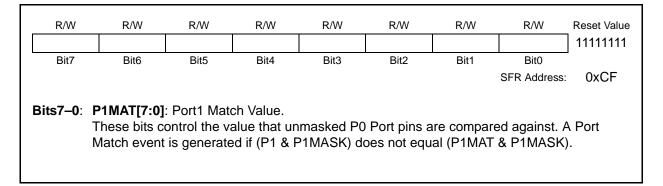

#### SFR Definition 13.14. P1MAT: Port1 Match

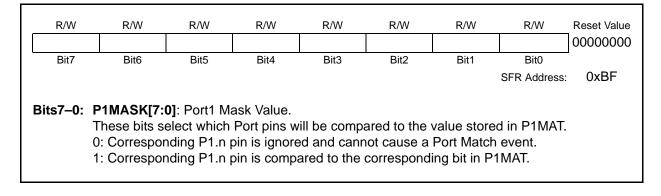

## SFR Definition 13.15. P1MASK: Port1 Mask

### 14.2. External Oscillator Drive Circuit

The external oscillator circuit may drive an external crystal, ceramic resonator, capacitor, or RC network. A CMOS clock may also provide a clock input. For a crystal or ceramic resonator configuration, the crystal/resonator must be wired across the XTAL1 and XTAL2 pins as shown in Option 1 of Figure 14.1. A 10 M $\Omega$  resistor also must be wired across the XTAL1 and XTAL2 pins for the crystal/resonator configuration. In RC, capacitor, or CMOS clock configuration, the clock source should be wired to the XTAL2 pin as shown in Option 2, 3, or 4 of Figure 14.1. The type of external oscillator must be selected in the OSCXCN register, and the frequency control bits (XFCN) must be selected appropriately (see SFR Definition 14.4. OSCXCN: External Oscillator Control).

**Important Note on External Oscillator Usage:** Port pins must be configured when using the external oscillator circuit. When the external oscillator drive circuit is enabled in crystal/resonator mode, Port pins P0.7 and P1.0 ('F53x/'F53xA) or P0.2 and P0.3 ('F52x/'F52xA) are used as XTAL1 and XTAL2 respectively. When the external oscillator drive circuit is enabled in capacitor, RC, or CMOS clock mode, Port pin P1.0 ('F53x/'F53xA) or P0.3 ('F52x/'F52xA) is used as XTAL2. The Port I/O Crossbar should be configured to skip the Port pins used by the oscillator circuit; see Section "13.1. Priority Crossbar Decoder" on page 122 for Crossbar configuration. Additionally, when using the external oscillator circuit in crystal/resonator, capacitor, or RC mode, the associated Port pins should be configured as **analog inputs**. In CMOS clock mode, the associated pin should be configured as a **digital input**. See Section "13.2. Port I/O Initialization" on page 126 for details on Port input mode selection.

#### 14.2.1. Clocking Timers Directly Through the External Oscillator

The external oscillator source divided by eight is a clock option for the timers (Section "18. Timers" on page 182) and the Programmable Counter Array (PCA) (Section "19. Programmable Counter Array (PCA0)" on page 195). When the external oscillator is used to clock these peripherals, but is not used as the system clock, the external oscillator frequency must be less than or equal to the system clock frequency. In this configuration, the clock supplied to the peripheral (external oscillator / 8) is synchronized with the system clock; the jitter associated with this synchronization is limited to  $\pm 0.5$  system clock cycles.

#### 14.2.2. External Crystal Example

If a crystal or ceramic resonator is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 14.1, Option 1. The External Oscillator Frequency Control value (XFCN) should be chosen from the Crystal column of the table in SFR Definition 14.4. For example, a 12 MHz crystal requires an XFCN setting of 111b.

When the crystal oscillator is first enabled, the oscillator amplitude detection circuit requires a settling time to achieve proper bias. Introducing a delay of 1 ms between enabling the oscillator and checking the XTLVLD bit will prevent a premature switch to the external oscillator as the system clock. Switching to the external oscillator before the crystal oscillator has stabilized can result in unpredictable behavior. The recommended procedure is:

- 1. Configure XTAL1 and XTAL2 pins by writing 1 to the port latch.

- 2. Configure XTAL1 and XTAL2 as analog inputs.

- 3. Enable the external oscillator.

- 4. Wait at least 1 ms.

- 5. Poll for XTLVLD => 1.

6. Switch the system clock to the external oscillator.

Note: Tuning-fork crystals may require additional settling time before XTLVLD returns a valid result.

The capacitors shown in the external crystal configuration provide the load capacitance required by the crystal for correct oscillation. These capacitors are "in series" as seen by the crystal and "in parallel" with the stray capacitance of the XTAL1 and XTAL2 pins.

### **15.2. Operational Modes**

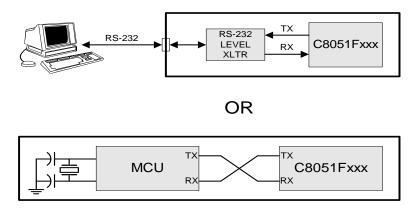

UART0 provides standard asynchronous, full duplex communication. The UART mode (8-bit or 9-bit) is selected by the S0MODE bit (SCON0.7). Typical UART connection options are shown below.

Figure 15.3. UART Interconnect Diagram

#### 15.2.1. 8-Bit UART

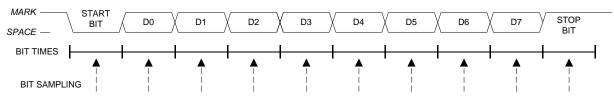

8-Bit UART mode uses a total of 10 bits per data byte: one start bit, eight data bits (LSB first), and one stop bit. Data are transmitted LSB first from the TX0 pin and received at the RX0 pin. On receive, the eight data bits are stored in SBUF0 and the stop bit goes into RB80 (SCON0.2).

Data transmission begins when software writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to logic 1. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: RI0 must be logic 0, and if MCE0 is logic 1, the stop bit must be logic 1. In the event of a receive data overrun, the first received 8 bits are latched into the SBUF0 receive register and the following overrun data bits are lost.

If these conditions are met, the eight bits of data is stored in SBUF0, the stop bit is stored in RB80 and the RI0 flag is set. If these conditions are not met, SBUF0 and RB80 will not be loaded and the RI0 flag will not be set. An interrupt will occur if enabled when either TI0 or RI0 is set.

Figure 15.4. 8-Bit UART Timing Diagram

## **19. Programmable Counter Array (PCA0)**

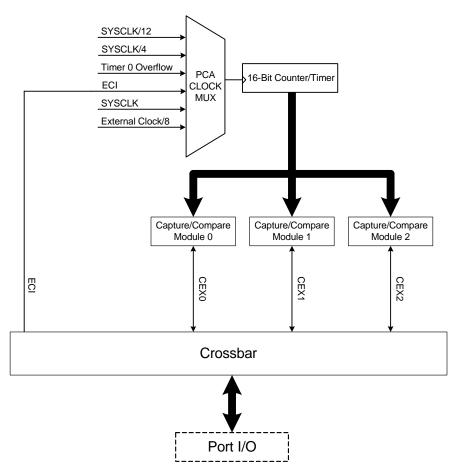

The Programmable Counter Array (PCA0) provides enhanced timer functionality while requiring less CPU intervention than the standard 8051 counter/timers. The PCA consists of a dedicated 16-bit counter/timer and three 16-bit capture/compare modules. Each capture/compare module has its own associated I/O line (CEXn) which is routed through the Crossbar to Port I/O when enabled (See Section "13.1. Priority Cross-bar Decoder" on page 122 for details on configuring the Crossbar). The counter/timer is driven by a programmable timebase that can select between six sources: system clock, system clock divided by four, system clock divided by twelve, the external oscillator clock source divided by 8, Timer 0 overflow, or an external clock signal on the ECI input pin. Each capture/compare module may be configured to operate independently in one of three modes: Edge-Triggered Capture, Software Timer, High-Speed Output, Frequency Output, 8-Bit PWM, or 16-Bit PWM (each mode is described in Section "19.2. Capture/Compare Modules" on page 197). The PCA is configured and controlled through the system controller's Special Function Registers. The PCA block diagram is shown in Figure 19.1.

**Important Note:** The PCA Module 2 may be used as a watchdog timer (WDT), and is enabled in this mode following a system reset. Access to certain PCA registers is restricted while WDT mode is enabled. See Section "19.3. Watchdog Timer Mode" on page 203 for details.

Figure 19.1. PCA Block Diagram

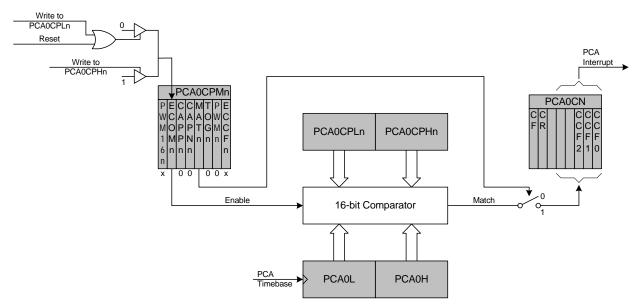

#### 19.2.2. Software Timer (Compare) Mode

In Software Timer mode, the PCA counter/timer value is compared to the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1 and an interrupt request is generated if CCF interrupts are enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Setting the ECOMn and MATn bits in the PCA0CPMn register enables Software Timer mode.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Figure 19.5. PCA Software Timer Mode Diagram

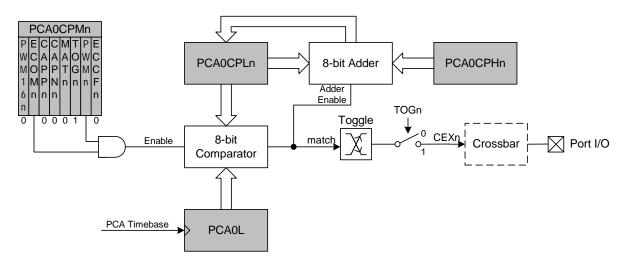

#### 19.2.4. Frequency Output Mode

Frequency Output Mode produces a programmable-frequency square wave on the module's associated CEXn pin. The capture/compare module high byte holds the number of PCA clocks to count before the output is toggled. The frequency of the square wave is then defined by Equation 19.1.

$$F_{CEXn} = \frac{F_{PCA}}{2 \times PCA0CPHn}$$

**Note:** A value of 0x00 in the PCA0CPHn register is equal to 256 for this equation.

#### Equation 19.1. Square Wave Frequency Output

Where  $F_{PCA}$  is the frequency of the clock selected by the CPS2-0 bits in the PCA mode register, PCA0MD. The lower byte of the capture/compare module is compared to the PCA counter low byte; on a match, CEXn is toggled and the offset held in the high byte is added to the matched value in PCA0CPLn. Frequency Output Mode is enabled by setting the ECOMn, TOGn, and PWMn bits in the PCA0CPMn register.

Figure 19.7. PCA Frequency Output Mode

## 20.5. V<sub>DD</sub> Monitor (VDDMON0) High Threshold Setting

The calibration behavior of the internal voltage regulator (REG0) and its impact on  $V_{DD}$  monitor (VDD-MON0) high threshold setting differs between the silicon revisions of C8051F52x/52xA/F53x/F53xA devices.

The following note applies to **Revision A and Revision B devices**: The output of the internal voltage regulator (REG0) is calibrated by the MCU immediately after any reset event. The output of the un-calibrated internal regulator could be below the high threshold setting ( $V_{RST-HIGH}$ ) of the  $V_{DD}$  Monitor (VDDMON0). If this is the case <u>and</u> the  $V_{DD}$  Monitor is set to the high threshold setting <u>and</u> if the MCU receives a non-power on reset, the MCU will remain in reset until a power-on reset (POR) occurs (i.e.  $V_{DD}$  Monitor will keep the device in reset). A POR will force the  $V_{DD}$  Monitor to the low threshold setting which is guaranteed to be below the un-calibrated output of the internal regulator. The device will then exit reset and resume normal operation. It is for this reason Silicon Labs strongly recommends that the  $V_{DD}$  Monitor is always left in the low threshold setting (i.e., default value upon POR).

When programming the Flash in-system, the  $V_{DD}$  Monitor (VDDMON0) must be set to the high threshold setting. For the highest system reliability, the time the  $V_{DD}$  Monitor is set to the high threshold setting should be minimized (e.g., setting the  $V_{DD}$  Monitor to the high threshold setting just before the Flash write operation and then changing it back to the low threshold setting immediately after the Flash write operation).

The following note applies to **Revision C devices**: The output of the internal voltage regulator (REG0) is calibrated by the MCU immediately after a power-on reset (POR). This calibrated output setting will stay calibrated through any type of reset other than POR. Because of this change in behavior of REG0, the "low threshold" recommendation noted above for Revision A and Revision B devices does not apply to Revision C devices; the V<sub>DD</sub> Monitor (VDDMON0) can be set to the high threshold as needed depending on the application.

#### 20.6. Reset Low Time

The maximum reset low time differs between the silicon revisions of C8051F52x/52xA/F53x/F53xA devices.

Reset low time is the duration for which the  $\overrightarrow{RST}$  pin is driven low by an external circuit while power is applied to the device. On Revision A and Revision B devices with assembly build date code earlier than 1124 (year 2011, work week 24), the reset low time should be a maximum of 1 second. For longer reset low times, a percentage of devices within a narrow range of temperatures (a 5 to 10 C window) may "lock up" and fail to execute code. The condition is cleared only by cycling power.

Revision B devices with assembly date code 1124 or later and Revision C devices do not have any restrictions on reset low time.

#### 20.7. Internal Oscillator Suspend Mode

The required bias setting for the internal oscillator before entering suspend mode differs between the silicon revisions of C8051F52x/52xA/F53x/F53xA devices.

On Revision A and Revision B devices, firmware must set the ZTCEN bit in REF0CN (SFR Definition 5.1) before entering suspend mode. If ZTCEN is not set to 1, there is a low probability of the device remaining in suspend even when a wake-up condition is triggered. On Revision C devices, this bit need not be set to 1 before entering suspend mode.