Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                  |

|----------------------------|------------------------------------------------------------------|

| Product Status             | Active                                                           |

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | LINbus, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT               |

| Number of I/O              | 6                                                                |

| Program Memory Size        | 4KB (4K x 8)                                                     |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 256 x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.25V                                                       |

| Data Converters            | A/D 6x12b                                                        |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                               |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 10-VFDFN Exposed Pad                                             |

| Supplier Device Package    | 10-DFN (3x3)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f523-c-im |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name         | Pin Nur           | nbers     | Туре             | Description                                                                                                                                                                                                                           |

|--------------|-------------------|-----------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | 'F52xA<br>'F52x-C | 'F52x     |                  |                                                                                                                                                                                                                                       |

| P0.3/TX*/    | —                 | 8         | D I/O or<br>A In | Port 0.3. See Port I/O Section for a complete description.                                                                                                                                                                            |

| XTAL2        |                   |           | D I/O            | External Clock Output. For an external crystal or resonator, this pin is the excitation driver. This pin is the external clock input for CMOS, capacitor, or RC oscillator configurations. See Section "14. Oscillators" on page 135. |

| P0.2         | 9                 | 9         | D I/O or         | Port 0.2. See Port I/O Section for a complete description.                                                                                                                                                                            |

| XTAL1        |                   |           | A In             | External Clock Input. This pin is the external oscillator return for a crystal or resonator. Section "14. Oscillators" on page 135.                                                                                                   |

| P0.1/        | 10                | 10        | D I/O or<br>A In | Port 0.1. See Port I/O Section for a complete description.                                                                                                                                                                            |

|              |                   |           |                  |                                                                                                                                                                                                                                       |

| C2D          |                   |           | D I/O            | Bi-directional data signal for the C2 Debug Interface                                                                                                                                                                                 |

| lote: Please | refer to Se       | ection "2 | 0. Device S      | Specific Behavior" on page 210.                                                                                                                                                                                                       |

### Table 3.1. Pin Definitions for the C8051F52x and C8051F52xA (DFN 10) (Continued)

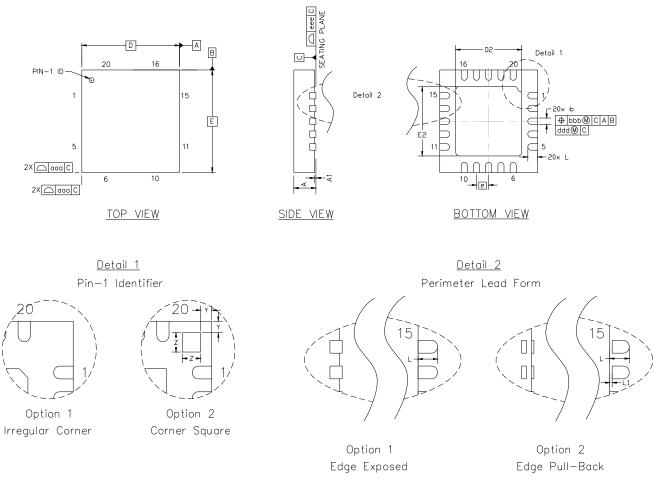

Figure 3.8. QFN-20 Package Diagram\*

\*Note: The Package Dimensions are given in Table 3.8, "QFN-20 Package Diagram Dimensions," on page 49.

## SFR Definition 4.4. ADC0MX: ADC0 Channel Select

| R/W     | R/W                     | R/W     | R/W             | R/W     | R/W   | R/W  | R/W  | Reset Value |

|---------|-------------------------|---------|-----------------|---------|-------|------|------|-------------|

| -       | -                       | -       |                 |         | AD0MX |      |      | 00011111    |

| Bit7    | Bit6                    | Bit5    | Bit4            | Bit3    | Bit2  | Bit1 | Bit0 | SFR Address |

|         |                         |         |                 |         |       |      |      | 0xBB        |

| 107 E.  |                         |         |                 |         |       |      |      |             |

|         | UNUSED. Re<br>AD0MX4–0: |         |                 |         |       |      |      |             |

| 1154-0. |                         | AIVIOAU | rosilive inpi   |         | 1     |      |      |             |

|         | AD0MX4-0                |         | ADC0 Input      | Channel |       |      |      |             |

|         | 00000                   |         | P0.0            |         |       |      |      |             |

|         | 00001                   |         | P0.1            |         |       |      |      |             |

|         | 00010                   |         | P0.2            |         |       |      |      |             |

|         | 00011                   |         | P0.3            |         |       |      |      |             |

|         | 00100                   |         | P0.4            |         |       |      |      |             |

|         | 00101                   |         | P0.5            |         |       |      |      |             |

|         | 00110                   |         | P0.6*           |         |       |      |      |             |

|         | 00111                   |         | P0.7*           |         |       |      |      |             |

|         | 01000                   |         | P1.0*           |         |       |      |      |             |

|         | 01001                   |         | P1.1*           |         |       |      |      |             |

|         | 01010                   |         | P1.2*           |         |       |      |      |             |

|         | 01011                   |         | P1.3*           |         |       |      |      |             |

|         | 01100                   |         | P1.4*           |         |       |      |      |             |

|         | 01101                   |         | P1.5*           |         |       |      |      |             |

|         | 01110                   |         | P1.6*           |         |       |      |      |             |

|         | 01111                   |         | P1.7*           |         |       |      |      |             |

|         | 11000                   |         | Temp Senso      | or      |       |      |      |             |

|         | 11001                   |         | V <sub>DD</sub> |         |       |      |      |             |

|         | 11010 - 1111            |         | GND             |         |       |      |      |             |

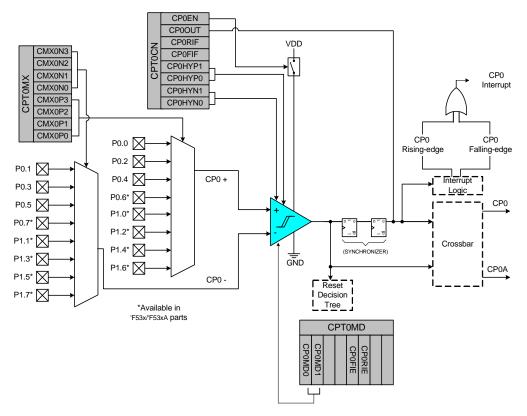

## 7. Comparator

C8051F52x/F52xA/F53x/F53xA devices include one on-chip programmable voltage comparator. The Comparator is shown in Figure 7.1.

The Comparator offers programmable response time and hysteresis, an analog input multiplexer, and two outputs that are optionally available at the Port pins: a synchronous "latched" output (CP0), or an asynchronous "raw" output (CP0A). The asynchronous CP0A signal is available even when the system clock is not active. This allows the Comparator to operate and generate an output with the device in STOP or SUS-PEND mode. When assigned to a Port pin, the Comparator output may be configured as open drain or push-pull (see Section "13.2. Port I/O Initialization" on page 126). The Comparator may also be used as a reset source (see Section "11.5. Comparator Reset" on page 110).

The Comparator inputs are selected in the CPT0MX register (SFR Definition 7.2). The CMX0P3–CMX0P0 bits select the Comparator0 positive input; the CMX0N3–CMX0N0 bits select the Comparator0 negative input.

**Important Note About Comparator Inputs:** The Port pins selected as Comparator inputs should be configured as analog inputs in their associated Port configuration register and configured to be skipped by the Crossbar (for details on Port configuration, see Section "13.3. General Purpose Port I/O" on page 128).

Figure 7.1. Comparator Functional Block Diagram

The Comparator output can be polled in software, used as an interrupt source, internal oscillator suspend awakening source and/or routed to a Port pin. When routed to a Port pin, the Comparator output is available asynchronous or synchronous to the system clock; the asynchronous output is available even in STOP or SUSPEND mode (with no system clock active). When disabled, the Comparator output (if assigned to a Port I/O pin via the Crossbar) defaults to the logic low state, and its supply current falls to

Note that false rising edges and falling edges can be detected when the comparator is first powered-on or if changes are made to the hysteresis or response time control bits. Therefore, it is recommended that the rising-edge and falling-edge flags be explicitly cleared to logic 0 a short time after the comparator is enabled or its mode bits have been changed. This Power Up Time is specified in Table 2.7 on page 31.

### SFR Definition 7.1. CPT0CN: Comparator0 Control

| R/W      | R                        | R/W           | R/W      | R/W       | R/W            | R/W          | R/W      | Reset Value  |  |  |  |  |

|----------|--------------------------|---------------|----------|-----------|----------------|--------------|----------|--------------|--|--|--|--|

| CP0EN    | CP0OUT                   | <b>CP0RIF</b> | CP0FIF   | CP0HYP1   | CP0HYP0        | CP0HYN1      | CP0HYN0  | 00000000     |  |  |  |  |

| Bit7     | Bit6                     | Bit5          | Bit4     | Bit3      | Bit2           | Bit1         | Bit0     | SFR Address: |  |  |  |  |

|          |                          |               |          |           |                |              |          |              |  |  |  |  |

|          |                          |               |          |           |                |              |          |              |  |  |  |  |

| Bit7:    | CP0EN: Cor               |               |          |           |                |              |          |              |  |  |  |  |

|          | 0: Comparator0 Disabled. |               |          |           |                |              |          |              |  |  |  |  |

|          | 1: Comparat              |               |          |           |                |              |          |              |  |  |  |  |

| Bit6:    | CPOOUT: Co               | •             | •        | ate Flag. |                |              |          |              |  |  |  |  |

|          | 0: Voltage or            |               |          |           |                |              |          |              |  |  |  |  |

| D.16     | 1: Voltage or            |               |          |           |                |              |          |              |  |  |  |  |

| Bit5:    | CPORIF: Col              | •             |          | •         | ainaa thia fl  | og woo loot  | alaarad  |              |  |  |  |  |

|          | 0: No Comparat           |               |          |           | since this h   | ag was last  | cleared. |              |  |  |  |  |

| Bit4:    | CP0FIF: Cor              | -             | -        |           |                |              |          |              |  |  |  |  |

| Bit4.    | 0: No Compa              |               |          |           | d since this f | lad was last | cleared  |              |  |  |  |  |

|          | 1: Comparat              |               |          |           |                | lag had lad  | cicalcal |              |  |  |  |  |

| Bits3-2: | CP0HYP1-0                |               |          |           | is Control Bi  | ts.          |          |              |  |  |  |  |

|          | 00: Positive             |               |          |           |                |              |          |              |  |  |  |  |

|          | 01: Positive             | Hysteresis    | = 5 mV.  |           |                |              |          |              |  |  |  |  |

|          | 10: Positive             | Hysteresis    | = 10 mV. |           |                |              |          |              |  |  |  |  |

|          | 11: Positive             |               |          |           |                |              |          |              |  |  |  |  |

| Bits1–0: | CP0HYN1-0                |               | •        |           | sis Control E  | Bits.        |          |              |  |  |  |  |

|          | 00: Negative             | •             |          |           |                |              |          |              |  |  |  |  |

|          | 01: Negative             |               |          |           |                |              |          |              |  |  |  |  |

|          | 10: Negative             |               |          |           |                |              |          |              |  |  |  |  |

|          | 11: Negative             | Hysteresis    | = 20 mV. |           |                |              |          |              |  |  |  |  |

|          |                          |               |          |           |                |              |          |              |  |  |  |  |

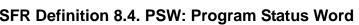

| R/W                     | R/W                                                                                                                                                              | R/W                                                                                                                         | R/W                                                                                                                      | R/W                                                                                                                 | R/W                                                                                                  | R/W                                    | R                                   | Reset Value       |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------------------------|-------------------|

| CY                      | AC                                                                                                                                                               | F0                                                                                                                          | RS1                                                                                                                      | RS0                                                                                                                 | OV                                                                                                   | F1                                     | PARITY                              | 0000000           |

| Bit7                    | Bit6                                                                                                                                                             | Bit5                                                                                                                        | Bit4                                                                                                                     | Bit3                                                                                                                | Bit2                                                                                                 | Bit1                                   | Bit0                                | Bit<br>Addressabl |

|                         |                                                                                                                                                                  |                                                                                                                             |                                                                                                                          |                                                                                                                     |                                                                                                      |                                        | SFR Address                         |                   |

| Bit7:                   | CY: Carry                                                                                                                                                        | Flag.                                                                                                                       |                                                                                                                          |                                                                                                                     |                                                                                                      |                                        |                                     |                   |

|                         |                                                                                                                                                                  | •                                                                                                                           | the last arithmet                                                                                                        | tic operatio                                                                                                        | n resulted i                                                                                         | n a carry (                            | addition) or a                      | a borrow          |

|                         |                                                                                                                                                                  |                                                                                                                             | eared to 0 by all                                                                                                        | other arith                                                                                                         | metic opera                                                                                          | ations.                                |                                     |                   |

| Bit6:                   | AC: Auxilia                                                                                                                                                      |                                                                                                                             |                                                                                                                          |                                                                                                                     |                                                                                                      |                                        |                                     |                   |

|                         |                                                                                                                                                                  |                                                                                                                             | he last arithmeti                                                                                                        |                                                                                                                     |                                                                                                      |                                        |                                     |                   |

|                         |                                                                                                                                                                  |                                                                                                                             | e high order nib                                                                                                         | ble. It is cl                                                                                                       | eared to 0 b                                                                                         | by all other                           | r arithmetic o                      | perations.        |

| Bit5:                   | F0: User F                                                                                                                                                       |                                                                                                                             |                                                                                                                          |                                                                                                                     |                                                                                                      |                                        |                                     |                   |

|                         |                                                                                                                                                                  |                                                                                                                             | able, general pu                                                                                                         | urpose flag                                                                                                         | for use und                                                                                          | der softwa                             | re control.                         |                   |

| Bits4–3:                |                                                                                                                                                                  |                                                                                                                             | Bank Select.                                                                                                             | I                                                                                                                   |                                                                                                      |                                        |                                     |                   |

|                         | I nese bits                                                                                                                                                      | select wr                                                                                                                   | nich register ban                                                                                                        | ik is used o                                                                                                        | uring regist                                                                                         | ter access                             | es.                                 |                   |

|                         |                                                                                                                                                                  | <b>D</b> 00                                                                                                                 |                                                                                                                          |                                                                                                                     |                                                                                                      |                                        |                                     |                   |

|                         |                                                                                                                                                                  |                                                                                                                             | Dogistor Book                                                                                                            | 0 A A A                                                                                                             | 000                                                                                                  |                                        |                                     |                   |

|                         | RS1                                                                                                                                                              | RS0                                                                                                                         | Register Bank                                                                                                            |                                                                                                                     |                                                                                                      |                                        |                                     |                   |

|                         | 0                                                                                                                                                                | 0                                                                                                                           | 0                                                                                                                        | 0x00–0x0                                                                                                            | )7                                                                                                   |                                        |                                     |                   |

|                         | 0<br>0                                                                                                                                                           | 0<br>1                                                                                                                      | 0                                                                                                                        | 0x00–0x0<br>0x08–0x0                                                                                                | )7<br>)F                                                                                             |                                        |                                     |                   |

|                         | 0<br>0<br>1                                                                                                                                                      | 0<br>1<br>0                                                                                                                 | 0<br>1<br>2                                                                                                              | 0x00–0x0<br>0x08–0x0<br>0x10–0x1                                                                                    | )7<br>)F<br>7                                                                                        |                                        |                                     |                   |

|                         | 0<br>0<br>1                                                                                                                                                      | 0<br>1                                                                                                                      | 0                                                                                                                        | 0x00–0x0<br>0x08–0x0                                                                                                | )7<br>)F<br>7                                                                                        |                                        |                                     |                   |

| Bit2:                   | 0<br>0<br>1<br>1                                                                                                                                                 | 0<br>1<br>0<br>1                                                                                                            | 0<br>1<br>2                                                                                                              | 0x00–0x0<br>0x08–0x0<br>0x10–0x1                                                                                    | )7<br>)F<br>7                                                                                        |                                        |                                     |                   |

| Bit2:                   | 0<br>0<br>1<br>1<br>1<br>0 <b>V</b> : Overfl                                                                                                                     | 0<br>1<br>0<br>1<br>ow Flag.                                                                                                | 0<br>1<br>2                                                                                                              | 0x00-0x0<br>0x08-0x0<br>0x10-0x1<br>0x18-0x1                                                                        | )7<br>)F<br>7<br>F                                                                                   |                                        |                                     |                   |

| Bit2:                   | 0<br>0<br>1<br>1<br>0<br>V: Overfl<br>This bit is :                                                                                                              | 0<br>1<br>0<br>1<br>ow Flag.<br>set to 1 ur                                                                                 | 0<br>1<br>2<br>3                                                                                                         | 0x00-0x0<br>0x08-0x0<br>0x10-0x1<br>0x18-0x1                                                                        | 07<br>0F<br>7<br>F<br>ances:                                                                         | nge overflo                            | DW.                                 |                   |

| Bit2:                   | 0<br>0<br>1<br>1<br><b>OV</b> : Overfl<br>This bit is :<br>• An ADD,                                                                                             | 0<br>1<br>0<br>1<br>ow Flag.<br>set to 1 ur<br>ADDC, or                                                                     | 0<br>1<br>2<br>3<br>nder the followin                                                                                    | 0x00-0x0<br>0x08-0x0<br>0x10-0x1<br>0x18-0x1<br>og circumst<br>on causes                                            | 07<br>0F<br>7<br>F<br>F<br>ances:<br>a sign-char                                                     |                                        |                                     |                   |

| Bit2:                   | 0<br>0<br>1<br>1<br><b>OV</b> : Overfil<br>This bit is s<br>• An ADD,<br>• A MUL in<br>• A DIV ins                                                               | 0<br>1<br>0<br>1<br>ow Flag.<br>set to 1 ur<br>ADDC, of<br>struction<br>struction c                                         | 0<br>1<br>2<br>3<br>nder the followin<br>r SUBB instructi<br>results in an ove<br>auses a divide-t                       | 0x00-0x0<br>0x08-0x0<br>0x10-0x1<br>0x18-0x1<br>on causes<br>erflow (resu                                           | 07<br>0F<br>7<br>F<br>ances:<br>a sign-char<br>ult is greate<br>ndition.                             | r than 255                             | ).                                  |                   |

| Bit2:                   | 0<br>0<br>1<br>1<br><b>OV</b> : Overfil<br>This bit is s<br>• An ADD,<br>• A MUL in<br>• A DIV ins                                                               | 0<br>1<br>0<br>1<br>ow Flag.<br>set to 1 ur<br>ADDC, of<br>struction<br>struction c                                         | 0<br>1<br>2<br>3<br>nder the followin<br>r SUBB instructi<br>results in an ove                                           | 0x00-0x0<br>0x08-0x0<br>0x10-0x1<br>0x18-0x1<br>on causes<br>erflow (resu                                           | 07<br>0F<br>7<br>F<br>ances:<br>a sign-char<br>ult is greate<br>ndition.                             | r than 255                             | ).                                  | in all othe       |

|                         | 0<br>0<br>1<br>1<br><b>OV</b> : Overfl<br>This bit is a<br>• An ADD,<br>• A MUL in<br>• A DIV ins<br>The OV bit<br>cases.                                        | 0<br>1<br>0<br>1<br>set to 1 ur<br>ADDC, of<br>struction<br>struction c<br>is cleared                                       | 0<br>1<br>2<br>3<br>nder the followin<br>r SUBB instructi<br>results in an ove<br>auses a divide-t                       | 0x00-0x0<br>0x08-0x0<br>0x10-0x1<br>0x18-0x1<br>on causes<br>erflow (resu                                           | 07<br>0F<br>7<br>F<br>ances:<br>a sign-char<br>ult is greate<br>ndition.                             | r than 255                             | ).                                  | in all othe       |

|                         | 0<br>0<br>1<br>1<br><b>OV</b> : Overfl<br>This bit is a<br>• An ADD,<br>• A MUL in<br>• A DIV ins<br>The OV bit<br>cases.<br><b>F1</b> : User F                  | 0<br>1<br>0<br>1<br>set to 1 ur<br>ADDC, o<br>struction<br>truction c<br>: is cleared<br>lag 1.                             | 0<br>1<br>2<br>3<br>nder the followin<br>r SUBB instructi<br>results in an ove<br>auses a divide-t<br>d to 0 by the AD   | 0x00-0x0<br>0x08-0x0<br>0x10-0x1<br>0x18-0x1<br>on causes<br>erflow (resu<br>by-zero con<br>D, ADDC,                | 07<br>0F<br>7<br>F<br>ances:<br>a sign-char<br>ult is greate<br>ndition.<br>SUBB, MU                 | r than 255<br>L, and DI∖               | ).<br>′ instructions                | in all othe       |

| Bit1:                   | 0<br>0<br>1<br>1<br>1<br>OV: Overfl<br>This bit is s<br>• An ADD,<br>• A MUL in<br>• A DIV ins<br>The OV bit<br>cases.<br>F1: User F<br>This is a b              | 0<br>1<br>0<br>1<br>set to 1 ur<br>ADDC, of<br>struction<br>struction c<br>is cleared<br>lag 1.                             | 0<br>1<br>2<br>3<br>3<br>SUBB instructi<br>results in an ove<br>auses a divide-t<br>d to 0 by the AD<br>able, general pu | 0x00-0x0<br>0x08-0x0<br>0x10-0x1<br>0x18-0x1<br>on causes<br>erflow (resu<br>by-zero con<br>D, ADDC,                | 07<br>0F<br>7<br>F<br>ances:<br>a sign-char<br>ult is greate<br>ndition.<br>SUBB, MU                 | r than 255<br>L, and DI∖               | ).<br>′ instructions                | in all othe       |

| Bit2:<br>Bit1:<br>Bit0: | 0<br>0<br>1<br>1<br>1<br>OV: Overfl<br>This bit is s<br>• An ADD,<br>• A MUL in<br>• A DIV ins<br>The OV bit<br>cases.<br>F1: User F<br>This is a b<br>PARITY: P | 0<br>1<br>0<br>1<br>set to 1 ur<br>ADDC, of<br>struction<br>struction c<br>is cleared<br>lag 1.<br>it-address<br>arity Flag | 0<br>1<br>2<br>3<br>3<br>SUBB instructi<br>results in an ove<br>auses a divide-t<br>d to 0 by the AD<br>able, general pu | 0x00-0x0<br>0x08-0x0<br>0x10-0x1<br>0x18-0x1<br>on causes<br>erflow (resu<br>by-zero con<br>D, ADDC,<br>urpose flag | 07<br>0F<br>7<br>F<br>ances:<br>a sign-char<br>ult is greate<br>ndition.<br>SUBB, MUI<br>for use und | r than 255<br>L, and DI∖<br>der softwa | ).<br>/ instructions<br>re control. |                   |

### **10.5. External Interrupts**

The INTO and INTO external interrupt sources are configurable as active high or low, edge or level sensitive. The INOPL (INTO Polarity) and IN1PL (INTO Polarity) bits in the IT01CF register select active high or active low; the IT0 and IT1 bits in TCON (Section "18.1. Timer 0 and Timer 1" on page 182) select level or edge sensitive. The table below lists the possible configurations.

| IT0 | IN0PL | INT0 Interrupt               |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

| IT1 | IN1PL | INT1 Interrupt               |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

INTO and INTO are assigned to Port pins as defined in the ITO1CF register (see SFR Definition 10.5). Note that INTO and INTO Port pin assignments are independent of any Crossbar assignments. INTO and INTO will monitor their assigned Port pins without disturbing the peripheral that was assigned the Port pin via the Crossbar. To assign a Port pin only to INTO and/or INTO, configure the Crossbar to skip the selected pin(s). This is accomplished by setting the associated bit in register XBRO (see Section "13.1. Priority Crossbar Decoder" on page 122 for complete details on configuring the Crossbar).

In the typical configuration, the external interrupt pins should be skipped in the crossbar and configured as open-drain with the pin latch set to 1. See Section "13. Port Input/Output" on page 120 for more information.

IE0 (TCON.1) and IE1 (TCON.3) serve as the interrupt-pending flags for the INT0 and INT0 external interrupts, respectively. If an INT0 or INT0 external interrupt is configured as edge-sensitive, the corresponding interrupt-pending flag is automatically cleared by the hardware when the CPU vectors to the ISR. When configured as level sensitive, the interrupt-pending flag remains logic 1 while the input is active as defined by the corresponding polarity bit (IN0PL or IN1PL); the flag remains logic 0 while the input is inactive. The external interrupt source must hold the input active until the interrupt request is recognized. It must then deactivate the interrupt request before execution of the ISR completes or another interrupt request will be generated.

### 11.3. External Reset

The external RST pin provides a means for external circuitry to force the device into a reset state. Asserting an active-low signal on the RST pin generates a reset; an external pullup and/or decoupling of the RST pin may be necessary to avoid erroneous noise-induced resets. See Table 2.8 on page 32 for complete RST pin specifications. The PINRSF flag (RSTSRC.0) is set on exit from an external reset.

### **11.4. Missing Clock Detector Reset**

The Missing Clock Detector (MCD) is a one-shot circuit that is triggered by the system clock. If the system clock remains high or low for more than 100  $\mu$ s, the one-shot will time out and generate a reset. After a MCD reset, the MCDRSF flag (RSTSRC.2) will read 1, signifying the MCD as the reset source; otherwise, this bit reads 0. Writing a 1 to the MCDRSF bit enables the Missing Clock Detector; writing a 0 disables it. The state of the RST pin is unaffected by this reset.

### 11.5. Comparator Reset

Comparator0 can be configured as a reset source by writing a 1 to the CORSEF flag (RSTSRC.5). Comparator0 should be enabled and allowed to settle prior to writing to CORSEF to prevent any turn-on chatter on the output from generating an unwanted reset. The Comparator0 reset is active-low: if the non-inverting input voltage (on CP0+) is less than the inverting input voltage (on CP0-), the device is put into the reset state. After a Comparator0 reset, the CORSEF flag (RSTSRC.5) will read 1 signifying Comparator0 as the reset source; otherwise, this bit reads 0. The state of the RST pin is unaffected by this reset.

### 11.6. PCA Watchdog Timer Reset

The programmable Watchdog Timer (WDT) function of the Programmable Counter Array (PCA) can be used to prevent software from running out of control during a system malfunction. The PCA WDT function can be enabled or disabled by software as described in Section "19.3. Watchdog Timer Mode" on page 203; the WDT is enabled and clocked by SYSCLK / 12 following any reset. If a system malfunction prevents user software from updating the WDT, a reset is generated and the WDTRSF bit (RSTSRC.5) is set to 1. The state of the RST pin is unaffected by this reset.

### 11.7. Flash Error Reset

If a Flash read/write/erase or program read targets an illegal address, a system reset is generated. This may occur due to any of the following:

- A Flash write or erase is attempted above user code space. This occurs when PSWE is set to 1 and a MOVX write operation targets an address above the Lock Byte address.

- A Flash read is attempted above user code space. This occurs when a MOVC operation targets an address above the Lock Byte address.

- A program read is attempted above user code space. This occurs when user code attempts to branch to an address above the Lock Byte address.

- A Flash read, write or erase attempt is restricted due to a Flash security setting (see Section "12.4. Security Options" on page 117).

- A Flash write or erase is attempted while the V<sub>DD</sub> Monitor (VDDMON0) is disabled or not set to its high threshold setting.

The FERROR bit (RSTSRC.6) is set following a Flash error reset. The state of the  $\overrightarrow{RST}$  pin is unaffected by this reset.

**Note:** Please refer to Section "20.6. Reset Low Time" on page 212 for restrictions on reset low time in older silicon revisions A and B.

## SFR Definition 11.2. RSTSRC: Reset Source

| R/W      | R                         | R/W          | R/W          | R                          | R/W           | R/W          | R Reset Value                   |

|----------|---------------------------|--------------|--------------|----------------------------|---------------|--------------|---------------------------------|

|          | FERROR                    | CORSEF       | SWRSF        | WDTRSF                     | MCDRSF        | PORSF        | PINRSF Variable                 |

| Bit7     | Bit6                      | Bit5         | Bit4         | Bit3                       | Bit2          | Bit1         | Bit0                            |

|          |                           |              |              |                            |               |              | SFR Address: 0xEF               |

|          |                           |              |              |                            |               |              |                                 |

| Note: So | oftware should            | avoid read   | modify wri   | te instructio              | ns when wri   | ting values  | to RSTSRC.                      |

| Bit7:    | UNUSED. R                 | ead = 1 Wi   | rite = don't | care                       |               |              |                                 |

| Bit6:    | FERROR: F                 |              |              | ouro.                      |               |              |                                 |

|          | 0: Source of              |              |              | lash read/w                | rite/erase er | ror.         |                                 |

|          | 1: Source of              | last reset w | as a Flash   | read/write/                | erase error.  |              |                                 |

| Bit5:    | CORSEF: Co                | •            |              |                            | -             |              |                                 |

|          | 0: <b>Read:</b> So        |              |              | •                          | ator0.        |              |                                 |

|          |                           | mparator0 i  |              |                            | •             |              |                                 |

|          | 1: Read: So               |              |              | comparator<br>ource (activ |               |              |                                 |

| Bit4:    | SWRSF: Sol                | •            |              | · ·                        | e-10w).       |              |                                 |

| DRT.     | 0: <b>Read:</b> So        |              |              | •                          | o the SWRS    | F bit.       |                                 |

|          | Write: No                 |              |              |                            |               |              |                                 |

|          | 1: Read: So               | urce of last | reset was    | a write to th              | e SWRSF bi    | it.          |                                 |

|          |                           | rces a syste |              |                            |               |              |                                 |

| Bit3:    | WDTRSF: W                 |              |              |                            |               |              |                                 |

|          | 0: Source of              |              |              |                            | •             |              |                                 |

| Bit2:    | 1: Source of<br>MCDRSF: M |              |              |                            |               |              |                                 |

| DILZ.    | 0: Read: So               | -            |              | -                          | a Clock Det   | ector time   | tuc                             |

|          |                           | ssing Clock  |              |                            | 9 010011 001  |              | 541.                            |

|          | 1: Read: So               | -            |              |                            | lock Detecto  | or timeout.  |                                 |

|          | Write: Mis                | ssing Clock  | Detector e   | nabled; trig               | gers a reset  | if a missin  | g clock condition is            |

|          | detected.                 |              | _            |                            |               |              |                                 |

| Bit1:    | PORSF: Pov                |              |              |                            | \\/           |              |                                 |

|          |                           |              |              |                            |               |              | es/disables the V <sub>DD</sub> |

|          |                           |              |              |                            | -             |              | efore the V <sub>DD</sub> moni- |

|          | Definition 11             |              | mzeu ma      | y cause a s                | ystem rese    | L See legi   | ster VDDMON (SFR                |

|          | 0: Read: Las              | ,            | not a pow    | er-on or V <sub>D</sub>    | monitor re    | set.         |                                 |

|          |                           |              |              | ) is not a re              | -             |              |                                 |

|          |                           |              |              |                            |               | all other re | eset flags indetermi-           |

|          | nate.                     |              | •            |                            | ,             |              | č                               |

|          | Write: V <sub>D</sub>     | D monitor (  | /DDMON0      | ) is a reset :             | source.       |              |                                 |

| Bit0:    | PINRSF: HV                | V Pin Reset  | Flag.        |                            |               |              |                                 |

|          | 0: Source of              |              |              |                            |               |              |                                 |

|          | 1: Source of              | last reset w | as RST pi    | n.                         |               |              |                                 |

|          |                           |              |              |                            |               |              |                                 |

|          |                           |              |              |                            |               |              |                                 |

|          |                           |              |              |                            |               |              |                                 |

### 12.2. Flash Write and Erase Guidelines

Any system which contains routines which write or erase Flash memory from software involves some risk that the write or erase routines will execute unintentionally if the CPU is operating outside its specified operating range of  $V_{DD}$ , system clock frequency, or temperature. This accidental execution of Flash modi-fying code can result in alteration of Flash memory contents causing a system failure that is only recoverable by re-Flashing the code in the device.

The following guidelines are recommended for any system which contains routines which write or erase Flash from code.

#### 12.2.1. $V_{DD}$ Maintenance and the $V_{DD}$ monitor

- 1. If the system power supply is subject to voltage or current "spikes," add sufficient transient protection devices to the power supply to ensure that the supply voltages listed in the Absolute Maximum Ratings table are not exceeded.

- Make certain that the maximum V<sub>DD</sub> ramp time specification (if applicable) is met. See Section 20.4 on page 211 for more details on V<sub>DD</sub> ramp time. If th<u>e sy</u>stem cannot meet this ramp time specification, then add an external V<sub>DD</sub> brownout circuit to the RST pin of th<u>e</u> device that holds the device in reset until V<sub>DD</sub> reaches the minimum specified V<sub>DD</sub> and re-asserts RST if V<sub>DD</sub> drops belowthat level. V<sub>DD</sub> (min) is specified in Table 2.2 on page 26.

- 3. Enable the on-chip V<sub>DD</sub> monitor (VDDMON0) and enable it as a reset source as early in code as possible. This should be the first set of instructions executed after the Reset Vector. For C-based systems, this will involve modifying the startup code added by the C compiler. See your compiler documentation for more details. Make certain that there are no delays in software between enabling the V<sub>DD</sub> monitor (VDDMON0) and enabling it as a reset source. Code examples showing this can be found in "AN201: Writing to Flash from Firmware", available from the Silicon Laboratories web site.

- 4. As an added precaution, explicitly enable the V<sub>DD</sub> monitor (VDDMON0) and enable the V<sub>DD</sub> monitor as a reset source inside the functions that write and erase Flash memory. The V<sub>DD</sub> monitor enable instructions should be placed just after the instruction to set PSWE to a 1, but before the Flash write or erase operation instruction.

- Make certain that all writes to the RSTSRC (Reset Sources) register use direct assignment operators and explicitly DO NOT use the bit-wise operators (such as AND or OR). For example, "RSTSRC = 0x02" is correct. "RSTSRC |= 0x02" is incorrect.

- 6. Make certain that all writes to the RSTSRC register explicitly set the PORSF bit to a 1. Areas to check are initialization code which enables other reset sources, such as the Missing Clock Detector or Comparator, for example, and instructions which force a Software Reset. A global search on "RSTSRC" can quickly verify this.

#### 12.2.2. PSWE Maintenance

- 1. Reduce the number of places in code where the PSWE bit (PSCTL.0) is set to a 1. There should be exactly one routine in code that sets PSWE to a 1 to write Flash bytes and one routine in code that sets PSWE and PSEE both to a 1 to erase Flash pages.

- Minimize the number of variable accesses while PSWE is set to a 1. Handle pointer address updates and loop variable maintenance outside the "PSWE = 1;... PSWE = 0;" area. Code examples showing this can be found in "AN201: Writing to Flash from Firmware," available from the Silicon Laboratories web site.

- 3. Disable interrupts prior to setting PSWE to a 1 and leave them disabled until after PSWE has been reset to '0'. Any interrupts posted during the Flash write or erase operation will be serviced in priority order after the Flash operation has been completed and interrupts have been re-enabled by software.

- Make certain that the Flash write and erase pointer variables are not located in XRAM. See your compiler documentation for instructions regarding how to explicitly locate variables in different memory areas.

5. Add address bounds checking to the routines that write or erase Flash memory to ensure that a routine called with an illegal address does not result in modification of the Flash.

#### 12.2.3. System Clock

- 1. If operating from an external crystal, be advised that crystal performance is susceptible to electrical interference and is sensitive to layout and to changes in temperature. If the system is operating in an electrically noisy environment, use the internal oscillator or use an external CMOS clock.

- 2. If operating from the external oscillator, switch to the internal oscillator during Flash write or erase operations. The external oscillator can continue to run, and the CPU can switch back to the external oscillator after the Flash operation has completed.

Additional Flash recommendations and example code can be found in application note "AN201: Writing to Flash from Firmware," available from the Silicon Laboratories website.

| SF Signals DFN10 | ΈF       |   | XTAL1 | XTAL2 |   | CNVSTR             |

|------------------|----------|---|-------|-------|---|--------------------|

| PIN I/O          | <u>ч</u> | 1 | 2     | 3     | 4 | <del>້ວ</del><br>5 |

| TX0              |          |   | _     |       |   |                    |

| RX0              |          |   |       |       |   |                    |

| ТХО              | -        |   |       |       |   |                    |

| RX0              |          |   |       |       |   |                    |

| SCK              |          |   |       |       |   |                    |

| MISO             |          |   | ĺ     |       |   |                    |

| MOSI             |          |   |       |       |   |                    |

| NSS*             |          |   |       |       |   |                    |

| LIN-TX           |          |   |       |       |   |                    |

| LIN_RX           |          |   | l     |       |   |                    |

| CP0              |          |   |       |       |   |                    |

| CP0A             |          |   |       |       |   |                    |

| /SYSCLK          |          |   |       |       |   |                    |

| CEX0             |          |   |       |       |   |                    |

| CEX1             |          |   |       |       |   |                    |

| CEX2             |          |   |       |       |   |                    |

| ECI              |          |   |       |       |   |                    |

| Т0               |          |   |       |       |   |                    |

| T1               |          |   |       |       |   |                    |

|                  | 0        | 0 | 0     | 0     | 0 | 0                  |

Note: 4-Wire SPI Only.

### Figure 13.5. Crossbar Priority Decoder with No Pins Skipped (DFN 10)

## SFR Definition 13.2. XBR1: Port I/O Crossbar Register 1

| R/W      | R/W                                                                                  | R/W                  | R/W         | R/W       | R/W      | R/W  | R/W         | Reset Value |  |  |  |  |

|----------|--------------------------------------------------------------------------------------|----------------------|-------------|-----------|----------|------|-------------|-------------|--|--|--|--|

| WEAKPL   | JD XBARE                                                                             | T1E                  | TOE         | ECIE      | Reserved | PC   | AOME        | 00000000    |  |  |  |  |

| Bit7     | Bit6                                                                                 | Bit5                 | Bit4        | Bit3      | Bit2     | Bit1 | Bit0        |             |  |  |  |  |

|          |                                                                                      |                      |             |           |          |      | SFR Address | :: 0xE2     |  |  |  |  |

|          |                                                                                      |                      |             |           |          |      |             |             |  |  |  |  |

| Bit7:    | WEAKPUD:                                                                             |                      |             |           |          |      |             |             |  |  |  |  |

|          | 0: Weak Pullups enabled (except for Ports whose I/O are configured as analog input). |                      |             |           |          |      |             |             |  |  |  |  |

| 5.40     | 1: Weak Pullups disabled.                                                            |                      |             |           |          |      |             |             |  |  |  |  |

| Bit6:    | XBARE: Crossbar Enable.                                                              |                      |             |           |          |      |             |             |  |  |  |  |

|          | 0: Crossbar o<br>1: Crossbar e                                                       |                      |             |           |          |      |             |             |  |  |  |  |

| Bit5:    | <b>T1E</b> : T1 Enal                                                                 |                      |             |           |          |      |             |             |  |  |  |  |

| DILJ.    | 0: T1 unavail                                                                        |                      | t nin       |           |          |      |             |             |  |  |  |  |

|          | 1: T1 routed                                                                         |                      | , pin       |           |          |      |             |             |  |  |  |  |

| Bit4:    | TOE: TO Enal                                                                         | •                    |             |           |          |      |             |             |  |  |  |  |

|          | 0: T0 unavail                                                                        | able at Por          | t pin.      |           |          |      |             |             |  |  |  |  |

|          | 1: T0 routed                                                                         | to Port pin.         | •           |           |          |      |             |             |  |  |  |  |

| Bit3:    | ECIE: PCA0                                                                           | External Co          | ounter Inpu | t Enable  |          |      |             |             |  |  |  |  |

|          | 0: ECI unava                                                                         | ilable at Po         | rt pin.     |           |          |      |             |             |  |  |  |  |

|          | 1: ECI routed                                                                        |                      |             |           |          |      |             |             |  |  |  |  |

| Bit2:    | Reserved. M                                                                          |                      | ~ .         |           |          |      |             |             |  |  |  |  |

| Bits1–0: | PCA0ME: PC                                                                           |                      |             |           |          |      |             |             |  |  |  |  |

|          | 00: All PCA I                                                                        |                      |             | pins.     |          |      |             |             |  |  |  |  |

|          | 01: CEX0 rou                                                                         |                      |             | •         |          |      |             |             |  |  |  |  |

|          | 10: CEX0, CI<br>11: CEX0, CI                                                         |                      |             |           |          |      |             |             |  |  |  |  |

|          |                                                                                      | $_{\Lambda 1}, OLAZ$ |             | ort pins. |          |      |             |             |  |  |  |  |

|          |                                                                                      |                      |             |           |          |      |             |             |  |  |  |  |

### 13.3. General Purpose Port I/O

Port pins that remain unassigned by the Crossbar and are not used by analog peripherals can be used for general purpose I/O. Ports P0–P1 are accessed through corresponding special function registers (SFRs) that are both byte addressable and bit addressable. When writing to a Port, the value written to the SFR is latched to maintain the output data value at each pin. When reading, the logic levels of the Port's input pins are returned regardless of the XBRn settings (i.e., even when the pin is assigned to another signal by the Crossbar, the Port register can always read its corresponding Port I/O pin). The exception to this is the execution of the read-modify-write instructions that target a Port Latch register as the destination. The read-modify-write instructions when operating on a Port SFR are the following: ANL, ORL, XRL, JBC, CPL, INC, DEC, DJNZ and MOV, CLR or SETB, when the destination is an individual bit in a Port SFR. For these instructions, the value of the latch register (not the pin) is read, modified, and written back to the SFR.

#### 14.1.1. Internal Oscillator Suspend Mode

When software writes a logic 1 to SUSPEND (OSCICN.5), the internal oscillator is suspended. If the system clock is derived from the internal oscillator, the input clock to the peripheral or CIP-51 will be stopped until one of the following events occur:

- Port 0 Match Event.

- Port 1 Match Event.

- Comparator 0 enabled and output is logic 0.

When one of the internal oscillator awakening events occur, the internal oscillator, CIP-51, and affected peripherals resume normal operation, regardless of whether the event also causes an interrupt. The CPU resumes execution at the instruction following the write to SUSPEND.

**Note:** Please refer to Section "20.7. Internal Oscillator Suspend Mode" on page 212 for a note about suspend mode in older silicon revisions.

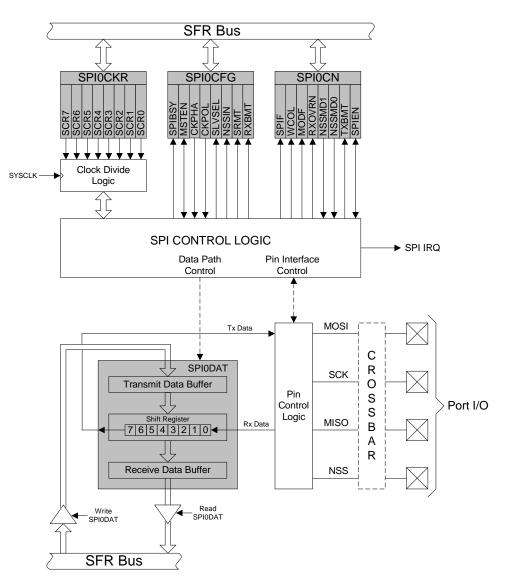

## 16. Enhanced Serial Peripheral Interface (SPI0)

The Serial Peripheral Interface (SPI0) provides access to a flexible, full-duplex synchronous serial bus. SPI0 can operate as a master or slave device in both 3-wire or 4-wire modes, and supports multiple masters and slaves on a single SPI bus. The slave-select (NSS) signal can be configured as an input to select SPI0 in slave mode, or to disable Master Mode operation in a multi-master environment, avoiding contention on the SPI bus when more than one master attempts simultaneous data transfers. NSS can also be configured as a chip-select output in master mode, or disabled for 3-wire operation. Additional general purpose port I/O pins can be used to select multiple slave devices in master mode.

## 17.3. LIN Master Mode Operation

The master node is responsible for the scheduling of messages and sends the header of each frame, containing the SYNCH BREAK FIELD, SYNCH FIELD and IDENTIFIER FIELD. The steps to schedule a message transmission or reception are listed below.

- 1. Load the 6-bit Identifier into the LIN0ID register.

- Load the data length into the LINOSIZE register. Set the value to the number of data bytes or "1111b" if the data length should be decoded from the identifier. Also, set the checksum type, classic or enhanced, in the same LINOSIZE register.

- 3. Set the data direction by setting the TXRX bit (LIN0CTRL.5). Set the bit to 1 to perform a master transmit operation, or set the bit to 0 to perform a master receive operation.

- 4. If performing a master transmit operation, load the data bytes to transmit into the data buffer (LIN0DT1 to LIN0DT8).

- Set the STREQ bit (LIN0CTRL.0) to start the message transfer. The LIN peripheral will schedule the message frame and request an interrupt if the message transfer is successfully completed or if an error has occurred.

This code segment shows the procedure to schedule a message in a transmission operation:

```

LINADDR = 0x08;// Point to LIN0CTRL

LINDATA |= 0x20;// Select to transmit data

LINADDR = 0x0E;// Point to LIN0ID

LINDATA = 0x11;// Load the ID, in this example 0x11

LINADDR = 0x0B;// Point to LIN0SIZE

LINDATA = ( LINDATA & 0xF0 ) | 0x08; // Load the size with 8

LINADDR = 0x00;// Point to Data buffer first byte

for (i=0; i<8; i++)

{

LINDATA = i + 0x41;// Load the buffer with `A', `B', ...

LINADDR++;// Increment the address to the next buffer

}

LINADDR = 0x08;// Point to LIN0CTRL

LINDATA = 0x01;// Start Request

```

The application should perform the following steps when an interrupt is requested.

- 1. Check the DONE bit (LIN0ST.0) and the ERROR bit (LIN0ST.2).

- 2. If performing a master receive operation and the transfer was successful, read the received data from the data buffer.

- 3. If the transfer was not successful, check the error register to determine the kind of error. Further error handling has to be done by the application.

- 4. Set the RSTINT (LIN0CTRL.3) and RSTERR bits (LIN0CTRL.2) to reset the interrupt request and the error flags.

### **19.2. Capture/Compare Modules**

Each module can be configured to operate independently in one of six operation modes: Edge-triggered Capture, Software Timer, High Speed Output, Frequency Output, 8-Bit Pulse Width Modulator, or 16-Bit Pulse Width Modulator. Each module has Special Function Registers (SFRs) associated with it in the CIP-51 system controller. These registers are used to exchange data with a module and configure the module's mode of operation.

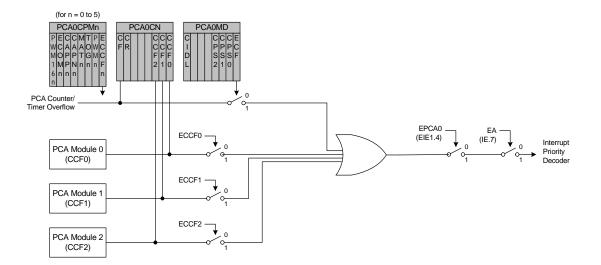

Table 19.2 summarizes the bit settings in the PCA0CPMn registers used to select the PCA capture/compare module's operating modes. Setting the ECCFn bit in a PCA0CPMn register enables the module's CCFn interrupt. Note that PCA0 interrupts must be globally enabled before individual CCFn interrupts are recognized. PCA0 interrupts are globally enabled by setting the EA bit and the EPCA0 bit to logic 1. See Figure 19.3 for details on the PCA interrupt configuration.

| PWM16    | ECOM   | CAPP | CAPN | MAT | TOG | PWM | ECCF | Operation Mode                             |

|----------|--------|------|------|-----|-----|-----|------|--------------------------------------------|

| Х        | Х      | 1    | 0    | 0   | 0   | 0   | Х    | Capture triggered by positive edge on CEXn |

| Х        | Х      | 0    | 1    | 0   | 0   | 0   | Х    | Capture triggered by negative edge on CEXn |

| Х        | Х      | 1    | 1    | 0   | 0   | 0   | Х    | Capture triggered by transition on<br>CEXn |

| Х        | 1      | 0    | 0    | 1   | 0   | 0   | Х    | Software Timer                             |

| Х        | 1      | 0    | 0    | 1   | 1   | 0   | Х    | High Speed Output                          |

| Х        | 1      | 0    | 0    | Х   | 1   | 1   | Х    | Frequency Output                           |

| 0        | 1      | 0    | 0    | Х   | 0   | 1   | Х    | 8-Bit Pulse Width Modulator                |

| 1        | 1      | 0    | 0    | Х   | 0   | 1   | Х    | 16-Bit Pulse Width Modulator               |

| X = Don' | t Care | •    |      |     |     | •   | •    |                                            |

Table 19.2. PCA0CPM Register Settings for PCA Capture/Compare Modules

Figure 19.3. PCA Interrupt Block Diagram

### **19.4. Register Descriptions for PCA**

Following are detailed descriptions of the special function registers related to the operation of the PCA.

## SFR Definition 19.1. PCA0CN: PCA Control

| 544               | DAM                         | DAV          | 5444        | 544            | D 444       | 544            |             | <b>D</b> (1)(1)    |

|-------------------|-----------------------------|--------------|-------------|----------------|-------------|----------------|-------------|--------------------|

| R/W               | R/W                         | R/W          | R/W         | R/W            | R/W         | R/W            | R/W         | Reset Value        |

| CF                | CR                          | Reserved     | Reserved    | Reserved       | CCF2        | CCF1           | CCF0        | 0000000            |

| Bit7              | Bit6                        | Bit5         | Bit4        | Bit3           | Bit2        | Bit1           | Bit0        | Bit<br>Addressable |

|                   |                             |              |             |                |             |                | SFR Address | s: 0xD8            |

| Bit7:             | CF: PCA Co                  | ounter/Timer | Overflow F  | lag.           |             |                |             |                    |

|                   | Set by hardv                | ware when t  | he PCA Co   | unter/Timer    | overflows f | rom 0xFFF      | F to 0x0000 | ). When the        |

|                   | Counter/Tim                 |              | · · ·       |                |             |                |             |                    |

|                   | to the PCA i                | •            |             | e. This bit is | not automa  | atically clear | red by hard | ware and           |

|                   | must be clea                | 2            |             |                |             |                |             |                    |

| Bit6:             | CR: PCA Co                  |              |             | -              |             |                |             |                    |

|                   | This bit enab               |              |             | Counter/Tim    | er.         |                |             |                    |

|                   | 0: PCA Cou                  |              |             |                |             |                |             |                    |

|                   | 1: PCA Cou                  | nter/Timer e | nabled.     |                |             |                |             |                    |

| Bits5–3:<br>Bit2: | Reserved.                   |              | antura/Can  | anara Flag     |             |                |             |                    |

| DILZ.             | CCF2: PCA<br>This bit is se |              | •           |                | oturo occu  | re Whon th     | o CCE2 int  | orrupt is          |

|                   | enabled, set                |              |             |                |             |                |             |                    |

|                   | bit is not aut              |              |             |                |             |                |             | Juline. This       |

| Bit1:             | CCF1: PCA                   |              |             |                |             |                | Jonano.     |                    |

|                   | This bit is se              |              |             |                | oture occui | rs. When th    | e CCF1 inte | errupt is          |

|                   | enabled, set                | •            |             |                |             |                |             | •                  |

|                   | bit is not aut              | omatically c | leared by h | ardware and    | d must be o | cleared by s   | software.   |                    |

| Bit0:             | CCF0: PCA                   | Module 0 C   | apture/Con  | npare Flag.    |             |                |             |                    |

|                   | This bit is se              | et by hardwa | are when a  | match or ca    | pture occui | rs. When th    | e CCF0 inte | errupt is          |

|                   | enabled, set                | •            |             |                |             |                |             | outine. This       |