Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                  |

|----------------------------|------------------------------------------------------------------|

| Product Status             | Active                                                           |

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | SPI, UART/USART                                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT               |

| Number of I/O              | 6                                                                |

| Program Memory Size        | 4KB (4K x 8)                                                     |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 256 x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.25V                                                       |

| Data Converters            | A/D 6x12b                                                        |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                               |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 10-VFDFN Exposed Pad                                             |

| Supplier Device Package    | 10-DFN (3x3)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f524-c-im |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table 2.8. Reset Electrical Characteristics**

-40 to +125 °C unless otherwise specified.

| Parameter                                              | Conditions                                                                                 | Min                         | Тур                     | Мах                         | Units                |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------|-------------------------|-----------------------------|----------------------|

| RST Output Low Voltage                                 | I <sub>OL</sub> = 8.5 mA, V <sub>DD</sub> =<br>2.1 V                                       | _                           | _                       | 0.8                         | V                    |

| RST Input High Voltage                                 |                                                                                            | 0.7 x<br>V <sub>REGIN</sub> |                         | _                           | V                    |

| RST Input Low Voltage                                  |                                                                                            |                             |                         | 0.3 x<br>V <sub>REGIN</sub> | V                    |

| RST Input Pullup Impedance                             | $V_{REGIN} = 1.8 V$<br>$V_{REGIN} = 2.7 V$<br>$V_{REGIN} = 3.3 V$<br>$V_{REGIN} = 5 V$     |                             | 330<br>160<br>130<br>80 |                             | kΩ<br>kΩ<br>kΩ<br>kΩ |

| Missing Clock Detector Timeout                         | Time from last system<br>clock rising edge to reset<br>initiation                          | 100                         | 350                     | 650                         | μs                   |

| Reset Time Delay (T <sub>PORDelay</sub> ) <sup>1</sup> | Delay between release<br>of any reset source and<br>code execution at loca-<br>tion 0x0000 |                             |                         | 350                         | μs                   |

| Minimum RST Low Time to Generate a System Reset        |                                                                                            | 10                          | _                       | _                           | μs                   |

| V <sub>DD</sub> Monitor (VDDMON0)                      |                                                                                            |                             |                         | •                           |                      |

| Low Threshold (V <sub>RST-LOW</sub> ) <sup>1,2,3</sup> | C8051F52x/53x<br>C8051F52xA/53xA<br>C8051F52x-C/53x-C                                      | 1.8<br>1.65<br>1.65         | 1.9<br>1.75<br>1.75     | 2.0<br>1.8<br>1.8           | V<br>V<br>V          |

| High Threshold (V <sub>RST-HIGH</sub> ) <sup>3</sup>   | C8051F52x/53x<br>C8051F52xA/53xA<br>C8051F52x-C/53x-C                                      | 2.1<br>2.25<br>2.25         | 2.2<br>2.3<br>2.3       | 2.3<br>2.4<br>2.45          | V<br>V<br>V          |

| Turn-on Time                                           |                                                                                            | _                           | 83                      |                             | μs                   |

| Supply Current                                         | V <sub>DD</sub> = 2.1 V                                                                    | _                           | 1                       | 2                           | μA                   |

| Level-Sensitive V <sub>DD</sub> Monitor (VDDMC         | <b>DN1)</b> <sup>1</sup>                                                                   | -                           |                         | •                           |                      |

| Threshold (V <sub>RST1</sub> ) <sup>1,2,3</sup>        | C8051F52x-C/53x-C                                                                          | 1.6                         | 1.75                    | 1.9                         | V                    |

| Supply Current                                         | C8051F52x-C/53x-C                                                                          |                             | 3                       | 6                           | μA                   |

| Notes:<br>1. Refer to Section "20. Device Specific     | Behavior" on page 210.                                                                     |                             |                         |                             |                      |

- Refer to Section "20. Device Specific Behavior" on page 210.

The POR threshold (V<sub>RST</sub>) is V<sub>RST-LOW</sub> or V<sub>RST1</sub>, whichever is higher.

The V<sub>RST</sub> threshold for power fail / brownout is the higher of VDDMON0 and VDDMON1 thresholds, if both are enabled.

# C8051F52x/F52xA/F53x/F53xA

| Name         | Pin Numbers       |           | Туре             | Description                                                                                                                                                                                                                           |

|--------------|-------------------|-----------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | 'F52xA<br>'F52x-C | 'F52x     |                  |                                                                                                                                                                                                                                       |

| P0.3/TX*/    | —                 | 8         | D I/O or<br>A In | Port 0.3. See Port I/O Section for a complete description.                                                                                                                                                                            |

| XTAL2        |                   |           | D I/O            | External Clock Output. For an external crystal or resonator, this pin is the excitation driver. This pin is the external clock input for CMOS, capacitor, or RC oscillator configurations. See Section "14. Oscillators" on page 135. |

| P0.2         | 9                 | 9         | D I/O or         | Port 0.2. See Port I/O Section for a complete description.                                                                                                                                                                            |

| XTAL1        |                   |           | A In             | External Clock Input. This pin is the external oscillator return for a crystal or resonator. Section "14. Oscillators" on page 135.                                                                                                   |

| P0.1/        | 10                | 10        | D I/O or<br>A In | Port 0.1. See Port I/O Section for a complete description.                                                                                                                                                                            |

|              |                   |           |                  |                                                                                                                                                                                                                                       |

| C2D          |                   |           | D I/O            | Bi-directional data signal for the C2 Debug Interface                                                                                                                                                                                 |

| lote: Please | refer to Se       | ection "2 | 20. Device S     | I<br>Specific Behavior" on page 210.                                                                                                                                                                                                  |

## Table 3.1. Pin Definitions for the C8051F52x and C8051F52xA (DFN 10) (Continued)

### 4.3.5. Output Conversion Code

The registers ADC0H and ADC0L contain the high and low bytes of the output conversion code. When the repeat count is set to 1, conversion codes are represented in 12-bit unsigned integer format and the output conversion code is updated after each conversion. Inputs are measured from 0 to  $V_{REF} \times 4095/4096$ . Data can be right-justified or left-justified, depending on the setting of the AD0LJST bit (ADC0CN.2). Unused bits in the ADC0H and ADC0L registers are set to 0. Example codes are shown below for both right-justified and left-justified data.

| Input Voltage                | Right-Justified ADC0H:ADC0L<br>(AD0LJST = 0) | Left-Justified ADC0H:ADC0L<br>(AD0LJST = 1) |

|------------------------------|----------------------------------------------|---------------------------------------------|

| V <sub>REF</sub> x 4095/4096 | 0x0FFF                                       | 0xFFF0                                      |

| V <sub>REF</sub> x 2048/4096 | 0x0800                                       | 0x8000                                      |

| V <sub>REF</sub> x 2047/4096 | 0x07FF                                       | 0x7FF0                                      |

| 0                            | 0x0000                                       | 0x0000                                      |

When the ADC0 Repeat Count is greater than 1, the output conversion code represents the accumulated result of the conversions performed and is updated after the last conversion in the series is finished. Sets of 4, 8, or 16 consecutive samples can be accumulated and represented in unsigned integer format. The repeat count can be selected using the AD0RPT bits in the ADC0CF register. The value must be right-justified (AD0LJST = "0"), and unused bits in the ADC0H and ADC0L registers are set to '0'. The following example shows right-justified codes for repeat counts greater than 1. Notice that accumulating  $2^n$  samples is equivalent to left-shifting by *n* bit positions when all samples returned from the ADC have the same value.

| Input Voltage                | Repeat Count = 4 | Repeat Count = 8 | Repeat Count = 16 |

|------------------------------|------------------|------------------|-------------------|

| V <sub>REF</sub> x 4095/4096 | 0x3FFC           | 0x7FF8           | 0xFFF0            |

| V <sub>REF</sub> x 2048/4096 | 0x2000           | 0x4000           | 0x8000            |

| V <sub>REF</sub> x 2047/4096 | 0x1FFC           | 0x3FF8           | 0x7FF0            |

| 0                            | 0x0000           | 0x0000           | 0x0000            |

# SFR Definition 4.5. ADC0CF: ADC0 Configuration

| R/W        | R/W             | R/W                        | R/W         | R/W           | R/W                  | R/W                 | R/W            | Reset Value  |

|------------|-----------------|----------------------------|-------------|---------------|----------------------|---------------------|----------------|--------------|

|            |                 | AD0SC                      |             |               | AD0                  | RPT                 | GAINEN         | 11111000     |

| Bit7       | Bit6            | Bit5                       | Bit4        | Bit3          | Bit2                 | Bit1                | Bit0           | SFR Address: |

|            |                 |                            |             |               |                      |                     |                | 0xBC         |

|            |                 |                            |             |               |                      |                     |                |              |

| Bits7-3:   | AD0SC4-0:       | ADC0 SAR                   | Conversio   | on Clock Per  | iod Bits.            |                     |                |              |

|            | SAR Conver      | sion clock is              | derived fr  | om FCLK by    | the followir         | ng equation         | , where AD     | 0SC refers   |

|            | to the 5-bit v  |                            |             |               |                      | • •                 |                |              |

|            | Table 2.3 on    | page 28.                   |             |               |                      |                     |                | 0            |

|            | BURSTEN =       |                            | the curren  | it system clo | ock.                 |                     |                |              |

|            | BURSTEN =       |                            |             | •             |                      | ed in Table         | 2.3.           |              |

|            |                 |                            |             |               | •                    |                     |                |              |

|            | ADOSC =         | $\frac{FCLK}{CLK_{SAR}}$ - | ·1* c       | or <i>CLK</i> | $SAR = \frac{1}{AD}$ | $\frac{CLR}{OCC+1}$ |                |              |

|            |                 | CLK <sub>SAR</sub>         |             |               | AD                   | 03C + 1             |                |              |

| Note: Roun | d the result up |                            |             |               |                      |                     |                |              |

|            | ·               |                            |             |               |                      |                     |                |              |

| Bits2–1:   | AD0RPT1-0       | ): ADC0 Rep                | eat Count   | t.            |                      |                     |                |              |

|            | Controls the    | number of c                | onversion   | s taken and   | accumulate           | ed between          | ADC0 End       | of           |

|            | Conversion      | (ADCINT) ar                | nd ADC0 V   | Vindow Con    | nparator (AD         | DCWINT) ir          | nterrupts. A   | convert      |

|            | start is requi  |                            |             |               |                      |                     |                |              |

|            | convert start   | can initiate               | multiple se | elf-timed cor | versions. R          | Results in be       | oth modes a    | are          |

|            | accumulated     | d in the ADC               | 0H:ADC0I    | _ register. W | hen AD0RI            | PT1-0 are           | set to a va    | lue other    |

|            | than '00', th   | e AD0LJST                  | bit in the  | ADC0CN r      | egister mus          | st be set to        | o '0' (right j | ustified).   |

|            | 00: 1 conver    | sion is perfo              | rmed.       |               |                      |                     |                | -            |

|            | 01: 4 conver    | sions are pe               | rformed a   | nd accumul    | ated.                |                     |                |              |

|            | 10: 8 conver    | sions are pe               | rformed a   | nd accumul    | ated.                |                     |                |              |

|            | 11: 16 conve    | ersions are p              | erformed    | and accumu    | lated.               |                     |                |              |

|            |                 | -                          |             |               |                      |                     |                |              |

| Bit0:      | GAINEN: Ga      | ain Enable B               | it.         |               |                      |                     |                |              |

|            | Controls the    | gain progra                | mming. Fo   | or more infor | mation of th         | ne usage, re        | efer to the f  | ollowing     |

|            | chapter: Sec    | ction "4.4. Se             | electable G | Gain" on pag  | e 60.                |                     |                |              |

|            |                 |                            |             |               |                      |                     |                |              |

## Table 9.2. Special Function Registers

| Register | Address | Description                                        | Page |

|----------|---------|----------------------------------------------------|------|

| ACC      | 0xE0    | Accumulator                                        | 89   |

| ADC0CF   | 0xBC    | ADC0 Configuration                                 | 65   |

| ADC0CN   | 0xE8    | ADC0 Control                                       | 67   |

| ADC0H    | 0xBE    | ADC0                                               | 66   |

| ADC0L    | 0xBD    | ADC0                                               | 66   |

| ADC0GTH  | 0xC4    | ADC0 Greater-Than Data High Byte                   | 69   |

| ADC0GTL  | 0xC3    | ADC0 Greater-Than Data Low Byte                    | 69   |

| ADC0LTH  | 0xC6    | ADC0 Less-Than Data High Byte                      | 70   |

| ADC0LTL  | 0xC5    | ADC0 Less-Than Data Low Byte                       | 70   |

| ADC0MX   | 0xBB    | ADC0 Channel Select                                | 64   |

| ADC0TK   | 0xBA    | ADC0 Tracking Mode Select                          | 68   |

| В        | 0xF0    | B Register                                         | 89   |

| CKCON    | 0x8E    | Clock Control                                      | 188  |

| CLKSEL   | 0xA9    | Clock Select                                       | 143  |

| CPT0CN   | 0x9B    | Comparator0 Control                                | 78   |

| CPT0MD   | 0x9D    | Comparator0 Mode Selection                         | 80   |

| CPT0MX   | 0x9F    | Comparator0 MUX Selection                          | 79   |

| DPH      | 0x83    | Data Pointer High                                  | 87   |

| DPL      | 0x82    | Data Pointer Low                                   | 87   |

| EIE1     | 0xE6    | Extended Interrupt Enable 1                        | 102  |

| EIP1     | 0xF6    | Extended Interrupt Priority 1                      | 103  |

| FLKEY    | 0xB7    | Flash Lock and Key                                 | 119  |

| IE       | 0xA8    | Interrupt Enable                                   | 100  |

| IP       | 0xB8    | Interrupt Priority                                 | 101  |

| IT01CF   | 0xE4    | INT0/INT1 Configuration                            | 105  |

| LINADDR  | 0x92    | LIN indirect address pointer                       | 172  |

| LINCF    | 0x95    | LIN master-slave and automatic baud rate selection | 173  |

| LINDATA  | 0x93    | LIN indirect data buffer                           | 172  |

| OSCICL   | 0xB3    | Internal Oscillator Calibration                    | 138  |

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

## 12.2. Flash Write and Erase Guidelines

Any system which contains routines which write or erase Flash memory from software involves some risk that the write or erase routines will execute unintentionally if the CPU is operating outside its specified operating range of  $V_{DD}$ , system clock frequency, or temperature. This accidental execution of Flash modi-fying code can result in alteration of Flash memory contents causing a system failure that is only recoverable by re-Flashing the code in the device.

The following guidelines are recommended for any system which contains routines which write or erase Flash from code.

#### 12.2.1. $V_{DD}$ Maintenance and the $V_{DD}$ monitor

- 1. If the system power supply is subject to voltage or current "spikes," add sufficient transient protection devices to the power supply to ensure that the supply voltages listed in the Absolute Maximum Ratings table are not exceeded.

- Make certain that the maximum V<sub>DD</sub> ramp time specification (if applicable) is met. See Section 20.4 on page 211 for more details on V<sub>DD</sub> ramp time. If th<u>e sy</u>stem cannot meet this ramp time specification, then add an external V<sub>DD</sub> brownout circuit to the RST pin of th<u>e</u> device that holds the device in reset until V<sub>DD</sub> reaches the minimum specified V<sub>DD</sub> and re-asserts RST if V<sub>DD</sub> drops belowthat level. V<sub>DD</sub> (min) is specified in Table 2.2 on page 26.

- 3. Enable the on-chip V<sub>DD</sub> monitor (VDDMON0) and enable it as a reset source as early in code as possible. This should be the first set of instructions executed after the Reset Vector. For C-based systems, this will involve modifying the startup code added by the C compiler. See your compiler documentation for more details. Make certain that there are no delays in software between enabling the V<sub>DD</sub> monitor (VDDMON0) and enabling it as a reset source. Code examples showing this can be found in "AN201: Writing to Flash from Firmware", available from the Silicon Laboratories web site.

- 4. As an added precaution, explicitly enable the V<sub>DD</sub> monitor (VDDMON0) and enable the V<sub>DD</sub> monitor as a reset source inside the functions that write and erase Flash memory. The V<sub>DD</sub> monitor enable instructions should be placed just after the instruction to set PSWE to a 1, but before the Flash write or erase operation instruction.

- Make certain that all writes to the RSTSRC (Reset Sources) register use direct assignment operators and explicitly DO NOT use the bit-wise operators (such as AND or OR). For example, "RSTSRC = 0x02" is correct. "RSTSRC |= 0x02" is incorrect.

- 6. Make certain that all writes to the RSTSRC register explicitly set the PORSF bit to a 1. Areas to check are initialization code which enables other reset sources, such as the Missing Clock Detector or Comparator, for example, and instructions which force a Software Reset. A global search on "RSTSRC" can quickly verify this.

#### 12.2.2. PSWE Maintenance

- 1. Reduce the number of places in code where the PSWE bit (PSCTL.0) is set to a 1. There should be exactly one routine in code that sets PSWE to a 1 to write Flash bytes and one routine in code that sets PSWE and PSEE both to a 1 to erase Flash pages.

- Minimize the number of variable accesses while PSWE is set to a 1. Handle pointer address updates and loop variable maintenance outside the "PSWE = 1;... PSWE = 0;" area. Code examples showing this can be found in "AN201: Writing to Flash from Firmware," available from the Silicon Laboratories web site.

- 3. Disable interrupts prior to setting PSWE to a 1 and leave them disabled until after PSWE has been reset to '0'. Any interrupts posted during the Flash write or erase operation will be serviced in priority order after the Flash operation has been completed and interrupts have been re-enabled by software.

- Make certain that the Flash write and erase pointer variables are not located in XRAM. See your compiler documentation for instructions regarding how to explicitly locate variables in different memory areas.

# 13. Port Input/Output

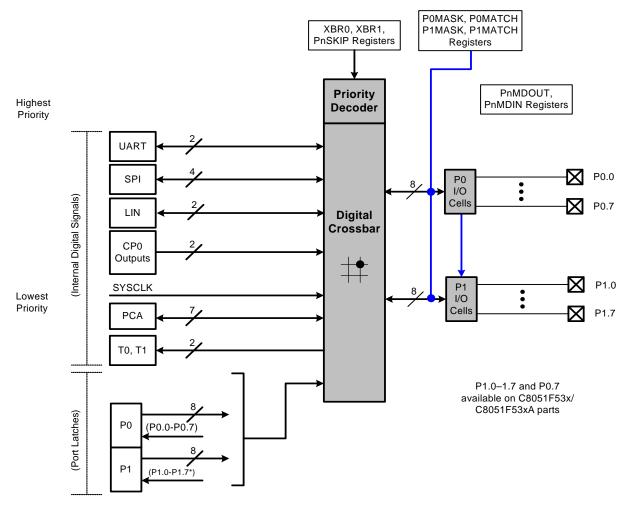

Digital and analog resources are available through up to 16 I/O pins. Port pins are organized as two or one byte-wide Ports. Each of the Port pins can be defined as general-purpose I/O (GPIO) or analog input/out-put; Port pins P0.0 - P2.7 can be assigned to one of the internal digital resources as shown in Figure 13.3. The designer has complete control over which functions are assigned, limited only by the number of physical I/O pins. This resource assignment flexibility is achieved through the use of a Priority Crossbar Decoder. Note that the state of a Port I/O pin can always be read in the corresponding Port latch, regardless of the Crossbar settings.

The Crossbar assigns the selected internal digital resources to the I/O pins based on the peripheral priority order of the Priority Decoder (Figure 13.3 and Figure 13.4). The registers XBR0 and XBR1, defined in SFR Definition 13.1 and SFR Definition 13.2, are used to select internal digital functions.

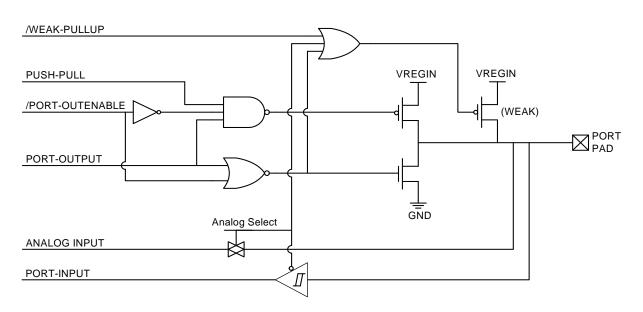

Port I/O pins are 5.25 V tolerant over the operating range of  $V_{REGIN}$ . Figure 13.2 shows the Port cell circuit. The Port I/O cells are configured as either push-pull or open-drain in the Port Output Mode registers (PnMDOUT, where n = 0,1). Complete Electrical Specifications for Port I/O are given in Table 2.10 on page 33.

Figure 13.1. Port I/O Functional Block Diagram

# C8051F52x/F52xA/F53x/F53xA

Figure 13.2. Port I/O Cell Block Diagram

# SFR Definition 13.2. XBR1: Port I/O Crossbar Register 1

| R/W      | R/W                         | R/W          | R/W         | R/W         | R/W           | R/W       | R/W           | Reset Value |

|----------|-----------------------------|--------------|-------------|-------------|---------------|-----------|---------------|-------------|

| WEAKP    | JD XBARE                    | T1E          | T0E         | ECIE        | Reserved      | PC        | A0ME          | 00000000    |

| Bit7     | Bit6                        | Bit5         | Bit4        | Bit3        | Bit2          | Bit1      | Bit0          |             |

|          |                             |              |             |             |               |           | SFR Address   | : 0xE2      |

|          |                             |              |             |             |               |           |               |             |

| Bit7:    | WEAKPUD                     |              |             |             |               |           |               |             |

|          |                             | •            | · ·         | or Ports wh | ose I/O are c | onfigured | d as analog i | nput).      |

| -        | 1: Weak Pul                 |              |             |             |               |           |               |             |

| Bit6:    | XBARE: Cro                  |              | le.         |             |               |           |               |             |

|          | 0: Crossbar                 |              |             |             |               |           |               |             |

| D:45     | 1: Crossbar                 |              |             |             |               |           |               |             |

| Bit5:    | <b>T1E</b> : T1 Ena         |              | t nin       |             |               |           |               |             |

|          | 0: T1 unava<br>1: T1 routed |              | t pin.      |             |               |           |               |             |

| Bit4:    | <b>TOE</b> : TO Ena         |              |             |             |               |           |               |             |

| DIL4.    | 0: T0 unava                 |              | t nin       |             |               |           |               |             |

|          | 1: T0 routed                |              |             |             |               |           |               |             |

| Bit3:    | ECIE: PCAC                  |              |             | it Enable   |               |           |               |             |

| 2.110.   | 0: ECI unava                |              |             |             |               |           |               |             |

|          | 1: ECI route                |              | •           |             |               |           |               |             |

| Bit2:    | Reserved.                   | •            |             |             |               |           |               |             |

| Bits1-0: | PCA0ME: P                   | CA Module    | I/O Enable  | Bits.       |               |           |               |             |

|          | 00: All PCA                 | I/O unavaila | ble at Port | pins.       |               |           |               |             |

|          | 01: CEX0 ro                 | uted to Port | pin.        | •           |               |           |               |             |

|          | 10: CEX0, C                 | EX1 routed   | to Port pin | s.          |               |           |               |             |

|          | 11: CEX0, C                 | EX1, CEX2    | routed to F | Port pins.  |               |           |               |             |

|          |                             |              |             |             |               |           |               |             |

|          |                             |              |             |             |               |           |               |             |

## 13.3. General Purpose Port I/O

Port pins that remain unassigned by the Crossbar and are not used by analog peripherals can be used for general purpose I/O. Ports P0–P1 are accessed through corresponding special function registers (SFRs) that are both byte addressable and bit addressable. When writing to a Port, the value written to the SFR is latched to maintain the output data value at each pin. When reading, the logic levels of the Port's input pins are returned regardless of the XBRn settings (i.e., even when the pin is assigned to another signal by the Crossbar, the Port register can always read its corresponding Port I/O pin). The exception to this is the execution of the read-modify-write instructions that target a Port Latch register as the destination. The read-modify-write instructions when operating on a Port SFR are the following: ANL, ORL, XRL, JBC, CPL, INC, DEC, DJNZ and MOV, CLR or SETB, when the destination is an individual bit in a Port SFR. For these instructions, the value of the latch register (not the pin) is read, modified, and written back to the SFR.

# SFR Definition 14.1. OSCICN: Internal Oscillator Control

| R/W      | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W                             | R                         | R                         | R/W                      | R/W       | R/W          | Reset Value |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------|---------------------------|--------------------------|-----------|--------------|-------------|--|--|

| IOSCEN   | 1 IOSCEN0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SUSPEND                         | IFRDY                     |                           | IFCN2                    | IFCN1     | IFCN0        | 11000000    |  |  |

| Bit7     | Bit6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Bit5                            | Bit4                      | Bit3                      | Bit2                     | Bit1      | Bit0         |             |  |  |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                 |                           |                           |                          |           | SFR Address: | 0xB2        |  |  |

| Bits7–6: | IOSCEN[1:0<br>00: Oscillato<br>01: Reserve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | r Disabled.<br>d.               | scillator Er              | nable Bits.               |                          |           |              |             |  |  |

|          | 10: Reserve<br>11: Oscillato                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 | Normal M                  | ode and Die               | sabled in Si             | uspond Mc | odo          |             |  |  |

| Bit5:    | Setting this b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Internal Osci<br>pit to logic 1 | llator Susp<br>places the | end Enable                | e Bit.<br>cillator in Sl | USPEND r  | node. The in |             |  |  |

| Bit4:    | IFRDY: Inter<br>0: Internal O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | nal Oscillato                   | r Frequenc                | cy Ready Fl<br>at program | ag.<br>med freque        | ncy.      | 0            |             |  |  |

| Bit3:    | UNUSED. R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ead = 0b, W                     | rite = don't              | care.                     |                          |           |              |             |  |  |

| Bits2–0: | UNUSED. Read = 0b, Write = don't care.<br>IFCN2-0: Internal Oscillator Frequency Control Bits.<br>000: SYSCLK derived from Internal Oscillator divided by 128 (default).<br>001: SYSCLK derived from Internal Oscillator divided by 64.<br>010: SYSCLK derived from Internal Oscillator divided by 32.<br>011: SYSCLK derived from Internal Oscillator divided by 16.<br>100: SYSCLK derived from Internal Oscillator divided by 8.<br>101: SYSCLK derived from Internal Oscillator divided by 4.<br>110: SYSCLK derived from Internal Oscillator divided by 4.<br>110: SYSCLK derived from Internal Oscillator divided by 2.<br>111: SYSCLK derived from Internal Oscillator divided by 1. |                                 |                           |                           |                          |           |              |             |  |  |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                 |                           |                           |                          |           |              |             |  |  |

# C8051F52x/F52xA/F53x/F53xA

# SFR Definition 14.4. OSCXCN: External Oscillator Control

| R        | R/W                                                                                                                                                                                                                                                                                                                                              | R/W                                              | R/W                          | R/W                  | R/W                  | R/W     | R/W            | Reset Value |  |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------|----------------------|----------------------|---------|----------------|-------------|--|--|--|--|

| XTLVLD   |                                                                                                                                                                                                                                                                                                                                                  | XOSCMD1 X                                        |                              | eserved              | XFCN2                | XFCN1   | XFCN0          | 00000000    |  |  |  |  |

| Bit7     | Bit6                                                                                                                                                                                                                                                                                                                                             | Bit5                                             | Bit4                         | Bit3                 | Bit2                 | Bit1    | Bit0           |             |  |  |  |  |

|          |                                                                                                                                                                                                                                                                                                                                                  |                                                  |                              |                      |                      |         | SFR Address    | :: 0xB1     |  |  |  |  |

| Bit7:    | <ul> <li>XTLVLD: Crystal Oscillator Valid Flag. (Read only when XOSCMD = 11x.)</li> <li>0: Crystal Oscillator is unused or not yet stable.</li> <li>1: Crystal Oscillator is running and stable.</li> <li>-4: XOSCMD2-0: External Oscillator Mode Bits.</li> </ul>                                                                               |                                                  |                              |                      |                      |         |                |             |  |  |  |  |

| Bits6–4: |                                                                                                                                                                                                                                                                                                                                                  |                                                  |                              | de Bits.             |                      |         |                |             |  |  |  |  |

| B:42     | <ul> <li>00x: External Oscillator circuit off.</li> <li>010: External CMOS Clock Mode.</li> <li>011: External CMOS Clock Mode with divide by 2 stage.</li> <li>100: RC Oscillator Mode.</li> <li>101: Capacitor Oscillator Mode.</li> <li>110: Crystal Oscillator Mode.</li> <li>111: Crystal Oscillator Mode with divide by 2 stage.</li> </ul> |                                                  |                              |                      |                      |         |                |             |  |  |  |  |

| Bita:    |                                                                                                                                                                                                                                                                                                                                                  | P. Read = 0b;                                    |                              |                      | al Dita              |         |                |             |  |  |  |  |

| Bits2–0: |                                                                                                                                                                                                                                                                                                                                                  | External Oscil<br>e table below                  | •                            | ncy Contr            | ol Bits.             |         |                |             |  |  |  |  |

|          | XFCN                                                                                                                                                                                                                                                                                                                                             | Crystal (XC                                      | <b>SCMD</b> = 11             | x) RC                | (XOSCMD              | = 10x)  | C (XOSCM       | /ID = 10x)  |  |  |  |  |

|          | 000                                                                                                                                                                                                                                                                                                                                              | f ≤ 2                                            | 20 kHz                       |                      | f ≤ 25 kH            | lz      | K Factor       | r = 0.87    |  |  |  |  |

|          | 001                                                                                                                                                                                                                                                                                                                                              | 20 kHz <                                         | < f ≤ 58 kHz                 | 25                   | kHz < f ≤ 5          | 50 kHz  | K Facto        | or = 2.6    |  |  |  |  |

|          | 010                                                                                                                                                                                                                                                                                                                                              | 58 kHz <                                         | $f \le 155 \text{ kHz}$      | 50 I                 | 50 kHz < f ≤ 100 kHz |         | K Facto        | or = 7.7    |  |  |  |  |

|          | 011                                                                                                                                                                                                                                                                                                                                              | 155 kHz <                                        | < f ≤ 415 kHz                | 100                  | $kHz < f \le 2$      | 200 kHz | K Factor = 22  |             |  |  |  |  |

|          | 100                                                                                                                                                                                                                                                                                                                                              | 415 kHz <                                        | : f ≤ 1.1 MHz                | 200                  | kHz < f ≤ 4          | l00 kHz | K Facto        | or = 65     |  |  |  |  |

|          | 101                                                                                                                                                                                                                                                                                                                                              | 1.1 MHz <                                        | < f ≤ 3.1 MHz                | 400                  | $kHz < f \le 8$      | 800 kHz | K Factor = 180 |             |  |  |  |  |

|          | 110                                                                                                                                                                                                                                                                                                                                              | 3.1 MHz <                                        | < f ≤ 8.2 MHz                | 800                  | $kHz < f \le 1$      | .6 MHz  | K Factor = 664 |             |  |  |  |  |

|          | 111                                                                                                                                                                                                                                                                                                                                              | 8.2 MHz «                                        | < f ≤ 25 MHz                 | 1.6                  | ИHz < f ≤ З          | 3.2 MHz | K Factor       | = 1590      |  |  |  |  |

| -        | Choose XFC<br>(Circuit from                                                                                                                                                                                                                                                                                                                      | from Figure 1<br>CN value to m<br>n Figure 14.1, | natch crystal<br>Option 2; X | or resona<br>OSCMD = | tor freque<br>= 10x) | ncy.    |                |             |  |  |  |  |

|          | _                                                                                                                                                                                                                                                                                                                                                | CN value to m                                    | •                            | ncy range            | :                    |         |                |             |  |  |  |  |

|          | •                                                                                                                                                                                                                                                                                                                                                | )/(R x C), w                                     |                              |                      |                      |         |                |             |  |  |  |  |

|          |                                                                                                                                                                                                                                                                                                                                                  | y of clock in N<br>or value in pF                |                              |                      |                      |         |                |             |  |  |  |  |

|          | •                                                                                                                                                                                                                                                                                                                                                | esistor value                                    |                              |                      |                      |         |                |             |  |  |  |  |

| C Mode ( | Circuit from I                                                                                                                                                                                                                                                                                                                                   | -igure 14.1, C                                   | Option 3; XO                 |                      | ,                    |         |                |             |  |  |  |  |

|          |                                                                                                                                                                                                                                                                                                                                                  | actor (KF) for                                   |                              | on freque            | ncy desire           | d:      |                |             |  |  |  |  |

|          |                                                                                                                                                                                                                                                                                                                                                  | x V <sub>DD</sub> ), where<br>y of clock in N    |                              |                      |                      |         |                |             |  |  |  |  |

|          |                                                                                                                                                                                                                                                                                                                                                  | or value the X                                   |                              | ρF                   |                      |         |                |             |  |  |  |  |

|          | •                                                                                                                                                                                                                                                                                                                                                | r Supply on N                                    |                              | F                    |                      |         |                |             |  |  |  |  |

|          |                                                                                                                                                                                                                                                                                                                                                  | -                                                |                              |                      |                      |         |                |             |  |  |  |  |

## **15.2. Operational Modes**

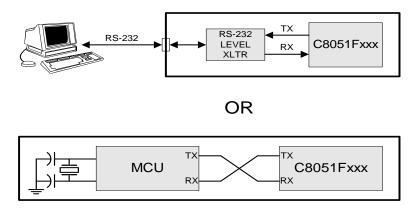

UART0 provides standard asynchronous, full duplex communication. The UART mode (8-bit or 9-bit) is selected by the S0MODE bit (SCON0.7). Typical UART connection options are shown below.

Figure 15.3. UART Interconnect Diagram

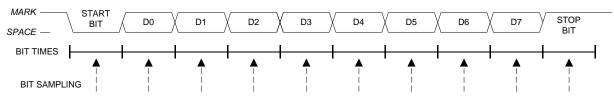

### 15.2.1. 8-Bit UART

8-Bit UART mode uses a total of 10 bits per data byte: one start bit, eight data bits (LSB first), and one stop bit. Data are transmitted LSB first from the TX0 pin and received at the RX0 pin. On receive, the eight data bits are stored in SBUF0 and the stop bit goes into RB80 (SCON0.2).

Data transmission begins when software writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to logic 1. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: RI0 must be logic 0, and if MCE0 is logic 1, the stop bit must be logic 1. In the event of a receive data overrun, the first received 8 bits are latched into the SBUF0 receive register and the following overrun data bits are lost.

If these conditions are met, the eight bits of data is stored in SBUF0, the stop bit is stored in RB80 and the RI0 flag is set. If these conditions are not met, SBUF0 and RB80 will not be loaded and the RI0 flag will not be set. An interrupt will occur if enabled when either TI0 or RI0 is set.

Figure 15.4. 8-Bit UART Timing Diagram

The shift register contents are locked after the slave detects the first edge of SCK. Writes to SPI0DAT that occur after the first SCK edge will be held in the TX latch until the end of the current transfer.

When configured as a slave, SPI0 can be configured for 4-wire or 3-wire operation. The default, 4-wire slave mode, is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 1. In 4-wire mode, the NSS signal is routed to a port pin and configured as a digital input. SPI0 is enabled when NSS is logic 0, and disabled when NSS is logic 1. The bit counter is reset on a falling edge of NSS. Note that the NSS signal must be driven low at least 2 system clocks before the first active edge of SCK for each byte transfer. Figure 16.4 shows a connection diagram between two slave devices in 4-wire slave mode and a master device.

3-wire slave mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. NSS is not used in this mode, and is not mapped to an external port pin through the crossbar. Since there is not a way of uniquely addressing the device in 3-wire slave mode, SPI0 must be the only slave device present on the bus. It is important to note that in 3-wire slave mode there is no external means of resetting the bit counter that determines when a full byte has been received. The bit counter can only be reset by disabling and re-enabling SPI0 with the SPIEN bit. Figure 16.3 shows a connection diagram between a slave device in 3-wire slave mode and a master device.

## 16.4. SPI0 Interrupt Sources

When SPI0 interrupts are enabled, the following four flags will generate an interrupt when they are set to logic 1:

Note that all of the following interrupt bits must be cleared by software.

- 1. The SPI Interrupt Flag, SPIF (SPI0CN.7) is set to logic 1 at the end of each byte transfer. This flag can occur in all SPI0 modes.

- 2. The Write Collision Flag, WCOL (SPI0CN.6) is set to logic 1 if a write to SPI0DAT is attempted when the transmit buffer has not been emptied to the SPI shift register. When this occurs, the write to SPI0DAT will be ignored, and the transmit buffer will not be written. This flag can occur in all SPI0 modes.

- 3. The Mode Fault Flag MODF (SPI0CN.5) is set to logic 1 when SPI0 is configured as a master in multimaster mode and the NSS pin is pulled low. When a Mode Fault occurs, the MSTEN and SPIEN bits in SPI0CN are set to logic 0 to disable SPI0 and allow another master device to access the bus.

- 4. The Receive Overrun Flag RXOVRN (SPI0CN.4) is set to logic 1 when configured as a slave, and a transfer is completed while the receive buffer still holds an unread byte from a previous transfer. The new byte is not transferred to the receive buffer, allowing the previously received data byte to be read. The data byte which caused the overrun is lost.

# SFR Definition 16.3. SPI0CKR: SPI0 Clock Rate

| 544        | <b>D</b> 444  | 5 444                         | 5 444                    | D 444        | 544         | D 444       | D 444               |             |

|------------|---------------|-------------------------------|--------------------------|--------------|-------------|-------------|---------------------|-------------|

| R/W        | R/W           | R/W                           | R/W                      | R/W          | R/W         | R/W         | R/W                 | Reset Value |

| SCR7       | SCR6          | SCR5                          | SCR4                     | SCR3         | SCR2        | SCR1        | SCR0                | 00000000    |

| Bit7       | Bit6          | Bit5                          | Bit4                     | Bit3         | Bit2        | Bit1        | Bit0<br>SFR Address | 0v A 2      |

|            |               |                               |                          |              |             |             | SFR Address         | S. UXAZ     |

| Bits7–0: S | SCR7-SCR      | 0: SPI0 Clo                   | ck Rate.                 |              |             |             |                     |             |

|            | These bits d  |                               |                          | of the SCk   | Coutput whe | en the SPI0 | module is           | configured  |

|            | or master m   |                               |                          |              |             |             |                     | •           |

|            | clock, and is |                               |                          |              |             |             |                     |             |

| a          | and SPI0CK    | R is the 8-b                  | oit value hel            | d in the SPI | 0CKR regis  | ster.       |                     |             |

|            |               |                               |                          |              |             |             |                     |             |

|            |               |                               |                          |              |             |             |                     |             |

|            | £             | S                             | YSCLK                    |              |             |             |                     |             |

|            | JSCK          | $-\frac{1}{2 \times (SH)}$    | $\frac{YSCLK}{PI0CKR +}$ | 1)           |             |             |                     |             |

|            |               | × ×                           |                          | ,            |             |             |                     |             |

|            |               |                               |                          |              |             |             |                     |             |

|            |               |                               |                          |              |             |             |                     |             |

| f          | or 0 <= SPI   | )CKR <= 2                     | 55                       |              |             |             |                     |             |

|            |               |                               |                          |              |             |             |                     |             |

| Example: I | f SYSCLK =    | 2 MHz and                     | d SPI0CKR                | = 0x04,      |             |             |                     |             |

|            |               |                               |                          |              |             |             |                     |             |

|            |               |                               |                          |              |             |             |                     |             |

|            | C             | 200000                        | 00                       |              |             |             |                     |             |

|            | $f_{SCK}$ =   | $=\frac{200000}{2\times(4+)}$ | 1)                       |              |             |             |                     |             |

|            |               |                               | -)                       |              |             |             |                     |             |

|            |               |                               |                          |              |             |             |                     |             |

|            |               |                               |                          |              |             |             |                     |             |

|            | $f_{SCV} =$   | 200 <i>kHz</i>                |                          |              |             |             |                     |             |

|            | JOLV          |                               |                          |              |             |             |                     |             |

|            |               |                               |                          |              |             |             |                     |             |

|            |               |                               |                          |              |             |             |                     |             |

|            |               |                               |                          |              |             |             |                     |             |

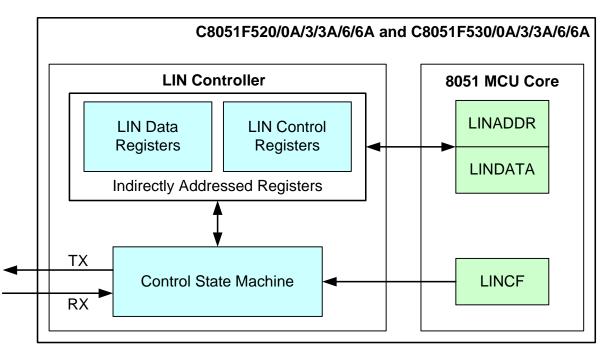

# 17. LIN (C8051F520/0A/3/3A/6/6A and C8051F530/0A/3/3A/6/6A)

**Important Note:** This chapter assumes an understanding of the Local Interconnect Network (LIN) protocol. For more information about the LIN protocol, including specifications, please refer to the LIN consortium (http://www.lin-subbus.org/).

LIN is an asynchronous, serial communications interface used primarily in automotive networks. The Silicon Laboratories LIN controller is compliant to the 2.1 Specification, implements a complete hardware LIN interface, and includes the following features:

- Selectable Master and Slave modes.

- Automatic baud rate option in slave mode

- The internal oscillator is accurate to within 0.5% of 24.5 MHz across the entire temperature range and for VDD voltages greater than or equal to the minimum output of the on-chip voltage regulator, so an external oscillator is not necessary for master mode operation for most systems.

Note: The minimum system clock (SYSCLK) required when using the LIN peripheral is 8 MHz.

Figure 17.1. LIN Block Diagram

The LIN peripheral has four main components:

- 1. LIN Access Registers—Provide the interface between the MCU core and the LIN peripheral.

- 2. LIN Data Registers—Where transmitted and received message data bytes are stored.

- 3. LIN Control Registers—Control the functionality of the LIN interface.

- 4. Control State Machine and Bit Streaming Logic—Contains the hardware that serializes messages and controls the bus timing of the controller.

## 17.4. LIN Slave Mode Operation

When the device is configured for slave mode operation, it must wait for a command from a master node. Access from the firmware to data buffer and ID registers of the LIN peripheral is only possible when a data request is pending (DTREQ bit (LIN0ST.4) is 1) and also when the LIN bus is not active (ACTIVE bit (LIN0ST.7) is set to 0).

The LIN peripheral in slave mode detects the header of the message frame sent by the LIN master. If slave synchronization is enabled (autobaud), the slave synchronizes its internal bit time to the master bit time.

The LIN peripheral configured for slave mode will generated an interrupt in one of three situations:

- 1. After the reception of the IDENTIFIER FIELD.

- 2. When an error is detected.

- 3. When the message transfer is completed.

The application should perform the following steps when an interrupt is detected:

- 1. Check the status of the DTREQ bit (LIN0ST.4). This bit is set when the IDENTIFIER FIELD has been received.

- 2. If DTREQ (LIN0ST.4) is set, read the identifier from LIN0ID and process it. If DTREQ (LIN0ST.4) is not set, continue to step 7.

- 3. Set the TXRX bit (LIN0CTRL.5) to 1 if the current frame is a transmit operation for the slave and set to 0 if the current frame is a receive operation for the slave.

- 4. Load the data length into LIN0SIZE.

- 5. For a slave transmit operation, load the data to transmit into the data buffer.

- 6. Set the DTACK bit (LIN0CTRL.4). Continue to step 10.

- 7. If DTREQ (LIN0ST.4) is not set, check the DONE bit (LIN0ST.0). The transmission was successful if the DONE bit is set.

- 8. If the transmission was successful and the current frame was a receive operation for the slave, load the received data bytes from the data buffer.

- 9. If the transmission was not successful, check LIN0ERR to determine the nature of the error. Further error handling has to be done by the application.

- 10.Set the RSTINT (LIN0CTRL.3) and RSTERR bits (LIN0CTRL.2) to reset the interrupt request and the error flags.

In addition to these steps, the application should be aware of the following:

- 1. If the current frame is a transmit operation for the slave, steps 1 through 5 must be completed during the IN-FRAME RESPONSE SPACE. If it is not completed in time, a timeout will be detected by the master.

- 2. If the current frame is a receive operation for the slave, steps 1 through 5 have to be finished until the reception of the first byte after the IDENTIFIER FIELD. Otherwise, the internal receive buffer of the LIN peripheral will be overwritten and a timeout error will be detected in the LIN peripheral.

- 3. The LIN module does not directly support LIN Version 1.3 Extended Frames. If the application detects an unknown identifier (e.g. extended identifier), it has to write a 1 to the STOP bit (LINOCTRL.7) instead of setting the DTACK (LINOCTRL.4) bit. At that time, steps 2 through 5 can then be skipped. In this situation, the LIN peripheral stops the processing of the LIN communication until the next SYNC BREAK is received.

- 4. Changing the configuration of the checksum during a transaction will cause the interface to reset and the transaction to be lost. To prevent this, the checksum should not be configured while a transaction is

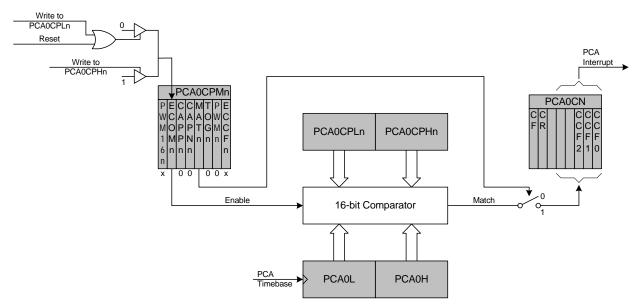

### 19.2.2. Software Timer (Compare) Mode

In Software Timer mode, the PCA counter/timer value is compared to the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1 and an interrupt request is generated if CCF interrupts are enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Setting the ECOMn and MATn bits in the PCA0CPMn register enables Software Timer mode.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Figure 19.5. PCA Software Timer Mode Diagram

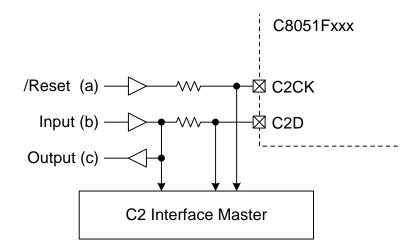

# 21.2. C2 Pin Sharing

The C2 protocol allows the C2 pins to be shared with user functions so that in-system debugging and Flash programming functions may be performed. This is possible because C2 communication is typically performed when the device is in the halt state, where all on-chip peripherals and user software are stalled. In this halted state, the C2 interface can safely 'borrow' the C2CK (/RST) and C2D (P0.1 or P0.6) pins. In most applications, external resistors are required to isolate C2 interface traffic from the user application. A typical isolation configuration is shown in Figure 21.1.

Figure 21.1. Typical C2 Pin Sharing

The configuration in Figure 21.1 assumes the following:

- 1. The user input (b) cannot change state while the target device is halted.

- 2. The /RST pin on the target device is used as an input only.

Additional resistors may be necessary depending on the specific application.

## Revision 1.2 to 1.3

- Updated "System Overview" on page 13 with a voltage range specification for the internal oscillator.

- Updated Table 2.11 on page 34 with new conditions for the internal oscillator accuracy. The internal

oscillator accuracy is dependent on the operating voltage range.

- Updated Section 2 to remove the internal oscillator curve across temperature diagram.

- Updated Figure "4.5 12-Bit ADC Burst Mode Example with Repeat Count Set to 4" on page 58 with new timing diagram when using CNVSTR pin.

- Updated SFR Definition 5.1 (REF0CN) with oscillator suspend requirement for ZTCEN.

- Updated SFR Definition 6.1 (REG0CN) with a new definition for Bit 6. The bit 6 reset value is 1b and must be written to 1b.

- Updated Section "8.3.3. Suspend Mode" on page 90 with note regarding ZTCEN.

- Updated Section "17. LIN (C8051F520/0A/3/3A/6/6A and C8051F530/0A/3/3A/6/6A)" on page 164 with a voltage range specification for the internal oscillator.

## Revision 1.3 to 1.4

- Added 'AEC-Q100' qualification information on page 1.

- Changed page headers throughout the document from 'C8051F52x/F52xA/F53x/F53xA' to 'C8051F52x/53x'.

- Updated supply voltage to "2.0 to 5.25 V" on page 1 and in Section 1 on page 13.

- Corrected reference to development kit (C8051F530DK) in Section "1.2.4. On-Chip Debug Circuitry" on page 18.

- Updated minimum Supply Input Voltage (V<sub>REGIN</sub>) for C8051F52x-C/F53x-C devices in Table 2.2 on page 26 and Table 2.6 on page 30.

- Updated digital supply current (I<sub>DD</sub> and Idle I<sub>DD</sub>) typical values for condition 'Clock = 25 MHz' in Table 2.2 on page 26.