Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                   |

|----------------------------|-------------------------------------------------------------------|

| Product Status             | Active                                                            |

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | LINbus, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                |

| Number of I/O              | 6                                                                 |

| Program Memory Size        | 2KB (2K x 8)                                                      |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 256 x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.25V                                                        |

| Data Converters            | A/D 6x12b                                                         |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 10-VFDFN Exposed Pad                                              |

| Supplier Device Package    | 10-DFN (3x3)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f526-c-imr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1. | System Overview                                                                  |    |

|----|----------------------------------------------------------------------------------|----|

|    | 1.1. Ordering Information                                                        | 14 |

|    | 1.2. CIP-51 <sup>™</sup> Microcontroller                                         | 18 |

|    | 1.2.1. Fully 8051 Compatible Instruction Set                                     | 18 |

|    | 1.2.2. Improved Throughput                                                       | 18 |

|    | 1.2.3. Additional Features                                                       | 18 |

|    | 1.2.4. On-Chip Debug Circuitry                                                   | 18 |

|    | 1.3. On-Chip Memory                                                              | 20 |

|    | 1.4. Operating Modes                                                             |    |

|    | 1.5. 12-Bit Analog to Digital Converter                                          | 22 |

|    | 1.6. Programmable Comparator                                                     | 23 |

|    | 1.7. Voltage Regulator                                                           | 23 |

|    | 1.8. Serial Port                                                                 | 23 |

|    | 1.9. Port Input/Output                                                           |    |

| 2. | Electrical Characteristics                                                       |    |

|    | 2.1. Absolute Maximum Ratings                                                    | 25 |

|    | 2.2. Electrical Characteristics                                                  |    |

|    | Pinout and Package Definitions                                                   |    |

| 4. | 12-Bit ADC (ADC0)                                                                |    |

|    | 4.1. Analog Multiplexer                                                          |    |

|    | 4.2. Temperature Sensor                                                          |    |

|    | 4.3. ADC0 Operation                                                              |    |

|    | 4.3.1. Starting a Conversion                                                     |    |

|    | 4.3.2. Tracking Modes                                                            |    |

|    | 4.3.3. Timing                                                                    |    |

|    | 4.3.4. Burst Mode                                                                |    |

|    | 4.3.5. Output Conversion Code                                                    |    |

|    | 4.3.6. Settling Time Requirements                                                |    |

|    | 4.4. Selectable Gain                                                             |    |

|    | 4.4.1. Calculating the Gain Value                                                |    |

|    | 4.4.2. Setting the Gain Value                                                    |    |

|    | 4.5. Programmable Window Detector                                                |    |

| _  | 4.5.1. Window Detector In Single-Ended Mode                                      |    |

| 5. | Voltage Reference                                                                | 72 |

|    | Voltage Regulator (REG0)                                                         |    |

|    | Comparator                                                                       |    |

| 8. | CIP-51 Microcontroller                                                           |    |

|    | 8.1. Instruction Set.                                                            |    |

|    | 8.1.1. Instruction and CPU Timing                                                |    |

|    | 8.1.2. MOVX Instruction and Program Memory                                       |    |

|    | <ul><li>8.2. Register Descriptions</li><li>8.3. Power Management Modes</li></ul> | 00 |

|    |                                                                                  |    |

|    | 8.3.1. Idle Mode                                                                 | 90 |

# 1.5. 12-Bit Analog to Digital Converter

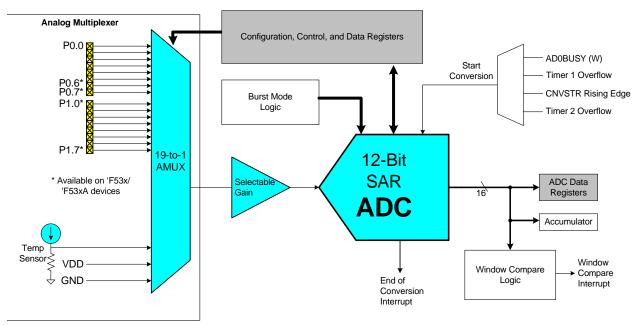

The C8051F52x/F52xA/F53x/F53xA devices include an on-chip 12-bit SAR ADC with a maximum throughput of 200 ksps. The ADC system includes a configurable analog multiplexer that selects the positive ADC input, which is measured with respect to GND. Ports 0 and 1 are available as ADC inputs; additionally, the ADC includes an innovative programmable gain stage which allows the ADC to sample inputs sources greater than the VREF voltage. The on-chip Temperature Sensor output and the core supply voltage (V<sub>DD</sub>) are also available as ADC inputs. User firmware may shut down the ADC or use it in Burst Mode to save power.

Conversions can be initiated in four ways: a software command, an overflow of Timer 1, an overflow of Timer 2, or an external convert start signal. This flexibility allows the start of conversion to be triggered by software events, a periodic signal (timer overflows), or external HW signals. Conversion completions are indicated by a status bit and an interrupt (if enabled) and occur after 1, 4, 8, or 16 samples have been accumulated by a hardware accumulator. The resulting 12-bit to 16-bit data word is latched into the ADC data SFRs upon completion of a conversion. When the system clock is slow, Burst Mode allows ADC0 to automatically wake from a low power shutdown state, acquire and accumulate samples, then re-enter the low power shutdown state without CPU intervention.

Window compare registers for the ADC data can be configured to interrupt the controller when ADC data is either within or outside of a specified range. The ADC can monitor a key voltage continuously in background mode, but not interrupt the controller unless the converted data is within/outside the specified range.

Figure 1.7. 12-Bit ADC Block Diagram

### Table 2.2. Global DC Electrical Characteristics

-40 to +125 °C, 25 MHz System Clock unless otherwise specified. Typical values are given at 25 °C

| Parameter                                                 | Conditions                                          | Min     | Тур    | Max | Units  |

|-----------------------------------------------------------|-----------------------------------------------------|---------|--------|-----|--------|

| Digital Supply Current—CPU Inactive (Id                   | le Mode, not fetching instructio                    | ns from | Flash) |     |        |

| Idle I <sub>DD</sub> <sup>3,4</sup>                       | V <sub>DD</sub> = 2.1 V:                            |         |        |     |        |

|                                                           | Clock = 32 kHz                                      | —       | 8      | —   | μA     |

|                                                           | Clock = 200 kHz                                     | —       | 22     | —   | μA     |

|                                                           | Clock = 1 MHz                                       | —       | 0.09   | —   | mA     |

|                                                           | Clock = 25 MHz                                      | —       | 2.2    | 5   | mA     |

|                                                           | V <sub>DD</sub> = 2.6 V:                            |         |        |     |        |

|                                                           | Clock = 32 kHz                                      | —       | 9      | —   | μA     |

|                                                           | Clock = 200 kHz                                     | _       | 30     | _   | μA     |

|                                                           | Clock = 1 MHz                                       | _       | 0.13   | _   | mA     |

|                                                           | Clock = 25 MHz                                      | —       | 3      | 6.5 | mA     |

| Idle I <sub>DD</sub> Frequency Sensitivity <sup>3,6</sup> | T = 25 °C:                                          |         |        |     |        |

|                                                           | V <sub>DD</sub> = 2.1 V, F <u>&lt;</u> 1 MHz        | —       | 90     | —   | µA/MHz |

|                                                           | $V_{DD} = 2.1 \text{ V}, \text{ F} > 1 \text{ MHz}$ | —       | 90     | —   | µA/MHz |

|                                                           | $V_{DD} = 2.6 V, F \le 1 MHz$                       | —       | 118    | —   | µA/MHz |

|                                                           | $V_{DD} = 2.6 \text{ V}, \text{ F} > 1 \text{ MHz}$ | —       | 118    | —   | µA/MHz |

| Disital Curshy Current <sup>3</sup>                       |                                                     |         |        |     |        |

| Digital Supply Current <sup>3</sup>                       | Oscillator not running,                             |         |        |     |        |

| (Stop or Suspend Mode)                                    | V <sub>DD</sub> Monitor Disabled.                   |         | _      |     |        |

|                                                           | T = 25 °C                                           | —       | 2      | —   | μA     |

|                                                           | T = 60 °C                                           | —       | 3      | —   | μA     |

|                                                           | T = 125 °C                                          | —       | 50     | _   | μA     |

#### Notes:

- 1. For more information on  $V_{\mbox{REGIN}}$  characteristics, see Table 2.6 on page 30.

- **2.** SYSCLK must be at least 32 kHz to enable debugging.

- **3.** Based on device characterization data; Not production tested.

- 4. Does not include internal oscillator or internal regulator supply current.

- 5. I<sub>DD</sub> can be estimated for frequencies <= 12 MHz by multiplying the frequency of interest by the frequency sensitivity number for that range. When using these numbers to estimate I<sub>DD</sub> > 12 MHz, the estimate should be the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number. For example: V<sub>DD</sub> = 2.6 V; F = 20 MHz, I<sub>DD</sub> = 7.3 mA (25 MHz 20 MHz) x 0.184 mA/MHz = 6.38 mA.

- 6. Idle  $I_{DD}$  can be estimated for frequencies <= 1 MHz by multiplying the frequency of interest by the frequency sensitivity number for that range. When using these numbers to estimate  $I_{DD}$  > 1 MHz, the estimate should be the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number. For example:  $V_{DD}$  = 2.6 V; F= 5 MHz, Idle  $I_{DD}$  = 3 mA (25 MHz– 5 MHz) x 118 µA/MHz = 0.64 mA.

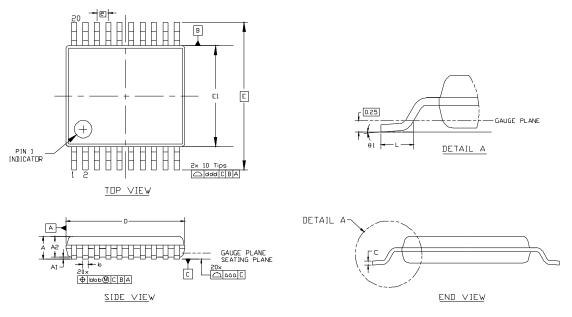

### Figure 3.5. TSSOP-20 Package Diagram

| Symbol | Min  | Nom       | Мах  |

|--------|------|-----------|------|

| A      |      |           | 1.20 |

| A1     | 0.05 | —         | 0.15 |

| A2     | 0.80 | 1.00      | 1.05 |

| b      | 0.19 | _         | 0.30 |

| С      | 0.09 | —         | 0.20 |

| D      | 6.40 | 6.50      | 6.60 |

| е      |      | 0.65 BSC. |      |

| E      |      | 6.40 BSC. |      |

| E1     | 4.30 | 4.40      | 4.50 |

| L      | 0.45 | 0.60      | 0.75 |

| θ1     | 0°   | —         | 8°   |

| aaa    |      | 0.10      |      |

| bbb    |      | 0.10      |      |

| ddd    |      | 0.20      |      |

| otes:  |      |           |      |

#### Table 3.5. TSSOP-20 Package Diagram Dimensions

1. All dimensions shown are in millimeters (mm).

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

**3.** This drawing conforms to JEDEC outline MO-153, variation AC.

**4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

For example, the initial example in this section requires a gain of 0.44 to convert 5 V full scale to 2.2 V full scale. Using Equation 4.3:

$$GAIN = \left(0.44 - GAINADD \times \left(\frac{1}{64}\right)\right) \times 4096$$

If GAINADD is set to 1, this makes the equation:

$$GAIN = \left(0.44 - 1 \times \left(\frac{1}{64}\right)\right) \times 4096 = 0.424 \times 4096 = 1738 = 0x06CA$$

The actual gain from setting GAINADD to 1 and ADC0GNH and ADC0GNL to 0x6CA is 0.4399. A similar gain can be achieved if GAINADD is set to 0 with a different value for ADC0GNH and ADC0GNL.

#### 4.4.2. Setting the Gain Value

The three programmable gain registers are accessed indirectly using the ADC0H and ADC0L registers when the GAINEN bit (ADC0CF.0) bit is set. ADC0H acts as the address register, and ADC0L is the data register. The programmable gain registers can only be written to and cannot be read. See Gain Register Definition 4.1, Gain Register Definition 4.2, and Gain Register Definition 4.3 for more information.

The gain is programmed using the following steps:

- 1. Set the GAINEN bit (ADC0CF.0)

- 2. Load the ADC0H with the ADC0GNH, ADC0GNL, or ADC0GNA address.

- 3. Load ADC0L with the desired value for the selected gain register.

- 4. Reset the GAINEN bit (ADC0CF.0)

#### Notes:

- 1. An ADC conversion should not be performed while the GAINEN bit is set.

- 2. Even with gain enabled, the maximum input voltage must be less than V<sub>REGIN</sub> and the maximum voltage of the signal after gain must be less than or equal to V<sub>REF</sub>.

In code, changing the value to 0.44 gain from the previous example looks like:

```

// in 'C':

ADC0CF |= 0x01;// GAINEN = 1

ADC0H = 0x04;// Load the ADC0GNH address

ADC0L = 0x6C;// Load the upper byte of 0x6CA to ADC0GNH

ADC0H = 0x07;// Load the ADC0GNL address

ADC0L = 0xA0;// Load the lower nibble of 0x6CA to ADC0GNL

ADC0H = 0x08;// Load the ADC0GNA address

ADC0L = 0x01;// Set the GAINADD bit

ADC0CF &= ~0x01;// GAINEN = 0

```

; in assembly ORL ADC0CF,#01H ; GAINEN = 1 MOV ADC0H,#04H; Load the ADC0GNH address MOV ADC0L,#06CH ; Load the upper byte of 0x6CA to ADC0GNH MOV ADC0H,#07H; Load the ADC0GNL address MOV ADC0L,#0A0H ; Load the lower nibble of 0x6CA to ADC0GNL MOV ADC0L,#0A0H ; Load the ADC0GNA address MOV ADC0H,#08H; Load the ADC0GNA address MOV ADC0L,#01H ; Set the GAINADD bit ANL ADC0CF,#0FEH ; GAINEN = 0

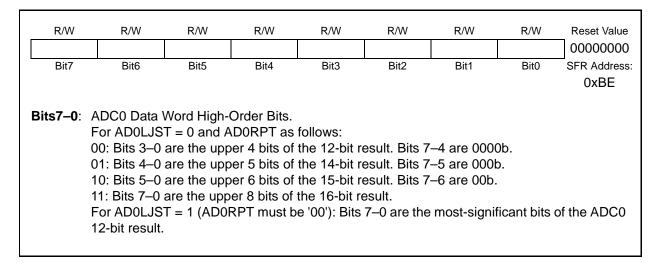

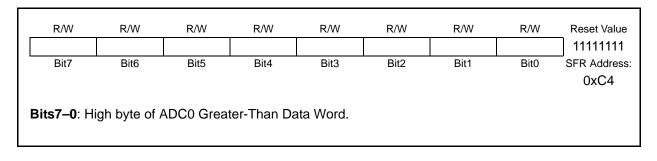

# SFR Definition 4.6. ADC0H: ADC0 Data Word MSB

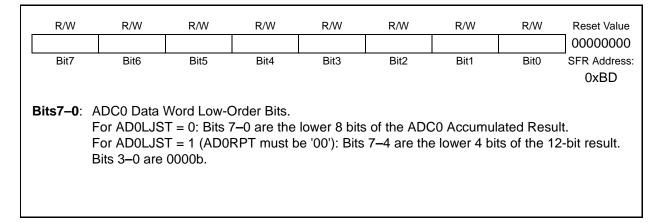

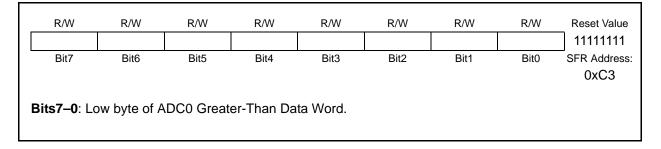

# SFR Definition 4.7. ADC0L: ADC0 Data Word LSB

# 4.5. Programmable Window Detector

The ADC Programmable Window Detector continuously compares the ADC0 output registers to user-programmed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD0WINT in register ADC0CN) can also be used in polled mode. The ADC0 Greater-Than (ADC0GTH, ADC0GTL) and Less-Than (ADC0LTH, ADC0LTL) registers hold the comparison values. The window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC0 Less-Than and ADC0 Greater-Than registers.

# SFR Definition 4.10. ADC0GTH: ADC0 Greater-Than Data High Byte

# SFR Definition 4.11. ADC0GTL: ADC0 Greater-Than Data Low Byte

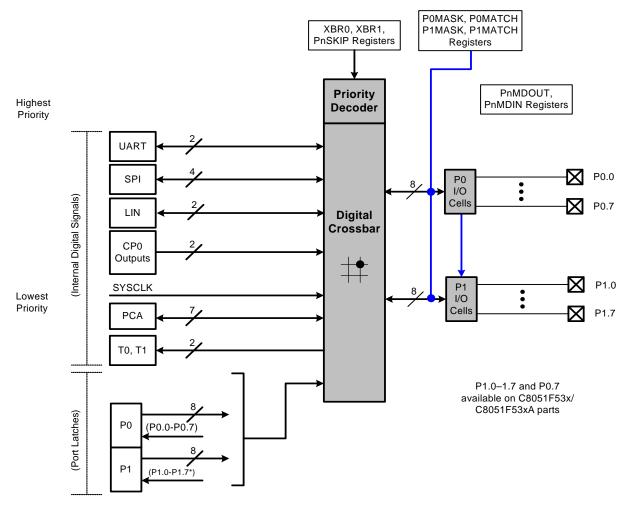

# 13. Port Input/Output

Digital and analog resources are available through up to 16 I/O pins. Port pins are organized as two or one byte-wide Ports. Each of the Port pins can be defined as general-purpose I/O (GPIO) or analog input/out-put; Port pins P0.0 - P2.7 can be assigned to one of the internal digital resources as shown in Figure 13.3. The designer has complete control over which functions are assigned, limited only by the number of physical I/O pins. This resource assignment flexibility is achieved through the use of a Priority Crossbar Decoder. Note that the state of a Port I/O pin can always be read in the corresponding Port latch, regardless of the Crossbar settings.

The Crossbar assigns the selected internal digital resources to the I/O pins based on the peripheral priority order of the Priority Decoder (Figure 13.3 and Figure 13.4). The registers XBR0 and XBR1, defined in SFR Definition 13.1 and SFR Definition 13.2, are used to select internal digital functions.

Port I/O pins are 5.25 V tolerant over the operating range of  $V_{REGIN}$ . Figure 13.2 shows the Port cell circuit. The Port I/O cells are configured as either push-pull or open-drain in the Port Output Mode registers (PnMDOUT, where n = 0,1). Complete Electrical Specifications for Port I/O are given in Table 2.10 on page 33.

Figure 13.1. Port I/O Functional Block Diagram

| SF Signals DFN10 | ΈF       |   | XTAL1 | XTAL2 |   | CNVSTR             |

|------------------|----------|---|-------|-------|---|--------------------|

| PIN I/O          | <u>ч</u> | 1 | 2     | 3     | 4 | <del>້ວ</del><br>5 |

| TX0              |          |   | _     |       |   |                    |

| RX0              |          |   |       |       |   |                    |

| ТХО              | -        |   |       |       |   |                    |

| RX0              |          |   |       |       |   |                    |

| SCK              |          |   |       |       |   |                    |

| MISO             |          |   | l     |       |   |                    |

| MOSI             |          |   |       |       |   |                    |

| NSS*             |          |   |       |       |   |                    |

| LIN-TX           |          |   |       |       |   |                    |

| LIN_RX           |          |   | Ĩ     |       |   |                    |

| CP0              |          |   |       |       |   |                    |

| CP0A             |          |   |       |       |   |                    |

| /SYSCLK          |          |   |       |       |   |                    |

| CEX0             |          |   |       |       |   |                    |

| CEX1             |          |   |       |       |   |                    |

| CEX2             |          |   |       |       |   |                    |

| ECI              |          |   |       |       |   |                    |

| Т0               |          |   |       |       |   |                    |

| T1               |          |   |       |       |   |                    |

|                  | 0        | 0 | 0     | 0     | 0 | 0                  |

Note: 4-Wire SPI Only.

## Figure 13.5. Crossbar Priority Decoder with No Pins Skipped (DFN 10)

**Important Note:** The SPI can be operated in either 3-wire or 4-wire modes, depending on the state of the NSSMD1–NSSMD0 bits in register SPI0CN. According to the SPI mode, the NSS signal may or may not be routed to a Port pin.

# 13.2. Port I/O Initialization

Port I/O initialization consists of the following steps:

- 1. Select the input mode (analog or digital) for all Port pins, using the Port Input Mode register (PnMDIN).

- 2. Select the output mode (open-drain or push-pull) for all Port pins, using the Port Output Mode register (PnMDOUT).

- 3. Select any pins to be skipped by the I/O Crossbar using the Port Skip registers (PnSKIP).

- 4. Assign Port pins to desired peripherals using the XBRn registers.

- 5. Enable the Crossbar (XBARE = 1).

All Port pins must be configured as either analog or digital inputs. Any pins to be used as Comparator or ADC inputs should be configured as an analog inputs. When a pin is configured as an analog input, its weak pullup, digital driver, and digital receiver are disabled. This process saves power and reduces noise on the analog input. Pins configured as digital inputs may still be used by analog peripherals; however, this practice is not recommended.

Additionally, all analog input pins should be configured to be skipped by the Crossbar (accomplished by setting the associated bits in PnSKIP). Port input mode is set in the PnMDIN register, where a 1 indicates a digital input, and a 0 indicates an analog input. All pins default to digital inputs on reset. See SFR Definition 13.4 for the PnMDIN register details.

Important Note: Port 0 and Port 1 pins are 5.25 V tolerant across the operating range of V<sub>REGIN</sub>.

The output driver characteristics of the I/O pins are defined using the Port Output Mode registers (PnMD-OUT). Each Port Output driver can be configured as either open drain or push-pull. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. When the WEAKPUD bit in XBR1 is 0, a weak pullup is enabled for all Port I/O configured as open-drain. WEAKPUD does not affect the push-pull Port I/O. Furthermore, the weak pullup is turned off on an output that is driving a 0 and for pins configured for analog input mode to avoid unnecessary power dissipation.

Registers XBR0 and XBR1 must be loaded with the appropriate values to select the digital I/O functions required by the design. Setting the XBARE bit in XBR1 to 1 enables the Crossbar. Until the Crossbar is enabled, the external pins remain as standard Port I/O (in input mode), regardless of the XBRn Register settings. For given XBRn Register settings, one can determine the I/O pin-out using the Priority Decode Table.

The Crossbar must be enabled to use Port pins as standard Port I/O in output mode. **Port output drivers** are disabled while the Crossbar is disabled.

# 16.1. Signal Descriptions

The four signals used by SPI0 (MOSI, MISO, SCK, NSS) are described below.

#### 16.1.1. Master Out, Slave In (MOSI)

The master-out, slave-in (MOSI) signal is an output from a master device and an input to slave devices. It is used to serially transfer data from the master to the slave. This signal is an output when SPI0 is operating as a master and an input when SPI0 is operating as a slave. Data is transferred most-significant bit first. When configured as a master, MOSI is driven by the MSB of the shift register in both 3- and 4-wire mode.

#### 16.1.2. Master In, Slave Out (MISO)

The master-in, slave-out (MISO) signal is an output from a slave device and an input to the master device. It is used to serially transfer data from the slave to the master. This signal is an input when SPI0 is operating as a master and an output when SPI0 is operating as a slave. Data is transferred most-significant bit first. The MISO pin is placed in a high-impedance state when the SPI module is disabled and when the SPI operates in 4-wire mode as a slave that is not selected. When acting as a slave in 3-wire mode, MISO is always driven by the MSB of the shift register.

#### 16.1.3. Serial Clock (SCK)

The serial clock (SCK) signal is an output from the master device and an input to slave devices. It is used to synchronize the transfer of data between the master and slave on the MOSI and MISO lines. SPI0 generates this signal when operating as a master. The SCK signal is ignored by a SPI slave when the slave is not selected (NSS = 1) in 4-wire slave mode.

#### 16.1.4. Slave Select (NSS)

The function of the slave-select (NSS) signal is dependent on the setting of the NSSMD1 and NSSMD0 bits in the SPI0CN register. There are three possible modes that can be selected with these bits:

- 1. NSSMD[1:0] = 00: 3-Wire Master or 3-Wire Slave Mode: SPI0 operates in 3-wire mode, and NSS is disabled. When operating as a slave device, SPI0 is always selected in 3-wire mode. Since no select signal is present, SPI0 must be the only slave on the bus in 3-wire mode. This is intended for point-to-point communication between a master and one slave.

- NSSMD[1:0] = 01: 4-Wire Slave or Multi-Master Mode: SPI0 operates in 4-wire mode, and NSS is enabled as an input. When operating as a slave, NSS selects the SPI0 device. When operating as a master, a 1-to-0 transition of the NSS signal disables the master function of SPI0 so that multiple master devices can be used on the same SPI bus.

- 3. NSSMD[1:0] = 1x: 4-Wire Master Mode: SPI0 operates in 4-wire mode, and NSS is enabled as an output. The setting of NSSMD0 determines what logic level the NSS pin will output. This configuration should only be used when operating SPI0 as a master device.

See Figure 16.2, Figure 16.3, and Figure 16.4 for typical connection diagrams of the various operational modes. **Note that the setting of NSSMD bits affects the pinout of the device.** When in 3-wire master or 3-wire slave mode, the NSS pin will not be mapped by the crossbar. In all other modes, the NSS signal will be mapped to a pin on the device. See Section "13. Port Input/Output" on page 120 for general purpose port I/O and crossbar information.

| Parameter          | Description                                                                                                                                        | Min                     | Max                     | Units |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------|-------|

| Master Mode        | Timing* (See Figure 16.6 and Figure 16.7)                                                                                                          |                         | 1                       | 1     |

| т <sub>мскн</sub>  | SCK High Time                                                                                                                                      | 1 x T <sub>SYSCLK</sub> | —                       | ns    |

| T <sub>MCKL</sub>  | SCK Low Time                                                                                                                                       | 1 x T <sub>SYSCLK</sub> | —                       | ns    |

| T <sub>MIS</sub>   | MISO Valid to SCK Sample Edge                                                                                                                      | 20                      | —                       | ns    |

| т <sub>мін</sub>   | SCK Sample Edge to MISO Change                                                                                                                     | 0                       | —                       | ns    |

| Slave Mode T       | iming* (See Figure 16.8 and Figure 16.9)                                                                                                           | ·                       |                         |       |

| T <sub>SE</sub>    | NSS Falling to First SCK Edge                                                                                                                      | 2 x T <sub>SYSCLK</sub> | —                       | ns    |

| T <sub>SD</sub>    | Last SCK Edge to NSS Rising                                                                                                                        | 2 x T <sub>SYSCLK</sub> | —                       | ns    |

| T <sub>SEZ</sub>   | NSS Falling to MISO Valid                                                                                                                          | —                       | 4 x T <sub>SYSCLK</sub> | ns    |

| T <sub>SDZ</sub>   | NSS Rising to MISO High-Z                                                                                                                          | —                       | 4 x T <sub>SYSCLK</sub> | ns    |

| тскн               | SCK High Time                                                                                                                                      | 5 x T <sub>SYSCLK</sub> | —                       | ns    |

| T <sub>CKL</sub>   | SCK Low Time                                                                                                                                       | 5 x T <sub>SYSCLK</sub> | —                       | ns    |

| T <sub>SIS</sub>   | MOSI Valid to SCK Sample Edge                                                                                                                      | 2 x T <sub>SYSCLK</sub> | —                       | ns    |

| T <sub>SIH</sub>   | SCK Sample Edge to MOSI Change                                                                                                                     | 2 x T <sub>SYSCLK</sub> | —                       | ns    |

| Т <sub>SOH</sub>   | SCK Shift Edge to MISO Change                                                                                                                      | -                       | 4 x T <sub>SYSCLK</sub> | ns    |

| The max<br>Transmi | is equal to one period of the device system clock (SYS<br>imum possible frequency of the SPI can be calculated<br>ssion: SYSCLK/2<br>on: SYSCLK/10 |                         |                         |       |

# Table 16.1. SPI Slave Timing Parameters

# SFR Definition 17.12. LIN0CTRL: LIN0 Control Register

| W            | W                               | W            | R/W          | R/W          | R/W          | R/W            | R/W          | Reset Value       |

|--------------|---------------------------------|--------------|--------------|--------------|--------------|----------------|--------------|-------------------|

| STOP         | SLEEP                           | TXRX         | DTACK        | RSTINT       | RSTERR       | WUPREQ         | STREQ        | 00000000          |

| Bit7         | Bit6                            | Bit5         | Bit4         | Bit3         | Bit2         | Bit1           | Bit0         | 7                 |

|              |                                 |              |              |              |              |                | Address      | : 0x08 (indirect) |

|              |                                 | <b>.</b> .   |              |              |              | <u>.</u> .     |              |                   |

| Bit7:        | STOP: Stop                      |              |              | •            |              | • /            |              |                   |

|              | This bit is to                  |              |              |              |              | •              |              |                   |

|              | until the next<br>request inter |              | •            |              |              |                | •            |                   |

|              | 0).                             | rupt and ca  | nnot use tri | e frame cor  |              | e received ic  |              | vays reaus        |

| Bit6:        | SLEEP: Slee                     | on Mode W    | arning       |              |              |                |              |                   |

| Bitto.       | This bit is to                  | •            | •            | on to warn t | the peripher | ral that a Sle | ep Mode F    | rame was          |

|              | received and                    |              |              |              |              |                | •            |                   |

|              | The applicat                    |              |              | •            |              |                |              |                   |

| Bit5:        | TXRX: Trans                     | smit/Receiv  | e Selection  | Bit.         |              | -              |              |                   |

|              | This bit dete                   |              |              |              | nsmit frame  | e or a receive | e frame.     |                   |

|              | 0: Current fra                  |              |              |              |              |                |              |                   |

| <b>D</b> 144 | 1: Current fra                  |              | •            |              |              |                |              |                   |

| Bit4:        | DTACK: Dat                      |              | •            |              | • /          |                |              |                   |

|              | Set to 1 after<br>matically be  | •            |              |              | to acknowle  | edge the trai  | nster. The c | oit will auto-    |

| Bit3:        | RSTINT: Inte                    |              |              | Controller.  |              |                |              |                   |

| Dito.        | This bit alwa                   |              |              |              |              |                |              |                   |

|              | 0: No effect.                   |              |              |              |              |                |              |                   |

|              | 1: Reset the                    | LININT bit   | (LIN0ST.3)   |              |              |                |              |                   |

| Bit2:        | RSTERR: EI                      | rror Reset E | Sit.         |              |              |                |              |                   |

|              | This bit alwa                   | ys reads as  | s 0.         |              |              |                |              |                   |

|              | 0: No effect.                   |              |              |              |              |                |              |                   |

|              | 1: Reset the                    |              |              | nd LIN0ERF   | र.           |                |              |                   |

| Bit1:        | WUPREQ: V                       |              |              | P            |              |                |              | C II . I .        |

|              | Set to 1 to te                  |              |              | y sending a  | wakeup się   | gnal. The bit  | will automa  | atically be       |

| Bit0:        | cleared to 0<br>STREQ: Sta      |              |              | mode only    | <i>(</i> )   |                |              |                   |

| DILU.        | 1: Start a LIN                  |              |              |              |              | oading the ic  | lentifier da | ta length         |

|              | and data buf                    |              |              |              | only alter i |                | ionanoi, ua  | alongin           |

|              | The bit is res                  |              |              | sion comple  | tion or erro | r detection.   |              |                   |

|              |                                 |              |              |              |              |                |              |                   |

|              |                                 |              |              |              |              |                |              |                   |

|              |                                 |              |              |              |              |                |              |                   |

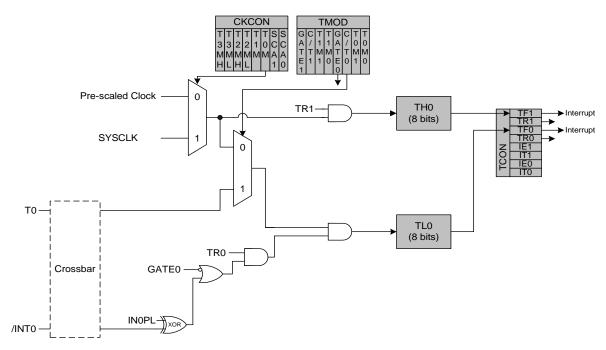

#### 18.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)

In Mode 3, Timer 0 is configured as two separate 8-bit counter/timers held in TL0 and TH0. The counter/timer in TL0 is controlled using the Timer 0 control/status bits in TCON and TMOD: TR0, C/T0, GATE0 and TF0. TL0 can use either the system clock or an external input signal as its timebase. The TH0 register is restricted to a timer function sourced by the system clock or prescaled clock. TH0 is enabled using the Timer 1 run control bit TR1. TH0 sets the Timer 1 overflow flag TF1 on overflow and thus controls the Timer 1 interrupt.

Timer 1 is inactive in Mode 3. When Timer 0 is operating in Mode 3, Timer 1 can be operated in Modes 0, 1 or 2, but cannot be clocked by external signals nor set the TF1 flag and generate an interrupt. However, the Timer 1 overflow can be used to generate baud rates for the SMBus and UART. While Timer 0 is operating in Mode 3, Timer 1 run control is handled through its mode settings. To run Timer 1 while Timer 0 is in Mode 3, set the Timer 1 Mode as 0, 1, or 2. To disable Timer 1, configure it for Mode 3.

Figure 18.3. T0 Mode 3 Block Diagram

| R/W               | R/W                                                                                                                                                                                                                            | R/W                                                                                                                                           | R/W                                                                                                                                                                               | R/W                                                                                                                                              | R/W                                                                                              | R/W                                                                    | R/W                        | Reset Value |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------|-------------|

| GATE1             | C/T1                                                                                                                                                                                                                           | T1M1                                                                                                                                          | T1M0                                                                                                                                                                              | GATE0                                                                                                                                            | C/T0                                                                                             | T0M1                                                                   | T0M0                       | 0000000     |

| Bit7              | Bit6                                                                                                                                                                                                                           | Bit5                                                                                                                                          | Bit4                                                                                                                                                                              | Bit3                                                                                                                                             | Bit2                                                                                             | Bit1                                                                   | Bit0<br>SFR Address:       | 0x89        |

|                   | GATE1: T                                                                                                                                                                                                                       |                                                                                                                                               |                                                                                                                                                                                   |                                                                                                                                                  |                                                                                                  |                                                                        |                            |             |

|                   | 1: Timer 1                                                                                                                                                                                                                     | enabled or                                                                                                                                    | then TR1 = 1 i                                                                                                                                                                    | = 1 AND INT                                                                                                                                      | 0 is active                                                                                      | as defined                                                             |                            | •           |

|                   | <b>C/T1</b> : Cou                                                                                                                                                                                                              |                                                                                                                                               | finition 10.5.<br>1 Select                                                                                                                                                        | TIUICE. IN                                                                                                                                       |                                                                                                  | Shinguration                                                           | i on page to               | 5).         |

|                   |                                                                                                                                                                                                                                |                                                                                                                                               | mer 1 increme                                                                                                                                                                     | ented by cloo                                                                                                                                    | ck defined b                                                                                     | by T1M bit                                                             | (CKCON.4).                 |             |

|                   |                                                                                                                                                                                                                                |                                                                                                                                               | Timer 1 increi                                                                                                                                                                    |                                                                                                                                                  |                                                                                                  |                                                                        |                            | iput pin    |

|                   | (T1).                                                                                                                                                                                                                          |                                                                                                                                               |                                                                                                                                                                                   |                                                                                                                                                  |                                                                                                  |                                                                        |                            |             |

|                   |                                                                                                                                                                                                                                |                                                                                                                                               | 1 Mode Select                                                                                                                                                                     |                                                                                                                                                  |                                                                                                  |                                                                        |                            |             |

|                   | These bits                                                                                                                                                                                                                     | select the                                                                                                                                    | Timer 1 opera                                                                                                                                                                     | ation mode.                                                                                                                                      |                                                                                                  |                                                                        |                            |             |

|                   | T1M1                                                                                                                                                                                                                           | T1M0                                                                                                                                          |                                                                                                                                                                                   | Mode                                                                                                                                             | ;                                                                                                |                                                                        |                            |             |

|                   | 0                                                                                                                                                                                                                              | 0                                                                                                                                             | Mode 0: 13-bi                                                                                                                                                                     | it counter/tin                                                                                                                                   |                                                                                                  |                                                                        |                            |             |

|                   | 0                                                                                                                                                                                                                              | 1                                                                                                                                             | Mada 1. 10 h                                                                                                                                                                      |                                                                                                                                                  |                                                                                                  |                                                                        |                            |             |

|                   | •                                                                                                                                                                                                                              | I                                                                                                                                             | Node 1: 16-bi                                                                                                                                                                     | it counter/tin                                                                                                                                   | ner                                                                                              |                                                                        |                            |             |

|                   | 1                                                                                                                                                                                                                              |                                                                                                                                               | Mode 1: 16-bit<br>Mode 2: 8-bit                                                                                                                                                   |                                                                                                                                                  |                                                                                                  | -reload                                                                |                            |             |

|                   | -                                                                                                                                                                                                                              | 0                                                                                                                                             |                                                                                                                                                                                   | counter/time                                                                                                                                     |                                                                                                  | o-reload                                                               |                            |             |

| D:40.             | 1                                                                                                                                                                                                                              | 0<br>1                                                                                                                                        | Mode 2: 8-bit<br>Mode 3: Time                                                                                                                                                     | counter/time                                                                                                                                     |                                                                                                  | o-reload                                                               |                            |             |

|                   | 1<br>1<br>GATE0: T                                                                                                                                                                                                             | 0<br>1<br>mer 0 Gate                                                                                                                          | Mode 2: 8-bit<br>Mode 3: Time<br>e Control.                                                                                                                                       | counter/time<br>r 1 inactive                                                                                                                     | er with auto                                                                                     |                                                                        |                            |             |

|                   | <b>GATE0</b> : T<br>0: Timer 0                                                                                                                                                                                                 | 0<br>1<br>mer 0 Gate<br>enabled w                                                                                                             | Mode 2: 8-bit<br>Mode 3: Time<br>e Control.<br>hen TR0 = 1 i                                                                                                                      | counter/time<br>r 1 inactive<br>rrespective                                                                                                      | er with auto                                                                                     | ic level.                                                              | by bit IN0PL               | in register |

|                   | 1<br>1<br>GATE0: T<br>0: Timer 0<br>1: Timer 0                                                                                                                                                                                 | 0<br>1<br>mer 0 Gate<br>enabled w<br>enabled or                                                                                               | Mode 2: 8-bit<br>Mode 3: Time<br>e Control.                                                                                                                                       | counter/time<br>r 1 inactive<br>rrespective<br>= 1 AND INT                                                                                       | er with auto<br>of INTO log<br>T0 is active                                                      | ic level.<br>as defined                                                |                            |             |

| Bit2:             | <b>GATE0</b> : T<br>0: Timer 0<br>1: Timer 0<br>IT01CF (s<br><b>C/T0</b> : Cou                                                                                                                                                 | 0<br>1<br>mer 0 Gate<br>enabled w<br>enabled or<br>ee SFR De<br>nter/Timer                                                                    | Mode 2: 8-bit<br>Mode 3: Time<br>e Control.<br>then TR0 = 1 i<br>hly when TR0<br>finition 10.5.<br>Select.                                                                        | counter/time<br>r 1 inactive<br>rrespective<br>= 1 AND INT<br>"IT01CF: IN                                                                        | er with auto<br>of INTO log<br>TO is active<br>TO/INT1 Co                                        | ic level.<br>as defined<br>onfiguratior                                | n" on page 10              |             |

| Bit2:             | <b>GATE0</b> : T<br>0: Timer 0<br>1: Timer 0<br>IT01CF (s<br><b>C/T0</b> : Cou<br>0: Timer F                                                                                                                                   | 0<br>1<br>enabled w<br>enabled or<br>ee SFR De<br>nter/Timer<br>unction: Ti                                                                   | Mode 2: 8-bit<br>Mode 3: Time<br>e Control.<br>then TR0 = 1 i<br>hly when TR0<br>finition 10.5.<br>Select.<br>mer 0 increme                                                       | counter/time<br>r 1 inactive<br>rrespective<br>= 1 AND INT<br>"IT01CF: IN<br>ented by cloo                                                       | er with auto<br>of INTO log<br>TO is active<br>TO/INT1 Co<br>ck defined b                        | ic level.<br>as defined<br>onfiguration<br>by TOM bit                  | " on page 10<br>(CKCON.3). | 5).         |

| Bit2:             | <b>GATE0</b> : T<br>0: Timer 0<br>1: Timer 0<br>IT01CF (s<br><b>C/T0</b> : Cou<br>0: Timer F<br>1: Counter                                                                                                                     | 0<br>1<br>enabled w<br>enabled or<br>ee SFR De<br>nter/Timer<br>unction: Ti                                                                   | Mode 2: 8-bit<br>Mode 3: Time<br>e Control.<br>then TR0 = 1 i<br>hly when TR0<br>finition 10.5.<br>Select.                                                                        | counter/time<br>r 1 inactive<br>rrespective<br>= 1 AND INT<br>"IT01CF: IN<br>ented by cloo                                                       | er with auto<br>of INTO log<br>TO is active<br>TO/INT1 Co<br>ck defined b                        | ic level.<br>as defined<br>onfiguration<br>by TOM bit                  | " on page 10<br>(CKCON.3). | 5).         |

| Bit2:             | <b>GATE0</b> : T<br>0: Timer 0<br>1: Timer 0<br>IT01CF (s<br><b>C/T0</b> : Cou<br>0: Timer F<br>1: Counter<br>(T0).                                                                                                            | 0<br>1<br>enabled w<br>enabled or<br>ee SFR De<br>nter/Timer<br>unction: Ti<br>Function:                                                      | Mode 2: 8-bit<br>Mode 3: Time<br>e Control.<br>then TR0 = 1 in<br>hy when TR0<br>efinition 10.5.<br>Select.<br>mer 0 increme<br>Timer 0 increme                                   | counter/time<br>r 1 inactive<br>= 1 AND INT<br>"IT01CF: IN<br>ented by cloomented by h                                                           | er with auto<br>of INTO log<br>TO is active<br>TO/INT1 Co<br>ck defined b                        | ic level.<br>as defined<br>onfiguration<br>by TOM bit                  | " on page 10<br>(CKCON.3). | 5).         |

| Bit2:<br>Bits1–0: | <b>GATE0</b> : T<br>0: Timer 0<br>1: Timer 0<br>IT01CF (s<br><b>C/T0</b> : Cou<br>0: Timer F<br>1: Counter<br>(T0).<br><b>T0M1–T0</b>                                                                                          | 0<br>1<br>mer 0 Gate<br>enabled w<br>enabled or<br>ee SFR De<br>nter/Timer<br>unction: Ti<br>Function: Ti                                     | Mode 2: 8-bit<br>Mode 3: Time<br>e Control.<br>then TR0 = 1 i<br>hly when TR0<br>finition 10.5.<br>Select.<br>mer 0 increme                                                       | counter/time<br>r 1 inactive<br>= 1 AND INT<br>"IT01CF: IN<br>ented by cloo<br>mented by h                                                       | er with auto<br>of INTO log<br>TO is active<br>TO/INT1 Co<br>ck defined b                        | ic level.<br>as defined<br>onfiguration<br>by TOM bit                  | " on page 10<br>(CKCON.3). | 5).         |

| Bit2:<br>Bits1–0: | <b>GATE0</b> : T<br>0: Timer 0<br>1: Timer 0<br>IT01CF (s<br><b>C/T0</b> : Cou<br>0: Timer F<br>1: Counter<br>(T0).<br><b>T0M1–T0</b>                                                                                          | 0<br>1<br>mer 0 Gate<br>enabled or<br>ee SFR De<br>nter/Timer<br>unction: Ti<br>Function:<br><b>M0</b> : Timer (<br>select the                | Mode 2: 8-bit<br>Mode 3: Time<br>e Control.<br>then TR0 = 1 i<br>hly when TR0<br>finition 10.5.<br>Select.<br>mer 0 increme<br>Timer 0 increme                                    | counter/time<br>r 1 inactive<br>= 1 AND INT<br>"IT01CF: IN<br>ented by cloo<br>mented by h<br>t.<br>ation mode.                                  | er with auto<br>of INTO log<br>TO is active<br>TO/INT1 Co<br>ck defined k<br>igh-to-low t        | ic level.<br>as defined<br>onfiguration<br>by TOM bit                  | " on page 10<br>(CKCON.3). | 5).         |

| Bit2:<br>Bits1–0: | 1           1           0: Timer 0           1: Timer 0           101CF (s           C/T0: Cou           0: Timer F           1: Counter           (T0).           TOM1-TOI           These bits                               | 0<br>1<br>mer 0 Gate<br>enabled or<br>ee SFR De<br>nter/Timer<br>unction: Ti<br>Function:<br><b>M0</b> : Timer (<br>select the<br><b>T0M0</b> | Mode 2: 8-bit<br>Mode 3: Time<br>e Control.<br>then TR0 = 1 i<br>hly when TR0<br>finition 10.5.<br>Select.<br>mer 0 increme<br>Timer 0 increme<br>D Mode Select<br>Timer 0 opera  | counter/time<br>r 1 inactive<br>= 1 AND INT<br>"IT01CF: IN<br>ented by cloo<br>mented by h<br>t.<br>ation mode.                                  | er with auto<br>of INTO log<br>TO is active<br>TO/INT1 Co<br>ck defined to<br>igh-to-low to<br>e | ic level.<br>as defined<br>onfiguration<br>by TOM bit                  | " on page 10<br>(CKCON.3). | 5).         |

| Bit2:<br>Bits1–0: | 1           1           0: Timer 0           1: Timer 0           IT01CF (s           C/T0: Courd           0: Timer F           1: Counter           (T0).           TOM1-TOI           These bits                            | 0<br>1<br>mer 0 Gate<br>enabled w<br>enabled or<br>ee SFR De<br>nter/Timer<br>unction: Ti<br>Function: Ti<br>Select the<br><b>TOM0</b><br>0   | Mode 2: 8-bit<br>Mode 3: Time<br>e Control.<br>then TR0 = 1 i<br>hly when TR0<br>efinition 10.5.<br>Select.<br>mer 0 increme<br>Timer 0 increme<br>D Mode Select<br>Timer 0 opera | counter/time<br>r 1 inactive<br>= 1 AND INT<br>"IT01CF: IN<br>ented by cloo<br>mented by h<br>t.<br>ation mode.<br><b>Mode</b><br>it counter/tim | er with auto                                                                                     | ic level.<br>as defined<br>onfiguration<br>by TOM bit                  | " on page 10<br>(CKCON.3). | 5).         |

| Bit2:<br>Bits1–0: | 1           1           0: Timer 0           1: Timer 0           1T01CF (s           C/T0: Could           0: Timer F           1: Counter           (T0).           TOM1-T0I           These bits           T0M1           0 | 0<br>1<br>mer 0 Gate<br>enabled or<br>ee SFR De<br>nter/Timer<br>unction: Ti<br>Function:<br>Select the<br><b>TOM0</b><br>0<br>1              | Mode 2: 8-bit<br>Mode 3: Time<br>e Control.<br>then TR0 = 1 i<br>hly when TR0<br>finition 10.5.<br>Select.<br>mer 0 increme<br>Timer 0 increme<br>D Mode Select<br>Timer 0 opera  | counter/time<br>r 1 inactive<br>= 1 AND INT<br>"IT01CF: IN<br>ented by cloo<br>mented by h<br>t.<br>ation mode.<br><b>Mode</b><br>it counter/tim | er with auto                                                                                     | ic level.<br>as defined<br>onfiguration<br>by TOM bit<br>transitions o | " on page 10<br>(CKCON.3). | 5).         |

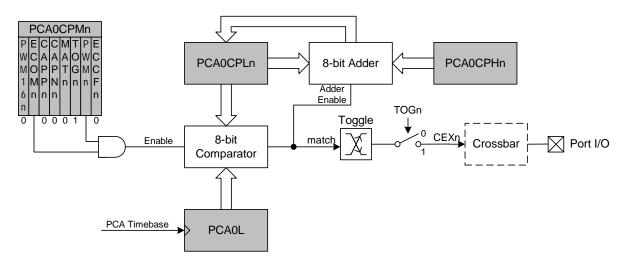

#### 19.2.4. Frequency Output Mode

Frequency Output Mode produces a programmable-frequency square wave on the module's associated CEXn pin. The capture/compare module high byte holds the number of PCA clocks to count before the output is toggled. The frequency of the square wave is then defined by Equation 19.1.

$$F_{CEXn} = \frac{F_{PCA}}{2 \times PCA0CPHn}$$

**Note:** A value of 0x00 in the PCA0CPHn register is equal to 256 for this equation.

#### Equation 19.1. Square Wave Frequency Output

Where  $F_{PCA}$  is the frequency of the clock selected by the CPS2-0 bits in the PCA mode register, PCA0MD. The lower byte of the capture/compare module is compared to the PCA counter low byte; on a match, CEXn is toggled and the offset held in the high byte is added to the matched value in PCA0CPLn. Frequency Output Mode is enabled by setting the ECOMn, TOGn, and PWMn bits in the PCA0CPMn register.

Figure 19.7. PCA Frequency Output Mode

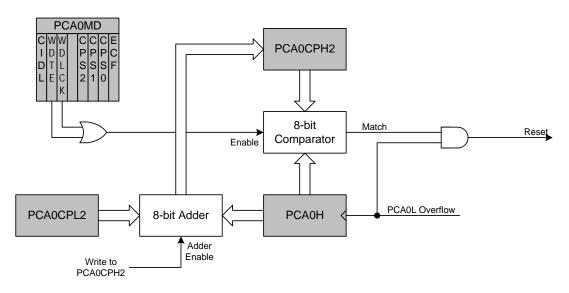

## 19.3.1. Watchdog Timer Operation

While the WDT is enabled:

- PCA counter is forced on.

- Writes to PCA0L and PCA0H are not allowed.

- PCA clock source bits (CPS2-CPS0) are frozen.

- PCA Idle control bit (CIDL) is frozen.

- Module 2 is forced into software timer mode.

- Writes to the Module 2 mode register (PCA0CPM2) are disabled.

While the WDT is enabled, writes to the CR bit will not change the PCA counter state; the counter will run until the WDT is disabled. The PCA counter run control (CR) will read zero if the WDT is enabled but user software has not enabled the PCA counter. If a match occurs between PCA0CPH2 and PCA0H while the WDT is enabled, a reset will be generated. To prevent a WDT reset, the WDT may be updated with a write of any value to PCA0CPH2. Upon a PCA0CPH2 write, PCA0H plus the offset held in PCA0CPL2 is loaded into PCA0CPH2 (See Figure 19.10).

#### Figure 19.10. PCA Module 2 with Watchdog Timer Enabled

Note that the 8-bit offset held in PCA0CPH2 is compared to the upper byte of the 16-bit PCA counter. This offset value is the number of PCA0L overflows before a reset. Up to 256 PCA clocks may pass before the first PCA0L overflow occurs, depending on the value of the PCA0L when the update is performed. The total offset is then given (in PCA clocks) by Equation 19.4, where PCA0L is the value of the PCA0L register at the time of the update.

$Offset = (256 \times PCA0CPL2) + (256 - PCA0L)$

#### Equation 19.4. Watchdog Timer Offset in PCA Clocks

The WDT reset is generated when PCA0L overflows while there is a match between PCA0CPH2 and PCA0H. Software may force a WDT reset by writing a 1 to the CCF2 flag (PCA0CN.2) while the WDT is enabled.

# C2 Register Definition 21.3. REVID: C2 Revision ID

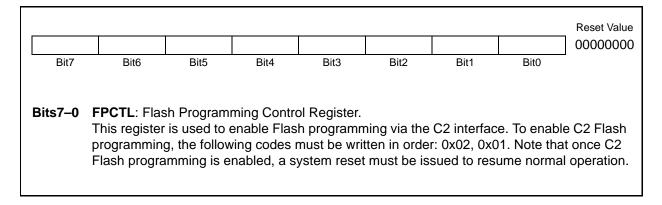

# C2 Register Definition 21.4. FPCTL: C2 Flash Programming Control

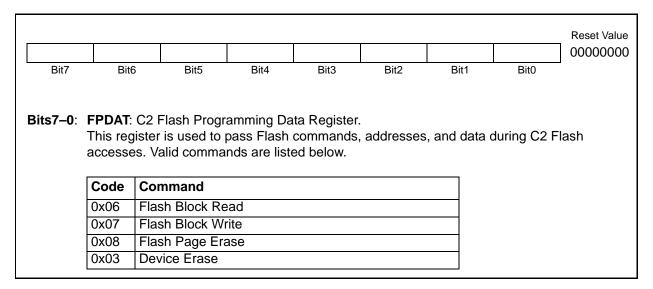

# C2 Register Definition 21.5. FPDAT: C2 Flash Programming Data

# **DOCUMENT CHANGE LIST**

## Revision 0.3 to 0.4

- Updated all specification tables.

- Added 'F52xA and 'F53xA information.

- Updated the Selectable Gain section in the ADC section.

- Updated the External Crystal Example in the Oscillators section.

- Updated the LIN section.

# Revision 0.4 to 0.5

- Updated all specification tables.

- Updated Figures 1.1, 1.2, 1.3, and 1.4.

- Updated Section 4 pinout diagrams and tables.

# Revision 0.5 to 1.0

- Updated all specification tables and moved them to one section.

- Added Figure 3.1 and Figure 3.2.

- Updated Section 4 pinout diagrams and tables.

- Updated Figure 5.6.

- Added Figure 15.3.

- Updated equations in Section 17.

- Updated Figure 21.3.

# Revision 1.0 to 1.1

- Updated Table 2.3, "ADC0 Electrical Characteristics," on page 28 with new Burst Mode Oscillator specification, new Power Supply Current maximum, and made corrections to Temperature Sensor Offset and Offset Error conditions.

- Updated Table 2.9, "Flash Electrical Characteristics," on page 33 with new Flash Write and Erase timing.

- Made correction in Equivalent Gain table in Section "4.4. Selectable Gain" on page 60.

- Updated Section "11.2. Power-Fail Reset / VDD Monitors (VDDMON0 and VDDMON1)" on page 108 regarding higher V<sub>DD</sub> monitor threshold.

## Revision 1.1 to 1.2

- Updated "Ordering Information" on page 14 and Table 1.1, "Product Selection Guide (Recommended for New Designs)," on page 14 to include -A (Automotive) devices and automotive qualification information.

- Updated Table 2.3, "ADC0 Electrical Characteristics," on page 28 to include Temperature Sensor tracking time requirement and update INL maximum specification.

- Updated Figure 3.2. 'DFN-10 Package Diagram' on page 38 with new Pin-1 detail drawing.

- Updated Table 8.1, "CIP-51 Instruction Set Summary," on page 83 with correct CJNE and CPL timing.

- Updated "Power-Fail Reset / VDD Monitors (VDDMON0 and VDDMON1)" on page 108 to clarify the recommendations for the VDD monitor.

Note: All items from the C8051F52xA-F53xA Errata dated August 26, 2009 are incorporated into this data sheet.

- Replaced minimum VDD value for Flash write/erase operations in Table 2.9 on page 33 with references to the V<sub>RST-HIGH</sub> theshold specified in Table 2.8 on page 32.

- Removed Output Low Voltage values for condition 'V<sub>REGIN</sub> = 1.8 V' from Table 2.10, "Port I/O DC Electrical Characteristics," on page 33.

- Corrected minor typo ("IFCN = 111b") in Table 2.11, "Internal Oscillator Electrical Characteristics," on page 34.

- Removed the typical value and added the maximum value for the 'Wake-up Time From Suspend' specification with the 'ZTCEN = 0' condition in Table 2.11, "Internal Oscillator Electrical Characteristics," on page 34.

- Added Internal Oscillator Supply current values at specific temperatures for conditions 'ZTCEN = 1' and 'ZTCEN = 0' in Table 2.11, "Internal Oscillator Electrical Characteristics," on page 34. Also updated the table name to clarify that the specifications apply to the internal oscillator.

- Updated Section "1.1. Ordering Information" on page 14 and Table 1.1 with new C8051F52x-C/F53x-C part numbers.

- Updated Table 1.2, "Product Selection Guide (Not Recommended for New Designs)," on page 15 to include C8051F52xA/F53xA part numbers.

- Updated Figure 1.1, Figure 1.2, Figure 1.3, and Figure 1.4 titles to clarify applicable silicon revisions.

- Added figure references to pinout diagrams (Figure 3.1, Figure 3.4, and Figure 3.7) and updated labels to clarify applicable part numbers.

- Updated Table 3.1, Table 3.4, and Table 3.7 to indicate pinouts applicable to C8051F52x-C/F53x-C devices.

- Added note in Section "6. Voltage Regulator (REG0)" on page 74 to indicate the need for bypass capacitors for voltage regulator stability.

- Updated Figure 11.1 on Page 106 and text in Section "11.1. Power-On Reset" on page 107 and Section "11.2. Power-Fail Reset / VDD Monitors (VDDMON0 and VDDMON1)" on page 108 to describe the new level-sensitive V<sub>DD</sub> monitor (VDDMON1).

- Updated SFR Definition 11.1. "VDDMON: VDD Monitor Control" on page 109 to include the VDM1EN bit (bit 4) that controls the new level-sensitive V<sub>DD</sub> monitor (VDDMON1).

- Added notes in Section 11.1 on page 107, Section 11.2 on page 108, and Section 11.3 on page 110 with references to relevant parts of Section "20. Device Specific Behavior" on page 210.

- Moved some notes related to VDD Monitor (VDDMON0) High Threshold setting (V<sub>RST-HIGH</sub>) from Section 11.2 on page 108 to Section 20.5 on page 212 in Section "20. Device Specific Behavior".

- Added Section "11.2.1. VDD Monitor Thresholds and Minimum VDD" on page 108 to describe the recommendations for minimum V<sub>DD</sub> as it relates to the V<sub>DD</sub> monitor thresholds.

- Clarified text in Section "11.7. Flash Error Reset" on page 110.

- Clarified text in items 2, 3 and 4 in Section "12.2.1. V<sub>DD</sub> Maintenance and the V<sub>DD</sub> monitor" on page 115 to reference appropriate specification tables and specify "VDDMON0".