Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                  |

|----------------------------|------------------------------------------------------------------|

| Product Status             | Active                                                           |

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | LINbus, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT               |

| Number of I/O              | 6                                                                |

| Program Memory Size        | 2KB (2K x 8)                                                     |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 256 x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                     |

| Data Converters            | A/D 6x12b                                                        |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                               |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 10-VFDFN Exposed Pad                                             |

| Supplier Device Package    | 10-DFN (3x3)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f526a-imr |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

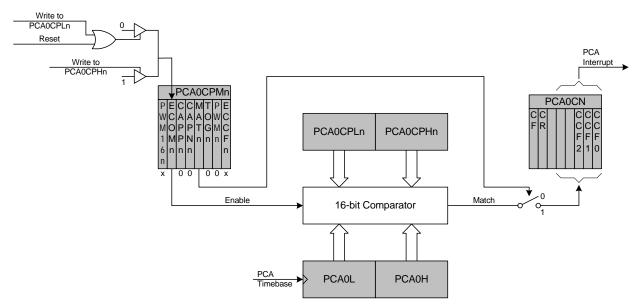

| 19. Programmable Counter Array (PCA0)              | 195 |

|----------------------------------------------------|-----|

| 19.1. PCA Counter/Timer                            |     |

| 19.2. Capture/Compare Modules                      | 197 |

| 19.2.1. Edge-triggered Capture Mode                | 198 |

| 19.2.2. Software Timer (Compare) Mode              |     |

| 19.2.3. High Speed Output Mode                     |     |

| 19.2.4. Frequency Output Mode                      |     |

| 19.2.5. 8-Bit Pulse Width Modulator Mode           |     |

| 19.2.6. 16-Bit Pulse Width Modulator Mode          |     |

| 19.3. Watchdog Timer Mode                          | 203 |

| 19.3.1. Watchdog Timer Operation                   |     |

| 19.3.2. Watchdog Timer Usage                       |     |

| 19.4. Register Descriptions for PCA                |     |

| 20. Device Specific Behavior                       |     |

| 20.1. Device Identification                        |     |

| 20.2. Reset Pin Behavior                           | 211 |

| 20.3. Reset Time Delay                             | 211 |

| 20.4. VDD Monitors and VDD Ramp Time               |     |

| 20.5. VDD Monitor (VDDMON0) High Threshold Setting | 212 |

| 20.6. Reset Low Time                               |     |

| 20.7. Internal Oscillator Suspend Mode             |     |

| 20.8. UART Pins                                    | 213 |

| 20.9. LIN                                          | 213 |

| 20.9.1. Stop Bit Check                             | 213 |

| 20.9.2. Synch Break and Synch Field Length Check   | 213 |

| 21. C2 Interface                                   | 214 |

| 21.1. C2 Interface Registers                       | 214 |

| 21.2. C2 Pin Sharing                               | 216 |

| Document Change List                               | 217 |

| Contact Information                                | 220 |

## **1.1. Ordering Information**

The following features are common to all devices in this family:

- 25 MHz system clock and 25 MIPS throughput (peak)

- 256 bytes of internal RAM

- Enhanced SPI peripheral

- Enhanced UART peripheral

- Three Timers

- Three Programmable Counter Array channels

- Internal 24.5 MHz oscillator

- Internal Voltage Regulator

- 12-bit, 200 ksps ADC

- Internal Voltage Reference and Temperature Sensor

- One Analog Comparator

Table 1.1 shows the features that differentiate the devices in this family.

#### Table 1.1. Product Selection Guide (Recommended for New Designs)

| Ordering Part Number | Flash Memory (kB) | Port I/Os | LIN          | Package | Ordering Part Number | Flash Memory (kB) | Port I/Os | LIN          | Package  |

|----------------------|-------------------|-----------|--------------|---------|----------------------|-------------------|-----------|--------------|----------|

| C8051F520-C-IM       | 8                 | 6         | $\checkmark$ | DFN-10  | C8051F534-C-IM       | 4                 | 16        | —            | QFN-20   |

| C8051F521-C-IM       | 8                 | 6         |              | DFN-10  | C8051F536-C-IM       | 2                 | 16        | $\checkmark$ | QFN-20   |

| C8051F523-C-IM       | 4                 | 6         | $\checkmark$ | DFN-10  | C8051F537-C-IM       | 2                 | 16        |              | QFN-20   |

| C8051F524-C-IM       | 4                 | 6         |              | DFN-10  | C8051F530-C-IT       | 8                 | 16        | $\checkmark$ | TSSOP-20 |

| C8051F526-C-IM       | 2                 | 6         | $\checkmark$ | DFN-10  | C8051F531-C-IT       | 8                 | 16        |              | TSSOP-20 |

| C8051F527-C-IM       | 2                 | 6         |              | DFN-10  | C8051F533-C-IT       | 4                 | 16        | $\checkmark$ | TSSOP-20 |

| C8051F530-C-IM       | 8                 | 16        | $\checkmark$ | QFN-20  | C8051F534-C-IT       | 4                 | 16        |              | TSSOP-20 |

| C8051F531-C-IM       | 8                 | 16        |              | QFN-20  | C8051F536-C-IT       | 2                 | 16        | $\checkmark$ | TSSOP-20 |

| C8051F533-C-IM       | 4                 | 16        | $\checkmark$ | QFN-20  | C8051F537-C-IT       | 2                 | 16        |              | TSSOP-20 |

All devices in Table 1.1 are also available in an automotive version. For the automotive version, the -I in the ordering part number is replaced with -A. For example, the automotive version of the C8051F520-C-IM is the C8051F520-C-AM.

The -AM and -AT devices receive full automotive quality production status, including AEC-Q100 qualification (fault coverage report available upon request), registration with International Material Data System (IMDS) and Part Production Approval Process (PPAP) documentation. PPAP documentation is available at www.silabs.com with a registered NDA and approved user account. The -AM and -AT devices enable high volume automotive OEM applications with their enhanced testing and processing. Please contact Silicon Labs sales for more information regarding -AM and -AT devices for your automotive project.

### 2.2. Electrical Characteristics

#### Table 2.2. Global DC Electrical Characteristics

-40 to +125 °C, 25 MHz System Clock unless otherwise specified. Typical values are given at 25 °C

| Parameter                                               | Conditions                                                                                                                                                                                           | Min                                         | Тур                                                | Мах                  | Units                                  |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------|----------------------|----------------------------------------|

| Supply Input Voltage (V <sub>REGIN</sub> ) <sup>1</sup> | Output Current <u>&lt;</u> 1 mA<br>C8051F52x/53x<br>C8051F52xA/53xA<br>C8051F52x-C/53x-C                                                                                                             | 2.7<br>1.8 <sup>1</sup><br>2.0 <sup>1</sup> |                                                    | 5.25<br>5.25<br>5.25 | V<br>V<br>V                            |

| Digital Supply Voltage (V <sub>DD</sub> )               | C8051F52x/53x<br>C8051F52xA/53xA<br>C8051F52x-C/53x-C                                                                                                                                                | 2.0<br>1.8<br>2.0                           |                                                    | 2.7<br>2.7<br>2.75   | V<br>V<br>V                            |

| Core Supply RAM Data Retention<br>Voltage               |                                                                                                                                                                                                      | _                                           | 1.5                                                |                      | V                                      |

| SYSCLK (System Clock) <sup>2</sup>                      |                                                                                                                                                                                                      | 0                                           | —                                                  | 25                   | MHz                                    |

| Specified Operating Temperature Range                   |                                                                                                                                                                                                      | -40                                         | —                                                  | +125                 | °C                                     |

| Digital Supply Current—CPU Active (Nor                  | mal Mode, fetching instructions                                                                                                                                                                      | s from F                                    | lash)                                              |                      |                                        |

| I <sub>DD</sub> <sup>3,4</sup>                          | V <sub>DD</sub> = 2.1 V:<br>Clock = 32 kHz<br>Clock = 200 kHz<br>Clock = 1 MHz<br>Clock = 25 MHz<br>V <sub>DD</sub> = 2.6 V:<br>Clock = 32 kHz<br>Clock = 200 kHz<br>Clock = 1 MHz<br>Clock = 25 MHz |                                             | 13<br>60<br>0.28<br>5.1<br>22<br>105<br>0.5<br>7.3 | <br>9<br><br>13      | μΑ<br>μΑ<br>mA<br>mA<br>μΑ<br>μΑ<br>mA |

| I <sub>DD</sub> Frequency Sensitivity <sup>3,5</sup>    | T = 25 °C:<br>$V_{DD}$ = 2.1 V, F $\leq$ 12 MHz<br>$V_{DD}$ = 2.1 V, F > 12 MHz<br>$V_{DD}$ = 2.6 V, F $\leq$ 12 MHz<br>$V_{DD}$ = 2.6 V, F > 12 MHz                                                 | <br><br>                                    | 0.276<br>0.140<br>0.424<br>0.184                   |                      | mA/MHz<br>mA/MHz<br>mA/MHz<br>mA/MHz   |

#### Notes:

- 1. For more information on  $V_{\mbox{REGIN}}$  characteristics, see Table 2.6 on page 30.

- 2. SYSCLK must be at least 32 kHz to enable debugging.

- 3. Based on device characterization data; Not production tested.

- 4. Does not include internal oscillator or internal regulator supply current.

- 5. I<sub>DD</sub> can be estimated for frequencies <= 12 MHz by multiplying the frequency of interest by the frequency sensitivity number for that range. When using these numbers to estimate I<sub>DD</sub> > 12 MHz, the estimate should be the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number. For example: V<sub>DD</sub> = 2.6 V; F = 20 MHz, I<sub>DD</sub> = 7.3 mA (25 MHz 20 MHz) x 0.184 mA/MHz = 6.38 mA.

- 6. Idle  $I_{DD}$  can be estimated for frequencies <= 1 MHz by multiplying the frequency of interest by the frequency sensitivity number for that range. When using these numbers to estimate  $I_{DD} > 1$  MHz, the estimate should be the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number. For example:  $V_{DD} = 2.6$  V; F= 5 MHz, Idle  $I_{DD} = 3$  mA (25 MHz– 5 MHz) x 118 µA/MHz = 0.64 mA.

#### Table 2.3. ADC0 Electrical Characteristics

$V_{DD}$  = 2.1 V,  $V_{REF}$  = 1.5 V (REFSL=0), -40 to +125 °C unless otherwise specified.

| Parameter                                  | Conditions                         | Min       | Тур       | Max                | Units  |

|--------------------------------------------|------------------------------------|-----------|-----------|--------------------|--------|

| DC Accuracy                                |                                    |           |           |                    |        |

| Resolution                                 |                                    |           | 12        |                    | bits   |

| Integral Nonlinearity                      |                                    | —         | —         | ±3                 | LSB    |

| Differential Nonlinearity                  | Guaranteed Monotonic               |           |           | ±1                 | LSB    |

| Offset Error <sup>1</sup>                  |                                    | -10       | ±1        | +10                | LSB    |

| Full Scale Error                           |                                    | -20       | ±1        | +20                | LSB    |

| Dynamic Performance (10 kHz sine           | e-wave Single-ended input, 0 to    | 1 dB belo | ow Full S | cale, 200 k        | sps)   |

| Signal-to-Noise Plus Distortion            |                                    | 60        | 66        |                    | dB     |

| Total Harmonic Distortion                  | Up to the 5 <sup>th</sup> harmonic | —         | 74        | —                  | dB     |

| Spurious-Free Dynamic Range                |                                    | —         | 88        | —                  | dB     |

| Conversion Rate                            |                                    |           |           |                    |        |

| SAR Conversion Clock                       |                                    |           |           | 3                  | MHz    |

| Burst Mode Oscillator                      |                                    | —         | —         | 27                 | MHz    |

| Conversion Time in SAR Clocks <sup>2</sup> |                                    | —         | 13        | —                  | clocks |

| Track/Hold Acquisition Time <sup>3,6</sup> |                                    | 1         | —         | —                  | μs     |

| Throughput Rate <sup>4</sup>               |                                    |           |           | 200                | ksps   |

| Analog Inputs                              |                                    |           |           |                    |        |

|                                            | gain = 1.0 (default)               | 0         | —         | V <sub>REF</sub>   | V      |

| ADC Input Voltage Range <sup>5</sup>       | gain = n                           | 0         | —         | $V_{REF}$ / n      |        |

| Absolute Pin Voltage wrt to GND            |                                    | 0         |           | V <sub>REGIN</sub> | V      |

| Sampling Capacitance                       |                                    |           | 24        | _                  | pF     |

| Input Multiplexer Impedance                |                                    | —         | 1.5       | —                  | kΩ     |

| Power Specifications                       |                                    |           |           |                    |        |

| Power Supply Current (from VDD)            | Operating Mode, 200 ksps           | _         | 1050      | 1400               | μA     |

| Burst Mode (Idle)                          |                                    | —         | 930       | —                  | μA     |

| Power-on Time                              |                                    | —         | 5         | —                  | μs     |

| Power Supply Rejection                     |                                    | —         | 1         | _                  | mV/V   |

1. Represents one standard deviation from the mean. Offset and full-scale error can be removed to calibration.

2. An additional 2 FCLK cycles are required to start and complete a conversion.

**3.** Additional tracking time may be required depending on the output impedance connected to the ADC input. See Section "4.3.6. Settling Time Requirements" on page 60.

4. An increase in tracking time will decrease the ADC throughput.

5. See Section "4.4. Selectable Gain" on page 60 for more information about setting the gain.

Additional tracking time might be needed ifVDD < 2.0 V; See Section "11.2.1. VDD Monitor Thresholds and Minimum VDD" on page 108 for minimum V<sub>DD</sub> requirements.

For example, the initial example in this section requires a gain of 0.44 to convert 5 V full scale to 2.2 V full scale. Using Equation 4.3:

$$GAIN = \left(0.44 - GAINADD \times \left(\frac{1}{64}\right)\right) \times 4096$$

If GAINADD is set to 1, this makes the equation:

$$GAIN = \left(0.44 - 1 \times \left(\frac{1}{64}\right)\right) \times 4096 = 0.424 \times 4096 = 1738 = 0x06CA$$

The actual gain from setting GAINADD to 1 and ADC0GNH and ADC0GNL to 0x6CA is 0.4399. A similar gain can be achieved if GAINADD is set to 0 with a different value for ADC0GNH and ADC0GNL.

#### 4.4.2. Setting the Gain Value

The three programmable gain registers are accessed indirectly using the ADC0H and ADC0L registers when the GAINEN bit (ADC0CF.0) bit is set. ADC0H acts as the address register, and ADC0L is the data register. The programmable gain registers can only be written to and cannot be read. See Gain Register Definition 4.1, Gain Register Definition 4.2, and Gain Register Definition 4.3 for more information.

The gain is programmed using the following steps:

- 1. Set the GAINEN bit (ADC0CF.0)

- 2. Load the ADC0H with the ADC0GNH, ADC0GNL, or ADC0GNA address.

- 3. Load ADC0L with the desired value for the selected gain register.

- 4. Reset the GAINEN bit (ADC0CF.0)

#### Notes:

- 1. An ADC conversion should not be performed while the GAINEN bit is set.

- 2. Even with gain enabled, the maximum input voltage must be less than V<sub>REGIN</sub> and the maximum voltage of the signal after gain must be less than or equal to V<sub>REF</sub>.

In code, changing the value to 0.44 gain from the previous example looks like:

```

// in 'C':

ADC0CF |= 0x01;// GAINEN = 1

ADC0H = 0x04;// Load the ADC0GNH address

ADC0L = 0x6C;// Load the upper byte of 0x6CA to ADC0GNH

ADC0H = 0x07;// Load the ADC0GNL address

ADC0L = 0xA0;// Load the lower nibble of 0x6CA to ADC0GNL

ADC0H = 0x08;// Load the ADC0GNA address

ADC0L = 0x01;// Set the GAINADD bit

ADC0CF &= ~0x01;// GAINEN = 0

```

; in assembly ORL ADC0CF,#01H ; GAINEN = 1 MOV ADC0H,#04H; Load the ADC0GNH address MOV ADC0L,#06CH ; Load the upper byte of 0x6CA to ADC0GNH MOV ADC0H,#07H; Load the ADC0GNL address MOV ADC0L,#0A0H ; Load the lower nibble of 0x6CA to ADC0GNL MOV ADC0L,#0A0H ; Load the ADC0GNA address MOV ADC0H,#08H; Load the ADC0GNA address MOV ADC0L,#01H ; Set the GAINADD bit ANL ADC0CF,#0FEH ; GAINEN = 0

### SFR Definition 4.4. ADC0MX: ADC0 Channel Select

| R/W     | R/W                     | R/W     | R/W             | R/W     | R/W   | R/W  | R/W  | Reset Value |

|---------|-------------------------|---------|-----------------|---------|-------|------|------|-------------|

| -       | -                       | -       |                 |         | AD0MX |      |      | 00011111    |

| Bit7    | Bit6                    | Bit5    | Bit4            | Bit3    | Bit2  | Bit1 | Bit0 | SFR Address |

|         |                         |         |                 |         |       |      |      | 0xBB        |

| 107 E.  |                         |         |                 |         |       |      |      |             |

|         | UNUSED. Re<br>AD0MX4–0: |         |                 |         |       |      |      |             |

| 1154-0. |                         | AIVIOAU | rosilive inpi   |         | 1     |      |      |             |

|         | AD0MX4-0                |         | ADC0 Input      | Channel |       |      |      |             |

|         | 00000                   |         | P0.0            |         |       |      |      |             |

|         | 00001                   |         | P0.1            |         |       |      |      |             |

|         | 00010                   |         | P0.2            |         |       |      |      |             |

|         | 00011                   |         | P0.3            |         |       |      |      |             |

|         | 00100                   |         | P0.4            |         |       |      |      |             |

|         | 00101                   |         | P0.5            |         |       |      |      |             |

|         | 00110                   |         | P0.6*           |         |       |      |      |             |

|         | 00111                   |         | P0.7*           |         |       |      |      |             |

|         | 01000                   |         | P1.0*           |         |       |      |      |             |

|         | 01001                   |         | P1.1*           |         |       |      |      |             |

|         | 01010                   |         | P1.2*           |         |       |      |      |             |

|         | 01011                   |         | P1.3*           |         |       |      |      |             |

|         | 01100                   |         | P1.4*           |         |       |      |      |             |

|         | 01101                   |         | P1.5*           |         |       |      |      |             |

|         | 01110                   |         | P1.6*           |         |       |      |      |             |

|         | 01111                   |         | P1.7*           |         |       |      |      |             |

|         | 11000                   |         | Temp Senso      | or      |       |      |      |             |

|         | 11001                   |         | V <sub>DD</sub> |         |       |      |      |             |

|         | 11010 - 1111            |         | GND             |         |       |      |      |             |

#### 4.5.1. Window Detector In Single-Ended Mode

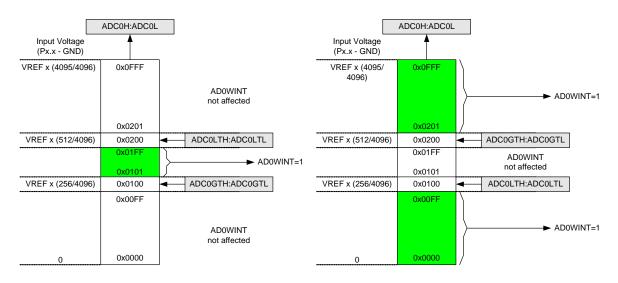

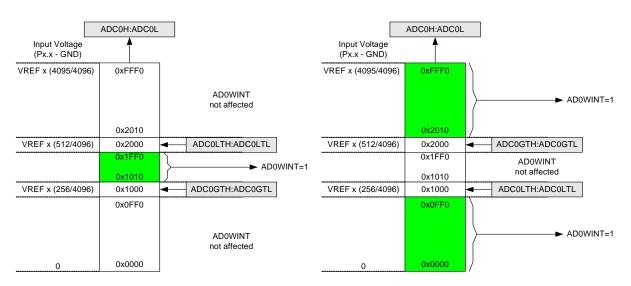

Figure 4.7 shows two example window comparisons for right-justified data with ADC0LTH:ADC0LTL = 0x0200 (512d) and ADC0GTH:ADC0GTL = 0x0100 (256d). The input voltage can range from 0 to V<sub>RFF</sub> x (4095/4096) with respect to GND, and is represented by a 12-bit unsigned integer value. The repeat count is set to one. In the left example, an AD0WINT interrupt will be generated if the ADC0 conversion word (ADC0H:ADC0L) is within the range defined by ADC0GTH:ADC0GTL and ADC0LTH:ADC0LTL (if 0x0100 < ADC0H:ADC0L < 0x0200). In the right example, and AD0WINT interrupt will be generated if the ADC0 conversion word is outside of the range defined by the ADC0GT and ADC0LT registers (if ADC0H:ADC0L < 0x0100 or ADC0H:ADC0L > 0x0200). Figure 4.8 shows an example using left-justified data with the same comparison values.

Figure 4.7. ADC Window Compare Example: Right-Justified Single-Ended Data

Figure 4.8. ADC Window Compare Example: Left-Justified Single-Ended Data

| Mnemonic                    | Description                                         | Bytes | Clock<br>Cycles |

|-----------------------------|-----------------------------------------------------|-------|-----------------|

| <b>Boolean Manipulation</b> |                                                     |       |                 |

| CLR C                       | Clear Carry                                         | 1     | 1               |

| CLR bit                     | Clear direct bit                                    | 2     | 2               |

| SETB C                      | Set Carry                                           | 1     | 1               |

| SETB bit                    | Set direct bit                                      | 2     | 2               |

| CPLC                        | Complement Carry                                    | 1     | 1               |

| CPL bit                     | Complement direct bit                               | 2     | 2               |

| ANL C, bit                  | AND direct bit to Carry                             | 2     | 2               |

| ANL C, /bit                 | AND complement of direct bit to Carry               | 2     | 2               |

| ORL C, bit                  | OR direct bit to carry                              | 2     | 2               |

| ORL C, /bit                 | OR complement of direct bit to Carry                | 2     | 2               |

| MOV C, bit                  | Move direct bit to Carry                            | 2     | 2               |

| MOV bit, C                  | Move Carry to direct bit                            | 2     | 2               |

| JC rel                      | Jump if Carry is set                                | 2     | 2/3             |

| JNC rel                     | Jump if Carry is not set                            | 2     | 2/3             |

| JB bit, rel                 | Jump if direct bit is set                           | 3     | 3/4             |

| JNB bit, rel                | Jump if direct bit is not set                       | 3     | 3/4             |

| JBC bit, rel                | Jump if direct bit is set and clear bit             | 3     | 3/4             |

| Program Branching           |                                                     |       |                 |

| ACALL addr11                | Absolute subroutine call                            | 2     | 3               |

| LCALL addr16                | Long subroutine call                                | 3     | 4               |

| RET                         | Return from subroutine                              | 1     | 5               |

| RETI                        | Return from interrupt                               | 1     | 5               |

| AJMP addr11                 | Absolute jump                                       | 2     | 3               |

| LJMP addr16                 | Long jump                                           | 3     | 4               |

| SJMP rel                    | Short jump (relative address)                       | 2     | 3               |

| JMP @A+DPTR                 | Jump indirect relative to DPTR                      | 1     | 3               |

| JZ rel                      | Jump if A equals zero                               | 2     | 2/3             |

| JNZ rel                     | Jump if A does not equal zero                       | 2     | 2/3             |

| CJNE A, direct, rel         | Compare direct byte to A and jump if not equal      | 3     | 4/5             |

| CJNE A, #data, rel          | Compare immediate to A and jump if not equal        | 3     | 3/4             |

| CJNE Rn, #data, rel         | Compare immediate to Register and jump if not equal | 3     | 3/4             |

| CJNE @Ri, #data, rel        | Compare immediate to indirect and jump if not equal | 3     | 4/5             |

| DJNZ Rn, rel                | Decrement Register and jump if not zero             | 2     | 2/3             |

| DJNZ direct, rel            | Decrement direct byte and jump if not zero          | 3     | 3/4             |

| NOP                         | No operation                                        | 1     | 1               |

### Table 8.1. CIP-51 Instruction Set Summary (Continued)

| R/W                     | R/W                                                                                                                                                              | R/W                                                                                                                         | R/W                                                                                                                      | R/W                                                                                                                 | R/W                                                                                                  | R/W                                    | R                                   | Reset Value       |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------------------------|-------------------|

| CY                      | AC                                                                                                                                                               | F0                                                                                                                          | RS1                                                                                                                      | RS0                                                                                                                 | OV                                                                                                   | F1                                     | PARITY                              | 0000000           |

| Bit7                    | Bit6                                                                                                                                                             | Bit5                                                                                                                        | Bit4                                                                                                                     | Bit3                                                                                                                | Bit2                                                                                                 | Bit1                                   | Bit0                                | Bit<br>Addressabl |

|                         |                                                                                                                                                                  |                                                                                                                             |                                                                                                                          |                                                                                                                     |                                                                                                      |                                        | SFR Address                         |                   |

| Bit7:                   | CY: Carry                                                                                                                                                        | Flag.                                                                                                                       |                                                                                                                          |                                                                                                                     |                                                                                                      |                                        |                                     |                   |

|                         |                                                                                                                                                                  | •                                                                                                                           | the last arithmet                                                                                                        | tic operatio                                                                                                        | n resulted i                                                                                         | n a carry (                            | addition) or a                      | a borrow          |

|                         |                                                                                                                                                                  |                                                                                                                             | eared to 0 by all                                                                                                        | other arith                                                                                                         | metic opera                                                                                          | ations.                                |                                     |                   |

| Bit6:                   | AC: Auxilia                                                                                                                                                      |                                                                                                                             |                                                                                                                          |                                                                                                                     |                                                                                                      |                                        |                                     |                   |

|                         |                                                                                                                                                                  |                                                                                                                             | he last arithmeti                                                                                                        |                                                                                                                     |                                                                                                      |                                        |                                     |                   |

|                         |                                                                                                                                                                  |                                                                                                                             | e high order nib                                                                                                         | ble. It is cl                                                                                                       | eared to 0 b                                                                                         | by all other                           | r arithmetic o                      | perations.        |

| Bit5:                   | F0: User F                                                                                                                                                       |                                                                                                                             |                                                                                                                          |                                                                                                                     |                                                                                                      |                                        |                                     |                   |

|                         |                                                                                                                                                                  |                                                                                                                             | able, general pu                                                                                                         | urpose flag                                                                                                         | for use und                                                                                          | der softwa                             | re control.                         |                   |

| Bits4–3:                |                                                                                                                                                                  |                                                                                                                             | Bank Select.                                                                                                             | I                                                                                                                   |                                                                                                      |                                        |                                     |                   |

|                         | I nese bits                                                                                                                                                      | select wr                                                                                                                   | nich register ban                                                                                                        | ik is used o                                                                                                        | uring regist                                                                                         | ter access                             | es.                                 |                   |

|                         |                                                                                                                                                                  | <b>D</b> 00                                                                                                                 |                                                                                                                          |                                                                                                                     |                                                                                                      |                                        |                                     |                   |

|                         |                                                                                                                                                                  |                                                                                                                             | Dogistor Book                                                                                                            | 0 A A A                                                                                                             | 000                                                                                                  |                                        |                                     |                   |

|                         | RS1                                                                                                                                                              | RS0                                                                                                                         | Register Bank                                                                                                            |                                                                                                                     |                                                                                                      |                                        |                                     |                   |

|                         | 0                                                                                                                                                                | 0                                                                                                                           | 0                                                                                                                        | 0x00–0x0                                                                                                            | )7                                                                                                   |                                        |                                     |                   |

|                         | 0<br>0                                                                                                                                                           | 0<br>1                                                                                                                      | 0                                                                                                                        | 0x00–0x0<br>0x08–0x0                                                                                                | )7<br>)F                                                                                             |                                        |                                     |                   |

|                         | 0<br>0<br>1                                                                                                                                                      | 0<br>1<br>0                                                                                                                 | 0<br>1<br>2                                                                                                              | 0x00-0x0<br>0x08-0x0<br>0x10-0x1                                                                                    | )7<br>)F<br>7                                                                                        |                                        |                                     |                   |

|                         | 0<br>0<br>1                                                                                                                                                      | 0<br>1                                                                                                                      | 0                                                                                                                        | 0x00–0x0<br>0x08–0x0                                                                                                | )7<br>)F<br>7                                                                                        |                                        |                                     |                   |

| Bit2:                   | 0<br>0<br>1<br>1                                                                                                                                                 | 0<br>1<br>0<br>1                                                                                                            | 0<br>1<br>2                                                                                                              | 0x00-0x0<br>0x08-0x0<br>0x10-0x1                                                                                    | )7<br>)F<br>7                                                                                        |                                        |                                     |                   |

| Bit2:                   | 0<br>0<br>1<br>1<br>1<br>0 <b>V</b> : Overfl                                                                                                                     | 0<br>1<br>0<br>1<br>ow Flag.                                                                                                | 0<br>1<br>2                                                                                                              | 0x00-0x0<br>0x08-0x0<br>0x10-0x1<br>0x18-0x1                                                                        | )7<br>)F<br>7<br>F                                                                                   |                                        |                                     |                   |

| Bit2:                   | 0<br>0<br>1<br>1<br>0<br>V: Overfl<br>This bit is :                                                                                                              | 0<br>1<br>0<br>1<br>ow Flag.<br>set to 1 ur                                                                                 | 0<br>1<br>2<br>3                                                                                                         | 0x00-0x0<br>0x08-0x0<br>0x10-0x1<br>0x18-0x1                                                                        | 07<br>0F<br>7<br>F<br>ances:                                                                         | nge overflo                            | DW.                                 |                   |

| Bit2:                   | 0<br>0<br>1<br>1<br><b>OV</b> : Overfl<br>This bit is :<br>• An ADD,                                                                                             | 0<br>1<br>0<br>1<br>ow Flag.<br>set to 1 ur<br>ADDC, or                                                                     | 0<br>1<br>2<br>3<br>nder the followin                                                                                    | 0x00-0x0<br>0x08-0x0<br>0x10-0x1<br>0x18-0x1<br>og circumst<br>on causes                                            | 07<br>0F<br>7<br>F<br>ances:<br>a sign-char                                                          |                                        |                                     |                   |

| Bit2:                   | 0<br>0<br>1<br>1<br><b>OV</b> : Overfil<br>This bit is s<br>• An ADD,<br>• A MUL in<br>• A DIV ins                                                               | 0<br>1<br>0<br>1<br>ow Flag.<br>set to 1 ur<br>ADDC, of<br>struction<br>struction c                                         | 0<br>1<br>2<br>3<br>nder the followin<br>r SUBB instructi<br>results in an ove<br>auses a divide-t                       | 0x00-0x0<br>0x08-0x0<br>0x10-0x1<br>0x18-0x1<br>on causes<br>erflow (resu                                           | 07<br>0F<br>7<br>F<br>ances:<br>a sign-char<br>ult is greate<br>ndition.                             | r than 255                             | ).                                  |                   |

| Bit2:                   | 0<br>0<br>1<br>1<br><b>OV</b> : Overfil<br>This bit is s<br>• An ADD,<br>• A MUL in<br>• A DIV ins                                                               | 0<br>1<br>0<br>1<br>ow Flag.<br>set to 1 ur<br>ADDC, of<br>struction<br>struction c                                         | 0<br>1<br>2<br>3<br>nder the followin<br>r SUBB instructi<br>results in an ove                                           | 0x00-0x0<br>0x08-0x0<br>0x10-0x1<br>0x18-0x1<br>on causes<br>erflow (resu                                           | 07<br>0F<br>7<br>F<br>ances:<br>a sign-char<br>ult is greate<br>ndition.                             | r than 255                             | ).                                  | in all othe       |

|                         | 0<br>0<br>1<br>1<br><b>OV</b> : Overfl<br>This bit is a<br>• An ADD,<br>• A MUL in<br>• A DIV ins<br>The OV bit<br>cases.                                        | 0<br>1<br>0<br>1<br>set to 1 ur<br>ADDC, of<br>struction<br>struction c<br>is cleared                                       | 0<br>1<br>2<br>3<br>nder the followin<br>r SUBB instructi<br>results in an ove<br>auses a divide-t                       | 0x00-0x0<br>0x08-0x0<br>0x10-0x1<br>0x18-0x1<br>on causes<br>erflow (resu                                           | 07<br>0F<br>7<br>F<br>ances:<br>a sign-char<br>ult is greate<br>ndition.                             | r than 255                             | ).                                  | in all othe       |

|                         | 0<br>0<br>1<br>1<br><b>OV</b> : Overfl<br>This bit is a<br>• An ADD,<br>• A MUL in<br>• A DIV ins<br>The OV bit<br>cases.<br><b>F1</b> : User F                  | 0<br>1<br>0<br>1<br>set to 1 ur<br>ADDC, o<br>struction<br>truction c<br>: is cleared<br>lag 1.                             | 0<br>1<br>2<br>3<br>nder the followin<br>r SUBB instructi<br>results in an ove<br>auses a divide-t<br>d to 0 by the AD   | 0x00-0x0<br>0x08-0x0<br>0x10-0x1<br>0x18-0x1<br>on causes<br>erflow (resu<br>by-zero con<br>D, ADDC,                | 07<br>0F<br>7<br>F<br>ances:<br>a sign-char<br>ult is greate<br>ndition.<br>SUBB, MU                 | r than 255<br>L, and DI∖               | ).<br>′ instructions                | in all othe       |

| Bit1:                   | 0<br>0<br>1<br>1<br>1<br>OV: Overfl<br>This bit is s<br>• An ADD,<br>• A MUL in<br>• A DIV ins<br>The OV bit<br>cases.<br>F1: User F<br>This is a b              | 0<br>1<br>0<br>1<br>set to 1 ur<br>ADDC, of<br>struction<br>struction c<br>is cleared<br>lag 1.                             | 0<br>1<br>2<br>3<br>3<br>SUBB instructi<br>results in an ove<br>auses a divide-t<br>d to 0 by the AD<br>able, general pu | 0x00-0x0<br>0x08-0x0<br>0x10-0x1<br>0x18-0x1<br>on causes<br>erflow (resu<br>by-zero con<br>D, ADDC,                | 07<br>0F<br>7<br>F<br>ances:<br>a sign-char<br>ult is greate<br>ndition.<br>SUBB, MU                 | r than 255<br>L, and DI∖               | ).<br>′ instructions                | in all othe       |

| Bit2:<br>Bit1:<br>Bit0: | 0<br>0<br>1<br>1<br>1<br>OV: Overfl<br>This bit is s<br>• An ADD,<br>• A MUL in<br>• A DIV ins<br>The OV bit<br>cases.<br>F1: User F<br>This is a b<br>PARITY: P | 0<br>1<br>0<br>1<br>set to 1 ur<br>ADDC, of<br>struction<br>struction c<br>is cleared<br>lag 1.<br>it-address<br>arity Flag | 0<br>1<br>2<br>3<br>3<br>SUBB instructi<br>results in an ove<br>auses a divide-t<br>d to 0 by the AD<br>able, general pu | 0x00-0x0<br>0x08-0x0<br>0x10-0x1<br>0x18-0x1<br>on causes<br>erflow (resu<br>by-zero con<br>D, ADDC,<br>urpose flag | 07<br>0F<br>7<br>F<br>ances:<br>a sign-char<br>ult is greate<br>ndition.<br>SUBB, MUI<br>for use und | r than 255<br>L, and DI∖<br>der softwa | ).<br>/ instructions<br>re control. |                   |

SFRs used to configure and access the sub-systems unique to the MCU. This allows the addition of new functionality while retaining compatibility with the MCS-51<sup>™</sup> instruction set. Table 9.1 lists the SFRs implemented in the CIP-51 System Controller.

The SFR registers are accessed anytime the direct addressing mode is used to access memory locations from 0x80 to 0xFF. SFRs with addresses ending in 0x0 or 0x8 (e.g. P0, TCON, IE, etc.) are bit-addressable as well as byte-addressable. All other SFRs are byte-addressable only. Unoccupied addresses in the SFR space are reserved for future use. Accessing these areas will have an indeterminate effect and should be avoided. Refer to the corresponding pages of the data sheet, as indicated in Table 9.2, for a detailed description of each register.

| F8 | SPI0CN        | PCA0L    | PCA0H    | PCA0CPL0 | PCA0CPH0 |         |         | VDDMON |

|----|---------------|----------|----------|----------|----------|---------|---------|--------|

| F0 | В             | POMDIN   | P1MDIN   |          |          |         | EIP1    |        |

| E8 | ADC0CN        | PCA0CPL1 | PCA0CPH1 | PCA0CPL2 | PCA0CPH2 |         |         | RSTSRC |

| E0 | ACC           | XBR0     | XBR1     |          | IT01CF   |         | EIE1    |        |

| D8 | PCA0CN        | PCA0MD   | PCA0CPM0 | PCA0CPM1 | PCA0CPM2 |         |         |        |

| D0 | PSW           | REF0CN   |          |          | P0SKIP   | P1SKIP  |         | P0MAT  |

| C8 | TMR2CN        | REG0CN   | TMR2RLL  | TMR2RLH  | TMR2L    | TMR2H   |         | P1MAT  |

| C0 |               |          |          | ADC0GTL  | ADC0GTH  | ADC0LTL | ADC0LTH | P0MASK |

| B8 | IP            |          | ADC0TK   | ADC0MX   | ADC0CF   | ADC0L   | ADC0    | P1MASK |

| B0 | OSCIFIN       | OSCXCN   | OSCICN   | OSCICL   |          |         |         | FLKEY  |

| A8 | IE            | CLKSEL   |          |          |          |         |         |        |

| A0 |               | SPI0CFG  | SPI0CKR  | SPI0DAT  | POMDOUT  | P1MDOUT |         |        |

| 98 | SCON0         | SBUF0    |          | CPT0CN   |          | CPT0MD  |         | CPT0MX |

| 90 | P1            |          | LINADDR  | LINDATA  |          | LINCF   |         |        |

| 88 | TCON          | TMOD     | TL0      | TL1      | TH0      | TH1     | CKCON   | PSCTL  |

| 80 | P0            | SP       | DPL      | DPH      |          |         |         | PCON   |

|    | 0(8)          | 1(9)     | 2(A)     | 3(B)     | 4(C)     | 5(D)    | 6(E)    | 7(F)   |

|    | (bit address- |          |          |          |          |         |         |        |

|    | able)         |          |          |          |          |         |         |        |

#### **10.4.** Interrupt Register Descriptions

The SFRs used to enable the interrupt sources and set their priority level are described below. Refer to the data sheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

### SFR Definition 10.1. IE: Interrupt Enable

| R/W    | R/W                            | R/W           | R/W          | R/W           | R/W            | R/W           | R/W          | Reset Value  |

|--------|--------------------------------|---------------|--------------|---------------|----------------|---------------|--------------|--------------|

| EA     | ESPI0                          | ET2           | ES0          | ET1           | EX1            | ET0           | EX0          | 00000000     |

| Bit7   | Bit6                           | Bit5          | Bit4         | Bit3          | Bit2           | Bit1          | Bit0         | Bit          |

|        |                                |               |              |               |                |               |              | Addressable  |

|        |                                |               |              |               |                |               | SFR Addres   | s: 0xA8      |

| Bit7:  | EA: Global I                   | nterrunt En   | able         |               |                |               |              |              |

| Biti . | This bit glob                  |               |              | ll interrupts | . It override: | s the individ | dual interru | pt mask set- |

|        | tings.                         |               |              |               |                |               |              |              |

|        | 0: Disable al                  | l interrupt s | ources.      |               |                |               |              |              |

|        | 1: Enable ea                   |               | •            |               |                | •             |              |              |

| Bit6:  | ESPI0: Enat                    |               | •            | · ·           | <i>,</i> .     |               |              |              |

|        | This bit sets                  |               | •            | 10 interrupts | S.             |               |              |              |

|        | 0: Disable al                  |               |              |               | _              |               |              |              |

| D:45   | 1: Enable int                  |               |              | ated by SPI   | ).             |               |              |              |

| Bit5:  | ET2: Enable                    |               | •            | or 2 intorru  | nt             |               |              |              |

|        | This bit sets<br>0: Disable Ti |               |              |               | pı.            |               |              |              |

|        | 1: Enable int                  |               |              | ated by the   | TE2L or TE     | 2H flags      |              |              |

| Bit4:  | ES0: Enable                    |               | •            |               |                | Li i nago.    |              |              |

| 2      | This bit sets                  |               |              | RT0 interru   | pt.            |               |              |              |

|        | 0: Disable U                   |               | •            |               | r ·            |               |              |              |

|        | 1: Enable UA                   | ART0 interr   | upt.         |               |                |               |              |              |

| Bit3:  | ET1: Enable                    | Timer 1 Int   | errupt.      |               |                |               |              |              |

|        | This bit sets                  |               | •            | ner 1 interru | pt.            |               |              |              |

|        | 0: Disable al                  |               |              |               |                |               |              |              |

| -      | 1: Enable int                  |               |              | ated by the   | TF1 flag.      |               |              |              |

| Bit2:  | EX1: Enable                    |               | •            | 1             |                |               |              |              |

|        | This bit sets                  |               |              | ernal interri | JPt 1.         |               |              |              |

|        | 0: Disable ex<br>1: Enable ex  |               |              | te            |                |               |              |              |

| Bit1:  | ETO: Enable                    |               |              | ιο.           |                |               |              |              |

| Ditt.  | This bit sets                  |               | •            | ner 0 interru | nt             |               |              |              |

|        | 0: Disable al                  |               | •            |               | pu             |               |              |              |

|        | 1: Enable int                  |               | •            | ated by the   | TF0 flag.      |               |              |              |

| Bit0:  | EX0: Enable                    |               |              |               | U              |               |              |              |

|        | This bit sets                  | the maskin    | g of the ext | ernal interro | upt 0.         |               |              |              |

|        | 0: Disable ex                  |               | •            |               |                |               |              |              |

|        | 1: Enable ex                   | tern interru  | pt 0 reques  | ts.           |                |               |              |              |

|        |                                |               |              |               |                |               |              |              |

**Important Note:** The SPI can be operated in either 3-wire or 4-wire modes, depending on the state of the NSSMD1–NSSMD0 bits in register SPI0CN. According to the SPI mode, the NSS signal may or may not be routed to a Port pin.

### 13.2. Port I/O Initialization

Port I/O initialization consists of the following steps:

- 1. Select the input mode (analog or digital) for all Port pins, using the Port Input Mode register (PnMDIN).

- 2. Select the output mode (open-drain or push-pull) for all Port pins, using the Port Output Mode register (PnMDOUT).

- 3. Select any pins to be skipped by the I/O Crossbar using the Port Skip registers (PnSKIP).

- 4. Assign Port pins to desired peripherals using the XBRn registers.

- 5. Enable the Crossbar (XBARE = 1).

All Port pins must be configured as either analog or digital inputs. Any pins to be used as Comparator or ADC inputs should be configured as an analog inputs. When a pin is configured as an analog input, its weak pullup, digital driver, and digital receiver are disabled. This process saves power and reduces noise on the analog input. Pins configured as digital inputs may still be used by analog peripherals; however, this practice is not recommended.

Additionally, all analog input pins should be configured to be skipped by the Crossbar (accomplished by setting the associated bits in PnSKIP). Port input mode is set in the PnMDIN register, where a 1 indicates a digital input, and a 0 indicates an analog input. All pins default to digital inputs on reset. See SFR Definition 13.4 for the PnMDIN register details.

Important Note: Port 0 and Port 1 pins are 5.25 V tolerant across the operating range of V<sub>REGIN</sub>.

The output driver characteristics of the I/O pins are defined using the Port Output Mode registers (PnMD-OUT). Each Port Output driver can be configured as either open drain or push-pull. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. When the WEAKPUD bit in XBR1 is 0, a weak pullup is enabled for all Port I/O configured as open-drain. WEAKPUD does not affect the push-pull Port I/O. Furthermore, the weak pullup is turned off on an output that is driving a 0 and for pins configured for analog input mode to avoid unnecessary power dissipation.

Registers XBR0 and XBR1 must be loaded with the appropriate values to select the digital I/O functions required by the design. Setting the XBARE bit in XBR1 to 1 enables the Crossbar. Until the Crossbar is enabled, the external pins remain as standard Port I/O (in input mode), regardless of the XBRn Register settings. For given XBRn Register settings, one can determine the I/O pin-out using the Priority Decode Table.

The Crossbar must be enabled to use Port pins as standard Port I/O in output mode. **Port output drivers** are disabled while the Crossbar is disabled.

## SFR Definition 13.1. XBR0: Port I/O Crossbar Register 0

| R/W         | R/W           | R/W         | R/W          | R/W           | R/W         | R/W         | R/W          | Reset Value |

|-------------|---------------|-------------|--------------|---------------|-------------|-------------|--------------|-------------|

| -           | -             | CP0AE       | CP0E         | SYSCKE        | LINE        | SPI0E       | URT0E        | 0000000     |

| Bit7        | Bit6          | Bit5        | Bit4         | Bit3          | Bit2        | Bit1        | Bit0         | -           |

|             |               |             |              |               |             |             | SFR Address  | : 0xE1      |

| Bit7–6:     | RESERVED      | . Read = 00 | )b; Must wr  | ite 00b.      |             |             |              |             |

| Bit5:       | CP0AE: Cor    |             |              |               | nable       |             |              |             |

|             | 0: Asynchror  |             |              |               |             |             |              |             |

|             | 1: Asynchror  |             |              | •             |             |             |              |             |

| Bit4:       | CP0E: Comp    |             | •            | e             |             |             |              |             |

|             | 0: CP0 unav   |             | •            |               |             |             |              |             |

|             | 1: CP0 route  |             |              |               |             |             |              |             |

| Bit3:       | SYSCKE: /S    |             | •            |               |             |             |              |             |

|             | 0: /SYSCLK    |             | •            |               |             |             |              |             |

|             | 1: /SYSCLK    |             |              | pin.          |             |             |              |             |

| Bit2:       | LINE. Lin Ou  | •           | e            |               |             |             |              |             |

| Bit1:       | SPIOE: SPI I  |             |              |               |             |             |              |             |

|             | 0: SPI I/O ur |             | •            |               |             |             |              |             |

| <b>D</b> .' | 1: SPI I/O ro |             |              | e that the SP | I can be as | signed eith | er 3 or 4 GF | 10 pins.    |

| Bit0:       | URTOE: UAR    |             |              |               |             |             |              |             |

|             | 0: UART I/O   |             |              |               |             |             |              |             |

|             | 1: UART TX    | U, RXU rout | ea to Port p | oins (P0.3 ar | na PU.4) or | (P0.4 and I | PU.5).^      |             |

|             |               |             |              |               |             |             |              |             |

## SFR Definition 14.4. OSCXCN: External Oscillator Control

| R                                                                            | R/W                                                                                                                                                                                                                                                                                               | R/W                                                   | R/W                            | R/W                  | R/W                  | R/W      | R/W              | Reset Value |  |  |  |

|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------|----------------------|----------------------|----------|------------------|-------------|--|--|--|

| XTLVLD                                                                       |                                                                                                                                                                                                                                                                                                   | XOSCMD1 X                                             |                                | eserved              | XFCN2                | XFCN1    | XFCN0            | 00000000    |  |  |  |

| Bit7                                                                         | Bit6                                                                                                                                                                                                                                                                                              | Bit5                                                  | Bit4                           | Bit3                 | Bit2                 | Bit1     | Bit0             |             |  |  |  |

|                                                                              |                                                                                                                                                                                                                                                                                                   |                                                       |                                |                      |                      |          | SFR Address      | :: 0xB1     |  |  |  |

| Bit7:                                                                        | 0: Crystal O<br>1: Crystal O                                                                                                                                                                                                                                                                      | ystal Oscillat<br>scillator is un<br>scillator is rur | used or not y<br>nning and sta | /et stable.<br>able. |                      | (OSCMD : | = 11x.)          |             |  |  |  |

| Bits6–4:                                                                     | <b>XOSCMD2–0</b> : External Oscillator Mode Bits.<br>00x: External Oscillator circuit off.                                                                                                                                                                                                        |                                                       |                                |                      |                      |          |                  |             |  |  |  |

| 5:0                                                                          | <ul> <li>010: External CMOS Clock Mode.</li> <li>011: External CMOS Clock Mode with divide by 2 stage.</li> <li>100: RC Oscillator Mode.</li> <li>101: Capacitor Oscillator Mode.</li> <li>110: Crystal Oscillator Mode.</li> <li>111: Crystal Oscillator Mode with divide by 2 stage.</li> </ul> |                                                       |                                |                      |                      |          |                  |             |  |  |  |

| Bita                                                                         |                                                                                                                                                                                                                                                                                                   | . Read = 0b;                                          |                                |                      |                      |          |                  |             |  |  |  |

| Bits2–0:                                                                     |                                                                                                                                                                                                                                                                                                   | External Oscil<br>e table below                       | •                              | ncy Contr            | ol Bits.             |          |                  |             |  |  |  |

|                                                                              | XFCN                                                                                                                                                                                                                                                                                              | Crystal (XC                                           | SCMD = 11                      | x) RC                | (XOSCMD              | = 10x)   | C (XOSCMD = 10x) |             |  |  |  |

|                                                                              | 000                                                                                                                                                                                                                                                                                               | f ≤ 2                                                 | 20 kHz                         |                      | f ≤ 25 kH            | z        | K Factor         | r = 0.87    |  |  |  |

|                                                                              | 001                                                                                                                                                                                                                                                                                               | 20 kHz <                                              | < f ≤ 58 kHz                   | 25                   | kHz < f ≤ 5          | 50 kHz   | K Facto          | or = 2.6    |  |  |  |

|                                                                              | 010                                                                                                                                                                                                                                                                                               | 58 kHz <                                              | f ≤ 155 kHz                    | 50 I                 | kHz < f ≤ 1          | 00 kHz   | K Facto          | or = 7.7    |  |  |  |

|                                                                              | 011                                                                                                                                                                                                                                                                                               | 155 kHz <                                             | < f ≤ 415 kHz                  | 100                  | $kHz < f \le 2$      | 200 kHz  | K Facto          | or = 22     |  |  |  |