Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detailo                    |                                                                 |

|----------------------------|-----------------------------------------------------------------|

| Product Status             | Active                                                          |

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SPI, UART/USART                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT              |

| Number of I/O              | 6                                                               |

| Program Memory Size        | 2KB (2K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 256 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                    |

| Data Converters            | A/D 6x12b                                                       |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                              |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 10-VFDFN Exposed Pad                                            |

| Supplier Device Package    | 10-DFN (3x3)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f527a-im |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1. | System Overview                                                                  |    |

|----|----------------------------------------------------------------------------------|----|

|    | 1.1. Ordering Information                                                        | 14 |

|    | 1.2. CIP-51 <sup>™</sup> Microcontroller                                         | 18 |

|    | 1.2.1. Fully 8051 Compatible Instruction Set                                     | 18 |

|    | 1.2.2. Improved Throughput                                                       | 18 |

|    | 1.2.3. Additional Features                                                       | 18 |

|    | 1.2.4. On-Chip Debug Circuitry                                                   | 18 |

|    | 1.3. On-Chip Memory                                                              | 20 |

|    | 1.4. Operating Modes                                                             |    |

|    | 1.5. 12-Bit Analog to Digital Converter                                          | 22 |

|    | 1.6. Programmable Comparator                                                     | 23 |

|    | 1.7. Voltage Regulator                                                           | 23 |

|    | 1.8. Serial Port                                                                 | 23 |

|    | 1.9. Port Input/Output                                                           |    |

| 2. | Electrical Characteristics                                                       |    |

|    | 2.1. Absolute Maximum Ratings                                                    | 25 |

|    | 2.2. Electrical Characteristics                                                  |    |

|    | Pinout and Package Definitions                                                   |    |

| 4. | 12-Bit ADC (ADC0)                                                                |    |

|    | 4.1. Analog Multiplexer                                                          |    |

|    | 4.2. Temperature Sensor                                                          |    |

|    | 4.3. ADC0 Operation                                                              |    |

|    | 4.3.1. Starting a Conversion                                                     |    |

|    | 4.3.2. Tracking Modes                                                            |    |

|    | 4.3.3. Timing                                                                    |    |

|    | 4.3.4. Burst Mode                                                                |    |

|    | 4.3.5. Output Conversion Code                                                    |    |

|    | 4.3.6. Settling Time Requirements                                                |    |

|    | 4.4. Selectable Gain                                                             |    |

|    | 4.4.1. Calculating the Gain Value                                                |    |

|    | 4.4.2. Setting the Gain Value                                                    |    |

|    | 4.5. Programmable Window Detector                                                |    |

| _  | 4.5.1. Window Detector In Single-Ended Mode                                      |    |

| 5. | Voltage Reference                                                                | 72 |

|    | Voltage Regulator (REG0)                                                         |    |

|    | Comparator                                                                       |    |

| 8. | CIP-51 Microcontroller                                                           |    |

|    | 8.1. Instruction Set.                                                            |    |

|    | 8.1.1. Instruction and CPU Timing                                                |    |

|    | 8.1.2. MOVX Instruction and Program Memory                                       |    |

|    | <ul><li>8.2. Register Descriptions</li><li>8.3. Power Management Modes</li></ul> | 00 |

|    |                                                                                  |    |

|    | 8.3.1. Idle Mode                                                                 | 90 |

| Figure 13.5. Crossbar Priority Decoder with No Pins Skipped (DFN 10) 124   |

|----------------------------------------------------------------------------|

| Figure 13.6. Crossbar Priority Decoder with Some Pins Skipped (DFN 10) 125 |

| Figure 14.1. Oscillator Diagram 135                                        |

| Figure 14.2. 32 kHz External Crystal Example 140                           |

| Figure 15.1. UART0 Block Diagram 144                                       |

| Figure 15.2. UART0 Baud Rate Logic 145                                     |

| Figure 15.3. UART Interconnect Diagram 146                                 |

| Figure 15.4. 8-Bit UART Timing Diagram 146                                 |

| Figure 15.5. 9-Bit UART Timing Diagram 147                                 |

| Figure 15.6. UART Multi-Processor Mode Interconnect Diagram                |

| Figure 16.1. SPI Block Diagram 151                                         |

| Figure 16.2. Multiple-Master Mode Connection Diagram 154                   |

| Figure 16.3. 3-Wire Single Master and Slave Mode Connection Diagram        |

| Figure 16.4. 4-Wire Single Master and Slave Mode Connection Diagram        |

| Figure 16.5. Data/Clock Timing Relationship                                |

| Figure 16.6. SPI Master Timing (CKPHA = 0)                                 |

| Figure 16.7. SPI Master Timing (CKPHA = 1)                                 |

| Figure 16.8. SPI Slave Timing (CKPHA = 0)                                  |

| Figure 16.9. SPI Slave Timing (CKPHA = 1)                                  |

| Figure 17.1. LIN Block Diagram                                             |

| Figure 18.1. T0 Mode 0 Block Diagram                                       |

| Figure 18.2. T0 Mode 2 Block Diagram                                       |

| Figure 18.3. T0 Mode 3 Block Diagram                                       |

| Figure 18.4. Timer 2 16-Bit Mode Block Diagram                             |

| Figure 18.5. Timer 2 8-Bit Mode Block Diagram                              |

| Figure 18.6. Timer 2 Capture Mode Block Diagram                            |

| Figure 19.1. PCA Block Diagram                                             |

| Figure 19.2. PCA Counter/Timer Block Diagram                               |

| Figure 19.3. PCA Interrupt Block Diagram                                   |

| Figure 19.4. PCA Capture Mode Diagram                                      |

| Figure 19.5. PCA Software Timer Mode Diagram                               |

| Figure 19.6. PCA High-Speed Output Mode Diagram                            |

| Figure 19.7. PCA Frequency Output Mode                                     |

| Figure 19.8. PCA 8-Bit PWM Mode Diagram                                    |

| Figure 19.9. PCA 16-Bit PWM Mode                                           |

| Figure 19.10. PCA Module 2 with Watchdog Timer Enabled                     |

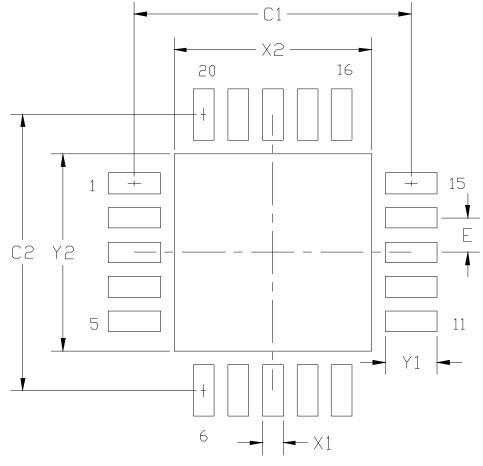

| Figure 20.1. Device Package—TSSOP 20                                       |

| Figure 20.2. Device Package—QFN 20                                         |

| Figure 20.3. Device Package—DFN 10                                         |

| Figure 21.1. Typical C2 Pin Sharing 216                                    |

|                                                                            |

## 1.1. Ordering Information

The following features are common to all devices in this family:

- 25 MHz system clock and 25 MIPS throughput (peak)

- 256 bytes of internal RAM

- Enhanced SPI peripheral

- Enhanced UART peripheral

- Three Timers

- Three Programmable Counter Array channels

- Internal 24.5 MHz oscillator

- Internal Voltage Regulator

- 12-bit, 200 ksps ADC

- Internal Voltage Reference and Temperature Sensor

- One Analog Comparator

Table 1.1 shows the features that differentiate the devices in this family.

#### Table 1.1. Product Selection Guide (Recommended for New Designs)

| Ordering Part Number | Flash Memory (kB) | Port I/Os | LIN          | Package | Ordering Part Number | Flash Memory (kB) | Port I/Os | LIN          | Package  |

|----------------------|-------------------|-----------|--------------|---------|----------------------|-------------------|-----------|--------------|----------|

| C8051F520-C-IM       | 8                 | 6         | $\checkmark$ | DFN-10  | C8051F534-C-IM       | 4                 | 16        | —            | QFN-20   |

| C8051F521-C-IM       | 8                 | 6         | —            | DFN-10  | C8051F536-C-IM       | 2                 | 16        | $\checkmark$ | QFN-20   |

| C8051F523-C-IM       | 4                 | 6         | $\checkmark$ | DFN-10  | C8051F537-C-IM       | 2                 | 16        |              | QFN-20   |

| C8051F524-C-IM       | 4                 | 6         | —            | DFN-10  | C8051F530-C-IT       | 8                 | 16        | $\checkmark$ | TSSOP-20 |

| C8051F526-C-IM       | 2                 | 6         | $\checkmark$ | DFN-10  | C8051F531-C-IT       | 8                 | 16        |              | TSSOP-20 |

| C8051F527-C-IM       | 2                 | 6         |              | DFN-10  | C8051F533-C-IT       | 4                 | 16        | $\checkmark$ | TSSOP-20 |

| C8051F530-C-IM       | 8                 | 16        | $\checkmark$ | QFN-20  | C8051F534-C-IT       | 4                 | 16        |              | TSSOP-20 |

| C8051F531-C-IM       | 8                 | 16        | —            | QFN-20  | C8051F536-C-IT       | 2                 | 16        | $\checkmark$ | TSSOP-20 |

| C8051F533-C-IM       | 4                 | 16        | $\checkmark$ | QFN-20  | C8051F537-C-IT       | 2                 | 16        |              | TSSOP-20 |

All devices in Table 1.1 are also available in an automotive version. For the automotive version, the -I in the ordering part number is replaced with -A. For example, the automotive version of the C8051F520-C-IM is the C8051F520-C-AM.

The -AM and -AT devices receive full automotive quality production status, including AEC-Q100 qualification (fault coverage report available upon request), registration with International Material Data System (IMDS) and Part Production Approval Process (PPAP) documentation. PPAP documentation is available at www.silabs.com with a registered NDA and approved user account. The -AM and -AT devices enable high volume automotive OEM applications with their enhanced testing and processing. Please contact Silicon Labs sales for more information regarding -AM and -AT devices for your automotive project.

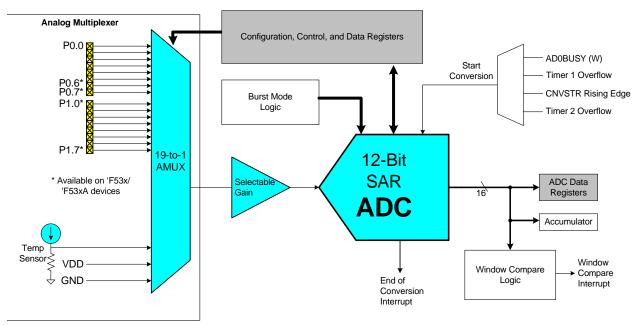

## 1.5. 12-Bit Analog to Digital Converter

The C8051F52x/F52xA/F53x/F53xA devices include an on-chip 12-bit SAR ADC with a maximum throughput of 200 ksps. The ADC system includes a configurable analog multiplexer that selects the positive ADC input, which is measured with respect to GND. Ports 0 and 1 are available as ADC inputs; additionally, the ADC includes an innovative programmable gain stage which allows the ADC to sample inputs sources greater than the VREF voltage. The on-chip Temperature Sensor output and the core supply voltage (V<sub>DD</sub>) are also available as ADC inputs. User firmware may shut down the ADC or use it in Burst Mode to save power.

Conversions can be initiated in four ways: a software command, an overflow of Timer 1, an overflow of Timer 2, or an external convert start signal. This flexibility allows the start of conversion to be triggered by software events, a periodic signal (timer overflows), or external HW signals. Conversion completions are indicated by a status bit and an interrupt (if enabled) and occur after 1, 4, 8, or 16 samples have been accumulated by a hardware accumulator. The resulting 12-bit to 16-bit data word is latched into the ADC data SFRs upon completion of a conversion. When the system clock is slow, Burst Mode allows ADC0 to automatically wake from a low power shutdown state, acquire and accumulate samples, then re-enter the low power shutdown state without CPU intervention.

Window compare registers for the ADC data can be configured to interrupt the controller when ADC data is either within or outside of a specified range. The ADC can monitor a key voltage continuously in background mode, but not interrupt the controller unless the converted data is within/outside the specified range.

Figure 1.7. 12-Bit ADC Block Diagram

### Table 2.2. Global DC Electrical Characteristics

-40 to +125 °C, 25 MHz System Clock unless otherwise specified. Typical values are given at 25 °C

| Parameter                                                 | Conditions                                          | Min     | Тур    | Max | Units  |

|-----------------------------------------------------------|-----------------------------------------------------|---------|--------|-----|--------|

| Digital Supply Current—CPU Inactive (Id                   | le Mode, not fetching instructio                    | ns from | Flash) |     |        |

| Idle I <sub>DD</sub> <sup>3,4</sup>                       | V <sub>DD</sub> = 2.1 V:                            |         |        |     |        |

|                                                           | Clock = 32 kHz                                      | —       | 8      | —   | μA     |

|                                                           | Clock = 200 kHz                                     | —       | 22     | —   | μA     |

|                                                           | Clock = 1 MHz                                       | —       | 0.09   | —   | mA     |

|                                                           | Clock = 25 MHz                                      | —       | 2.2    | 5   | mA     |

|                                                           | V <sub>DD</sub> = 2.6 V:                            |         |        |     |        |

|                                                           | Clock = 32 kHz                                      | —       | 9      | —   | μA     |

|                                                           | Clock = 200 kHz                                     | _       | 30     | _   | μA     |

|                                                           | Clock = 1 MHz                                       | _       | 0.13   | _   | mA     |

|                                                           | Clock = 25 MHz                                      | —       | 3      | 6.5 | mA     |

| Idle I <sub>DD</sub> Frequency Sensitivity <sup>3,6</sup> | T = 25 °C:                                          |         |        |     |        |

|                                                           | V <sub>DD</sub> = 2.1 V, F <u>&lt;</u> 1 MHz        | —       | 90     | —   | µA/MHz |

|                                                           | $V_{DD} = 2.1 \text{ V}, \text{ F} > 1 \text{ MHz}$ | —       | 90     | —   | µA/MHz |

|                                                           | $V_{DD} = 2.6 V, F \le 1 MHz$                       | —       | 118    | —   | µA/MHz |

|                                                           | $V_{DD} = 2.6 \text{ V}, \text{ F} > 1 \text{ MHz}$ | —       | 118    | —   | µA/MHz |

| Disital Curshy Current <sup>3</sup>                       |                                                     |         |        |     |        |

| Digital Supply Current <sup>3</sup>                       | Oscillator not running,                             |         |        |     |        |

| (Stop or Suspend Mode)                                    | V <sub>DD</sub> Monitor Disabled.                   |         | _      |     |        |

|                                                           | T = 25 °C                                           | —       | 2      | —   | μA     |

|                                                           | T = 60 °C                                           | —       | 3      | —   | μA     |

|                                                           | T = 125 °C                                          | —       | 50     | _   | μA     |

#### Notes:

- 1. For more information on  $V_{\mbox{REGIN}}$  characteristics, see Table 2.6 on page 30.

- **2.** SYSCLK must be at least 32 kHz to enable debugging.

- **3.** Based on device characterization data; Not production tested.

- 4. Does not include internal oscillator or internal regulator supply current.

- 5. I<sub>DD</sub> can be estimated for frequencies <= 12 MHz by multiplying the frequency of interest by the frequency sensitivity number for that range. When using these numbers to estimate I<sub>DD</sub> > 12 MHz, the estimate should be the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number. For example: V<sub>DD</sub> = 2.6 V; F = 20 MHz, I<sub>DD</sub> = 7.3 mA (25 MHz 20 MHz) x 0.184 mA/MHz = 6.38 mA.

- 6. Idle  $I_{DD}$  can be estimated for frequencies <= 1 MHz by multiplying the frequency of interest by the frequency sensitivity number for that range. When using these numbers to estimate  $I_{DD}$  > 1 MHz, the estimate should be the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number. For example:  $V_{DD}$  = 2.6 V; F= 5 MHz, Idle  $I_{DD}$  = 3 mA (25 MHz– 5 MHz) x 118 µA/MHz = 0.64 mA.

### **Table 2.9. Flash Electrical Characteristics**

$V_{DD}$  = 1.8 to 2.75 V; –40 to +125 °C unless otherwise specified

| Parameter              | Conditions                                           | Min                                | Тур   | Max | Units       |

|------------------------|------------------------------------------------------|------------------------------------|-------|-----|-------------|

| Flash Size             | 'F520/0A/1/1A and 'F530/0A/1/1A                      | 7680                               | _     | _   | bytes       |

|                        | 'F523/3A/4/4A and 'F533/3A/4/4A                      | 4096                               |       |     |             |

|                        | 'F526/6A/7/7A and 'F536/6A/7/7A                      | 2048                               |       |     |             |

| Endurance <sup>2</sup> | V <sub>DD</sub> ≥ V <sub>RST-HIGH</sub> <sup>1</sup> | 20 k                               | 150 k |     | Erase/Write |

| Erase Cycle Time       |                                                      | 27                                 | 32    | 38  | ms          |

| Write Cycle Time       |                                                      | 57                                 | 65    | 74  | μs          |

| V <sub>DD</sub>        | Write/Erase Operations                               | V <sub>RST-HIGH</sub> <sup>1</sup> |       |     | V           |

| Netaa                  |                                                      |                                    |       |     |             |

Notes:

See Table 2.8 on page 32 for the V<sub>RST-HIGH</sub> specification.

For –I (industrial Grade) parts, flash should be programmed (erase/write) at a minimum temperature of 0 °C for reliable flash operation across the entire temperature range of -40 to +125 °C. This minimum programming temperature does not apply to -A (Automotive Grade) parts.

#### Table 2.10. Port I/O DC Electrical Characteristics

V<sub>REGIN</sub> = 2.7 to 5.25 V, -40 to +125 °C unless otherwise specified

| Parameters       | Conditions                                                        | Min                       | Тур                     | Max                  | Units |

|------------------|-------------------------------------------------------------------|---------------------------|-------------------------|----------------------|-------|

| Output High      | I <sub>OH</sub> = –3 mA, Port I/O push-pull                       | V <sub>REGIN</sub> – 0.4  | _                       |                      | V     |

| Voltage          | I <sub>OH</sub> = −10 μA, Port I/O push-pull                      | V <sub>REGIN</sub> – 0.02 | —                       |                      |       |

|                  | I <sub>OH</sub> = –10 mA, Port I/O push-pull                      | —                         | V <sub>REGIN</sub> -0.7 | —                    |       |

| Output Low       | V <sub>REGIN</sub> = 2.7 V:                                       |                           |                         |                      |       |

| Voltage          | I <sub>OL</sub> = 70 μA                                           | —                         | —                       | 45                   |       |

|                  | l <sub>OL</sub> = 8.5 mA                                          | —                         | —                       | 550                  | mV    |

|                  | V <sub>REGIN</sub> = 5.25 V:                                      |                           |                         |                      | IIIV  |

|                  | I <sub>OL</sub> = 70 μA                                           | —                         | —                       | 40                   |       |

|                  | I <sub>OL</sub> = 8.5 mA                                          | —                         | —                       | 400                  |       |

| Input High       |                                                                   | V <sub>REGIN</sub> x 0.7  | _                       | —                    | V     |

| Voltage          |                                                                   |                           |                         |                      |       |

| Input Low        |                                                                   | —                         |                         | V <sub>REGIN</sub> x | V     |

| Voltage          |                                                                   |                           |                         | 0.3                  |       |

| Input<br>Leakage | Weak Pullup Off                                                   | —                         | —                       | <u>+2</u>            |       |

| Current          | C8051F52xA/53xA:                                                  |                           |                         |                      |       |

|                  | Weak Pullup On, $V_{IN}$ = 0 V; $V_{REGIN}$ = 1.8 V               | —                         | 5                       | 15                   | μA    |

|                  | C8051F52x/52xA/53x/53xA:                                          |                           |                         |                      |       |

|                  | Weak Pullup On, V <sub>IN</sub> = 0 V; V <sub>REGIN</sub> = 2.7 V |                           | 20                      | 50                   |       |

|                  | Weak Pullup On, $V_{IN} = 0$ V; $V_{REGIN} = 5.25$ V              | —                         | 65                      | 115                  |       |

Figure 3.9. QFN-20 Landing Diagram\*

Note: The Landing Dimensions are given in Table 3.9, "QFN-20 Landing Diagram Dimensions," on page 51.

#### 4.4.1. Calculating the Gain Value

The ADC0 selectable gain feature is controlled by 13 bits in three registers. ADC0GNH contains the 8 upper bits of the gain value and ADC0GNL contains the 4 lower bits of the gain value. The final GAINADD bit (ADC0GNA.0) controls an optional extra 1/64 (0.016) of gain that can be added in addition to the ADC0GNH and ADC0GNL gain. The ADC0GNA.0 bit is set to 1 after a power-on reset.

The equivalent gain for the ADC0GNH, ADC0GNL and ADC0GNA registers is:

$$gain = \left(\frac{GAIN}{4096}\right) + GAINADD \times \left(\frac{1}{64}\right)$$

#### Equation 4.2. Equivalent Gain from the ADC0GNH and ADC0GNL Registers

Where:

*GAIN* is the 12-bit word of ADC0GNH[7:0] and ADC0GNL[7:4] *GAINADD* is the value of the GAINADD bit (ADC0GNA.0) *gain* is the equivalent gain value from 0 to 1.016

For example, if ADC0GNH = 0xFC, ADC0GNL = 0x00, and GAINADD = '1', GAIN = 0xFC0 = 4032, and the resulting equation is:

$$gain = \left(\frac{4032}{4096}\right) + 1 \times \left(\frac{1}{64}\right) = 0.984 + 0.016 = 1.0$$

The table below equates values in the ADC0GNH, ADC0GNL, and ADC0GNA registers to the equivalent gain using this equation.

| ADC0GNH Value  | ADC0GNL Value  | GAINADD Value | GAIN Value | Equivalent Gain |

|----------------|----------------|---------------|------------|-----------------|

| 0xFC (default) | 0x00 (default) | 1 (default)   | 4032 + 64  | 1.0 (default)   |

| 0x7C           | 0x00           | 1             | 1984 + 64  | 0.5             |

| 0xBC           | 0x00           | 1             | 3008 + 64  | 0.75            |

| 0x3C           | 0x00           | 1             | 960 + 64   | 0.25            |

| 0xFF           | 0xF0           | 0             | 4095 + 0   | ~1.0            |

| 0xFF           | 0xF0           | 1             | 4095 + 64  | 1.016           |

For any desired gain value, the GAIN registers can be calculated by:

$$GAIN = \left(gain - GAINADD \times \left(\frac{1}{64}\right)\right) \times 4096$$

Equation 4.3. Calculating the ADC0GNH and ADC0GNL Values from the Desired Gain Where:

*GAIN* is the 12-bit word of ADC0GNH[7:0] and ADC0GNL[7:4] *GAINADD* is the value of the GAINADD bit (ADC0GNA.0) *gain* is the equivalent gain value from 0 to 1.016

When calculating the value of GAIN to load into the ADC0GNH and ADC0GNL registers, the GAINADD bit can be turned on or off to reach a value closer to the desired gain value.

For example, the initial example in this section requires a gain of 0.44 to convert 5 V full scale to 2.2 V full scale. Using Equation 4.3:

$$GAIN = \left(0.44 - GAINADD \times \left(\frac{1}{64}\right)\right) \times 4096$$

If GAINADD is set to 1, this makes the equation:

$$GAIN = \left(0.44 - 1 \times \left(\frac{1}{64}\right)\right) \times 4096 = 0.424 \times 4096 = 1738 = 0x06CA$$

The actual gain from setting GAINADD to 1 and ADC0GNH and ADC0GNL to 0x6CA is 0.4399. A similar gain can be achieved if GAINADD is set to 0 with a different value for ADC0GNH and ADC0GNL.

#### 4.4.2. Setting the Gain Value

The three programmable gain registers are accessed indirectly using the ADC0H and ADC0L registers when the GAINEN bit (ADC0CF.0) bit is set. ADC0H acts as the address register, and ADC0L is the data register. The programmable gain registers can only be written to and cannot be read. See Gain Register Definition 4.1, Gain Register Definition 4.2, and Gain Register Definition 4.3 for more information.

The gain is programmed using the following steps:

- 1. Set the GAINEN bit (ADC0CF.0)

- 2. Load the ADC0H with the ADC0GNH, ADC0GNL, or ADC0GNA address.

- 3. Load ADC0L with the desired value for the selected gain register.

- 4. Reset the GAINEN bit (ADC0CF.0)

#### Notes:

- 1. An ADC conversion should not be performed while the GAINEN bit is set.

- 2. Even with gain enabled, the maximum input voltage must be less than V<sub>REGIN</sub> and the maximum voltage of the signal after gain must be less than or equal to V<sub>REF</sub>.

In code, changing the value to 0.44 gain from the previous example looks like:

```

// in 'C':

ADC0CF |= 0x01;// GAINEN = 1

ADC0H = 0x04;// Load the ADC0GNH address

ADC0L = 0x6C;// Load the upper byte of 0x6CA to ADC0GNH

ADC0H = 0x07;// Load the ADC0GNL address

ADC0L = 0xA0;// Load the lower nibble of 0x6CA to ADC0GNL

ADC0H = 0x08;// Load the ADC0GNA address

ADC0L = 0x01;// Set the GAINADD bit

ADC0CF &= ~0x01;// GAINEN = 0

```

; in assembly ORL ADC0CF,#01H ; GAINEN = 1 MOV ADC0H,#04H; Load the ADC0GNH address MOV ADC0L,#06CH ; Load the upper byte of 0x6CA to ADC0GNH MOV ADC0H,#07H; Load the ADC0GNL address MOV ADC0L,#0A0H ; Load the lower nibble of 0x6CA to ADC0GNL MOV ADC0L,#0A0H ; Load the ADC0GNA address MOV ADC0H,#08H; Load the ADC0GNA address MOV ADC0L,#01H ; Set the GAINADD bit ANL ADC0CF,#0FEH ; GAINEN = 0

## 4.5. Programmable Window Detector

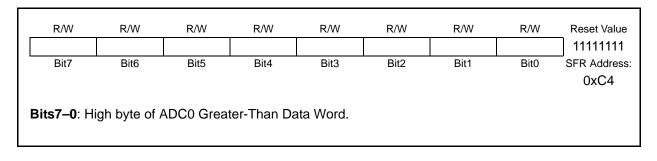

The ADC Programmable Window Detector continuously compares the ADC0 output registers to user-programmed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD0WINT in register ADC0CN) can also be used in polled mode. The ADC0 Greater-Than (ADC0GTH, ADC0GTL) and Less-Than (ADC0LTH, ADC0LTL) registers hold the comparison values. The window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC0 Less-Than and ADC0 Greater-Than registers.

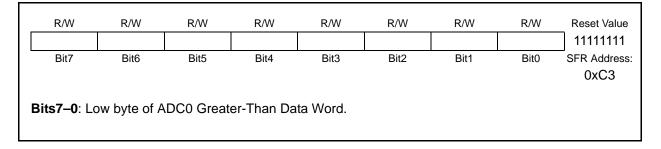

## SFR Definition 4.10. ADC0GTH: ADC0 Greater-Than Data High Byte

## SFR Definition 4.11. ADC0GTL: ADC0 Greater-Than Data Low Byte

#### Performance

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute, and usually have a maximum system clock of 12 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with no instructions taking more than eight system clock cycles.

With the CIP-51's system clock running at 25 MHz, it has a peak throughput of 25 MIPS. The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute      | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

|------------------------|----|----|-----|----|-----|---|-----|---|---|

| Number of Instructions | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

#### **Programming and Debugging Support**

In-system programming of the Flash program memory and communication with on-chip debug support logic is accomplished via the Silicon Labs 2-Wire (C2) interface. Note that the re-programmable Flash can also be read and written a single byte at a time by the application software using the MOVC and MOVX instructions. This feature allows program memory to be used for non-volatile data storage as well as updating program code under software control.

The on-chip debug support logic facilitates full speed in-circuit debugging, allowing the setting of hardware breakpoints, starting, stopping and single stepping through program execution (including interrupt service routines), examination of the program's call stack, and reading/writing the contents of registers and memory. This method of on-chip debugging is completely non-intrusive, requiring no RAM, Stack, timers, or other on-chip resources.

The CIP-51 is supported by development tools from Silicon Laboratories, Inc. and third party vendors. Silicon Laboratories provides an integrated development environment (IDE) including editor, evaluation compiler, assembler, debugger and programmer. The IDE's debugger and programmer interface to the CIP-51 via the on-chip debug logic to provide fast and efficient in-system device programming and debugging. Third party macro assemblers and C compilers are also available.

### 8.1. Instruction Set

The instruction set of the CIP-51 System Controller is fully compatible with the standard MCS-51<sup>™</sup> instruction set. Standard 8051 development tools can be used to develop software for the CIP-51. All CIP-51 instructions are the binary and functional equivalent of their MCS-51<sup>™</sup> counterparts, including opcodes, addressing modes and effect on PSW flags. However, instruction timing is different than that of the standard 8051.

#### 8.1.1. Instruction and CPU Timing

In many 8051 implementations, a distinction is made between machine cycles and clock cycles, with machine cycles varying from 2 to 12 clock cycles in length. However, the CIP-51 implementation is based solely on clock cycle timing. All instruction timings are specified in terms of clock cycles.

Due to the pipelined architecture of the CIP-51, most instructions execute in the same number of clock cycles as there are program bytes in the instruction. Conditional branch instructions take one less clock cycle to complete when the branch is not taken as opposed to when the branch is taken. Table 8.1 is the CIP-51 Instruction Set Summary, which includes the mnemonic, number of bytes, and number of clock cycles for each instruction.

## 9.2. Data Memory

The C8051F52x/F52xA/F53x/F53xAincludes 256 bytes of internal RAM mapped into the data memory space from 0x00 through 0xFF. The lower 128 bytes of data memory are used for general purpose registers and scratch pad memory. Either direct or indirect addressing may be used to access the lower 128 bytes of data memory. Locations 0x00 through 0x1F are addressable as four banks of general purpose registers, each bank consisting of eight byte-wide registers. The next 16 bytes, locations 0x20 through 0x2F, may either be addressed as bytes or as 128 bit locations accessible with the direct addressing mode.

The upper 128 bytes of data memory are accessible only by indirect addressing. This region occupies the same address space as the Special Function Registers (SFRs) but is physically separate from the SFR space. The addressing mode used by an instruction when accessing locations above 0x7F determines whether the CPU accesses the upper 128 bytes of data memory space or the SFRs. Instructions that use direct addressing will access the SFR space. Instructions using indirect addressing above 0x7F access the upper 128 bytes of data memory organization of the C8051F52x/F52xA/F53x/F53xA.

## 9.3. General Purpose Registers

The lower 32 bytes of data memory (locations 0x00 through 0x1F) may be addressed as four banks of general-purpose registers. Each bank consists of eight byte-wide registers designated R0 through R7. Only one of these banks may be enabled at a time. Two bits in the program status word, RS0 (PSW.3) and RS1 (PSW.4), select the active register bank (see description of the PSW in SFR Definition 8.4. PSW: Program Status Word). This allows fast context switching when entering subroutines and interrupt service routines. Indirect addressing modes use registers R0 and R1 as index registers.

## 9.4. Bit Addressable Locations

In addition to direct access to data memory organized as bytes, the sixteen data memory locations at 0x20 through 0x2F are also accessible as 128 individually addressable bits. Each bit has a bit address from 0x00 to 0x7F. Bit 0 of the byte at 0x20 has bit address 0x00 while bit 7 of the byte at 0x20 has bit address 0x07. Bit 7 of the byte at 0x2F has bit address 0x7F. A bit access is distinguished from a full byte access by the type of instruction used (bit source or destination operands as opposed to a byte source or destination).

The MCS-51<sup>™</sup> assembly language allows an alternate notation for bit addressing of the form XX.B where XX is the byte address and B is the bit position within the byte. For example, the instruction:

MOV C, 22.3h

moves the Boolean value at 0x13 (bit 3 of the byte at location 0x22) into the Carry flag.

#### 9.5. Stack

A programmer's stack can be located anywhere in the 256-byte data memory. The stack area is designated using the Stack Pointer (SP, 0x81) SFR. The SP will point to the last location used. The next value pushed on the stack is placed at SP+1 and then SP is incremented. A reset initializes the stack pointer to location 0x07. Therefore, the first value pushed on the stack is placed at location 0x08, which is also the first register (R0) of register bank 1. Thus, if more than one register bank is to be used, the SP should be initialized to a location in the data memory not being used for data storage. The stack depth can extend up to 256 bytes.

#### 9.6. Special Function Registers

The direct-access data memory locations from 0x80 to 0xFF constitute the special function registers (SFRs). The SFRs provide control and data exchange with the CIP-51's resources and peripherals. The CIP-51 duplicates the SFRs found in a typical 8051 implementation as well as implementing additional

## SFR Definition 12.1. PSCTL: Program Store R/W Control

| R                 | R                                                                                                                                                                                                                                                                                                                                                                                                  | R                                                       | R                                                  | R                                                        | R            | R/W                                 | R/W                    | Reset Value  |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------|--------------|-------------------------------------|------------------------|--------------|--|--|--|

| —                 | —                                                                                                                                                                                                                                                                                                                                                                                                  | —                                                       | —                                                  | —                                                        | _            | PSEE                                | PSWE                   | 00000000     |  |  |  |

| Bit7              | Bit6                                                                                                                                                                                                                                                                                                                                                                                               | Bit5                                                    | Bit4                                               | Bit3                                                     | Bit2         | Bit1                                | Bit0                   |              |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                    |                                                         |                                                    |                                                          |              |                                     | SFR Address            | s: 0x8F      |  |  |  |

| Bits7–2:<br>Bit1: | UNUSED: R<br>PSEE: Progr<br>Setting this b<br>to be erased                                                                                                                                                                                                                                                                                                                                         | ram Store Er<br>bit (in combir                          | rase Enabl<br>nation with                          | le<br>PSWE) allo                                         | ws an entir  |                                     |                        |              |  |  |  |

|                   | Flash memo<br>tion addresse<br>0: Flash prog<br>1: Flash prog                                                                                                                                                                                                                                                                                                                                      | ry using the<br>ed by the M<br>gram memoi<br>gram memoi | MOVX ins<br>OVX instru<br>ry erasure<br>ry erasure | struction will<br>uction. The v<br>disabled.<br>enabled. | erase the e  | entire page                         | that contair           | ns the loca- |  |  |  |

| Bit0:             | <ul> <li>it0: PSWE: Program Store Write Enable</li> <li>Setting this bit allows writing a byte of data to the Flash program memory using the MOVX write instruction. The Flash location should be erased before writing data.</li> <li>0: Writes to Flash program memory disabled.</li> <li>1: Writes to Flash program memory enabled; the MOVX write instruction targets Flash memory.</li> </ul> |                                                         |                                                    |                                                          |              |                                     |                        |              |  |  |  |

| Note: See         | Section "12.1.<br>requirements                                                                                                                                                                                                                                                                                                                                                                     |                                                         | -                                                  | -                                                        | page 113 for | <sup>-</sup> minimum V <sub>I</sub> | <sub>DD</sub> and temp | erature      |  |  |  |

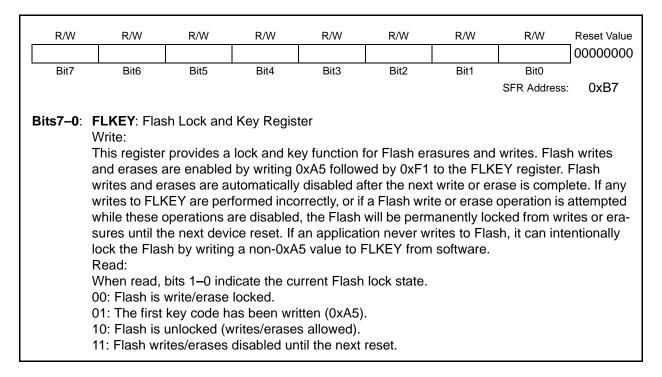

## SFR Definition 12.2. FLKEY: Flash Lock and Key

## 13. Port Input/Output

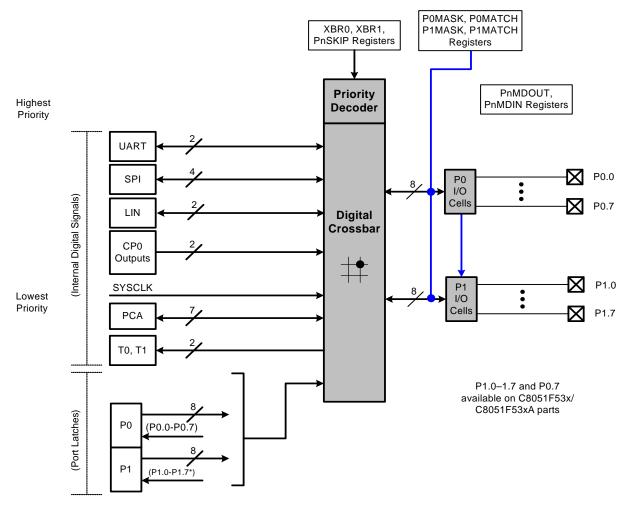

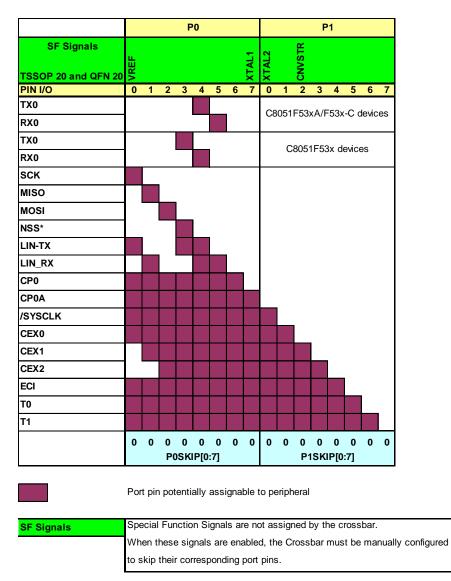

Digital and analog resources are available through up to 16 I/O pins. Port pins are organized as two or one byte-wide Ports. Each of the Port pins can be defined as general-purpose I/O (GPIO) or analog input/out-put; Port pins P0.0 - P2.7 can be assigned to one of the internal digital resources as shown in Figure 13.3. The designer has complete control over which functions are assigned, limited only by the number of physical I/O pins. This resource assignment flexibility is achieved through the use of a Priority Crossbar Decoder. Note that the state of a Port I/O pin can always be read in the corresponding Port latch, regardless of the Crossbar settings.

The Crossbar assigns the selected internal digital resources to the I/O pins based on the peripheral priority order of the Priority Decoder (Figure 13.3 and Figure 13.4). The registers XBR0 and XBR1, defined in SFR Definition 13.1 and SFR Definition 13.2, are used to select internal digital functions.

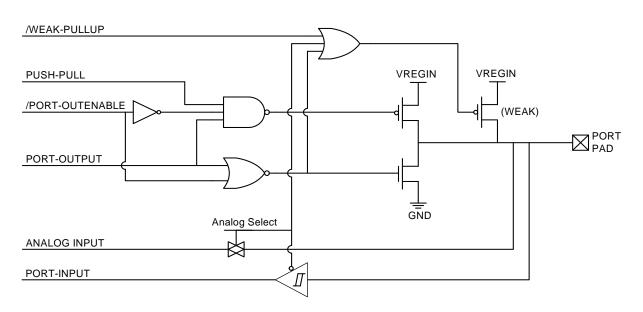

Port I/O pins are 5.25 V tolerant over the operating range of  $V_{REGIN}$ . Figure 13.2 shows the Port cell circuit. The Port I/O cells are configured as either push-pull or open-drain in the Port Output Mode registers (PnMDOUT, where n = 0,1). Complete Electrical Specifications for Port I/O are given in Table 2.10 on page 33.

Figure 13.1. Port I/O Functional Block Diagram

Figure 13.2. Port I/O Cell Block Diagram

## **13.1. Priority Crossbar Decoder**

The Priority Crossbar Decoder (Figure 13.3) assigns a priority to each I/O function, starting at the top with UART0. When a digital resource is selected, the least-significant unassigned Port pin is assigned to that resource (excluding UART0, which will be assigned to pins P0.4 and P0.5). If a Port pin is assigned, the Crossbar skips that pin when assigning the next selected resource. Additionally, the Crossbar will skip Port pins whose associated bits in the PnSKIP registers are set. The PnSKIP registers allow software to skip Port pins that are to be used for analog input, dedicated functions, or GPIO.

Note: 4-Wire SPI Only.

### Figure 13.3. Crossbar Priority Decoder with No Pins Skipped (TSSOP 20 and QFN 20)

**Important Note on Crossbar Configuration**: If a Port pin is claimed by a peripheral without use of the Crossbar, its corresponding PnSKIP bit should be set. This applies to P1.0 and/or P0.7 (F53x/F53xA) or P0.2 and/or P0.3 (F52x/F52xA) for the external oscillator, P0.0 for V<sub>REF</sub>, P1.2 (F53x/F53xA) or P0.5

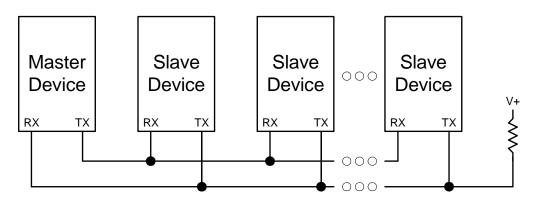

## 15.3. Multiprocessor Communications

9-Bit UART mode supports multiprocessor communication between a master processor and one or more slave processors by special use of the ninth data bit. When a master processor wants to transmit to one or more slaves, it first sends an address byte to select the target(s). An address byte differs from a data byte in that its ninth bit is logic 1; in a data byte, the ninth bit is always set to logic 0.

Setting the MCE0 bit (SCON0.5) of a slave processor configures its UART such that when a stop bit is received, the UART will generate an interrupt only if the ninth bit is logic 1 (RB80 = 1) signifying an address byte has been received. In the UART interrupt handler, software will compare the received address with the slave's own assigned 8-bit address. If the addresses match, the slave will clear its MCE0 bit to enable interrupts on the reception of the following data byte(s). Slaves that weren't addressed leave their MCE0 bits set and do not generate interrupts on the reception of the following data byte(s) addressed slave resets its MCE0 bit to ignore all transmissions until it receives the next address byte.

Multiple addresses can be assigned to a single slave and/or a single address can be assigned to multiple slaves, thereby enabling "broadcast" transmissions to more than one slave simultaneously. The master processor can be configured to receive all transmissions or a protocol can be implemented such that the master/slave role is temporarily reversed to enable half-duplex transmission between the original master and slave(s).

Figure 15.6. UART Multi-Processor Mode Interconnect Diagram

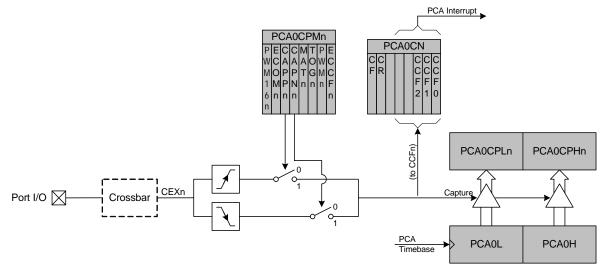

#### 19.2.1. Edge-triggered Capture Mode

In this mode, a valid transition on the CEXn pin causes the PCA to capture the value of the PCA counter/timer and load it into the corresponding module's 16-bit capture/compare register (PCA0CPLn and PCA0CPHn). The CAPPn and CAPNn bits in the PCA0CPMn register are used to select the type of transition that triggers the capture: low-to-high transition (positive edge), high-to-low transition (negative edge), or either transition (positive or negative edge). When a capture occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1 and an interrupt request is generated if CCF interrupts are enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. If both CAPPn and CAPNn bits are set to logic 1, then the state of the Port pin associated with CEXn can be read directly to determine whether a rising-edge or falling-edge caused the capture.

Figure 19.4. PCA Capture Mode Diagram

Note: The CEXn input signal must remain high or low for at least 2 system clock cycles to be recognized by the hardware.

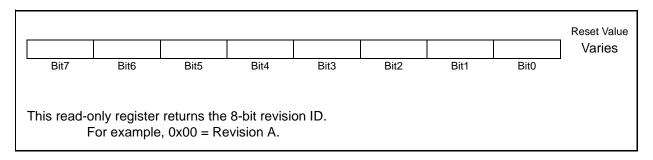

## C2 Register Definition 21.3. REVID: C2 Revision ID

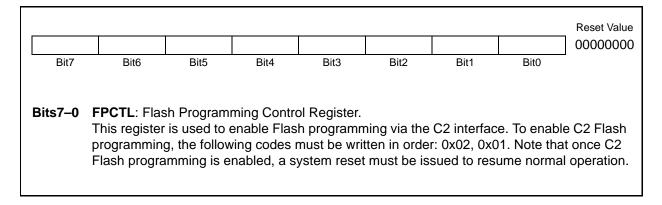

## C2 Register Definition 21.4. FPCTL: C2 Flash Programming Control

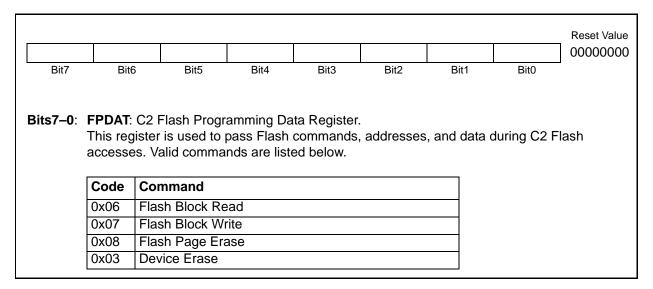

## C2 Register Definition 21.5. FPDAT: C2 Flash Programming Data