# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                           |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | LINbus, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT               |

| Number of I/O              | 16                                                               |

| Program Memory Size        | 8KB (8K x 8)                                                     |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 256 x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.25V                                                       |

| Data Converters            | A/D 16x12b                                                       |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                               |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                  |

| Supplier Device Package    | 20-TSSOP                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f530-c-it |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

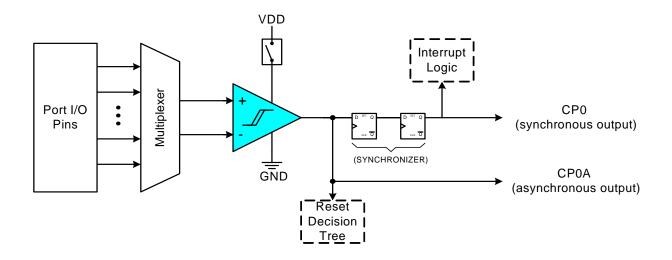

#### **1.6. Programmable Comparator**

C8051F52x/F52xA/F53x/F53xA devices include a software-configurable voltage comparator with an input multiplexer. The comparator offers programmable response time and hysteresis and an output that is optionally available at the Port pins: a synchronous "latched" output (CP0). The comparator interrupt may be generated on rising, falling, or both edges. When in IDLE or SUSPEND mode, these interrupts may be used as a "wake-up" source for the processor. The Comparator may also be configured as a reset source. A block diagram of the comparator is shown in Figure 1.8.

Figure 1.8. Comparator Block Diagram

#### 1.7. Voltage Regulator

C8051F52x/F52xA/F53x/F53xA devices include an on-chip low dropout voltage regulator (REG0). The input to REG0 at the V<sub>REGIN</sub> pin can be as high as 5.25 V. The output can be selected by software to 2.1 or 2.6 V. When enabled, the output of REG0 powers the device and drives the V<sub>DD</sub> pin. The voltage regulator can be used to power external devices connected to V<sub>DD</sub>.

#### 1.8. Serial Port

The C8051F52x/F52xA/F53x/F53xA family includes a full-duplex UART with enhanced baud rate configuration, and an Enhanced SPI interface. Each of the serial buses is fully implemented in hardware and makes extensive use of the CIP-51's interrupts, thus requiring very little CPU intervention.

| Name     | Pin Numbers       |    | Туре             | Description                                                                                                                                                                                                                      |  |  |  |  |  |

|----------|-------------------|----|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|          | ʻF53xA<br>ʻF53x-C |    |                  |                                                                                                                                                                                                                                  |  |  |  |  |  |

| P1.0/    | 13                | 13 | D I/O or<br>A In | Port 1.0. See Port I/O Section for a complete description.                                                                                                                                                                       |  |  |  |  |  |

| XTAL2    |                   |    | D I/O            | External Clock Output. For an external crystal or resonator, this pin is the excitation driver. This pin is the external clock input fo CMOS, capacitor, or RC oscillator configurations. Section "14. Oscillators" on page 135. |  |  |  |  |  |

| P0.7/    | 14                | 14 | D I/O or         | Port 0.7. See Port I/O Section for a complete description.                                                                                                                                                                       |  |  |  |  |  |

| XTAL1    |                   |    | A In             | External Clock Input. This pin is the external oscillator return for a crystal or resonator. See Oscillator Section.                                                                                                             |  |  |  |  |  |

| P0.6/    | 15                | 15 | D I/O or<br>A In | Port 0.6. See Port I/O Section for a complete description.                                                                                                                                                                       |  |  |  |  |  |

| C2D      |                   |    | D I/O            | Bi-directional data signal for the C2 Debug Interface.                                                                                                                                                                           |  |  |  |  |  |

| P0.5/RX* | 16                | —  | D I/O or<br>A In | Port 0.5. See Port I/O Section for a complete description.                                                                                                                                                                       |  |  |  |  |  |

| P0.5     |                   | 16 | D I/O or<br>A In | Port 0.5. See Port I/O Section for a complete description.                                                                                                                                                                       |  |  |  |  |  |

| P0.4/TX* | 17                |    | D I/O or<br>A In | Port 0.4. See Port I/O Section for a complete description.                                                                                                                                                                       |  |  |  |  |  |

| P0.4/RX* | _                 | 17 | D I/O or<br>A In | Port 0.4. See Port I/O Section for a complete description.                                                                                                                                                                       |  |  |  |  |  |

| P0.3     | 18                |    | D I/O or<br>A In | Port 0.3. See Port I/O Section for a complete description.                                                                                                                                                                       |  |  |  |  |  |

| P0.3/TX* | —                 | 18 | D I/O or<br>A In | Port 0.3. See Port I/O Section for a complete description.                                                                                                                                                                       |  |  |  |  |  |

| P0.2     | 19                | 19 | D I/O or<br>A In | Port 0.2. See Port I/O Section for a complete description.                                                                                                                                                                       |  |  |  |  |  |

| P0.1     | 20                | 20 | D I/O or<br>A In | Port 0.1. See Port I/O Section for a complete description.                                                                                                                                                                       |  |  |  |  |  |

#### Table 3.7. Pin Definitions for the C8051F53x and C805153xA (QFN 20) (Continued)

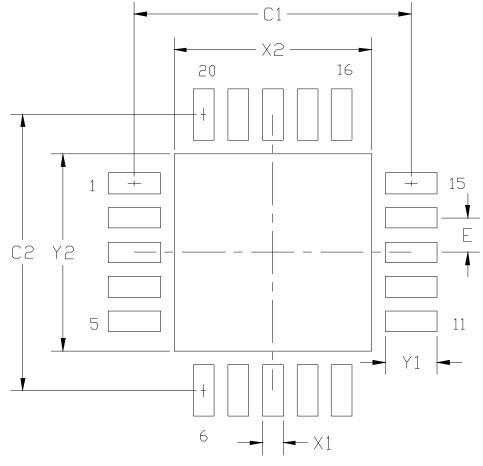

Figure 3.9. QFN-20 Landing Diagram\*

Note: The Landing Dimensions are given in Table 3.9, "QFN-20 Landing Diagram Dimensions," on page 51.

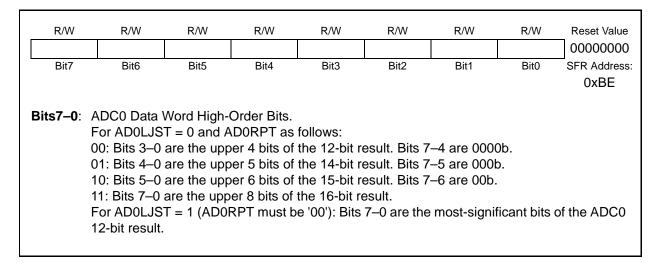

#### SFR Definition 4.6. ADC0H: ADC0 Data Word MSB

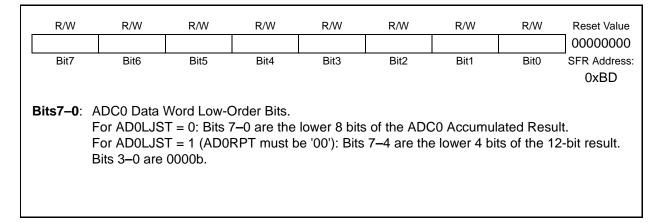

#### SFR Definition 4.7. ADC0L: ADC0 Data Word LSB

## SFR Definition 6.1. REG0CN: Regulator Control

| R/W      | R/W            | R                                        | R/W           | R            | R       | R    | R            | Reset Value |  |

|----------|----------------|------------------------------------------|---------------|--------------|---------|------|--------------|-------------|--|

| REGDIS   | 8 Reserved     | _                                        | REG0MD        |              |         |      | DROPOUT      | 01010000    |  |

| Bit7     | Bit6           | Bit5                                     | Bit4          | Bit3         | Bit2    | Bit1 | Bit0         |             |  |

|          |                |                                          |               |              |         |      | SFR Address: | 0xC9        |  |

|          |                |                                          |               |              |         |      |              |             |  |

| Bit7:    | REGDIS: Vo     | ltage Regu                               | lator Disable | e Bit.       |         |      |              |             |  |

|          | This bit disat | oles/enable                              | s the Voltag  | e Regulato   | r.      |      |              |             |  |

|          | 0: Voltage Re  | egulator Er                              | abled.        | -            |         |      |              |             |  |

|          | 1: Voltage Re  | egulator Di                              | sabled.       |              |         |      |              |             |  |

| Bit6:    | RESERVED       | . Read = 11                              | o. Must write | e 1b.        |         |      |              |             |  |

| Bit5:    | UNUSED. R      | ead = 0b. V                              | Vrite = don't | care.        |         |      |              |             |  |

| Bit4:    | REGOMD: Vo     | oltage Reg                               | ulator Mode   | Select Bit.  |         |      |              |             |  |

|          | This bit seled | cts the Volt                             | age Regulat   | or output vo | oltage. |      |              |             |  |

|          | 0: Voltage R   | egulator ou                              | tput is 2.1 V | ′.           |         |      |              |             |  |

|          | 1: Voltage R   | egulator ou                              | tput is 2.6 V | ' (default). |         |      |              |             |  |

| Bits3–1: | UNUSED. R      | JNUSED. Read = 000b. Write = don't care. |               |              |         |      |              |             |  |

| Bit0:    | DROPOUT:       | Voltage Re                               | gulator Drop  | out Indicat  | or Bit. |      |              |             |  |

|          | 0: Voltage R   | egulator is                              | not in dropo  | ut.          |         |      |              |             |  |

|          | 1: Voltage R   | egulator is                              | in or near dı | ropout.      |         |      |              |             |  |

| l        |                |                                          |               |              |         |      |              |             |  |

### SFR Definition 7.2. CPT0MX: Comparator0 MUX Selection

| R/W<br>CMX0N3         | R/W<br>3 CMX0N2                                                                                      | R/W<br>2 CMX0N                                                                                      | R/W                                                                                              |                                                                                             | R/W<br>P3 CMX0P2                                                                                                           | R/W<br>CMX0P1 | R/W<br>CMX0P0 | Reset Value<br>01110111 |

|-----------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------|---------------|-------------------------|

|                       | Bit6                                                                                                 | 2 CIVIAUN<br>Bit5                                                                                   | Bit4                                                                                             | Bit3                                                                                        | Bit2                                                                                                                       | Bit1          | Bit0          |                         |

| Bit7                  | BIto                                                                                                 | Bito                                                                                                | BIt4                                                                                             | Bit3                                                                                        | Bitz                                                                                                                       | BIU           | BItU          | SFR Address             |

|                       |                                                                                                      |                                                                                                     |                                                                                                  |                                                                                             |                                                                                                                            |               |               | 0x9F                    |

| Rite7_1·              | CMX0N3_                                                                                              |                                                                                                     | Comparato                                                                                        | r0 Negative                                                                                 | e Input MUX Se                                                                                                             | alact         |               |                         |

| JII37- <del>4</del> . |                                                                                                      |                                                                                                     | •                                                                                                | -                                                                                           | the Comparate                                                                                                              |               | innut         |                         |

|                       |                                                                                                      | Sciect with                                                                                         | on ron pin                                                                                       | 13 0300 03                                                                                  |                                                                                                                            | no negative   | s input.      |                         |

|                       | CMX0N3                                                                                               | CMX0N2                                                                                              | CMX0N1                                                                                           | CMX0N0                                                                                      | Negative Inp                                                                                                               | out           |               |                         |

|                       | 0                                                                                                    | 0                                                                                                   | 0                                                                                                | 0                                                                                           | P0.1                                                                                                                       |               |               |                         |

|                       | 0                                                                                                    | 0                                                                                                   | 0                                                                                                | 1                                                                                           | P0.3                                                                                                                       |               |               |                         |

|                       | 0                                                                                                    | 0                                                                                                   | 1                                                                                                | 0                                                                                           | P0.5                                                                                                                       |               |               |                         |

|                       | 0                                                                                                    | 0                                                                                                   | 1                                                                                                | 1                                                                                           | P0.7*                                                                                                                      |               |               |                         |

|                       | 0                                                                                                    | 1                                                                                                   | 0                                                                                                | 0                                                                                           | P1.1*                                                                                                                      |               |               |                         |

|                       | -                                                                                                    |                                                                                                     |                                                                                                  |                                                                                             |                                                                                                                            |               |               |                         |

|                       | 0                                                                                                    | 1                                                                                                   | 0                                                                                                | 1                                                                                           | P1.3*                                                                                                                      |               |               |                         |

|                       | 0                                                                                                    | 1<br>1                                                                                              | 0<br>1                                                                                           | 1<br>0                                                                                      | P1.3*<br>P1.5*                                                                                                             |               |               |                         |

|                       | 0<br>0<br>0<br>able only on t                                                                        | 1<br>1<br>he C8051Ft                                                                                | 1<br>1<br>53x/53xA de                                                                            | 0<br>1<br>vices                                                                             | P1.5*<br>P1.7*                                                                                                             |               |               |                         |

|                       | 0<br>0<br>able only on t<br><b>CMX0P3</b> –0<br>These bits                                           | 1<br>1<br>he C8051F5<br><b>CMX0P0</b> : C<br>select whic                                            | 1<br>53x/53xA de<br>Comparato<br>ch Port pin                                                     | 0<br>1<br>vices<br>r0 Positive<br>is used as                                                | P1.5*<br>P1.7*<br>Input MUX Sel<br>the Comparato                                                                           | or0 positive  | input.        |                         |

|                       | 0<br>0<br>0<br>able only on t<br>CMX0P3–<br>These bits<br>CMX0P3                                     | 1<br>1<br>he C8051Ff<br>CMX0P0: (<br>select which<br>CMX0P2                                         | 1<br>53x/53xA de<br>Comparato<br>ch Port pin<br>CMX0P1                                           | 0<br>1<br>vices<br>r0 Positive<br>is used as<br>CMX0P0                                      | P1.5*<br>P1.7*<br>Input MUX Sel<br>the Comparato                                                                           | or0 positive  | input.        |                         |

|                       | 0<br>0<br>0<br>able only on t<br>CMX0P3-0<br>These bits<br>CMX0P3<br>0                               | 1<br>1<br>cmx0p0: (<br>select white<br>cmx0p2<br>0                                                  | 1<br>53x/53xA de<br>Comparato<br>ch Port pin<br>CMX0P1<br>0                                      | 0<br>1<br>vices<br>r0 Positive<br>is used as<br>CMX0P0<br>0                                 | P1.5*<br>P1.7*<br>Input MUX Sel<br>the Comparato<br><b>Positive Inp</b><br>P0.0                                            | or0 positive  | input.        |                         |

|                       | 0<br>0<br>0<br>able only on t<br>CMX0P3-0<br>These bits<br>CMX0P3<br>0<br>0                          | 1<br>1<br>cmx090: (<br>select white<br>0<br>0                                                       | 1<br>53x/53xA de<br>Comparato<br>ch Port pin<br><b>CMX0P1</b><br>0<br>0                          | 0<br>1<br>vices<br>r0 Positive<br>is used as<br>CMX0P0<br>0<br>1                            | P1.5*<br>P1.7*<br>Input MUX Sel<br>the Comparato<br><b>Positive Inp</b><br>P0.0<br>P0.2                                    | or0 positive  | input.        |                         |

|                       | 0<br>0<br>0<br>able only on t<br>CMX0P3–<br>These bits<br>CMX0P3<br>0<br>0<br>0                      | 1<br>1<br>cmx0P0: (<br>select white<br>0<br>0<br>0                                                  | 1<br>53x/53xA de<br>Comparator<br>ch Port pin<br><b>CMX0P1</b><br>0<br>0<br>1                    | 0<br>1<br>vices<br>r0 Positive<br>is used as<br><b>CMX0P0</b><br>0<br>1<br>0                | P1.5*<br>P1.7*<br>Input MUX Sel<br>the Comparato<br><b>Positive Inp</b><br>P0.0<br>P0.2<br>P0.4                            | or0 positive  | input.        |                         |

|                       | 0<br>0<br>0<br>able only on t<br>CMX0P3–<br>These bits<br>CMX0P3<br>0<br>0<br>0<br>0                 | 1<br>1<br>he C8051F6<br><b>CMX0P0</b> : 0<br>select white<br><b>CMX0P2</b><br>0<br>0<br>0<br>0<br>0 | 1<br>53x/53xA de<br>Comparator<br>ch Port pin<br>CMX0P1<br>0<br>0<br>1<br>1                      | 0<br>1<br>vices<br>r0 Positive<br>is used as<br>CMX0P0<br>0<br>1<br>0<br>1                  | P1.5*<br>P1.7*<br>Input MUX Sel<br>the Comparato<br><b>Positive Inp</b><br>P0.0<br>P0.2<br>P0.4<br>P0.6*                   | or0 positive  | input.        |                         |

|                       | 0<br>0<br>0<br>able only on t<br>CMX0P3-0<br>These bits<br>CMX0P3<br>0<br>0<br>0<br>0<br>0<br>0      | 1<br>1<br>cmx0P0: 0<br>select white<br>cmx0P2<br>0<br>0<br>0<br>0<br>1                              | 1<br>53x/53xA de<br>Comparator<br>ch Port pin<br><b>CMX0P1</b><br>0<br>0<br>1<br>1<br>1<br>0     | 0<br>1<br>vices<br>r0 Positive<br>is used as<br><b>CMX0P0</b><br>0<br>1<br>0<br>1<br>0      | P1.5*<br>P1.7*<br>Input MUX Sel<br>the Comparato<br><b>Positive Inp</b><br>P0.0<br>P0.2<br>P0.4<br>P0.6*<br>P1.0*          | or0 positive  | input.        |                         |

|                       | 0<br>0<br>0<br>able only on t<br>CMX0P3-0<br>These bits<br>CMX0P3<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 1<br>1<br>cmx0P0: C<br>select white<br>CMX0P2<br>0<br>0<br>0<br>0<br>0<br>1<br>1                    | 1<br>53x/53xA de<br>Comparato<br>ch Port pin<br><b>CMX0P1</b><br>0<br>0<br>1<br>1<br>1<br>0<br>0 | 0<br>1<br>vices<br>r0 Positive<br>is used as<br><b>CMX0P0</b><br>0<br>1<br>0<br>1<br>0<br>1 | P1.5*<br>P1.7*<br>Input MUX Sel<br>the Comparato<br><b>Positive Inp</b><br>P0.0<br>P0.2<br>P0.4<br>P0.6*<br>P1.0*<br>P1.2* | or0 positive  | input.        |                         |

|                       | 0<br>0<br>0<br>able only on t<br>CMX0P3-0<br>These bits<br>CMX0P3<br>0<br>0<br>0<br>0<br>0           | 1<br>1<br>cmx0P0: 0<br>select white<br>cmx0P2<br>0<br>0<br>0<br>0<br>1                              | 1<br>53x/53xA de<br>Comparator<br>ch Port pin<br><b>CMX0P1</b><br>0<br>0<br>1<br>1<br>1<br>0     | 0<br>1<br>vices<br>r0 Positive<br>is used as<br><b>CMX0P0</b><br>0<br>1<br>0<br>1<br>0      | P1.5*<br>P1.7*<br>Input MUX Sel<br>the Comparato<br><b>Positive Inp</b><br>P0.0<br>P0.2<br>P0.4<br>P0.6*<br>P1.0*          | or0 positive  | input.        |                         |

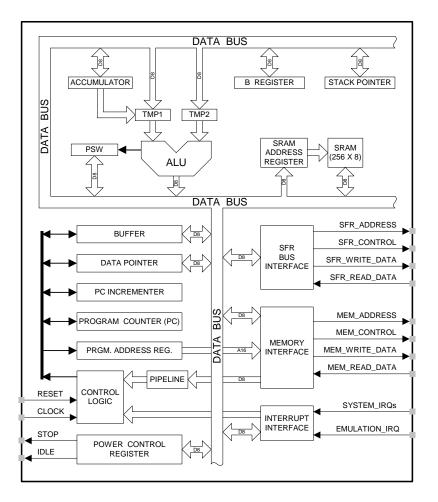

## 8. CIP-51 Microcontroller

The MCU system controller core is the CIP-51 microcontroller. The CIP-51 is fully compatible with the MCS-51<sup>™</sup> instruction set. Standard 803x/805x assemblers and compilers can be used to develop software. The C8051F52x/F52xA/F53x/F53xA family has a superset of all the peripherals included with a standard 8051. See Section "1. System Overview" on page 13 for more information about the available peripherals. The CIP-51 includes on-chip debug hardware which interfaces directly with the analog and digital subsystems, providing a complete data acquisition or control-system solution in a single integrated circuit.

The CIP-51 Microcontroller core implements the standard 8051 organization and peripherals as well as additional custom peripherals and functions to extend its capability (see Figure 8.1 for a block diagram). The CIP-51 core includes the following features:

- Fully Compatible with MCS-51 Instruction Set

- 25 MIPS Peak Throughput

- 256 Bytes of Internal RAM

- Extended Interrupt Handler

- Reset Input

- Power Management Modes

- Integrated Debug Logic

- Program and Data Memory Security

Figure 8.1. CIP-51 Block Diagram

#### Table 9.2. Special Function Registers (Continued)

| Register | Address | Description                       | Page |

|----------|---------|-----------------------------------|------|

| REF0CN   | 0xD1    | Voltage Reference Control         | 73   |

| REG0CN   | 0xC9    | Voltage Regulator Control         | 75   |

| RSTSRC   | 0xEF    | Reset Source Configuration/Status | 112  |

| SBUF0    | 0x99    | UART0 Data Buffer                 | 150  |

| SCON0    | 0x98    | UART0 Control                     | 149  |

| SP       | 0x81    | Stack Pointer                     | 87   |

| SPI0CFG  | 0xA1    | SPI Configuration                 | 157  |

| SPI0CKR  | 0xA2    | SPI Clock Rate Control            | 159  |

| SPI0CN   | 0xF8    | SPI Control                       | 158  |

| SPI0DAT  | 0xA3    | SPI Data                          | 160  |

| TCON     | 0x88    | Timer/Counter Control             | 186  |

| TH0      | 0x8C    | Timer/Counter 0 High              | 189  |

| TH1      | 0x8D    | Timer/Counter 1 High              | 189  |

| TL0      | 0x8A    | Timer/Counter 0 Low               | 189  |

| TL1      | 0x8B    | Timer/Counter 1 Low               | 189  |

| TMOD     | 0x89    | Timer/Counter Mode                | 187  |

| TMR2CN   | 0xC8    | Timer/Counter 2 Control           | 193  |

| TMR2H    | 0xCD    | Timer/Counter 2 High              | 194  |

| TMR2L    | 0xCC    | Timer/Counter 2 Low               | 194  |

| TMR2RLH  | 0xCB    | Timer/Counter 2 Reload High       | 194  |

| TMR2RLL  | 0xCA    | Timer/Counter 2 Reload Low        | 194  |

| VDDMON   | 0xFF    | V <sub>DD</sub> Monitor Control   | 109  |

| XBR0     | 0xE1    | Port I/O Crossbar Control 0       | 127  |

| XBR1     | 0xE2    | Port I/O Crossbar Control 1       | 128  |

SFRs are listed in alphabetical order. All undefined SFR locations are reserved

### SFR Definition 10.3. EIE1: Extended Interrupt Enable 1

| EMAT         EREGO         ELIN         ECPR         ECPF         EPCA0         EADC0         EWADC0         00000000           Bit7         Bit6         Bit5         Bit4         Bit3         Bit2         Bit1         Bit0         SFR Address:         0xE6           Bit7:         EMAT: Enable Port Match Interrupt.         This bit sets the masking of the Port Match interrupt.         Bit3         Bit2         Bit1         Bit0         SFR Address:         0xE6           Bit7:         EMAT: Enable Port Match Interrupt.         This bit sets the masking of the Voltage Regulator Dropout interrupt.         Disable the Port Match Interrupt.         This bit sets the masking of the Voltage Regulator Dropout Interrupt.         0. Disable the Voltage Regulator Dropout Interrupt.         1: Enable the Voltage Regulator Dropout Interrupt.         1: Enable the Voltage Regulator Dropout Interrupt.         0. Disable LIN Interrupt.         1: Enable LIN Interrupt.         1: Enable LIN Interrupt.         1: Enable COP Rising Edge Interrupt.         1: Enable COP Rising Edge Interrupt.         1: Enable COP Rising Edge Interrupt.         1: Enable CPO Rising Edge Interrupt.         1: Enable CPO Falling Edge Interrupt.         1: Enable COP Falling Edge Interrupt.         1: Enable CPO Falling Edge Interrupt.         1: Enable C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W   | R/W           | R/W               | R/W          | R/W           | R/W          | R/W          | R/W    | Reset Value |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------|-------------------|--------------|---------------|--------------|--------------|--------|-------------|--|

| <ul> <li>SFR Address: 0xE6</li> <li>Bit7: EMAT: Enable Port Match Interrupt.<br/>This bit sets the masking of the Port Match interrupt.<br/>Disable the Port Match interrupt.<br/>1: Enable the Port Match interrupt.<br/>1: Enable the Port Match interrupt.<br/>This bit sets the masking of the Voltage Regulator Dropout interrupt.<br/>Disable the Voltage Regulator Dropout interrupt.<br/>1: Enable the Voltage Regulator Dropout interrupt.<br/>Disable the Voltage Regulator Dropout interrupt.<br/>1: Enable the Voltage Regulator Dropout interrupt.<br/>1: Enable the Voltage Regulator Dropout interrupt.<br/>Bit5: ELIN: Enable LIN Interrupt.<br/>This bit sets the masking of the LIN interrupt.<br/>Disable LIN interrupts.<br/>1: Enable LIN interrupts.<br/>1: Enable LIN interrupts.<br/>1: Enable COP Rising Edge Interrupt<br/>This bit sets the masking of the CPO Rising Edge interrupt.<br/>Disable CPO Rising Edge Interrupt.<br/>1: Enable CPO Rising Edge Interrupt.<br/>3: Enable CPO Falling Edge Interrupt.<br/>1: Enable CPO Falling Edge Interrupt.<br/>3: Enable CPO Falling Edge Interrupt.<br/>1: Enable CPO Falling Edge Interrupt.<br/>3: Enable ADCO Conversion Complete Interrupt.<br/>3: Enable all PCA0 interrupts.<br/>3: Enable ADCO Conversion Complete Interrupt.<br/>3: Enable ADCO Window Comparison Interrupt.<br/>3: Enable ADCO Window Comparison Interrupt.<br/>3: Disable ADCO Window Comparison</li></ul> | EMAT  | EREG0         | ELIN              | ECPR         | ECPF          | EPCA0        | EADC0        | EWADC0 | 00000000    |  |

| <ul> <li>Bit7: EMAT: Enable Port Match Interrupt.<br/>This bit sets the masking of the Port Match interrupt.</li> <li>0: Disable the Port Match interrupt.</li> <li>1: Enable the Port Match interrupt.</li> <li>Bit6: EREGO: Enable Voltage Regulator Interrupt.<br/>This bit sets the masking of the Voltage Regulator Dropout interrupt.</li> <li>0: Disable the Voltage Regulator Dropout interrupt.</li> <li>1: Enable the Voltage Regulator Dropout interrupt.</li> <li>1: Enable LIN Interrupt.<br/>This bit sets the masking of the LIN interrupt.</li> <li>0: Disable LIN Interrupt.<br/>This bit sets the masking of the LIN interrupt.</li> <li>0: Disable LIN interrupts.</li> <li>1: Enable COMparator 0 Rising Edge Interrupt<br/>This bit sets the masking of the CPO Rising Edge interrupt<br/>This bit sets the masking of the CPO Rising Edge interrupt.</li> <li>0: Disable CPO Rising Edge Interrupt.</li> <li>1: Enable CPO Falling Edge Interrupt.</li> <li>1: Enable ADCO Conversion Complete Interrupt.</li> <li>1: Enable interrupt requests generated by PCA0.</li> <li>Bit1: EADCO: Enable ADCO Conversion Complete Interrupt.</li> <li>1: Enable Interrupt requests generated by the ADOINT flag.</li> <li>Bit0: EWADCO: Enable ADCO Window Comparison Interrupt.</li> <li>1: Disable ADCO Window Comparison Interrupt.</li> <li>1: Disable ADCO Window Comparison Interrupt.</li> <li>1: Disable ADCO Window Compa</li></ul>                                                                                                                   | Bit7  | Bit6          | Bit5              | Bit4         | Bit3          | Bit2         | Bit1         | Bit0   | J           |  |

| <ul> <li>This bit sets the masking of the Port Match interrupt.</li> <li>0: Disable the Port Match interrupt.</li> <li>1: Enable the Port Match interrupt.</li> <li>1: Enable the Port Match interrupt.</li> <li>Bit6: EREG0: Enable Voltage Regulator Interrupt.</li> <li>This bit sets the masking of the Voltage Regulator Dropout interrupt.</li> <li>0: Disable the Voltage Regulator Dropout interrupt.</li> <li>1: Enable the Voltage Regulator Dropout interrupt.</li> <li>1: Enable LIN Interrupt.</li> <li>This bit sets the masking of the LIN interrupt.</li> <li>0: Disable LIN Interrupt.</li> <li>This bit sets the masking of the LIN interrupt.</li> <li>0: Disable LIN interrupts.</li> <li>1: Enable LIN interrupt requests.</li> <li>Bit4: ECPR: Enable Comparator 0 Rising Edge Interrupt</li> <li>This bit sets the masking of the CPO Rising Edge interrupt.</li> <li>0: Disable CPO Rising Edge Interrupt.</li> <li>1: Enable CPO Rising Edge Interrupt.</li> <li>1: Enable CPO Rising Edge Interrupt.</li> <li>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt.</li> <li>0: Disable CPO Ralling Edge Interrupt.</li> <li>Bit4: ECPR: Enable Comparator 0 Falling Edge Interrupt.</li> <li>0: Disable CPO Falling Edge Interrupt.</li> <li>1: Enable Programmable Counter Array (PCA0) Interrupt.</li> <li>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable ADCO Conversion Complete Interrupt.</li> <li>1: Enable ADCO Window Comparison Interrupt.</li> <li>1: Enable ADCO Window Comparison Interrupt.</li> <li>1: Disable ADCO Window Comp</li></ul>                                                                                                                                           |       |               | SFR Address: 0xE6 |              |               |              |              |        |             |  |

| <ul> <li>This bit sets the masking of the Port Match interrupt.</li> <li>0: Disable the Port Match interrupt.</li> <li>1: Enable the Port Match interrupt.</li> <li>1: Enable the Port Match interrupt.</li> <li>Bit6: EREG0: Enable Voltage Regulator Interrupt.</li> <li>This bit sets the masking of the Voltage Regulator Dropout interrupt.</li> <li>0: Disable the Voltage Regulator Dropout interrupt.</li> <li>1: Enable the Voltage Regulator Dropout interrupt.</li> <li>1: Enable LIN Interrupt.</li> <li>This bit sets the masking of the LIN interrupt.</li> <li>0: Disable LIN Interrupt.</li> <li>This bit sets the masking of the LIN interrupt.</li> <li>0: Disable LIN interrupts.</li> <li>1: Enable LIN interrupt requests.</li> <li>Bit4: ECPR: Enable Comparator 0 Rising Edge Interrupt</li> <li>This bit sets the masking of the CPO Rising Edge interrupt.</li> <li>0: Disable CPO Rising Edge Interrupt.</li> <li>1: Enable CPO Rising Edge Interrupt.</li> <li>1: Enable CPO Rising Edge Interrupt.</li> <li>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt.</li> <li>0: Disable CPO Ralling Edge Interrupt.</li> <li>Bit4: ECPR: Enable Comparator 0 Falling Edge Interrupt.</li> <li>0: Disable CPO Falling Edge Interrupt.</li> <li>1: Enable Programmable Counter Array (PCA0) Interrupt.</li> <li>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable ADCO Conversion Complete Interrupt.</li> <li>1: Enable ADCO Window Comparison Interrupt.</li> <li>1: Enable ADCO Window Comparison Interrupt.</li> <li>1: Disable ADCO Window Comp</li></ul>                                                                                                                                           |       |               |                   |              |               |              |              |        |             |  |

| <ul> <li>0: Disable the Port Match interrupt.</li> <li>1: Enable the Port Match interrupt.</li> <li>Bit6: EREG0: Enable Voltage Regulator Interrupt.<br/>This bit sets the masking of the Voltage Regulator Dropout interrupt.</li> <li>0: Disable the Voltage Regulator Dropout interrupt.</li> <li>1: Enable the Voltage Regulator Dropout interrupt.</li> <li>1: Enable the Voltage Regulator Dropout interrupt.</li> <li>Bit5: ELIN: Enable LIN Interrupt.<br/>This bit sets the masking of the LIN interrupt.</li> <li>0: Disable LIN interrupt requests.</li> <li>Bit4: ECPR: Enable Comparator 0 Rising Edge Interrupt<br/>This bit sets the masking of the CP0 Rising Edge interrupt.</li> <li>0: Disable CP0 Rising Edge Interrupt.</li> <li>1: Enable CP0 Rising Edge Interrupt.</li> <li>1: Enable CP0 Rising Edge Interrupt.</li> <li>1: Enable CP0 Rising Edge Interrupt.</li> <li>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>Bit2: EPCA0: Enable Programmable Counter Array (PCA0) Interrupt.</li> <li>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable ADC0 Conversion Complete Interrupt.</li> <li>1: Enable ADC0 Window Comparison Interrupt.</li> <li>1: Bit sets the masking of the ADC0 Window Comparison Interrupt.</li> <li>1: Disable ADC0 Window Comparison Interrupt.<th>Bit7:</th><th>EMAT: Enab</th><th>le Port Mat</th><th>ch Interrupt</th><th></th><th></th><th></th><th></th><th></th></li></ul>           | Bit7: | EMAT: Enab    | le Port Mat       | ch Interrupt |               |              |              |        |             |  |

| <ul> <li>1: Enable the Port Match interrupt.</li> <li>Bit6: EREG0: Enable Voltage Regulator Interrupt.<br/>This bit sets the masking of the Voltage Regulator Dropout interrupt.<br/>0: Disable the Voltage Regulator Dropout interrupt.</li> <li>1: Enable the Voltage Regulator Dropout interrupt.</li> <li>Bit5: ELIN: Enable LIN Interrupt.<br/>This bit sets the masking of the LIN interrupt.<br/>0: Disable LIN interrupts.</li> <li>Bit4: ECPR: Enable Comparator 0 Rising Edge Interrupt<br/>This bit sets the masking of the CP0 Rising Edge interrupt.</li> <li>0: Disable CP0 Rising Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>1: Enable PCA0 interrupts.</li> <li>0: Disable ADC0 Conversion Complete Interrupt.</li> <li>1: Enable interrupt requests generated by PCA0.</li> <li>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.</li> <li>1: Enable interrupt requests generated by the AD0INT flag.</li> <li>Bit0: EWADC0: Enable ADC0 Window Comparison Interrupt.</li> <li>1: Sisable ADC0 Window Comparison Interrupt.</li> <li>1: Sisable ADC0 Window Comparison Interrupt.</li> <li>1: Sisable ADC0 Window Comparison Interrupt.</li> <li>1: Disable ADC0 Window Comparison Interrupt.</li> </ul>                                                                                                                                                                                              |       |               |                   |              |               | errupt.      |              |        |             |  |

| <ul> <li>Bit6: EREG0: Enable Voltage Regulator Interrupt.<br/>This bit sets the masking of the Voltage Regulator Dropout interrupt.<br/>0: Disable the Voltage Regulator Dropout interrupt.<br/>1: Enable the Voltage Regulator Dropout interrupt.<br/>1: Enable LIN Interrupt.<br/>This bit sets the masking of the LIN interrupt.<br/>0: Disable LIN interrupt.<br/>This bit sets the masking of the LIN interrupt<br/>0: Disable LIN interrupt requests.<br/>Bit4: ECPR: Enable Comparator 0 Rising Edge Interrupt<br/>This bit sets the masking of the CP0 Rising Edge interrupt.<br/>0: Disable CP0 Rising Edge Interrupt.<br/>1: Enable CP0 Rising Edge Interrupt.<br/>1: Enable CP0 Rising Edge Interrupt.<br/>1: Enable CP0 Rising Edge Interrupt.<br/>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt.<br/>Di Disable CP0 Falling Edge Interrupt.<br/>Bit4: ECPR: Enable Comparator 0 Falling Edge Interrupt.<br/>Bit5: ECPF: Enable Comparator 0 Falling Edge Interrupt.<br/>Bit6: ECPF: Enable Comparator 0 Falling Edge Interrupt.<br/>Bit6: ECPC Falling Edge Interrupt.<br/>Bit2: EPCA0: Enable Programmable Counter Array (PCA0) Interrupt.<br/>This bit sets the masking of the PCA0 interrupts.<br/>0: Disable all PCA0 interrupts.<br/>1: Enable interrupt requests generated by PCA0.<br/>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.<br/>This bit sets the masking of the ADC0 Conversion Complete interrupt.<br/>0: Disable ADC0 Conversion Complete Interrupt.<br/>Bit0: EWADC0: Enable ADC0 Window Comparison Interrupt.<br/>This bit sets the masking of the ADC0 Window Comparison interrupt.<br/>0: Disable ADC0 Window Comparison interrupt.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                          |       |               |                   |              |               |              |              |        |             |  |

| <ul> <li>This bit sets the masking of the Voltage Regulator Dropout interrupt.</li> <li>0: Disable the Voltage Regulator Dropout interrupt.</li> <li>1: Enable the Voltage Regulator Dropout interrupt.</li> <li>Bit5: ELIN: Enable LIN Interrupt.</li> <li>This bit sets the masking of the LIN interrupt.</li> <li>0: Disable LIN interrupts.</li> <li>1: Enable LIN interrupt requests.</li> <li>Bit4: ECPR: Enable Comparator 0 Rising Edge Interrupt</li> <li>This bit sets the masking of the CP0 Rising Edge Interrupt.</li> <li>0: Disable CP0 Rising Edge Interrupt.</li> <li>1: Enable CP0 Rising Edge Interrupt.</li> <li>0: Disable CP0 Rising Edge Interrupt.</li> <li>1: Enable COMparator 0 Falling Edge Interrupt.</li> <li>0: Disable CP0 Rising Edge Interrupt.</li> <li>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt.</li> <li>0: Disable CP0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>0: Disable CP0 Falling Edge Interrupt.</li> <li>1: Enable Interrupt requests generated by PCA0.</li> <li>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.</li> <li>1: Enable Interrupt requests generated by PCA0.</li> <li>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.</li> <li>1: Enable Interrupt requests generated by the ADOINT flag.</li> <li>Bit0: EWADC0: Enable ADC0 Window Comparison Interrupt.</li> <li>1: Enable ADC0 Window Comparison Interrupt.</li> <li>1: Disable ADC0 Window Comparison Interrupt.</li> <li>1: Disable ADC0 Window Comparison Interrupt.</li> <li>1: Disable ADC0 Window Comparison Interrupt.</li> </ul>                                                                                                                                                                                                                 |       |               |                   |              |               |              |              |        |             |  |

| <ul> <li>0: Disable the Voltage Regulator Dropout interrupt.</li> <li>1: Enable the Voltage Regulator Dropout interrupt.</li> <li>Bit5: ELIN: Enable LIN Interrupt.<br/>This bit sets the masking of the LIN interrupt.</li> <li>0: Disable LIN interrupts.</li> <li>1: Enable LIN interrupts.</li> <li>1: Enable Comparator 0 Rising Edge Interrupt</li> <li>This bit sets the masking of the CP0 Rising Edge interrupt.</li> <li>0: Disable CP0 Rising Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>3: ECPF: Enable Comparator 0 Falling Edge Interrupt.</li> <li>0: Disable CP0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>3: Enable CP0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>3: Enable CP0 Falling Edge Interrupt.</li> <li>3: Enable CP0 Falling Edge Interrupt.</li> <li>3: Enable CP0 Falling Edge Interrupt.</li> <li>4: Enable Programmable Counter Array (PCA0) Interrupt.</li> <li>5: Disable all PCA0 interrupts.</li> <li>1: Enable Interrupt requests generated by PCA0.</li> <li>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.</li> <li>3: Disable ADC0 Conversion Complete Interrupt.</li> <li>4: Enable Interrupt requests generated by PCA0.</li> <li>Bit0: EWADC0: Enable ADC0 Window Comparison Interrupt.</li> <li>5: Disable ADC0 Window Comparison Interrupt.</li> <li>6: Disable ADC0 Window Comparison Interrupt.</li> <li>7: Disable ADC0 Window Comparison Interrupt.</li> <li>6: Disable ADC0 Window Comparison Interrupt.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                        | Bit6: |               |                   |              |               |              |              |        |             |  |

| <ul> <li>1: Enable the Voltage Regulator Dropout interrupt.</li> <li>Bit5: ELIN: Enable LIN Interrupt.<br/>This bit sets the masking of the LIN interrupt.<br/>0: Disable LIN interrupts.<br/>1: Enable LIN interrupts.<br/>1: Enable LIN interrupts.</li> <li>Bit4: ECPR: Enable Comparator 0 Rising Edge Interrupt<br/>This bit sets the masking of the CP0 Rising Edge interrupt.<br/>0: Disable CP0 Rising Edge Interrupt.<br/>1: Enable CP0 Rising Edge Interrupt.<br/>1: Enable CP0 Rising Edge Interrupt.</li> <li>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt<br/>This bit sets the masking of the CP0 Falling Edge interrupt.<br/>0: Disable CP0 Falling Edge Interrupt.<br/>1: Enable CP0 Falling Edge Interrupt.<br/>1: Enable CP0 Falling Edge Interrupt.<br/>1: Enable CP0 Falling Edge Interrupt.</li> <li>Bit2: EPCA0: Enable Programmable Counter Array (PCA0) Interrupt.<br/>This bit sets the masking of the PCA0 interrupts.<br/>0: Disable all PCA0 interrupts.<br/>1: Enable interrupt requests generated by PCA0.</li> <li>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.<br/>This bit sets the masking of the ADC0 Conversion Complete interrupt.<br/>0: Disable ADC0 Conversion Complete Interrupt.<br/>1: Enable interrupt requests generated by the AD0INT flag.</li> <li>Bit0: EWADC0: Enable ADC0 Window Comparison Interrupt.<br/>This bit sets the masking of the ADC0 Window Comparison interrupt.<br/>0: Disable ADC0 Window Comparison Interrupt.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |               |                   | •            | • •           | •            | t interrupt. |        |             |  |

| <ul> <li>Bit5: ELIN: Enable LIN Interrupt.<br/>This bit sets the masking of the LIN interrupt.<br/>0: Disable LIN interrupts.<br/>1: Enable LIN interrupt requests.</li> <li>Bit4: ECPR: Enable Comparator 0 Rising Edge Interrupt<br/>This bit sets the masking of the CP0 Rising Edge interrupt.<br/>0: Disable CP0 Rising Edge Interrupt.<br/>1: Enable COP Rising Edge Interrupt.<br/>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt<br/>This bit sets the masking of the CP0 Falling Edge interrupt.<br/>0: Disable CP0 Falling Edge Interrupt.<br/>1: Enable CP0 Falling Edge Interrupt.<br/>0: Disable CP0 Falling Edge Interrupt.<br/>1: Enable CP0 Falling Edge Interrupt.<br/>Bit2: EPCA0: Enable Programmable Counter Array (PCA0) Interrupt.<br/>This bit sets the masking of the PCA0 interrupts.<br/>0: Disable all PCA0 interrupts.<br/>1: Enable interrupt requests generated by PCA0.<br/>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.<br/>This bit sets the masking of the ADC0 Conversion Complete interrupt.<br/>0: Disable ADC0 Conversion Complete Interrupt.<br/>1: Enable interrupt requests generated by the AD0INT flag.<br/>Bit0: EWADC0: Enable ADC0 Window Comparison Interrupt.<br/>This bit sets the masking of the ADC0 Window Comparison interrupt.<br/>0: Disable ADC0 Window Comparison interrupt.</li> </ul>                                                                                                                                                                                                                                                   |       |               | •                 | •            | •             | •            |              |        |             |  |

| <ul> <li>This bit sets the masking of the LIN interrupt.</li> <li>0: Disable LIN interrupts.</li> <li>1: Enable LIN interrupt requests.</li> <li>Bit4: ECPR: Enable Comparator 0 Rising Edge Interrupt</li> <li>This bit sets the masking of the CP0 Rising Edge interrupt.</li> <li>0: Disable CP0 Rising Edge Interrupt.</li> <li>1: Enable Comparator 0 Falling Edge Interrupt</li> <li>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt.</li> <li>0: Disable CP0 Falling Edge Interrupt.</li> <li>Bit4: ECPR: Enable Comparator 0 Falling Edge Interrupt.</li> <li>0: Disable CP0 Falling Edge Interrupt.</li> <li>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt.</li> <li>0: Disable CP0 Falling Edge Interrupt.</li> <li>Bit2: EPCA0: Enable Programmable Counter Array (PCA0) Interrupt.</li> <li>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable interrupt requests generated by PCA0.</li> <li>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.</li> <li>This bit sets the masking of the ADC0 Conversion Complete interrupt.</li> <li>0: Disable ADC0 Conversion Complete Interrupt.</li> <li>1: Enable interrupt requests generated by the AD0INT flag.</li> <li>Bit0: EWADC0: Enable ADC0 Window Comparison Interrupt.</li> <li>This bit sets the masking of the ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison Interrupt.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |               | •                 | •            | opout interr  | upt.         |              |        |             |  |

| <ul> <li>0: Disable LIN interrupts.</li> <li>1: Enable LIN interrupt requests.</li> <li>Bit4: ECPR: Enable Comparator 0 Rising Edge Interrupt<br/>This bit sets the masking of the CP0 Rising Edge interrupt.</li> <li>0: Disable CP0 Rising Edge Interrupt.</li> <li>1: Enable CP0 Rising Edge Interrupt.</li> <li>1: Enable CP0 Rising Edge Interrupt.</li> <li>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt<br/>This bit sets the masking of the CP0 Falling Edge interrupt.</li> <li>0: Disable CP0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>Bit2: EPCA0: Enable Programmable Counter Array (PCA0) Interrupt.<br/>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable interrupt requests generated by PCA0.</li> <li>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.</li> <li>This bit sets the masking of the ADC0 conversion Complete interrupt.</li> <li>0: Disable ADC0 Conversion Complete Interrupt.</li> <li>1: Enable interrupt requests generated by the AD0INT flag.</li> <li>Bit0: EWADC0: Enable ADC0 Window Comparison Interrupt.</li> <li>This bit sets the masking of the ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison Interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Bit5: |               |                   |              |               |              |              |        |             |  |

| <ul> <li>1: Enable LIN interrupt requests.</li> <li>Bit4: ECPR: Enable Comparator 0 Rising Edge Interrupt<br/>This bit sets the masking of the CP0 Rising Edge interrupt.</li> <li>0: Disable CP0 Rising Edge Interrupt.</li> <li>1: Enable CP0 Rising Edge Interrupt.</li> <li>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt<br/>This bit sets the masking of the CP0 Falling Edge interrupt.</li> <li>0: Disable CP0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>Bit2: EPCA0: Enable Programmable Counter Array (PCA0) Interrupt.<br/>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable interrupt requests generated by PCA0.</li> <li>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.<br/>This bit sets the masking of the ADC0 Conversion Complete interrupt.</li> <li>0: Disable ADC0 Conversion Complete Interrupt.</li> <li>1: Enable interrupt requests generated by the ADOINT flag.</li> <li>Bit0: EWADC0: Enable ADC0 Window Comparison Interrupt.</li> <li>This bit sets the masking of the ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |               |                   |              | I interrupt.  |              |              |        |             |  |

| <ul> <li>Bit4: ECPR: Enable Comparator 0 Rising Edge Interrupt<br/>This bit sets the masking of the CP0 Rising Edge interrupt.</li> <li>0: Disable CP0 Rising Edge Interrupt.</li> <li>1: Enable CP0 Rising Edge Interrupt.</li> <li>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt<br/>This bit sets the masking of the CP0 Falling Edge interrupt.</li> <li>0: Disable CP0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>Bit2: EPCA0: Enable Programmable Counter Array (PCA0) Interrupt.<br/>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable interrupt requests generated by PCA0.</li> <li>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.</li> <li>0: Disable ADC0 Conversion Complete Interrupt.</li> <li>1: Enable interrupt requests generated by the AD0INT flag.</li> <li>Bit0: EWADC0: Enable ADC0 Window Comparison Interrupt.</li> <li>0: Disable ADC0 Window Comparison Interrupt.</li> <li>0: Disable ADC0 Window Comparison Interrupt.</li> <li>0: Disable ADC0 Window Comparison Interrupt.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |               |                   |              |               |              |              |        |             |  |

| <ul> <li>This bit sets the masking of the CPO Rising Edge interrupt.</li> <li>0: Disable CPO Rising Edge Interrupt.</li> <li>1: Enable CPO Rising Edge Interrupt.</li> <li>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt</li> <li>This bit sets the masking of the CPO Falling Edge interrupt.</li> <li>0: Disable CPO Falling Edge Interrupt.</li> <li>1: Enable CPO Falling Edge Interrupt.</li> <li>1: Enable CPO Falling Edge Interrupt.</li> <li>Bit2: EPCA0: Enable Programmable Counter Array (PCA0) Interrupt.</li> <li>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable interrupt requests generated by PCA0.</li> <li>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.</li> <li>This bit sets the masking of the ADC0 Conversion Complete interrupt.</li> <li>0: Disable ADC0 Conversion Complete Interrupt.</li> <li>1: Enable interrupt requests generated by the AD0INT flag.</li> <li>Bit0: EWADC0: Enable ADC0 Window Comparison Interrupt.</li> <li>This bit sets the masking of the ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | D:44  |               |                   | •            | a Edao Into   | *****        |              |        |             |  |

| <ul> <li>0: Disable CP0 Rising Edge Interrupt.</li> <li>1: Enable CP0 Rising Edge Interrupt.</li> <li>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt<br/>This bit sets the masking of the CP0 Falling Edge interrupt.</li> <li>0: Disable CP0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>Bit2: EPCA0: Enable Programmable Counter Array (PCA0) Interrupt.<br/>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable interrupt requests generated by PCA0.</li> <li>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.<br/>This bit sets the masking of the ADC0 Conversion Complete Interrupt.</li> <li>0: Disable ADC0 Conversion Complete Interrupt.</li> <li>1: Enable interrupt requests generated by the AD0INT flag.</li> <li>Bit0: EWADC0: Enable ADC0 Window Comparison Interrupt.<br/>This bit sets the masking of the ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DIT4. |               |                   |              |               |              |              |        |             |  |

| <ul> <li>1: Enable CP0 Rising Edge Interrupt.</li> <li>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt<br/>This bit sets the masking of the CP0 Falling Edge interrupt.</li> <li>0: Disable CP0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>Bit2: EPCA0: Enable Programmable Counter Array (PCA0) Interrupt.<br/>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable interrupt requests generated by PCA0.</li> <li>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.<br/>This bit sets the masking of the ADC0 Conversion Complete interrupt.</li> <li>0: Disable ADC0 Conversion Complete Interrupt.</li> <li>1: Enable interrupt requests generated by the AD0INT flag.</li> <li>Bit0: EWADC0: Enable ADC0 Window Comparison Interrupt.<br/>This bit sets the masking of the ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |               |                   | •            | •             | ge menup     |              |        |             |  |

| <ul> <li>Bit3: ECPF: Enable Comparator 0 Falling Edge Interrupt<br/>This bit sets the masking of the CP0 Falling Edge interrupt.</li> <li>0: Disable CP0 Falling Edge Interrupt.</li> <li>Bit2: EPCA0: Enable Programmable Counter Array (PCA0) Interrupt.</li> <li>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable interrupt requests generated by PCA0.</li> <li>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.</li> <li>This bit sets the masking of the ADC0 Conversion Complete interrupt.</li> <li>0: Disable ADC0 Conversion Complete Interrupt.</li> <li>1: Enable interrupt requests generated by the AD0INT flag.</li> <li>Bit0: EWADC0: Enable ADC0 Window Comparison Interrupt.</li> <li>This bit sets the masking of the ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |               | •                 | •            | •             |              |              |        |             |  |

| <ul> <li>This bit sets the masking of the CP0 Falling Edge interrupt.</li> <li>0: Disable CP0 Falling Edge Interrupt.</li> <li>1: Enable CP0 Falling Edge Interrupt.</li> <li>Bit2: EPCA0: Enable Programmable Counter Array (PCA0) Interrupt.</li> <li>This bit sets the masking of the PCA0 interrupts.</li> <li>0: Disable all PCA0 interrupts.</li> <li>1: Enable interrupt requests generated by PCA0.</li> <li>Bit1: EADC0: Enable ADC0 Conversion Complete Interrupt.</li> <li>This bit sets the masking of the ADC0 Conversion Complete interrupt.</li> <li>0: Disable ADC0 Conversion Complete Interrupt.</li> <li>1: Enable interrupt requests generated by the AD0INT flag.</li> <li>Bit0: EWADC0: Enable ADC0 Window Comparison Interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> <li>0: Disable ADC0 Window Comparison interrupt.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Bit3  |               | •                 | •            |               | rrupt        |              |        |             |  |