Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| 2000                       |                                                                   |

|----------------------------|-------------------------------------------------------------------|

| Product Status             | Active                                                            |

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | SPI, UART/USART                                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                |

| Number of I/O              | 16                                                                |

| Program Memory Size        | 8KB (8K x 8)                                                      |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 256 x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.25V                                                        |

| Data Converters            | A/D 16x12b                                                        |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 20-VFQFN Exposed Pad                                              |

| Supplier Device Package    | 20-QFN (4x4)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f531-c-imr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 8.3.2. Stop Mode                                                    | 90  |

|---------------------------------------------------------------------|-----|

| 8.3.3. Suspend Mode                                                 |     |

| 9. Memory Organization and SFRs                                     | 92  |

| 9.1. Program Memory                                                 |     |

| 9.2. Data Memory                                                    |     |

| 9.3. General Purpose Registers                                      | 93  |

| 9.4. Bit Addressable Locations                                      | 93  |

| 9.5. Stack                                                          | 93  |

| 9.6. Special Function Registers                                     | 93  |

| 10. Interrupt Handler                                               | 98  |

| 10.1. MCU Interrupt Sources and Vectors                             | 98  |

| 10.2. Interrupt Priorities                                          |     |

| 10.3. Interrupt Latency                                             | 98  |

| 10.4. Interrupt Register Descriptions                               | 100 |

| 10.5. External Interrupts                                           | 104 |

| 11. Reset Sources                                                   |     |

| 11.1. Power-On Reset                                                |     |

| 11.2. Power-Fail Reset / VDD Monitors (VDDMON0 and VDDMON1)         | 108 |

| 11.2.1. VDD Monitor Thresholds and Minimum VDD                      | 108 |

| 11.3. External Reset                                                |     |

| 11.4. Missing Clock Detector Reset                                  |     |

| 11.5. Comparator Reset                                              | 110 |

| 11.6. PCA Watchdog Timer Reset                                      | 110 |

| 11.7. Flash Error Reset                                             | 110 |

| 11.8. Software Reset                                                | 111 |

| 12. Flash Memory                                                    | 113 |

| 12.1. Programming The Flash Memory                                  |     |

| 12.1.1. Flash Lock and Key Functions                                |     |

| 12.1.2. Flash Erase Procedure                                       |     |

| 12.1.3. Flash Write Procedure                                       |     |

| 12.2. Flash Write and Erase Guidelines                              | -   |

| 12.2.1. V <sub>DD</sub> Maintenance and the V <sub>DD</sub> monitor |     |

| 12.2.2. PSWE Maintenance                                            |     |

| 12.2.3. System Clock                                                |     |

| 12.3. Non-volatile Data Storage                                     |     |

| 12.4. Security Options                                              |     |

| 13. Port Input/Output                                               |     |

| 13.1. Priority Crossbar Decoder                                     |     |

| 13.2. Port I/O Initialization                                       |     |

| 13.3. General Purpose Port I/O                                      |     |

| 14. Oscillators                                                     |     |

| 14.1. Programmable Internal Oscillator                              |     |

| 14.1.1. Internal Oscillator Suspend Mode                            |     |

| 14.2. External Oscillator Drive Circuit                             |     |

| 14.2.1. Clocking Timers Directly Through the External Oscillator    | 139 |

| 19. Programmable Counter Array (PCA0)1             | 195 |

|----------------------------------------------------|-----|

| 19.1. PCA Counter/Timer 1                          |     |

| 19.2. Capture/Compare Modules 1                    | 197 |

| 19.2.1. Edge-triggered Capture Mode 1              | 198 |

| 19.2.2. Software Timer (Compare) Mode 1            |     |

| 19.2.3. High Speed Output Mode                     |     |

| 19.2.4. Frequency Output Mode                      |     |

| 19.2.5. 8-Bit Pulse Width Modulator Mode           |     |

| 19.2.6. 16-Bit Pulse Width Modulator Mode          |     |

| 19.3. Watchdog Timer Mode                          | 203 |

| 19.3.1. Watchdog Timer Operation                   |     |

| 19.3.2. Watchdog Timer Usage                       |     |

| 19.4. Register Descriptions for PCA 2              |     |

| 20. Device Specific Behavior                       |     |

| 20.1. Device Identification                        |     |

| 20.2. Reset Pin Behavior                           | 211 |

| 20.3. Reset Time Delay                             | 211 |

| 20.4. VDD Monitors and VDD Ramp Time               |     |

| 20.5. VDD Monitor (VDDMON0) High Threshold Setting | 212 |

| 20.6. Reset Low Time                               |     |

| 20.7. Internal Oscillator Suspend Mode 2           |     |

| 20.8. UART Pins                                    | 213 |

| 20.9. LIN                                          | 213 |

| 20.9.1. Stop Bit Check                             | 213 |

| 20.9.2. Synch Break and Synch Field Length Check   | 213 |

| 21. C2 Interface                                   |     |

| 21.1. C2 Interface Registers                       | 214 |

| 21.2. C2 Pin Sharing                               | 216 |

| Document Change List                               | 217 |

| Contact Information                                |     |

| SFR Definition 13.13. P0SKIP: Port0 Skip                           | 134 |

|--------------------------------------------------------------------|-----|

| SFR Definition 13.14. P1MAT: Port1 Match                           | 134 |

| SFR Definition 13.15. P1MASK: Port1 Mask                           |     |

| SFR Definition 14.1. OSCICN: Internal Oscillator Control           |     |

| SFR Definition 14.2. OSCICL: Internal Oscillator Calibration       |     |

| SFR Definition 14.3. OSCIFIN: Internal Fine Oscillator Calibration |     |

| SFR Definition 14.4. OSCXCN: External Oscillator Control           | 142 |

| SFR Definition 14.5. CLKSEL: Clock Select                          |     |

| SFR Definition 15.1. SCON0: Serial Port 0 Control                  |     |

| SFR Definition 15.2. SBUF0: Serial (UART0) Port Data Buffer        |     |

| SFR Definition 16.1. SPI0CFG: SPI0 Configuration                   | 157 |

| SFR Definition 16.2. SPI0CN: SPI0 Control                          |     |

| SFR Definition 16.3. SPI0CKR: SPI0 Clock Rate                      |     |

| SFR Definition 16.4. SPI0DAT: SPI0 Data                            |     |

| SFR Definition 17.1. LINADDR: Indirect Address Register            |     |

| SFR Definition 17.2. LINDATA: LIN Data Register                    |     |

| SFR Definition 17.3. LINCF Control Mode Register                   |     |

| SFR Definition 17.4. LIN0DT1: LIN0 Data Byte 1                     |     |

| SFR Definition 17.5. LIN0DT2: LIN0 Data Byte 2                     |     |

| SFR Definition 17.6. LIN0DT3: LIN0 Data Byte 3                     |     |

| SFR Definition 17.7. LIN0DT4: LIN0 Data Byte 4                     |     |

| SFR Definition 17.8. LIN0DT5: LIN0 Data Byte 5                     | 176 |

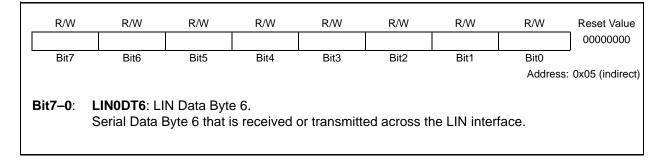

| SFR Definition 17.9. LIN0DT6: LIN0 Data Byte 6                     |     |

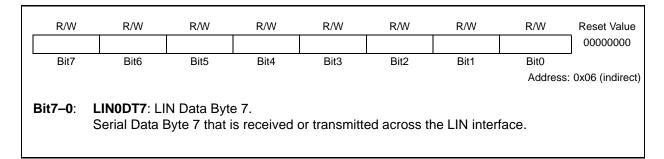

| SFR Definition 17.10. LIN0DT7: LIN0 Data Byte 7                    |     |

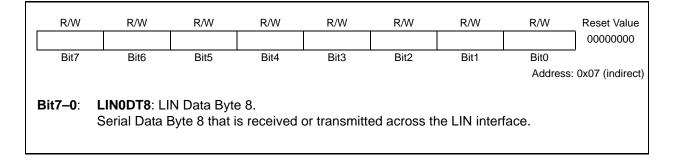

| SFR Definition 17.11. LIN0DT8: LIN0 Data Byte 8                    |     |

| SFR Definition 17.12. LIN0CTRL: LIN0 Control Register              |     |

| SFR Definition 17.13. LIN0ST: LIN0 STATUS Register                 |     |

| SFR Definition 17.14. LIN0ERR: LIN0 ERROR Register                 |     |

| SFR Definition 17.15. LIN0SIZE: LIN0 Message Size Register         | 180 |

| SFR Definition 17.16. LIN0DIV: LIN0 Divider Register               |     |

| SFR Definition 17.17. LIN0MUL: LIN0 Multiplier Register            |     |

| SFR Definition 17.18. LIN0ID: LIN0 ID Register                     |     |

| SFR Definition 18.1. TCON: Timer Control                           |     |

| SFR Definition 18.2. TMOD: Timer Mode                              |     |

| SFR Definition 18.3. CKCON: Clock Control                          |     |

| SFR Definition 18.4. TL0: Timer 0 Low Byte                         |     |

| SFR Definition 18.5. TL1: Timer 1 Low Byte                         |     |

| SFR Definition 18.6. TH0: Timer 0 High Byte                        |     |

| SFR Definition 18.7. TH1: Timer 1 High Byte                        |     |

| SFR Definition 18.8. TMR2CN: Timer 2 Control                       |     |

| SFR Definition 18.9. TMR2RLL: Timer 2 Reload Register Low Byte     |     |

| SFR Definition 18.10. TMR2RLH: Timer 2 Reload Register High Byte   |     |

| SFR Definition 18.11. TMR2L: Timer 2 Low Byte                      |     |

| SFR Definition 18.12. TMR2H Timer 2 High Byte                      | 194 |

| SFR Definition 19.1. PCA0CN: PCA Control                           | 206 |

|                                                                    |     |

### **Table 2.8. Reset Electrical Characteristics**

-40 to +125 °C unless otherwise specified.

| Parameter                                                      | Conditions                                                                                 | Min                         | Тур                     | Мах                         | Units                |  |  |  |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------|-------------------------|-----------------------------|----------------------|--|--|--|

| RST Output Low Voltage                                         | I <sub>OL</sub> = 8.5 mA, V <sub>DD</sub> =<br>2.1 V                                       | _                           | _                       | 0.8                         | V                    |  |  |  |

| RST Input High Voltage                                         |                                                                                            | 0.7 x<br>V <sub>REGIN</sub> |                         | _                           | V                    |  |  |  |

| RST Input Low Voltage                                          |                                                                                            |                             |                         | 0.3 x<br>V <sub>REGIN</sub> | V                    |  |  |  |

| RST Input Pullup Impedance                                     | $V_{REGIN} = 1.8 V$<br>$V_{REGIN} = 2.7 V$<br>$V_{REGIN} = 3.3 V$<br>$V_{REGIN} = 5 V$     |                             | 330<br>160<br>130<br>80 |                             | kΩ<br>kΩ<br>kΩ<br>kΩ |  |  |  |

| Missing Clock Detector Timeout                                 | Time from last system<br>clock rising edge to reset<br>initiation                          | 100                         | 350                     | 650                         | μs                   |  |  |  |

| Reset Time Delay (T <sub>PORDelay</sub> ) <sup>1</sup>         | Delay between release<br>of any reset source and<br>code execution at loca-<br>tion 0x0000 |                             |                         | 350                         | μs                   |  |  |  |

| Minimum RST Low Time to Generate a System Reset                |                                                                                            | 10                          | _                       | _                           | μs                   |  |  |  |

| V <sub>DD</sub> Monitor (VDDMON0)                              |                                                                                            |                             |                         | •                           |                      |  |  |  |

| Low Threshold (V <sub>RST-LOW</sub> ) <sup>1,2,3</sup>         | C8051F52x/53x<br>C8051F52xA/53xA<br>C8051F52x-C/53x-C                                      | 1.8<br>1.65<br>1.65         | 1.9<br>1.75<br>1.75     | 2.0<br>1.8<br>1.8           | V<br>V<br>V          |  |  |  |

| High Threshold (V <sub>RST-HIGH</sub> ) <sup>3</sup>           | C8051F52x/53x<br>C8051F52xA/53xA<br>C8051F52x-C/53x-C                                      | 2.1<br>2.25<br>2.25         | 2.2<br>2.3<br>2.3       | 2.3<br>2.4<br>2.45          | V<br>V<br>V          |  |  |  |

| Turn-on Time                                                   |                                                                                            | _                           | 83                      |                             | μs                   |  |  |  |

| Supply Current                                                 | V <sub>DD</sub> = 2.1 V                                                                    | _                           | 1                       | 2                           | μA                   |  |  |  |

| Level-Sensitive V <sub>DD</sub> Monitor (VDDMON1) <sup>1</sup> |                                                                                            |                             |                         |                             |                      |  |  |  |

| Threshold (V <sub>RST1</sub> ) <sup>1,2,3</sup>                | C8051F52x-C/53x-C                                                                          | 1.6                         | 1.75                    | 1.9                         | V                    |  |  |  |

| Supply Current                                                 | C8051F52x-C/53x-C                                                                          |                             | 3                       | 6                           | μA                   |  |  |  |

| Notes:<br>1. Refer to Section "20. Device Specific             | Behavior" on page 210.                                                                     |                             |                         |                             |                      |  |  |  |

- Refer to Section "20. Device Specific Behavior" on page 210.

The POR threshold (V<sub>RST</sub>) is V<sub>RST-LOW</sub> or V<sub>RST1</sub>, whichever is higher.

The V<sub>RST</sub> threshold for power fail / brownout is the higher of VDDMON0 and VDDMON1 thresholds, if both are enabled.

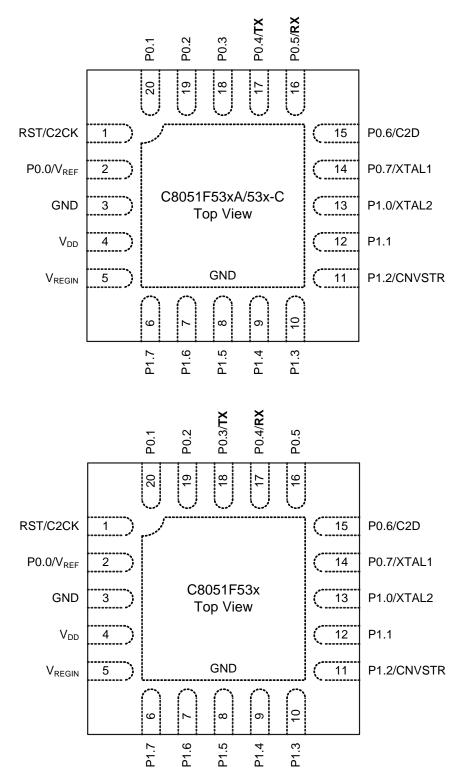

Figure 3.7. QFN-20 Pinout Diagram (Top View)

less than 100 nA. See Section "13.1. Priority Crossbar Decoder" on page 122 for details on configuring Comparator outputs via the digital Crossbar. Comparator inputs can be externally driven from -0.25 V to (V<sub>REGIN</sub>) + 0.25 V without damage or upset. The complete Comparator electrical specifications are given in Table 2.7 on page 31.

The Comparator response time may be configured in software via the CPTnMD register (see SFR Definition 7.3). Selecting a longer response time reduces the Comparator supply current. See Table 2.7 on page 31 for complete timing and current consumption specifications.

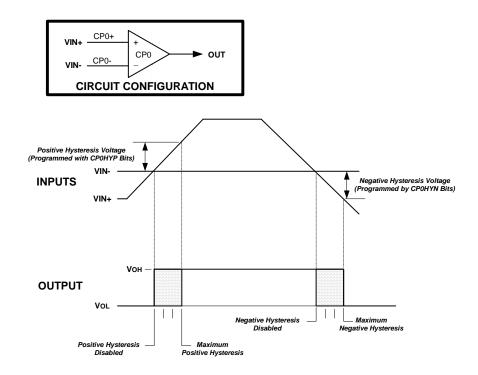

Figure 7.2. Comparator Hysteresis Plot

The Comparator hysteresis is software-programmable via its Comparator Control register CPT0CN. The user can program both the amount of hysteresis voltage (referred to the input voltage) and the positive and negative-going symmetry of this hysteresis around the threshold voltage.

The Comparator hysteresis is programmed using Bits3–0 in the Comparator Control Register CPT0CN (shown in SFR Definition 7.1). The amount of negative hysteresis voltage is determined by the settings of the CP0HYN bits. As shown in Table 2.7 on page 31, settings of 20, 10 or 5 mV of negative hysteresis can be programmed, or negative hysteresis can be disabled. In a similar way, the amount of positive hysteresis is determined by the setting the CP0HYP bits.

Comparator interrupts can be generated on both rising-edge and falling-edge output transitions. (For Interrupt enable and priority control, see Section "10. Interrupt Handler" on page 98). The CP0FIF flag is set to logic 1 upon a Comparator falling-edge detect, and the CP0RIF flag is set to logic 1 upon the Comparator rising-edge detect. Once set, these bits remain set until cleared by software. The output state of the Comparator can be obtained at any time by reading the CP0OUT bit. The Comparator is enabled by setting the CP0EN bit to logic 1 and is disabled by clearing this bit to logic 0. When the Comparator is enabled, the internal oscillator is awakened from SUSPEND mode if the Comparator output is logic 0.

### 8.1.2. MOVX Instruction and Program Memory

The MOVX instruction is typically used to access data stored in XDATA memory space. In the CIP-51, the MOVX instruction can also be used to write or erase on-chip program memory space implemented as reprogrammable Flash memory. The Flash access feature provides a mechanism for the CIP-51 to update program code and use the program memory space for non-volatile data storage. Refer to Section "12. Flash Memory" on page 113 for further details.

| Mnemonic              | Description                              | Bytes | Clock<br>Cycles |  |  |  |  |  |

|-----------------------|------------------------------------------|-------|-----------------|--|--|--|--|--|

| Arithmetic Operations |                                          |       |                 |  |  |  |  |  |

| ADD A, Rn             | Add register to A                        | 1     | 1               |  |  |  |  |  |

| ADD A, direct         | Add direct byte to A                     | 2     | 2               |  |  |  |  |  |

| ADD A, @Ri            | Add indirect RAM to A                    | 1     | 2               |  |  |  |  |  |

| ADD A, #data          | Add immediate to A                       | 2     | 2               |  |  |  |  |  |

| ADDC A, Rn            | Add register to A with carry             | 1     | 1               |  |  |  |  |  |

| ADDC A, direct        | Add direct byte to A with carry          | 2     | 2               |  |  |  |  |  |

| ADDC A, @Ri           | Add indirect RAM to A with carry         | 1     | 2               |  |  |  |  |  |

| ADDC A, #data         | Add immediate to A with carry            | 2     | 2               |  |  |  |  |  |

| SUBB A, Rn            | Subtract register from A with borrow     | 1     | 1               |  |  |  |  |  |

| SUBB A, direct        | Subtract direct byte from A with borrow  | 2     | 2               |  |  |  |  |  |

| SUBB A, @Ri           | Subtract indirect RAM from A with borrow | 1     | 2               |  |  |  |  |  |

| SUBB A, #data         | Subtract immediate from A with borrow    | 2     | 2               |  |  |  |  |  |

| INC A                 | Increment A                              | 1     | 1               |  |  |  |  |  |

| INC Rn                | Increment register                       | 1     | 1               |  |  |  |  |  |

| INC direct            | Increment direct byte                    | 2     | 2               |  |  |  |  |  |

| INC @Ri               | Increment indirect RAM                   | 1     | 2               |  |  |  |  |  |

| DEC A                 | Decrement A                              | 1     | 1               |  |  |  |  |  |

| DEC Rn                | Decrement register                       | 1     | 1               |  |  |  |  |  |

| DEC direct            | Decrement direct byte                    | 2     | 2               |  |  |  |  |  |

| DEC @Ri               | Decrement indirect RAM                   | 1     | 2               |  |  |  |  |  |

| INC DPTR              | Increment Data Pointer                   | 1     | 1               |  |  |  |  |  |

| MUL AB                | Multiply A and B                         | 1     | 4               |  |  |  |  |  |

| DIV AB                | Divide A by B                            | 1     | 8               |  |  |  |  |  |

| DA A                  | Decimal adjust A                         | 1     | 1               |  |  |  |  |  |

| Logical Operations    | ·                                        |       |                 |  |  |  |  |  |

| ANL A, Rn             | AND Register to A                        | 1     | 1               |  |  |  |  |  |

| ANL A, direct         | AND direct byte to A                     | 2     | 2               |  |  |  |  |  |

| ANL A, @Ri            | AND indirect RAM to A                    | 1     | 2               |  |  |  |  |  |

| ANL A, #data          | AND immediate to A                       | 2     | 2               |  |  |  |  |  |

| ANL direct, A         | AND A to direct byte                     | 2     | 2               |  |  |  |  |  |

| ANL direct, #data     | AND immediate to direct byte             | 3     | 3               |  |  |  |  |  |

| ORL A, Rn             | OR Register to A                         | 1     | 1               |  |  |  |  |  |

| ORL A, direct         | OR direct byte to A                      | 2     | 2               |  |  |  |  |  |

| ORL A, @Ri            | OR indirect RAM to A                     | 1     | 2               |  |  |  |  |  |

| ORL A, #data          | OR immediate to A                        | 2     | 2               |  |  |  |  |  |

| ORL direct, A         | OR A to direct byte                      | 2     | 2               |  |  |  |  |  |

### Notes on Registers, Operands and Addressing Modes:

**Rn** - Register R0–R7 of the currently selected register bank.

@Ri - Data RAM location addressed indirectly through R0 or R1.

**rel** - 8-bit, signed (two's complement) offset relative to the first byte of the following instruction. Used by SJMP and all conditional jumps.

**direct** - 8-bit internal data location's address. This could be a direct-access Data RAM location (0x00– 0x7F) or an SFR (0x80–0xFF).

#data - 8-bit constant

#data16 - 16-bit constant

**bit** - Direct-accessed bit in Data RAM or SFR

**addr11** - 11-bit destination address used by ACALL and AJMP. The destination must be within the same 2 kB page of program memory as the first byte of the following instruction.

**addr16** - 16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 7680 bytes of program memory space.

There is one unused opcode (0xA5) that performs the same function as NOP. All mnemonics copyrighted © Intel Corporation 1980.

### 8.2. Register Descriptions

Following are descriptions of SFRs related to the operation of the CIP-51 System Controller. Reserved bits should not be set to logic 1. Future product versions may use these bits to implement new features in which case the reset value of the bit will be logic 0, selecting the feature's default state. Detailed descriptions of the remaining SFRs are included in the sections of the datasheet associated with their corresponding system function.

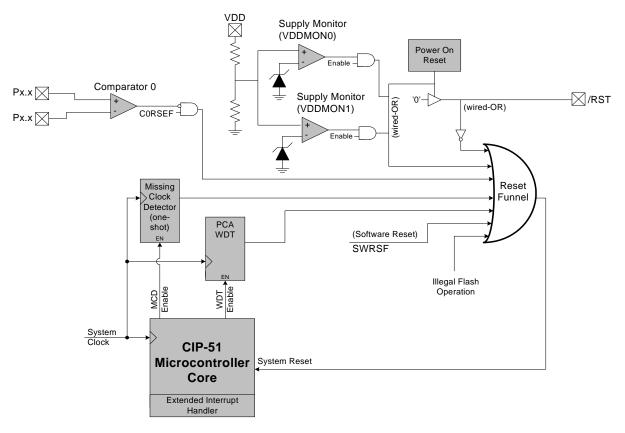

# 11. Reset Sources

Reset circuitry allows the controller to be easily placed in a predefined default condition. On entry to this reset state, the following occur:

- CIP-51 halts program execution

- Special Function Registers (SFRs) are initialized to their defined reset values

- External Port pins are forced to a known state

- Interrupts and timers are disabled.

All SFRs are reset to the predefined values noted in the SFR detailed descriptions. The contents of internal data memory are unaffected during a reset; any previously stored data is preserved. However, since the stack pointer SFR is reset, the stack is effectively lost, even though the data on the stack is not altered.

The Port I/O latches are reset to 0xFF (all logic ones) in open-drain mode. Weak pullups are enabled during and after the reset. For  $V_{DD}$  Monitor and power-on resets, the  $\overrightarrow{RST}$  pin is driven low until the device exits the reset state.

On exit from the reset state, the program counter (PC) is reset, and the system clock defaults to the internal oscillator. Refer to Section "14. Oscillators" on page 135 for information on selecting and configuring the system clock source. The Watchdog Timer is enabled with the system clock divided by 12 as its clock source (Section "19.3. Watchdog Timer Mode" on page 203 details the use of the Watchdog Timer). Program execution begins at location 0x0000.

Figure 11.1. Reset Sources

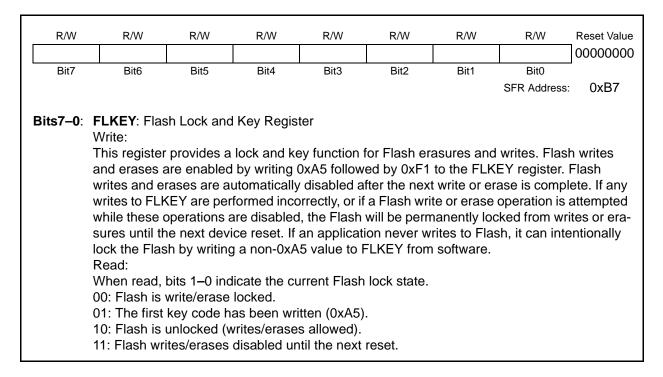

### 12.1.2. Flash Erase Procedure

The Flash memory can be programmed by software using the MOVX write instruction with the address and data byte to be programmed provided as normal operands. Before writing to Flash memory using MOVX, Flash write operations must be enabled by: (1) setting the PSWE Program Store Write Enable bit (PSCTL.0) to logic 1 (this directs the MOVX writes to target Flash memory); and (2) Writing the Flash key codes in sequence to the Flash Lock register (FLKEY). The PSWE bit remains set until cleared by software.

A write to Flash memory can clear bits to logic 0 but cannot set them; only an erase operation can set bits to logic 1 in Flash. A byte location to be programmed should be erased before a new value is written. The Flash memory is organized in 512-byte pages. The erase operation applies to an entire page (setting all bytes in the page to 0xFF). To erase an entire 512-byte page, perform the following steps:

- 1. Disable interrupts (recommended).

- 2. Write the first key code to FLKEY: 0xA5.

- 3. Write the second key code to FLKEY: 0xF1.

- 4. Set the PSEE bit (register PSCTL).

- 5. Set the PSWE bit (register PSCTL).

- 6. Using the MOVX instruction, write a data byte to any location within the 512-byte page to be erased.

- 7. Clear the PSWE and PSEE bits.

- 8. Re-enable interrupts.

- 12.1.3. Flash Write Procedure

Flash bytes are programmed by software with the following sequence:

- 1. Disable interrupts.

- 2. Write the first key code to FLKEY: 0xA5.

- 3. Write the second key code to FLKEY: 0xF1.

- 4. Set the PSWE bit (register PSCTL).

- 5. Clear the PSEE bit (register PSCTL).

- 6. Using the MOVX instruction, write a single data byte to the desired location within the 512-byte sector.

- 7. Clear the PSWE bit.

- 8. Re-enable interrupts.

Steps 2–7 must be repeated for each byte to be written. After Flash writes are complete, PSWE should be cleared so that MOVX instructions do not target program memory.

## SFR Definition 12.1. PSCTL: Program Store R/W Control

| R                 | R                                                                                                                                                                                                                                                                                                                                                                                             | R                              | R                         | R                | R           | R/W  | R/W         | Reset Value |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|---------------------------|------------------|-------------|------|-------------|-------------|

| —                 | —                                                                                                                                                                                                                                                                                                                                                                                             | —                              | —                         | —                | _           | PSEE | PSWE        | 00000000    |

| Bit7              | Bit6                                                                                                                                                                                                                                                                                                                                                                                          | Bit5                           | Bit4                      | Bit3             | Bit2        | Bit1 | Bit0        |             |

|                   |                                                                                                                                                                                                                                                                                                                                                                                               |                                |                           |                  |             |      | SFR Address | s: 0x8F     |

| Bits7–2:<br>Bit1: | UNUSED: R<br>PSEE: Progr<br>Setting this b<br>to be erased                                                                                                                                                                                                                                                                                                                                    | ram Store Er<br>bit (in combir | rase Enabl<br>nation with | le<br>PSWE) allo | ws an entir |      |             |             |

|                   | to be erased. If this bit is logic 1 and Flash writes are enabled (PSWE is logic 1), a write to<br>Flash memory using the MOVX instruction will erase the entire page that contains the loca-<br>tion addressed by the MOVX instruction. The value of the data byte written does not matter.<br>0: Flash program memory erasure disabled.<br>1: Flash program memory erasure enabled.         |                                |                           |                  |             |      |             |             |

| Bit0:             | <ul> <li>PSWE: Program Store Write Enable</li> <li>Setting this bit allows writing a byte of data to the Flash program memory using the MOVX write instruction. The Flash location should be erased before writing data.</li> <li>0: Writes to Flash program memory disabled.</li> <li>1: Writes to Flash program memory enabled; the MOVX write instruction targets Flash memory.</li> </ul> |                                |                           |                  |             |      |             |             |

| Note: See         | <b>Note</b> : See Section "12.1. Programming The Flash Memory" on page 113 for minimum V <sub>DD</sub> and temperature requirements for flash erase and write operations.                                                                                                                                                                                                                     |                                |                           |                  |             |      |             |             |

## SFR Definition 12.2. FLKEY: Flash Lock and Key

## **15.2. Operational Modes**

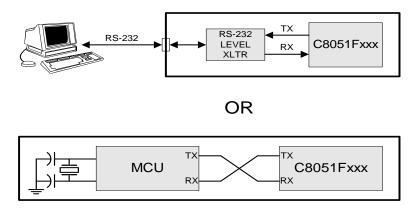

UART0 provides standard asynchronous, full duplex communication. The UART mode (8-bit or 9-bit) is selected by the S0MODE bit (SCON0.7). Typical UART connection options are shown below.

Figure 15.3. UART Interconnect Diagram

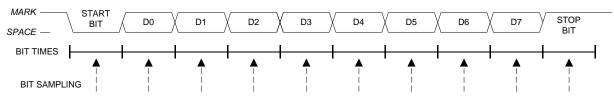

### 15.2.1. 8-Bit UART

8-Bit UART mode uses a total of 10 bits per data byte: one start bit, eight data bits (LSB first), and one stop bit. Data are transmitted LSB first from the TX0 pin and received at the RX0 pin. On receive, the eight data bits are stored in SBUF0 and the stop bit goes into RB80 (SCON0.2).

Data transmission begins when software writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to logic 1. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: RI0 must be logic 0, and if MCE0 is logic 1, the stop bit must be logic 1. In the event of a receive data overrun, the first received 8 bits are latched into the SBUF0 receive register and the following overrun data bits are lost.

If these conditions are met, the eight bits of data is stored in SBUF0, the stop bit is stored in RB80 and the RI0 flag is set. If these conditions are not met, SBUF0 and RB80 will not be loaded and the RI0 flag will not be set. An interrupt will occur if enabled when either TI0 or RI0 is set.

Figure 15.4. 8-Bit UART Timing Diagram

#### SFR Definition 15.1. SCON0: Serial Port 0 Control R/W R/W R/W Reset Value R R/W R/W R/W R/W SOMODE RI0 01000000 -MCE0 REN0 TB80 **RB80** TI0 Bit Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Addressable SFR Address: 0x98 Bit7: SOMODE: Serial Port 0 Operation Mode. This bit selects the UART0 Operation Mode. 0: 8-bit UART with Variable Baud Rate. 1: 9-bit UART with Variable Baud Rate. Bit6: **UNUSED**. Read = 1b. Write = don't care. Bit5: MCE0: Multiprocessor Communication Enable. The function of this bit is dependent on the Serial Port 0 Operation Mode. SOMODE = 0: Checks for valid stop bit. 0: Logic level of stop bit is ignored. 1: RIO will only be activated if stop bit is logic level 1. S0MODE = 1: Multiprocessor Communications Enable. 0: Logic level of ninth bit is ignored. 1: RI0 is set and an interrupt is generated only when the ninth bit is logic 1. Bit4: **REN0:** Receive Enable. This bit enables/disables the UART receiver. 0: UART0 reception disabled. 1: UART0 reception enabled. Bit3: TB80: Ninth Transmission Bit. The logic level of this bit will be assigned to the ninth transmission bit in 9-bit UART Mode. It is not used in 8-bit UART Mode. Set or cleared by software as required. Bit2: RB80: Ninth Receive Bit. RB80 is assigned the value of the STOP bit in Mode 0; it is assigned the value of the 9th data bit in Mode 1. Bit1: TIO: Transmit Interrupt Flag. Set by hardware when a byte of data has been transmitted by UART0 (after the 8th bit in 8bit UART Mode, or at the beginning of the STOP bit in 9-bit UART Mode). When the UART0 interrupt is enabled, setting this bit causes the CPU to vector to the UART0 interrupt service routine. This bit must be cleared manually by software. Bit0: RIO: Receive Interrupt Flag. Set to 1 by hardware when a byte of data has been received by UART0 (set at the STOP bit sampling time). When the UART0 interrupt is enabled, setting this bit to 1 causes the CPU to vector to the UART0 interrupt service routine. This bit must be cleared manually by software.

# SFR Definition 16.1. SPI0CFG: SPI0 Configuration

| R         | R/W                                                                                                                               | R/W            | R/W         | R             | R            | R             | R              | Reset Value |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|---------------|--------------|---------------|----------------|-------------|--|

| SPIBSY    | MSTEN                                                                                                                             | CKPHA          | CKPOL       | SLVSEL        | NSSIN        | SRMT          | RXBMT          | 00000111    |  |

| Bit7      | Bit6                                                                                                                              | Bit5           | Bit4        | Bit3          | Bit2         | Bit1          | Bit0           |             |  |

|           | SFR Address: 0xA1                                                                                                                 |                |             |               |              |               |                |             |  |

|           |                                                                                                                                   |                |             |               |              |               |                |             |  |

| Bit 7:    | <b>SPIBSY</b> : SPI Busy (read only).<br>This bit is set to logic 1 when a SPI transfer is in progress (Master or Slave Mode).    |                |             |               |              |               |                |             |  |

| Bit 6:    | MSTEN: Ma                                                                                                                         |                |             | i transfer is | in progress  | (Master or    | Slave Mode     | e).         |  |

| DIL 0.    | 0: Disable m                                                                                                                      |                |             | n slave mod   | <u>م</u>     |               |                |             |  |

|           | 1: Enable ma                                                                                                                      |                |             |               | с.           |               |                |             |  |

| Bit 5:    | CKPHA: SP                                                                                                                         |                |             | s a master.   |              |               |                |             |  |

| Dit J.    | This bit cont                                                                                                                     |                |             | ise           |              |               |                |             |  |

|           | 0: Data cent                                                                                                                      |                |             |               |              |               |                |             |  |

|           | 1: Data cent                                                                                                                      |                |             |               | d.*          |               |                |             |  |

| Bit 4:    | CKPOL: SP                                                                                                                         |                |             |               | -            |               |                |             |  |

|           | This bit cont                                                                                                                     |                |             | arity.        |              |               |                |             |  |

|           | 0: SCK line I                                                                                                                     | ow in idle s   | tate.       |               |              |               |                |             |  |

|           | 1: SCK line h                                                                                                                     | high in idle s | state.      |               |              |               |                |             |  |

| Bit 3:    | SLVSEL: Sla                                                                                                                       | ave Selecte    | d Flag (rea | d only).      |              |               |                |             |  |

|           | This bit is se                                                                                                                    | •              |             |               |              | •             |                |             |  |

|           | is cleared to                                                                                                                     |                |             |               |              |               |                |             |  |

|           | instantaneou                                                                                                                      |                |             |               |              | ed version of | of the pin in  | put.        |  |

| Bit 2:    | NSSIN: NSS                                                                                                                        |                |             | •             | • /          |               |                |             |  |

|           | This bit mim                                                                                                                      |                |             |               | •            | the NSS po    | ort pin at the | e time that |  |

|           | the register i                                                                                                                    |                | •           | •             |              |               |                |             |  |

| Bit 1:    | SRMT: Shift                                                                                                                       |                |             |               |              |               |                | .,          |  |

|           | This bit will b                                                                                                                   |                |             |               |              |               |                | •           |  |

|           | and there is                                                                                                                      |                |             |               |              |               |                |             |  |

|           | receive buffe<br>the transmit                                                                                                     |                |             |               | byte is tran | isterred to t | ne sniit regi  | ster from   |  |

|           | NOTE: SRM                                                                                                                         |                |             |               |              |               |                |             |  |

| Bit 0:    | RXBMT: Red                                                                                                                        |                |             |               | Mode read    | l only)       |                |             |  |

| DIL U.    | This bit will b                                                                                                                   |                |             |               |              |               | nd contains    | no new      |  |

|           |                                                                                                                                   |                |             |               |              |               |                |             |  |

|           | information. If there is new information available in the receive buffer that has not been read, this bit will return to logic 0. |                |             |               |              |               |                |             |  |

|           | NOTE: RXBMT = 1 when in Master Mode.                                                                                              |                |             |               |              |               |                |             |  |

|           |                                                                                                                                   |                |             |               |              |               |                |             |  |

| te: See T | able 16.1 for ti                                                                                                                  | ming parame    | eters.      |               |              |               |                |             |  |

|           |                                                                                                                                   | 01             |             |               |              |               |                |             |  |

in progress. The same applies to changes in the LIN interface mode from slave mode to master mode and from master mode to slave mode.

## 17.5. Sleep Mode and Wake-Up

To reduce the system's power consumption, the LIN Protocol Specification defines a Sleep Mode. The message used to broadcast a Sleep Mode request must be transmitted by the LIN master application in the same way as a normal transmit message. The LIN slave application must decode the Sleep Mode Frame from the Identifier and data bytes. After that, the LIN slave node must be put into the Sleep Mode by setting the SLEEP bit (LINOCTRL.6).

If the SLEEP bit (LIN0CTRL.6) of the LIN slave application is not set and there is no bus activity for four seconds (specified bus idle timeout), the IDLTOUT bit (LIN0ST.6) is set and an interrupt request is generated. After that the application may assume that the LIN bus is in Sleep Mode and set the SLEEP bit (LIN0CTRL.6).

Sending a Wakeup signal from the master or any slave node terminates the Sleep Mode of the LIN bus. To send a Wakeup signal, the application has to set the WUPREQ bit (LIN0CTRL.1). After successful transmission of the wakeup signal, the DONE bit (LIN0ST.0) of the master node is set and an interrupt request is generated. The LIN slave does not generate an interrupt request after successful transmission of the Wakeup signal but it generates an interrupt request if the master does not respond to the Wakeup signal within 150 milliseconds. In that case, the ERROR bit (LIN0ST.2) and TOUT bit (LIN0ERR.2) are set. The application then has to decide whether or not to transmit another Wakeup signal.

All LIN nodes that detect a wakeup signal will set the WAKEUP (LIN0ST.1) and DONE bits (LIN0ST.0) and generate an interrupt request. After that, the application has to clear the SLEEP bit (LIN0CTRL.6) in the LIN slave.

### 17.6. Error Detection and Handling

The LIN peripheral generates an interrupt request and stops the processing of the current frame if it detects an error. The application has to check the type of error by processing LIN0ERR. After that, it has to reset the error register and the ERROR bit (LIN0ST.2) by writing a 1 to the RSTERR bit (LIN0CTRL.2). Starting a new message with the LIN peripheral selected as master or sending a Wakeup signal with the LIN peripheral selected as a master or slave is possible only if ERROR bit (LIN0ST.2) is set to 0.

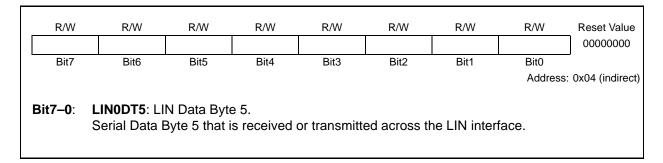

## SFR Definition 17.8. LIN0DT5: LIN0 Data Byte 5

## SFR Definition 17.9. LIN0DT6: LIN0 Data Byte 6

## SFR Definition 17.10. LIN0DT7: LIN0 Data Byte 7

## SFR Definition 17.11. LIN0DT8: LIN0 Data Byte 8

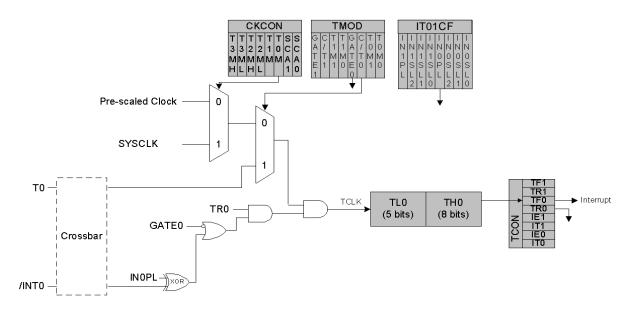

clocked by the system clock. When T0M is cleared, Timer 0 is clocked by the source selected by the Clock Scale bits in CKCON (see SFR Definition 18.3).

Setting the TR0 bit (TCON.4) enables the timer when either GATE0 (TMOD.3) is logic 0 or the input signal INT0 is active as defined by bit IN0PL in register IT01CF (see SFR Definition 10.5. IT01CF: INT0/INT1 Configuration). Setting GATE0 to 1 allows the timer to be controlled by the external input signal INT0 (see Section "10.4. Interrupt Register Descriptions" on page 100), facilitating pulse width measurements.

| TR0            | GATE0 | ΙΝΤΟ | Counter/Timer |  |  |  |

|----------------|-------|------|---------------|--|--|--|

| 0              | Х     | Х    | Disabled      |  |  |  |

| 1              | 0     | Х    | Enabled       |  |  |  |

| 1              | 1     | 0    | Disabled      |  |  |  |

| 1              | 1     | 1    | Enabled       |  |  |  |

| X = Don't Care |       |      |               |  |  |  |

Setting TR0 does not force the timer to reset. The timer registers should be loaded with the desired initial value before the timer is enabled.

TL1 and TH1 form the 13-bit register for Timer 1 in the same manner as described above for TL0 and TH0. Timer 1 is configured and controlled using the relevant TCON and TMOD bits just as with Timer 0. The input signal INT0 is used with Timer 1; the INT0 polarity is defined by bit IN1PL in register IT01CF (see SFR Definition 10.5. IT01CF: INT0/INT1 Configuration).

Figure 18.1. T0 Mode 0 Block Diagram

183

### 19.3.2. Watchdog Timer Usage

To configure the WDT, perform the following tasks:

- Disable the WDT by writing a 0 to the WDTE bit.

- Select the desired PCA clock source (with the CPS2-CPS0 bits).

- Load PCA0CPL2 with the desired WDT update offset value.

- Configure the PCA Idle mode (set CIDL if the WDT should be suspended while the CPU is in Idle mode).

- Enable the WDT by setting the WDTE bit to 1.

The PCA clock source and Idle mode select cannot be changed while the WDT is enabled. The watchdog timer is enabled by setting the WDTE or WDLCK bits in the PCA0MD register. When WDLCK is set, the WDT cannot be disabled until the next system reset. If WDLCK is not set, the WDT is disabled by clearing the WDTE bit.

The WDT is enabled following any reset. The PCA0 counter clock defaults to the system clock divided by 12, PCA0L defaults to 0x00, and PCA0CPL2 defaults to 0x00. Using Equation 19.4, this results in a WDT timeout interval of 3072 system clock cycles. Table 19.3 lists some example timeout intervals for typical system clocks.

| System Clock (Hz)                                     | PCA0CPL2 | Timeout Interval (ms) |

|-------------------------------------------------------|----------|-----------------------|

| 24,500,000                                            | 255      | 32.1                  |

| 24,500,000                                            | 128      | 16.2                  |

| 24,500,000                                            | 32       | 4.1                   |

| 18,432,000                                            | 255      | 42.7                  |

| 18,432,000                                            | 128      | 21.5                  |

| 18,432,000                                            | 32       | 5.5                   |

| 11,059,200                                            | 255      | 71.1                  |

| 11,059,200                                            | 128      | 35.8                  |

| 11,059,200                                            | 32       | 9.2                   |

| 3,062,500                                             | 255      | 257                   |

| 3,062,500                                             | 128      | 129.5                 |

| 3,062,500                                             | 32       | 33.1                  |

| 191,406 <sup>2</sup>                                  | 255      | 4109                  |

| 191,406 <sup>2</sup>                                  | 128      | 2070                  |

| 191,406 <sup>2</sup>                                  | 32       | 530                   |

| 32,000                                                | 255      | 24576                 |

| 32,000                                                | 128      | 12384                 |

| 32,000                                                | 32       | 3168                  |

| Notes:<br>1. Assumes SYSCLK /<br>value of 0x00 at the |          | k source, and a PCA0L |

## Table 19.3. Watchdog Timer Timeout Intervals<sup>1</sup>

2. Internal oscillator reset frequency.

## Revision 1.2 to 1.3

- Updated "System Overview" on page 13 with a voltage range specification for the internal oscillator.

- Updated Table 2.11 on page 34 with new conditions for the internal oscillator accuracy. The internal

oscillator accuracy is dependent on the operating voltage range.

- Updated Section 2 to remove the internal oscillator curve across temperature diagram.

- Updated Figure "4.5 12-Bit ADC Burst Mode Example with Repeat Count Set to 4" on page 58 with new timing diagram when using CNVSTR pin.

- Updated SFR Definition 5.1 (REF0CN) with oscillator suspend requirement for ZTCEN.

- Updated SFR Definition 6.1 (REG0CN) with a new definition for Bit 6. The bit 6 reset value is 1b and must be written to 1b.

- Updated Section "8.3.3. Suspend Mode" on page 90 with note regarding ZTCEN.

- Updated Section "17. LIN (C8051F520/0A/3/3A/6/6A and C8051F530/0A/3/3A/6/6A)" on page 164 with a voltage range specification for the internal oscillator.

## Revision 1.3 to 1.4

- Added 'AEC-Q100' qualification information on page 1.

- Changed page headers throughout the document from 'C8051F52x/F52xA/F53x/F53xA' to 'C8051F52x/53x'.

- Updated supply voltage to "2.0 to 5.25 V" on page 1 and in Section 1 on page 13.

- Corrected reference to development kit (C8051F530DK) in Section "1.2.4. On-Chip Debug Circuitry" on page 18.

- Updated minimum Supply Input Voltage (V<sub>REGIN</sub>) for C8051F52x-C/F53x-C devices in Table 2.2 on page 26 and Table 2.6 on page 30.

- Updated digital supply current (I<sub>DD</sub> and Idle I<sub>DD</sub>) typical values for condition 'Clock = 25 MHz' in Table 2.2 on page 26.

- Updated I<sub>DD</sub> Frequency Sensitivity and Idle I<sub>DD</sub> Frequency Sensitivity values in Table 2.2 on page 26; removed Figure 2.1 and Figure 2.2 that used to provide the same frequency sensitivity slopes. Also removed IDD Supply Sensitivity and Idle IDD Supply Sensitivity typical values.

- Added Digital Supply Current (Stop or Suspend Mode) values at multiple temperatures Table 2.2 on page 26.

- Added a note in Table 2.3, "ADC0 Electrical Characteristics," on page 28 with reference to Section "4.4. Selectable Gain" on page 60; also added note to indicate that additional tracking time may be necessary if VDD is less than the minimum specified VDD.

- Split off temperature sensor specifications from Table 2.3 into a separate table Table 2.4; Updated temperature sensor gain and added supply current values.

- Added temperature condition for Bias Current specification in Table 2.6 on page 30.

- Updated Comparator Input Offset Voltage values in Table 2.7 on page 31.

- Updated VDD Monitor (VDDMON0) Low Threshold (V<sub>RST-LOW</sub>) minimum value for C8051F52xA/F52x-C/F53xA/F53x-C devices in Table 2.8 on page 32.

- Updated VDD Monitor (VDDMON0) supply current values in Table 2.8 on page 32.

- Added specifications for the new level-sensitive VDD monitor (VDDMON1) to Table 2.8, "Reset Electrical Characteristics," on page 32 and also added notes to clarify the applicable V<sub>RST</sub> theshold level.

- Added note in Table 2.9, "Flash Electrical Characteristics," on page 33 to describe the minimum flash programming temperature for –I (Industrial Grade) devices; Also added the same note and references to it in Section "12.1. Programming The Flash Memory" on page 113, Section "12.3. Non-volatile Data Storage" on page 117, and in SFR Definition 12.1 (PSCTL).

### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific to result in significant personal injury or death. Silicon Laboratories products are generally not intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

### **Trademark Information**

Silicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISOmodem ®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

# http://www.silabs.com