# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                           |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | SPI, UART/USART                                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT               |

| Number of I/O              | 16                                                               |

| Program Memory Size        | 8KB (8K x 8)                                                     |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 256 x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                     |

| Data Converters            | A/D 16x12b                                                       |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                               |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                  |

| Supplier Device Package    | 20-TSSOP                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f531a-itr |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

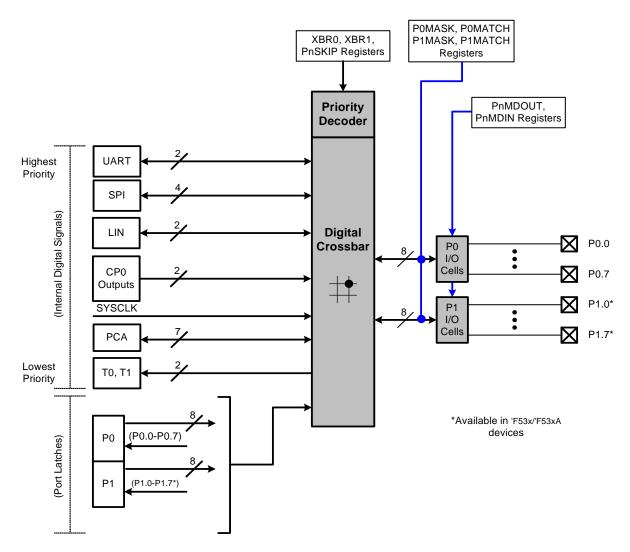

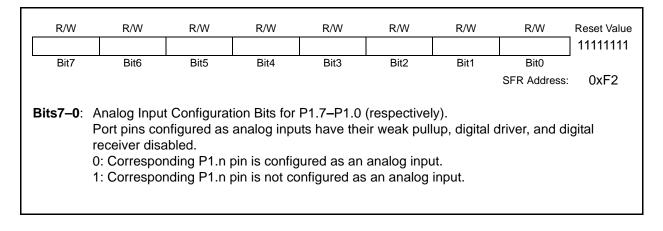

#### 1.9. Port Input/Output

C8051F52x/F52xA/F53x/F53xA devices include up to 16 I/O pins. Port pins are organized as two bytewide ports. The port pins behave like typical 8051 ports with a few enhancements. Each port pin can be configured as a digital or analog I/O pin. Pins selected as digital I/O can be configured for push-pull or open-drain operation. The "weak pullups" that are fixed on typical 8051 devices may be globally disabled to save power.

The Digital Crossbar allows mapping of internal digital system resources to port I/O pins. On-chip counter/timers, serial buses, hardware interrupts, and other digital signals can be configured to appear on the port pins using the Crossbar control registers. This allows the user to select the exact mix of general-purpose port I/O, digital, and analog resources needed for the application.

Figure 1.9. Port I/O Functional Block Diagram

#### Table 2.2. Global DC Electrical Characteristics

-40 to +125 °C, 25 MHz System Clock unless otherwise specified. Typical values are given at 25 °C

| Parameter                                                 | Conditions                                          | Min     | Тур    | Max | Units  |

|-----------------------------------------------------------|-----------------------------------------------------|---------|--------|-----|--------|

| Digital Supply Current—CPU Inactive (Id                   | le Mode, not fetching instructio                    | ns from | Flash) |     |        |

| Idle I <sub>DD</sub> <sup>3,4</sup>                       | V <sub>DD</sub> = 2.1 V:                            |         |        |     |        |

|                                                           | Clock = 32 kHz                                      | —       | 8      | —   | μA     |

|                                                           | Clock = 200 kHz                                     | —       | 22     | —   | μA     |

|                                                           | Clock = 1 MHz                                       | —       | 0.09   | —   | mA     |

|                                                           | Clock = 25 MHz                                      | —       | 2.2    | 5   | mA     |

|                                                           | V <sub>DD</sub> = 2.6 V:                            |         |        |     |        |

|                                                           | Clock = 32 kHz                                      | —       | 9      | —   | μA     |

|                                                           | Clock = 200 kHz                                     | _       | 30     | _   | μA     |

|                                                           | Clock = 1 MHz                                       | _       | 0.13   | _   | mA     |

|                                                           | Clock = 25 MHz                                      | —       | 3      | 6.5 | mA     |

| Idle I <sub>DD</sub> Frequency Sensitivity <sup>3,6</sup> | T = 25 °C:                                          |         |        |     |        |

|                                                           | V <sub>DD</sub> = 2.1 V, F <u>&lt;</u> 1 MHz        | —       | 90     | —   | µA/MHz |

|                                                           | $V_{DD} = 2.1 \text{ V}, \text{ F} > 1 \text{ MHz}$ | —       | 90     | —   | µA/MHz |

|                                                           | $V_{DD} = 2.6 V, F \le 1 MHz$                       | —       | 118    | —   | µA/MHz |

|                                                           | $V_{DD} = 2.6 \text{ V}, \text{ F} > 1 \text{ MHz}$ | —       | 118    | —   | µA/MHz |

| Disital Curshy Current <sup>3</sup>                       |                                                     |         |        |     |        |

| Digital Supply Current <sup>3</sup>                       | Oscillator not running,                             |         |        |     |        |

| (Stop or Suspend Mode)                                    | V <sub>DD</sub> Monitor Disabled.                   |         | _      |     |        |

|                                                           | T = 25 °C                                           | —       | 2      | —   | μA     |

|                                                           | T = 60 °C                                           | —       | 3      | —   | μA     |

|                                                           | T = 125 °C                                          | —       | 50     | _   | μA     |

#### Notes:

- 1. For more information on  $V_{\mbox{REGIN}}$  characteristics, see Table 2.6 on page 30.

- **2.** SYSCLK must be at least 32 kHz to enable debugging.

- **3.** Based on device characterization data; Not production tested.

- 4. Does not include internal oscillator or internal regulator supply current.

- 5. I<sub>DD</sub> can be estimated for frequencies <= 12 MHz by multiplying the frequency of interest by the frequency sensitivity number for that range. When using these numbers to estimate I<sub>DD</sub> > 12 MHz, the estimate should be the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number. For example: V<sub>DD</sub> = 2.6 V; F = 20 MHz, I<sub>DD</sub> = 7.3 mA (25 MHz 20 MHz) x 0.184 mA/MHz = 6.38 mA.

- 6. Idle  $I_{DD}$  can be estimated for frequencies <= 1 MHz by multiplying the frequency of interest by the frequency sensitivity number for that range. When using these numbers to estimate  $I_{DD}$  > 1 MHz, the estimate should be the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number. For example:  $V_{DD}$  = 2.6 V; F= 5 MHz, Idle  $I_{DD}$  = 3 mA (25 MHz– 5 MHz) x 118 µA/MHz = 0.64 mA.

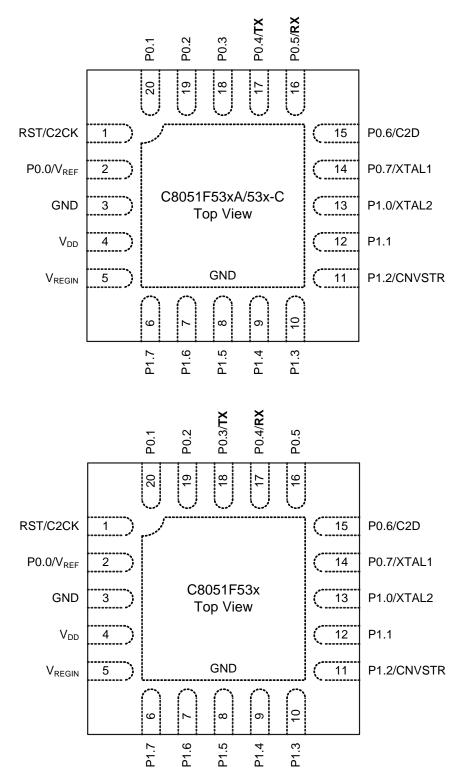

Figure 3.7. QFN-20 Pinout Diagram (Top View)

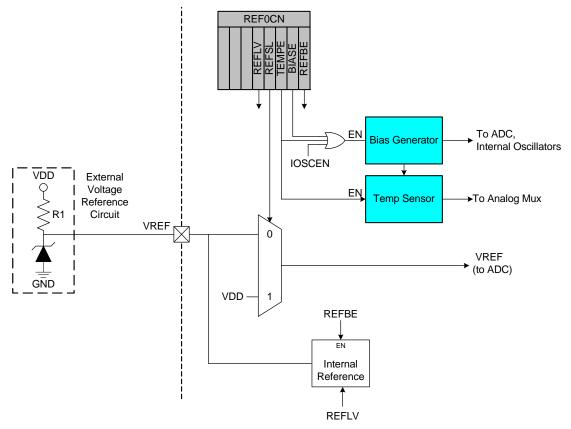

### 5. Voltage Reference

The Voltage reference MUX on C8051F52x/F52xA/F53x/F53xA devices is configurable to use an externally connected voltage reference, the internal reference voltage generator, or the  $V_{DD}$  power supply voltage (see Figure 5.1). The REFSL bit in the Reference Control register (REF0CN) selects the reference source. For an external source or the internal reference applied to the  $V_{REF}$  pin, REFSL should be set to 0. To use  $V_{DD}$  as the reference source, REFSL should be set to 1.

The BIASE bit enables the internal voltage bias generator, which is used by the ADC, Temperature Sensor, and internal oscillators. This bit is forced to logic 1 when any of the aforementioned peripherals are enabled. The bias generator may be enabled manually by writing a 1 to the BIASE bit in register REFOCN; see SFR Definition 5.1 for REFOCN register details. The electrical specifications for the voltage reference circuit are given in Table 2.5 on page 29.

The internal voltage reference circuit consists of a temperature stable bandgap voltage reference generator and a gain-of-two output buffer amplifier. The output voltage is selectable between 1.5 V and 2.2 V. The internal voltage reference can be driven out on the  $V_{REF}$  pin by setting the REFBE bit in register REF0CN to a 1 (see Figure 5.1). The load seen by the  $V_{REF}$  pin must draw less than 200 µA to GND. When using the internal voltage reference, bypass capacitors of 0.1 µF and 4.7 µF are recommended from the  $V_{REF}$  pin to GND. If the internal reference is not used, the REFBE bit should be cleared to 0. Electrical specifications for the internal voltage reference are given in Table 2.5 on page 29.

Figure 5.1. Voltage Reference Functional Block Diagram

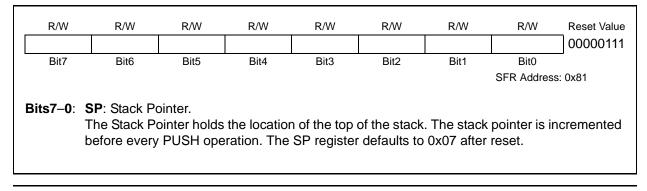

#### SFR Definition 8.1. SP: Stack Pointer

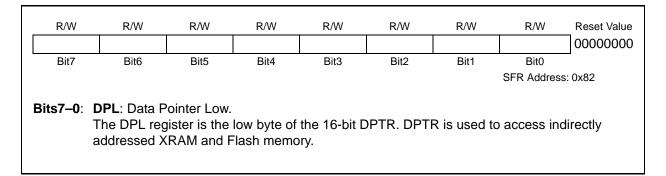

#### SFR Definition 8.2. DPL: Data Pointer Low Byte

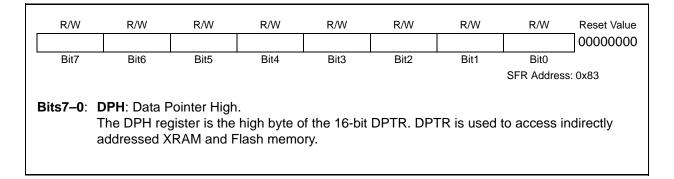

### SFR Definition 8.3. DPH: Data Pointer High Byte

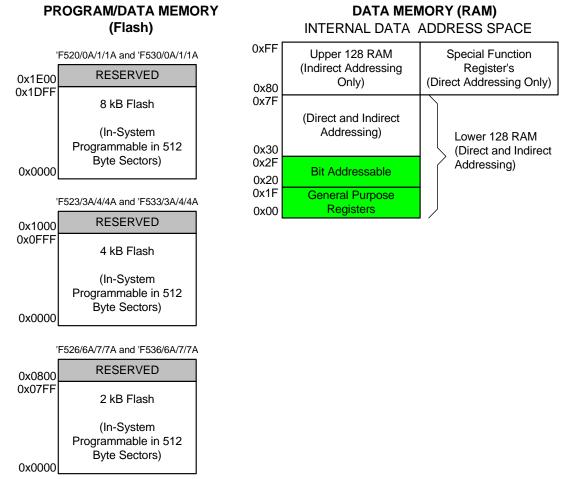

### 9. Memory Organization and SFRs

The memory organization of the C8051F52x/F52xA/F53x/F53x/F53xA is similar to that of a standard 8051. There are two separate memory spaces: program memory and data memory. Program and data memory share the same address space but are accessed via different instruction types. The memory map is shown in Figure 9.1.

Figure 9.1. Memory Map

#### 9.1. Program Memory

The CIP-51 core has a 64 kB program memory space. The C8051F520/0A/1/1A and C8051F530/0A/1/1A implement 8 kB of this program memory space as in-system, re-programmable Flash memory, organized in a contiguous block from addresses 0x0000 to 0x1FFF. Addresses above 0x1DFF are reserved on the 8 kB devices. The C8051F523/3A/4/4A and C8051F533/3A/4/4A implement 4 kB of Flash from addresses 0x0000 to 0x0FFF. The C8051F526/6A/7/7A and C8051F536/6A/7/7A implement 2 kB of Flash from addresses 0x0000 to 0x07FF.

Program memory is normally assumed to be read-only. However, the C8051F52x/F52xA/F53x/F53xA can write to program memory by setting the Program Store Write Enable bit (PSCTL.0) and using the MOVX write instruction. This feature provides a mechanism for updates to program code and use of the program memory space for non-volatile data storage. Refer to Section "12. Flash Memory" on page 113 for further details.

#### 11.2. Power-Fail Reset / V<sub>DD</sub> Monitors (VDDMON0 and VDDMON1)

C8051F52x-C/F53x-C devices include two V<sub>DD</sub> monitors: a standard V<sub>DD</sub> monitor (VDDMON0) and a level-sensitive V<sub>DD</sub> monitor (VDDMON1). VDDMON0 is primarily intended for setting a higher threshold to allow safe erase or write of Flash memory from firmware. VDDMON1 is used to hold the device in a reset state during power-up and brownout conditions.

**Note:** VDDMON1 is not present in older silicon revisions A and B. Please refer to Section "20.4. VDD Monitors and VDD Ramp Time" on page 211 for more details.

When a power-down transition or power irregularity causes  $V_{DD}$  to drop below  $V_{RST}$ , the power supply monitors (VDDMON0 and VDDMON1) will drive the RST pin low and hold the CIP-51 in a reset state (see Figure 11.2). When  $V_{DD}$  returns to a level above  $V_{RST}$ , the CIP-51 will be released from the reset state. Note that even though internal data memory contents are not altered by the power-fail reset, it is impossible to determine if  $V_{DD}$  dropped below the level required for data retention. If the PORSF flag reads 1, the data may no longer be valid.

VDDMON0 is enabled and is selected as a reset source after power-on resets; however its defined state (enabled/disabled) is not altered by any other reset source. For example, if VDDMON0 is disabled by software, and a software reset is performed, VDDMON0 will still be disabled after that reset.

VDDMON1 is enabled and is selected as a reset source after power-on reset and any other type of reset. There is no register setting that can disable this level-sensitive VDD monitor as a reset source.

To protect the integrity of Flash contents, the  $V_{DD}$  monitor (VDDMON0) must be enabled to the higher setting (VDMLVL = '1') and selected as a reset source if software contains routines which erase or write Flash memory. If the  $V_{DD}$  monitor is not enabled and set to the higher setting, any erase or write performed on Flash memory will cause a Flash Error device reset.

**Note:** Please refer to Section "20.5. VDD Monitor (VDDMON0) High Threshold Setting" on page 212 for important notes related to the VDD Monitor high threshold setting in older silicon revisions A and B.

The V<sub>DD</sub> monitor (VDDMON0) must be enabled before it is selected as a reset source. Selecting the VDDMON0 as a reset source before it is enabled and stabilized may cause a system reset. The procedure for re-enabling the  $V_{DD}$  monitor and configuring the  $V_{DD}$  monitor as a reset source is shown below:

- 1. Enable the  $V_{DD}$  monitor (VDMEN bit in VDDMON = 1).

- Wait for the V<sub>DD</sub> monitor to stabilize (see Table 2.8 on page 32 for the V<sub>DD</sub> Monitor turn-on time). Note: This delay should be omitted if software contains routines which write or erase Flash memory.

- 3. Select the  $V_{DD}$  monitor as a reset source (PORSF bit in RSTSRC = 1).

See Figure 11.2 for  $V_{DD}$  monitor timing; note that the reset delay is not incurred after a  $V_{DD}$  monitor reset. See Table 2.8 on page 32 for complete electrical characteristics of the  $V_{DD}$  monitor.

**Note:** Software should take care not to inadvertently disable the V<sub>DD</sub> Monitor (VDDMON0) as a reset source when writing to RSTSRC to enable other reset sources or to trigger a software reset. All writes to RSTSRC should explicitly set PORSF to '1' to keep the V<sub>DD</sub> Monitor enabled as a reset source.

#### 11.2.1. VDD Monitor Thresholds and Minimum VDD

The minimum operating digital supply voltage ( $V_{DD}$ ) is specified as 2.0 V in Table 2.2 on page 26. The voltage at which the MCU is released from reset ( $V_{RST}$ ) can be as low as 1.65 V based on the  $V_{DD}$  Monitor thresholds that are specified in Table 2.8 on page 32. This could allow code execution during the power-up

#### 11.3. External Reset

The external RST pin provides a means for external circuitry to force the device into a reset state. Asserting an active-low signal on the RST pin generates a reset; an external pullup and/or decoupling of the RST pin may be necessary to avoid erroneous noise-induced resets. See Table 2.8 on page 32 for complete RST pin specifications. The PINRSF flag (RSTSRC.0) is set on exit from an external reset.

#### **11.4. Missing Clock Detector Reset**

The Missing Clock Detector (MCD) is a one-shot circuit that is triggered by the system clock. If the system clock remains high or low for more than 100  $\mu$ s, the one-shot will time out and generate a reset. After a MCD reset, the MCDRSF flag (RSTSRC.2) will read 1, signifying the MCD as the reset source; otherwise, this bit reads 0. Writing a 1 to the MCDRSF bit enables the Missing Clock Detector; writing a 0 disables it. The state of the RST pin is unaffected by this reset.

#### 11.5. Comparator Reset

Comparator0 can be configured as a reset source by writing a 1 to the CORSEF flag (RSTSRC.5). Comparator0 should be enabled and allowed to settle prior to writing to CORSEF to prevent any turn-on chatter on the output from generating an unwanted reset. The Comparator0 reset is active-low: if the non-inverting input voltage (on CP0+) is less than the inverting input voltage (on CP0-), the device is put into the reset state. After a Comparator0 reset, the CORSEF flag (RSTSRC.5) will read 1 signifying Comparator0 as the reset source; otherwise, this bit reads 0. The state of the RST pin is unaffected by this reset.

#### 11.6. PCA Watchdog Timer Reset

The programmable Watchdog Timer (WDT) function of the Programmable Counter Array (PCA) can be used to prevent software from running out of control during a system malfunction. The PCA WDT function can be enabled or disabled by software as described in Section "19.3. Watchdog Timer Mode" on page 203; the WDT is enabled and clocked by SYSCLK / 12 following any reset. If a system malfunction prevents user software from updating the WDT, a reset is generated and the WDTRSF bit (RSTSRC.5) is set to 1. The state of the RST pin is unaffected by this reset.

#### 11.7. Flash Error Reset

If a Flash read/write/erase or program read targets an illegal address, a system reset is generated. This may occur due to any of the following:

- A Flash write or erase is attempted above user code space. This occurs when PSWE is set to 1 and a MOVX write operation targets an address above the Lock Byte address.

- A Flash read is attempted above user code space. This occurs when a MOVC operation targets an address above the Lock Byte address.

- A program read is attempted above user code space. This occurs when user code attempts to branch to an address above the Lock Byte address.

- A Flash read, write or erase attempt is restricted due to a Flash security setting (see Section "12.4. Security Options" on page 117).

- A Flash write or erase is attempted while the V<sub>DD</sub> Monitor (VDDMON0) is disabled or not set to its high threshold setting.

The FERROR bit (RSTSRC.6) is set following a Flash error reset. The state of the  $\overrightarrow{RST}$  pin is unaffected by this reset.

**Note:** Please refer to Section "20.6. Reset Low Time" on page 212 for restrictions on reset low time in older silicon revisions A and B.

| SF Signals DFN10 | ΈF       |   | XTAL1 | XTAL2 |   | CNVSTR             |

|------------------|----------|---|-------|-------|---|--------------------|

| PIN I/O          | <u>ч</u> | 1 | 2     | 3     | 4 | <del>້ວ</del><br>5 |

| TX0              |          |   | _     |       |   |                    |

| RX0              |          |   |       |       |   |                    |

| ТХО              | -        |   |       |       |   |                    |

| RX0              |          |   |       |       |   |                    |

| SCK              |          |   |       |       |   |                    |

| MISO             |          |   | l     |       |   |                    |

| MOSI             |          |   |       |       |   |                    |

| NSS*             |          |   |       |       |   |                    |

| LIN-TX           |          |   |       |       |   |                    |

| LIN_RX           |          |   | Ĩ     |       |   |                    |

| CP0              |          |   |       |       |   |                    |

| CP0A             |          |   |       |       |   |                    |

| /SYSCLK          |          |   |       |       |   |                    |

| CEX0             |          |   |       |       |   |                    |

| CEX1             |          |   |       |       |   |                    |

| CEX2             |          |   |       |       |   |                    |

| ECI              |          |   |       |       |   |                    |

| Т0               |          |   |       |       |   |                    |

| T1               |          |   |       |       |   |                    |

|                  | 0        | 0 | 0     | 0     | 0 | 0                  |

Note: 4-Wire SPI Only.

#### Figure 13.5. Crossbar Priority Decoder with No Pins Skipped (DFN 10)

#### SFR Definition 13.9. P1: Port1

| R/W      | R/W                                                                                                                | R/W                                                                       | R/W                                          | R/W                           | R/W         | R/W      | R/W          | Reset Value        |

|----------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------|-------------------------------|-------------|----------|--------------|--------------------|

| P1.7     | P1.6                                                                                                               | P1.5                                                                      | P1.4                                         | P1.3                          | P1.2        | P1.1     | P1.0         | 11111111           |

| Bit7     | Bit6 Bit5 Bit4 Bit3 Bit2 Bit1                                                                                      |                                                                           |                                              |                               |             |          | Bit0         | Bit<br>Addressable |

|          |                                                                                                                    |                                                                           |                                              |                               |             |          | SFR Address: | 0x90               |

| Bits7–0: | Write - Outpu<br>0: Logic Low<br>1: Logic High<br>Read - Alway<br>pin when con<br>0: P1.n pin is<br>1: P1.n pin is | o Output.<br>In Output (hi<br>ys reads 0<br>Infigured as<br>Is logic low. | igh impedar<br>if selected a<br>digital inpu | nce if corres<br>as analog in | sponding P1 | 1MDOUT.n | •            | eads Port          |

#### SFR Definition 13.10. P1MDIN: Port1 Input Mode

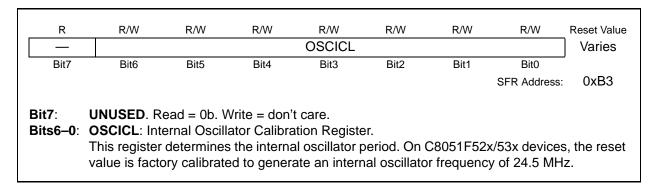

#### SFR Definition 14.2. OSCICL: Internal Oscillator Calibration

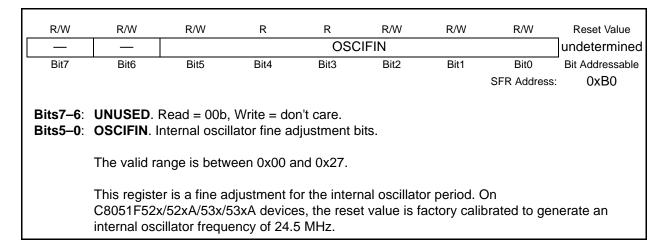

#### SFR Definition 14.3. OSCIFIN: Internal Fine Oscillator Calibration

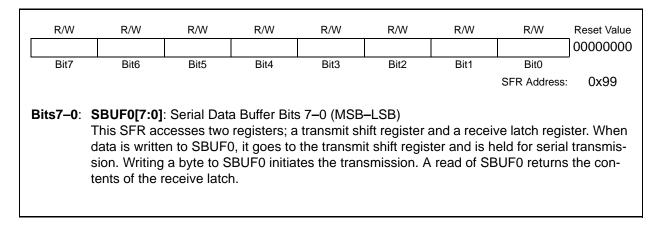

#### SFR Definition 15.2. SBUF0: Serial (UART0) Port Data Buffer

## Table 15.1. Timer Settings for Standard Baud RatesUsing the Internal Oscillator

|                   | Frequency: 24.5 MHz          |                      |                                |                       |                                     |      |                                  |  |  |  |  |  |

|-------------------|------------------------------|----------------------|--------------------------------|-----------------------|-------------------------------------|------|----------------------------------|--|--|--|--|--|

|                   | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscillator<br>Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select)* | T1M* | Timer 1<br>Reload<br>Value (hex) |  |  |  |  |  |

|                   | 230400                       | -0.32%               | 106                            | SYSCLK                | XX                                  | 1    | 0xCB                             |  |  |  |  |  |

|                   | 115200                       | -0.32%               | 212                            | SYSCLK                | XX                                  | 1    | 0x96                             |  |  |  |  |  |

|                   | 57600                        | 0.15%                | 426                            | SYSCLK                | XX                                  | 1    | 0x2B                             |  |  |  |  |  |

| from<br>Sc.       | 28800                        | -0.32%               | 848                            | SYSCLK/4              | 01                                  | 0    | 0x96                             |  |  |  |  |  |

| < fror<br>Osc.    | 14400                        | 0.15%                | 1704                           | SYSCLK / 12           | 00                                  | 0    | 0xB9                             |  |  |  |  |  |

| <u> </u>          | 9600                         | -0.32%               | 2544                           | SYSCLK / 12           | 00                                  | 0    | 0x96                             |  |  |  |  |  |

| SYSCL<br>Internal | 2400                         | -0.32%               | 10176                          | SYSCLK / 48           | 10                                  | 0    | 0x96                             |  |  |  |  |  |

| SY<br>Int         | 1200                         | 0.15%                | 20448                          | SYSCLK / 48           | 10                                  | 0    | 0x2B                             |  |  |  |  |  |

X = Don't care

**Note:** SCA1–SCA0 and T1M bit definitions can be found in Section 18.1.

### SFR Definition 16.1. SPI0CFG: SPI0 Configuration

| R         | R/W                                                                                                                            | R/W            | R/W         | R           | R            | R             | R              | Reset Value |  |  |  |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|-------------|--------------|---------------|----------------|-------------|--|--|--|--|

| SPIBSY    | MSTEN                                                                                                                          | CKPHA          | CKPOL       | SLVSEL      | NSSIN        | SRMT          | RXBMT          | 00000111    |  |  |  |  |

| Bit7      | Bit6                                                                                                                           | Bit5           | Bit4        | Bit3        | Bit2         | Bit1          | Bit0           | _1          |  |  |  |  |

|           |                                                                                                                                |                |             |             |              |               | SFR Address    | : 0xA1      |  |  |  |  |

|           | CDIDCV: SDI Duov (road only)                                                                                                   |                |             |             |              |               |                |             |  |  |  |  |

| Bit 7:    | <b>SPIBSY</b> : SPI Busy (read only).<br>This bit is set to logic 1 when a SPI transfer is in progress (Master or Slave Mode). |                |             |             |              |               |                |             |  |  |  |  |

| Bit 6:    | MSTEN: Master Mode Enable.                                                                                                     |                |             |             |              |               |                |             |  |  |  |  |

| DIL 0.    | 0: Disable master mode. Operate in slave mode.                                                                                 |                |             |             |              |               |                |             |  |  |  |  |

|           | 1: Enable ma                                                                                                                   |                |             |             | с.           |               |                |             |  |  |  |  |

| Bit 5:    | CKPHA: SP                                                                                                                      |                |             | s a master. |              |               |                |             |  |  |  |  |

| Dit J.    | This bit cont                                                                                                                  |                |             | ise         |              |               |                |             |  |  |  |  |

|           | 0: Data cent                                                                                                                   |                |             |             |              |               |                |             |  |  |  |  |

|           | 1: Data cent                                                                                                                   |                |             |             | d.*          |               |                |             |  |  |  |  |

| Bit 4:    | CKPOL: SP                                                                                                                      |                |             |             | -            |               |                |             |  |  |  |  |

|           | This bit cont                                                                                                                  |                |             | arity.      |              |               |                |             |  |  |  |  |

|           | 0: SCK line I                                                                                                                  | ow in idle s   | tate.       |             |              |               |                |             |  |  |  |  |

|           | 1: SCK line h                                                                                                                  | high in idle s | state.      |             |              |               |                |             |  |  |  |  |

| Bit 3:    | SLVSEL: Sla                                                                                                                    | ave Selecte    | d Flag (rea | d only).    |              |               |                |             |  |  |  |  |

|           | This bit is se                                                                                                                 | •              |             |             |              | •             |                |             |  |  |  |  |

|           | is cleared to                                                                                                                  |                |             |             |              |               |                |             |  |  |  |  |

|           | instantaneou                                                                                                                   |                |             |             |              | ed version of | of the pin in  | put.        |  |  |  |  |

| Bit 2:    | NSSIN: NSS                                                                                                                     |                |             | •           | • /          |               |                |             |  |  |  |  |

|           | This bit mim                                                                                                                   |                |             |             | •            | the NSS po    | ort pin at the | e time that |  |  |  |  |

|           | the register i                                                                                                                 |                | •           | •           |              |               |                |             |  |  |  |  |

| Bit 1:    | SRMT: Shift                                                                                                                    |                |             |             |              |               |                | .,          |  |  |  |  |

|           | This bit will b                                                                                                                |                |             |             |              |               |                | •           |  |  |  |  |

|           | and there is                                                                                                                   |                |             |             |              |               |                |             |  |  |  |  |

|           | receive buffe<br>the transmit                                                                                                  |                |             |             | byte is tran | isterred to t | ne sniit regi  | ster from   |  |  |  |  |

|           | NOTE: SRM                                                                                                                      |                |             |             |              |               |                |             |  |  |  |  |

| Bit 0:    | RXBMT: Red                                                                                                                     |                |             |             | Mode read    | l only)       |                |             |  |  |  |  |

| DIL U.    | This bit will b                                                                                                                |                |             |             |              |               | nd contains    | no new      |  |  |  |  |

|           | information.                                                                                                                   |                |             |             |              |               |                |             |  |  |  |  |

|           | this bit will re                                                                                                               |                |             |             |              |               | nat nas not    | beenread    |  |  |  |  |

|           | NOTE: RXB                                                                                                                      | 0              |             | r Mode.     |              |               |                |             |  |  |  |  |

|           |                                                                                                                                |                |             |             |              |               |                |             |  |  |  |  |

| te: See T | able 16.1 for ti                                                                                                               | ming parame    | eters.      |             |              |               |                |             |  |  |  |  |

|           |                                                                                                                                | 01             |             |             |              |               |                |             |  |  |  |  |

### 17.7. LIN Registers

The following Special Function Registers (SFRs) are available:

#### 17.7.1. LIN Direct Access SFR Registers Definition

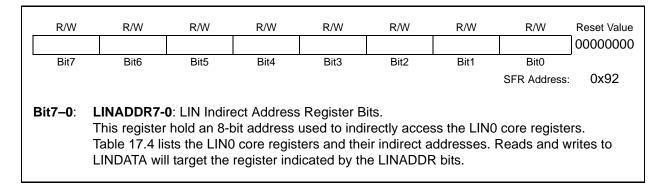

#### SFR Definition 17.1. LINADDR: Indirect Address Register

#### SFR Definition 17.2. LINDATA: LIN Data Register

| R/W                                                                                                                                                                                                                                                                                                   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|-------------|--|--|--|

| Bit7                                                                                                                                                                                                                                                                                                  | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | 00000000    |  |  |  |

| Diti                                                                                                                                                                                                                                                                                                  | Bito | Dito | DIG  | Dito | Ditz | Ditt |      | 0x93        |  |  |  |

| <ul> <li>Bit7-0: LINDATA7-0: LIN Indirect Data Register Bits.</li> <li>When this register is read, it will read the contents of the LIN0 core register pointed to by LINADDR.</li> <li>When this register is written, it will write the value to the LIN0 core register pointed to by LIN-</li> </ul> |      |      |      |      |      |      |      |             |  |  |  |

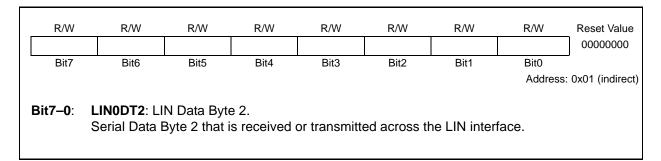

#### SFR Definition 17.5. LIN0DT2: LIN0 Data Byte 2

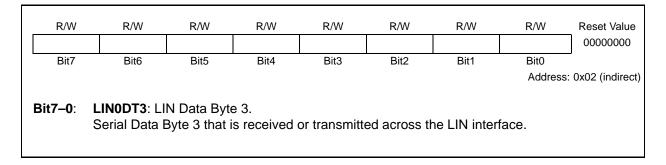

#### SFR Definition 17.6. LIN0DT3: LIN0 Data Byte 3

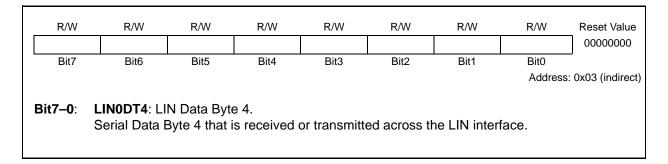

### SFR Definition 17.7. LIN0DT4: LIN0 Data Byte 4

### SFR Definition 18.1. TCON: Timer Control

| R/W   | R/W                             | R/W          | R/W         | R/W          | R/W          | R/W          | R/W           | Reset Value        |  |  |  |  |

|-------|---------------------------------|--------------|-------------|--------------|--------------|--------------|---------------|--------------------|--|--|--|--|

| TF1   | TR1                             | TF0          | TR0         | IE1          | IT1          | IE0          | IT0           | 00000000           |  |  |  |  |

| Bit7  | Bit6                            | Bit5         | Bit4        | Bit3         | Bit2         | Bit1         | Bit0          | Bit<br>Addressable |  |  |  |  |

|       |                                 |              |             |              |              |              | SFR Address   | s: 0x88            |  |  |  |  |

| Bit7: | TF1: Timer 1                    | Overflow I   | -lag.       |              |              |              |               |                    |  |  |  |  |

|       | Set by hardw                    |              |             | rflows. This | s flag can b | e cleared b  | y software b  | out is auto-       |  |  |  |  |

|       | matically clea                  |              |             | ctors to the | e Timer 1 in | terrupt serv | rice routine. |                    |  |  |  |  |

|       | 0: No Timer                     |              |             |              |              |              |               |                    |  |  |  |  |

|       | 1: Timer 1 has overflowed.      |              |             |              |              |              |               |                    |  |  |  |  |

| Bit6: | TR1: Timer 1 Run Control.       |              |             |              |              |              |               |                    |  |  |  |  |

|       | 0: Timer 1 dis<br>1: Timer 1 er |              |             |              |              |              |               |                    |  |  |  |  |

| Bit5: | <b>TF0</b> : Timer 0            |              | Flan        |              |              |              |               |                    |  |  |  |  |

| Sito. | Set by hardw                    |              | •           | rflows. This | s flag can b | e cleared h  | v software h  | out is auto-       |  |  |  |  |

|       | matically clea                  |              |             |              | -            |              | •             |                    |  |  |  |  |

|       | 0: No Timer (                   |              |             |              |              |              |               |                    |  |  |  |  |

|       | 1: Timer 0 ha                   | as overflow  | ed.         |              |              |              |               |                    |  |  |  |  |

| Bit4: | TRO: Timer C                    | Run Cont     | rol.        |              |              |              |               |                    |  |  |  |  |

|       | 0: Timer 0 di                   |              |             |              |              |              |               |                    |  |  |  |  |

| _     | 1: Timer 0 er                   |              |             |              |              |              |               |                    |  |  |  |  |

| Bit3: | IE1: External                   | •            |             |              |              | <i></i>      |               |                    |  |  |  |  |

|       | This flag is so                 |              |             |              |              |              |               |                    |  |  |  |  |

|       | cleared by so                   |              |             |              |              |              |               |                    |  |  |  |  |

|       | rupt 1 service<br>defined by bi |              |             |              |              |              |               |                    |  |  |  |  |

|       | figuration" or                  |              | -           |              |              | JI 10.5. II  |               |                    |  |  |  |  |

| Bit2: | IT1: Interrupt                  |              |             |              |              |              |               |                    |  |  |  |  |

|       | This bit selec                  |              |             | red INT0 ir  | terrupt will | be edge or   | level sensiti | ve. INT0 is        |  |  |  |  |

|       | configured a                    |              |             |              |              |              |               |                    |  |  |  |  |

|       | Definition 10                   | .5. "IT01C   | F: INT0/INT | 1 Configur   | ation" on pa | ige 105).    |               |                    |  |  |  |  |

|       | 0: <u>INT0</u> is lev           |              |             |              |              |              |               |                    |  |  |  |  |

|       | 1: INT0 is ed                   | 0 00         |             |              |              |              |               |                    |  |  |  |  |

| Bit1: | IE0: External                   | •            |             |              |              | <i></i>      | <u></u>       |                    |  |  |  |  |

|       | This flag is so                 |              |             |              |              |              |               |                    |  |  |  |  |

|       | cleared by so<br>rupt 0 service |              |             |              |              |              |               |                    |  |  |  |  |

|       | defined by bi                   |              |             |              |              |              |               |                    |  |  |  |  |

|       | figuration" or                  |              | •           | 101 (366 0   |              |              |               |                    |  |  |  |  |

| Bit0: | ITO: Interrupt                  |              |             |              |              |              |               |                    |  |  |  |  |

|       | This bit selec                  |              |             | red INT0 ir  | terrupt will | be edge or   | level sensiti | ve. INT0 is        |  |  |  |  |

|       | configured a                    |              |             |              |              |              |               |                    |  |  |  |  |

|       | "IT <u>01C</u> F: INT           |              |             | on page 1    | 05).         |              |               |                    |  |  |  |  |

|       | 0: INTO is lev                  |              |             |              |              |              |               |                    |  |  |  |  |

|       | 1: INT0 is ed                   | lae triaaere | d           |              |              |              |               |                    |  |  |  |  |

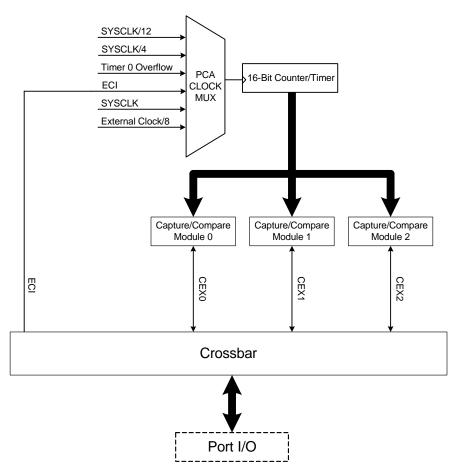

### **19. Programmable Counter Array (PCA0)**

The Programmable Counter Array (PCA0) provides enhanced timer functionality while requiring less CPU intervention than the standard 8051 counter/timers. The PCA consists of a dedicated 16-bit counter/timer and three 16-bit capture/compare modules. Each capture/compare module has its own associated I/O line (CEXn) which is routed through the Crossbar to Port I/O when enabled (See Section "13.1. Priority Cross-bar Decoder" on page 122 for details on configuring the Crossbar). The counter/timer is driven by a programmable timebase that can select between six sources: system clock, system clock divided by four, system clock divided by twelve, the external oscillator clock source divided by 8, Timer 0 overflow, or an external clock signal on the ECI input pin. Each capture/compare module may be configured to operate independently in one of three modes: Edge-Triggered Capture, Software Timer, High-Speed Output, Frequency Output, 8-Bit PWM, or 16-Bit PWM (each mode is described in Section "19.2. Capture/Compare Modules" on page 197). The PCA is configured and controlled through the system controller's Special Function Registers. The PCA block diagram is shown in Figure 19.1.

**Important Note:** The PCA Module 2 may be used as a watchdog timer (WDT), and is enabled in this mode following a system reset. Access to certain PCA registers is restricted while WDT mode is enabled. See Section "19.3. Watchdog Timer Mode" on page 203 for details.

Figure 19.1. PCA Block Diagram

#### **19.2. Capture/Compare Modules**

Each module can be configured to operate independently in one of six operation modes: Edge-triggered Capture, Software Timer, High Speed Output, Frequency Output, 8-Bit Pulse Width Modulator, or 16-Bit Pulse Width Modulator. Each module has Special Function Registers (SFRs) associated with it in the CIP-51 system controller. These registers are used to exchange data with a module and configure the module's mode of operation.

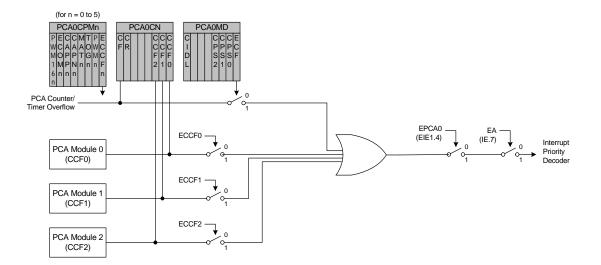

Table 19.2 summarizes the bit settings in the PCA0CPMn registers used to select the PCA capture/compare module's operating modes. Setting the ECCFn bit in a PCA0CPMn register enables the module's CCFn interrupt. Note that PCA0 interrupts must be globally enabled before individual CCFn interrupts are recognized. PCA0 interrupts are globally enabled by setting the EA bit and the EPCA0 bit to logic 1. See Figure 19.3 for details on the PCA interrupt configuration.

| PWM16    | ECOM   | CAPP | CAPN | MAT | TOG | PWM | ECCF | Operation Mode                             |

|----------|--------|------|------|-----|-----|-----|------|--------------------------------------------|

| Х        | Х      | 1    | 0    | 0   | 0   | 0   | Х    | Capture triggered by positive edge on CEXn |

| Х        | Х      | 0    | 1    | 0   | 0   | 0   | Х    | Capture triggered by negative edge on CEXn |

| Х        | Х      | 1    | 1    | 0   | 0   | 0   | Х    | Capture triggered by transition on<br>CEXn |

| Х        | 1      | 0    | 0    | 1   | 0   | 0   | Х    | Software Timer                             |

| Х        | 1      | 0    | 0    | 1   | 1   | 0   | Х    | High Speed Output                          |

| Х        | 1      | 0    | 0    | Х   | 1   | 1   | Х    | Frequency Output                           |

| 0        | 1      | 0    | 0    | Х   | 0   | 1   | Х    | 8-Bit Pulse Width Modulator                |

| 1        | 1      | 0    | 0    | Х   | 0   | 1   | Х    | 16-Bit Pulse Width Modulator               |

| X = Don' | t Care | •    |      |     |     | •   | •    |                                            |

Table 19.2. PCA0CPM Register Settings for PCA Capture/Compare Modules

Figure 19.3. PCA Interrupt Block Diagram

#### 19.2.3. High Speed Output Mode

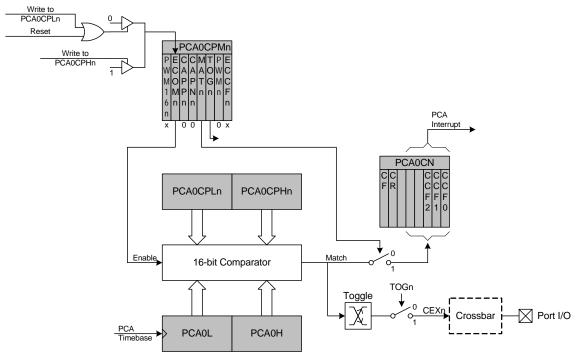

In High Speed Output mode, a module's associated CEXn pin is toggled each time a match occurs between the PCA Counter and the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn) Setting the TOGn, MATn, and ECOMn bits in the PCA0CPMn register enables the High-Speed Output mode.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Figure 19.6. PCA High-Speed Output Mode Diagram

**Note:** The initial state of the Toggle output is logic 1 and is initialized to this state when the module enters High Speed Output Mode.

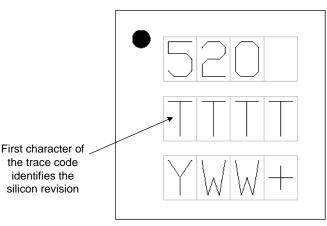

Figure 20.3. Device Package—DFN 10

#### 20.2. Reset Pin Behavior

The reset behavior differs between the silicon revisions of C8051F52x/52xA/F53x/F53xA devices. The differences affect the state of the RST pin during a VDD Monitor reset.

On Revision A devices, a  $V_{DD}$  Monitor reset does not affect the state of the  $\overline{RST}$  pin. On Revision B and Revision C devices, a  $V_{DD}$  Monitor reset will pull the  $\overline{RST}$  pin low for the duration of the brownout condition.

#### 20.3. Reset Time Delay

The reset time delay differs between the silicon revisions of C8051F52x/52xA/F53x/F53xA devices.

On Revision A devices, the reset time delay will be as long as 80 ms following a power-on reset, meaning it can take up to 80 ms to begin code execution. Subsequent resets will not cause the long delay. On Revision B and Revision C devices, the startup time is around 350  $\mu$ s, specified as T<sub>PORDELAY</sub> in Table 2.8, "Reset Electrical Characteristics," on page 32.

#### 20.4. $V_{DD}$ Monitors and $V_{DD}$ Ramp Time

The number of  $V_{DD}$  monitors and definition of " $V_{DD}$  ramp time" differs between the silicon revisions of C8051F52x/52xA/F53x/F53xA devices.

On Revision A and Revision B devices, the only  $V_{DD}$  monitor present is the standard  $V_{DD}$  monitor (VDD-MON0). On these devices, the  $V_{DD}$  ramp time is defined as how fast  $V_{DD}$  ramps from 0 V to  $V_{RST}$ . Here,  $V_{RST}$  is the  $V_{RST-LOW}$  threshold of VDDMON0 specified in Table 2.8, "Reset Electrical Characteristics," on page 32. The maximum  $V_{DD}$  ramp time for these devices is 1 ms; slower ramp times may cause the device to be released from reset before  $V_{DD}$  reaches the  $V_{RST-LOW}$  level.

Revision C devices include two  $V_{DD}$  monitors: a standard  $V_{DD}$  monitor (VDDMON0) and a level-sensitive  $V_{DD}$  monitor (VDDMON1). See Section 11.2 on page 108 for more details. On these devices, the  $V_{DD}$  ramp time is defined as how fast  $V_{DD}$  ramps from 0 V to  $V_{RST1}$ .  $V_{RST1}$  is specified in Table 2.8, "Reset Electrical Characteristics," on page 32 as the threshold of the new level-sensitive  $V_{DD}$  monitor (VDD-MON1). This new  $V_{DD}$  monitor will hold the device in reset until  $V_{DD}$  reaches the  $V_{RST1}$  level irrespective of the length of the  $V_{DD}$  ramp time.

**Note:** Please refer to Section "11.2.1. VDD Monitor Thresholds and Minimum VDD" on page 108 for recommendations related to minimum V<sub>DD</sub>.