# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                           |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | LINbus, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT               |

| Number of I/O              | 16                                                               |

| Program Memory Size        | 4KB (4K x 8)                                                     |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 256 x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.25V                                                       |

| Data Converters            | A/D 16x12b                                                       |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                               |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                  |

| Supplier Device Package    | 20-TSSOP                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f533-c-it |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 14.2.2. External Crystal Example                            | 139 |

|-------------------------------------------------------------|-----|

| 14.2.3. External RC Example                                 | 141 |

| 14.2.4. External Capacitor Example                          | 141 |

| 14.3. System Clock Selection                                | 143 |

| 15. UART0                                                   |     |

| 15.1. Enhanced Baud Rate Generation                         |     |

| 15.2. Operational Modes                                     |     |

| 15.2.1. 8-Bit UART                                          |     |

| 15.2.2. 9-Bit UART                                          |     |

| 15.3. Multiprocessor Communications                         |     |

| 16. Enhanced Serial Peripheral Interface (SPI0)             |     |

| 16.1. Signal Descriptions                                   | 152 |

| 16.1.1. Master Out, Slave In (MOSI)                         |     |

| 16.1.2. Master In, Slave Out (MISO)                         |     |

| 16.1.3. Serial Clock (SCK)                                  |     |

| 16.1.4. Slave Select (NSS)                                  |     |

| 16.2. SPI0 Master Mode Operation                            |     |

| 16.3. SPI0 Slave Mode Operation                             |     |

| 16.4. SPI0 Interrupt Sources                                |     |

| 16.5. Serial Clock Timing                                   |     |

| 16.6. SPI Special Function Registers                        |     |

| 17. LIN (C8051F520/0A/3/3A/6/6A and C8051F530/0A/3/3A/6/6A) |     |

| 17.1. Software Interface with the LIN Peripheral            |     |

| 17.2. LIN Interface Setup and Operation                     |     |

| 17.2.1. Mode Definition                                     |     |

| 17.2.2. Baud Rate Options: Manual or Autobaud               |     |

| 17.2.3. Baud Rate Calculations—Manual Mode                  |     |

| 17.2.4. Baud Rate Calculations—Automatic Mode               |     |

| 17.3. LIN Master Mode Operation                             |     |

| 17.4. LIN Slave Mode Operation                              |     |

| 17.5. Sleep Mode and Wake-Up                                |     |

| 17.6. Error Detection and Handling                          |     |

| 17.7. LIN Registers                                         |     |

| 17.7.1. LIN Direct Access SFR Registers Definition          |     |

| 17.7.2. LIN Indirect Access SFR Registers Definition        |     |

| 18. Timers                                                  |     |

| 18.1. Timer 0 and Timer 1                                   |     |

| 18.1.1. Mode 0: 13-bit Counter/Timer                        |     |

| 18.1.2. Mode 1: 16-bit Counter/Timer                        |     |

| 18.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload        |     |

| 18.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)     |     |

| 18.2. Timer 2                                               |     |

| 18.2.1. 16-bit Timer with Auto-Reload                       |     |

| 18.2.2. 8-bit Timers with Auto-Reload                       | 101 |

| 18.2.3. External Capture Mode                               |     |

| Figure 13.5. Crossbar Priority Decoder with No Pins Skipped (DFN 10) 124   |

|----------------------------------------------------------------------------|

| Figure 13.6. Crossbar Priority Decoder with Some Pins Skipped (DFN 10) 125 |

| Figure 14.1. Oscillator Diagram 135                                        |

| Figure 14.2. 32 kHz External Crystal Example 140                           |

| Figure 15.1. UART0 Block Diagram 144                                       |

| Figure 15.2. UART0 Baud Rate Logic 145                                     |

| Figure 15.3. UART Interconnect Diagram 146                                 |

| Figure 15.4. 8-Bit UART Timing Diagram 146                                 |

| Figure 15.5. 9-Bit UART Timing Diagram 147                                 |

| Figure 15.6. UART Multi-Processor Mode Interconnect Diagram                |

| Figure 16.1. SPI Block Diagram 151                                         |

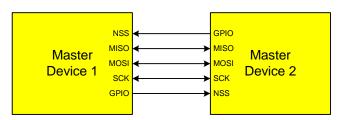

| Figure 16.2. Multiple-Master Mode Connection Diagram 154                   |

| Figure 16.3. 3-Wire Single Master and Slave Mode Connection Diagram        |

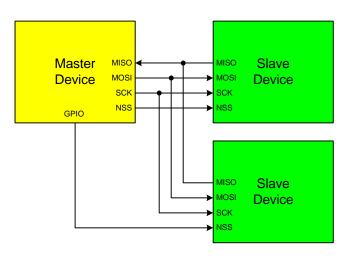

| Figure 16.4. 4-Wire Single Master and Slave Mode Connection Diagram        |

| Figure 16.5. Data/Clock Timing Relationship                                |

| Figure 16.6. SPI Master Timing (CKPHA = 0)                                 |

| Figure 16.7. SPI Master Timing (CKPHA = 1)                                 |

| Figure 16.8. SPI Slave Timing (CKPHA = 0)                                  |

| Figure 16.9. SPI Slave Timing (CKPHA = 1)                                  |

| Figure 17.1. LIN Block Diagram                                             |

| Figure 18.1. T0 Mode 0 Block Diagram                                       |

| Figure 18.2. T0 Mode 2 Block Diagram                                       |

| Figure 18.3. T0 Mode 3 Block Diagram                                       |

| Figure 18.4. Timer 2 16-Bit Mode Block Diagram                             |

| Figure 18.5. Timer 2 8-Bit Mode Block Diagram                              |

| Figure 18.6. Timer 2 Capture Mode Block Diagram                            |

| Figure 19.1. PCA Block Diagram                                             |

| Figure 19.2. PCA Counter/Timer Block Diagram                               |

| Figure 19.3. PCA Interrupt Block Diagram                                   |

| Figure 19.4. PCA Capture Mode Diagram                                      |

| Figure 19.5. PCA Software Timer Mode Diagram                               |

| Figure 19.6. PCA High-Speed Output Mode Diagram                            |

| Figure 19.7. PCA Frequency Output Mode                                     |

| Figure 19.8. PCA 8-Bit PWM Mode Diagram                                    |

| Figure 19.9. PCA 16-Bit PWM Mode                                           |

| Figure 19.10. PCA Module 2 with Watchdog Timer Enabled                     |

| Figure 20.1. Device Package—TSSOP 20                                       |

| Figure 20.2. Device Package—QFN 20                                         |

| Figure 20.3. Device Package—DFN 10                                         |

| Figure 21.1. Typical C2 Pin Sharing 216                                    |

|                                                                            |

## List of Tables

| Table 1.1. Product Selection Guide (Recommended for New Designs)        | 14  |

|-------------------------------------------------------------------------|-----|

| Table 1.2. Product Selection Guide (Not Recommended for New Designs)    |     |

| Table 1.3. Operating Modes Summary                                      |     |

| Table 2.1. Absolute Maximum Ratings                                     |     |

| Table 2.2. Global DC Electrical Characteristics                         |     |

| Table 2.3. ADC0 Electrical Characteristics                              |     |

| Table 2.4. Temperature Sensor Electrical Characteristics                |     |

| Table 2.5. Voltage Reference Electrical Characteristics                 |     |

| Table 2.6. Voltage Regulator Electrical Specifications                  |     |

| Table 2.7. Comparator Electrical Characteristics                        |     |

| Table 2.8. Reset Electrical Characteristics                             |     |

| Table 2.9. Flash Electrical Characteristics                             |     |

| Table 2.10. Port I/O DC Electrical Characteristics                      |     |

| Table 2.11. Internal Oscillator Electrical Characteristics              |     |

| Table 3.1. Pin Definitions for the C8051F52x and C8051F52xA (DFN 10)    |     |

| Table 3.2. DFN-10 Package Diagram Dimensions                            |     |

| Table 3.3. DFN-10 Landing Diagram Dimensions                            |     |

| Table 3.4. Pin Definitions for the C8051F53x and C805153xA (TSSOP 20)   |     |

| Table 3.5. TSSOP-20 Package Diagram Dimensions                          |     |

| Table 3.6. TSSOP-20 Landing Diagram Dimensions                          |     |

| Table 3.7. Pin Definitions for the C8051F53x and C805153xA (QFN 20)     |     |

| Table 3.8. QFN-20 Package Diagram Dimensions                            | 49  |

| Table 3.9. QFN-20 Landing Diagram Dimensions                            | 51  |

| Table 8.1. CIP-51 Instruction Set Summary                               | 83  |

| Table 9.1. Special Function Register (SFR) Memory Map                   | 94  |

| Table 9.2. Special Function Registers                                   |     |

| Table 10.1. Interrupt Summary                                           | 99  |

| Table 12.1. Flash Security Summary 1                                    |     |

| Table 15.1. Timer Settings for Standard Baud Rates                      |     |

| Using the Internal Oscillator 1                                         | 50  |

| Table 16.1. SPI Slave Timing Parameters 1                               | 63  |

| Table 17.1. Baud-Rate Calculation Variable Ranges 1                     | 66  |

| Table 17.2. Manual Baud Rate Parameters Examples 1                      | 67  |

| Table 17.3. Autobaud Parameters Examples 1                              | 68  |

| Table 17.4. LIN Registers* (Indirectly Addressable) 1                   | 74  |

| Table 19.1. PCA Timebase Input Options 1                                | 196 |

| Table 19.2. PCA0CPM Register Settings for PCA Capture/Compare Modules 1 | 97  |

| Table 19.3. Watchdog Timer Timeout Intervals1 2                         | 205 |

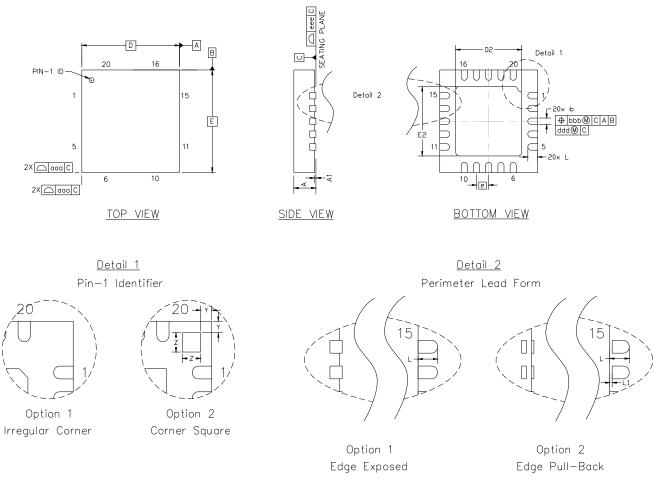

Figure 3.8. QFN-20 Package Diagram\*

\*Note: The Package Dimensions are given in Table 3.8, "QFN-20 Package Diagram Dimensions," on page 49.

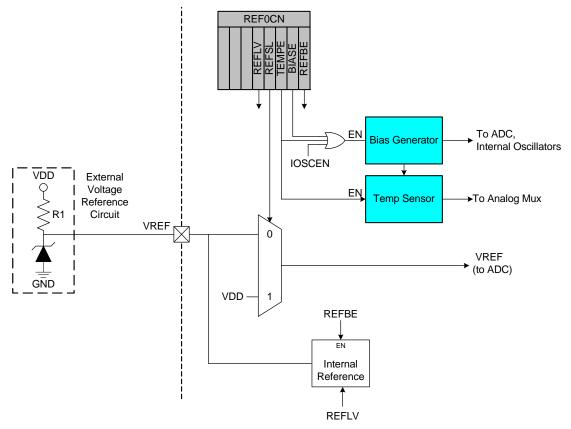

## 5. Voltage Reference

The Voltage reference MUX on C8051F52x/F52xA/F53x/F53xA devices is configurable to use an externally connected voltage reference, the internal reference voltage generator, or the  $V_{DD}$  power supply voltage (see Figure 5.1). The REFSL bit in the Reference Control register (REF0CN) selects the reference source. For an external source or the internal reference applied to the  $V_{REF}$  pin, REFSL should be set to 0. To use  $V_{DD}$  as the reference source, REFSL should be set to 1.

The BIASE bit enables the internal voltage bias generator, which is used by the ADC, Temperature Sensor, and internal oscillators. This bit is forced to logic 1 when any of the aforementioned peripherals are enabled. The bias generator may be enabled manually by writing a 1 to the BIASE bit in register REFOCN; see SFR Definition 5.1 for REFOCN register details. The electrical specifications for the voltage reference circuit are given in Table 2.5 on page 29.

The internal voltage reference circuit consists of a temperature stable bandgap voltage reference generator and a gain-of-two output buffer amplifier. The output voltage is selectable between 1.5 V and 2.2 V. The internal voltage reference can be driven out on the  $V_{REF}$  pin by setting the REFBE bit in register REF0CN to a 1 (see Figure 5.1). The load seen by the  $V_{REF}$  pin must draw less than 200 µA to GND. When using the internal voltage reference, bypass capacitors of 0.1 µF and 4.7 µF are recommended from the  $V_{REF}$  pin to GND. If the internal reference is not used, the REFBE bit should be cleared to 0. Electrical specifications for the internal voltage reference are given in Table 2.5 on page 29.

Figure 5.1. Voltage Reference Functional Block Diagram

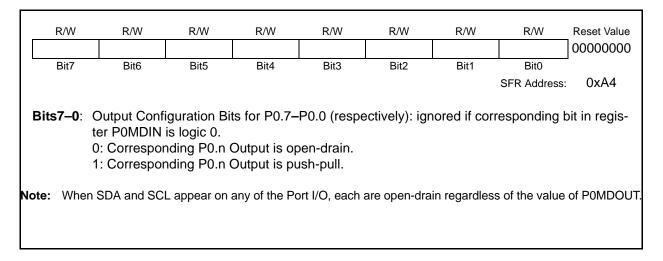

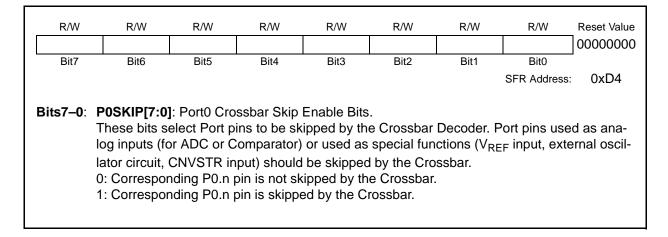

**Important Note About the V<sub>REF</sub> Pin:** Port pin P0.0 is used as the external V<sub>REF</sub> input and as an output for the internal V<sub>REF</sub>. When using either an external voltage reference or the internal reference circuitry, P0.0 should be configured as an analog pin, and skipped by the Digital Crossbar. To configure P0.0 as an analog pin, clear Bit 0 in register P0MDIN to 0. To configure the Crossbar to skip P0.0, set Bit 0 in register P0SKIP to 1. Refer to Section "13. Port Input/Output" on page 120 for complete Port I/O configuration details.

The TEMPE bit in register REF0CN enables/disables the temperature sensor. While disabled, the temperature sensor defaults to a high impedance state and any ADC0 measurements performed on the sensor result in meaningless data.

| R/W          | R/W                                          | R/W         | R/W           | R/W         | R/W          | R/W           | R/W           | Reset Value |  |

|--------------|----------------------------------------------|-------------|---------------|-------------|--------------|---------------|---------------|-------------|--|

| Reserve      |                                              | ZTCEN       | REFLV         | REFSL       | TEMPE        | BIASE         | REFBE         | 1 00000000  |  |

| Bit7         | Bit6                                         | Bit5        | Bit4          | Bit3        | Bit2         | Bit1          | Bit0          | SFR Address |  |

|              |                                              |             |               |             |              |               |               | 0xD1        |  |

|              |                                              |             |               |             |              |               |               |             |  |

| Bits7-6:     | RESERVED                                     | . Read = 00 | )b. Must wr   | ite 00b.    |              |               |               |             |  |

| Bit5:        | <b>ZTCEN</b> : Zero-TempCo Bias Enable Bit*. |             |               |             |              |               |               |             |  |

|              | 0: ZeroTC Bi                                 |             |               |             | ed when ne   | eded.         |               |             |  |

|              | 1: ZeroTC Bi                                 |             |               |             |              |               |               |             |  |

| Bit4:        | REFLV: Volta                                 | •           |               |             |              |               |               |             |  |

|              | This bit selec                               |             | •             |             | internal vol | tage referei  | nce.          |             |  |

|              | 0: Internal vo                               | •           |               |             |              |               |               |             |  |

| <b>D</b> '/0 | 1: Internal vo                               | -           |               |             |              |               |               |             |  |

| Bit3:        | REFSL: Volt                                  | •           |               |             |              |               |               |             |  |

|              | This bit selec                               |             |               |             | ige referenc | ce.           |               |             |  |

|              | 0: V <sub>REF</sub> pin ι                    |             | -             | nce.        |              |               |               |             |  |

|              | 1: V <sub>DD</sub> used                      |             |               |             |              |               |               |             |  |

| Bit2:        | TEMPE: Ten                                   |             |               |             |              |               |               |             |  |

|              | 0: Internal Te                               | •           |               |             |              |               |               |             |  |

| D'44         | 1: Internal Te                               | •           |               |             | D'1          |               |               |             |  |

| Bit1:        | BIASE: Inter                                 | •           |               |             |              | uhan naalo    | ام            |             |  |

|              | 0: Internal A                                |             |               |             | y enabled v  | vnen neede    | ea.           |             |  |

| Bit0:        | 1: Internal A<br>REFBE: Inte                 | •           |               |             |              |               |               |             |  |

| DILU.        | 0: Internal R                                |             |               |             |              |               |               |             |  |

|              | 1: Internal R                                |             |               |             | voltage refe | ronco drivo   | n on the V.   | nin         |  |

|              | r. memariki                                  |             |               | a. memai    | ionaye iele  |               |               |             |  |

| *Note: Se    | e Section "20.7                              | Internal O  | cillator Susr | end Mode" o | n nage 212 f | or a note rel | ated to the 7 | TCEN hit in |  |

| 1010.00      | older silicon re                             |             | onator ousp   |             | 11 page 2121 |               |               |             |  |

|              |                                              |             |               |             |              |               |               |             |  |

|              |                                              |             |               |             |              |               |               |             |  |

### SFR Definition 5.1. REF0CN: Reference Control

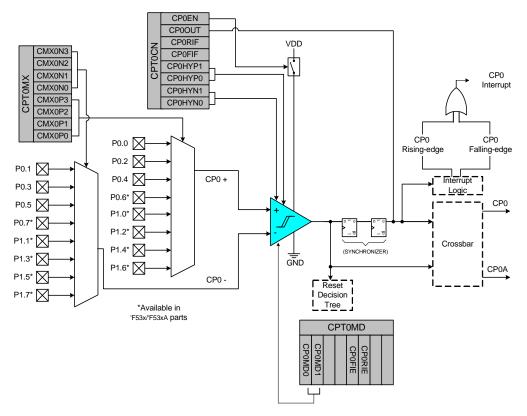

## 7. Comparator

C8051F52x/F52xA/F53x/F53xA devices include one on-chip programmable voltage comparator. The Comparator is shown in Figure 7.1.

The Comparator offers programmable response time and hysteresis, an analog input multiplexer, and two outputs that are optionally available at the Port pins: a synchronous "latched" output (CP0), or an asynchronous "raw" output (CP0A). The asynchronous CP0A signal is available even when the system clock is not active. This allows the Comparator to operate and generate an output with the device in STOP or SUS-PEND mode. When assigned to a Port pin, the Comparator output may be configured as open drain or push-pull (see Section "13.2. Port I/O Initialization" on page 126). The Comparator may also be used as a reset source (see Section "11.5. Comparator Reset" on page 110).

The Comparator inputs are selected in the CPT0MX register (SFR Definition 7.2). The CMX0P3–CMX0P0 bits select the Comparator0 positive input; the CMX0N3–CMX0N0 bits select the Comparator0 negative input.

**Important Note About Comparator Inputs:** The Port pins selected as Comparator inputs should be configured as analog inputs in their associated Port configuration register and configured to be skipped by the Crossbar (for details on Port configuration, see Section "13.3. General Purpose Port I/O" on page 128).

Figure 7.1. Comparator Functional Block Diagram

The Comparator output can be polled in software, used as an interrupt source, internal oscillator suspend awakening source and/or routed to a Port pin. When routed to a Port pin, the Comparator output is available asynchronous or synchronous to the system clock; the asynchronous output is available even in STOP or SUSPEND mode (with no system clock active). When disabled, the Comparator output (if assigned to a Port I/O pin via the Crossbar) defaults to the logic low state, and its supply current falls to

Note that false rising edges and falling edges can be detected when the comparator is first powered-on or if changes are made to the hysteresis or response time control bits. Therefore, it is recommended that the rising-edge and falling-edge flags be explicitly cleared to logic 0 a short time after the comparator is enabled or its mode bits have been changed. This Power Up Time is specified in Table 2.7 on page 31.

### SFR Definition 7.1. CPT0CN: Comparator0 Control

| R/W      | R                              | R/W                      | R/W      | R/W       | R/W            | R/W          | R/W      | Reset Value  |  |

|----------|--------------------------------|--------------------------|----------|-----------|----------------|--------------|----------|--------------|--|

| CP0EN    | CP0OUT                         | <b>CP0RIF</b>            | CP0FIF   | CP0HYP1   | CP0HYP0        | CP0HYN1      | CP0HYN0  | 00000000     |  |

| Bit7     | Bit6                           | Bit5                     | Bit4     | Bit3      | Bit2           | Bit1         | Bit0     | SFR Address: |  |

|          |                                |                          |          |           |                |              |          | 0x9B         |  |

|          |                                |                          |          |           |                |              |          |              |  |

| Bit7:    | CP0EN: Comparator0 Enable Bit. |                          |          |           |                |              |          |              |  |

|          |                                | 0: Comparator0 Disabled. |          |           |                |              |          |              |  |

|          | 1: Comparat                    |                          |          |           |                |              |          |              |  |

| Bit6:    | CPOOUT: Co                     | •                        | •        | ate Flag. |                |              |          |              |  |

|          | 0: Voltage or                  |                          |          |           |                |              |          |              |  |

| D.16     | 1: Voltage or                  |                          |          |           |                |              |          |              |  |

| Bit5:    | CPORIF: Col                    | •                        |          | •         | ainaa thia fl  | og woo loot  | alaarad  |              |  |

|          | 0: No Comparat                 |                          |          |           | since this h   | ag was last  | cleared. |              |  |

| Bit4:    | CP0FIF: Cor                    | -                        | -        |           |                |              |          |              |  |

| Bit4.    | 0: No Compa                    |                          |          |           | d since this f | lad was last | cleared  |              |  |

|          | 1: Comparat                    |                          |          |           |                | lag had lad  | cicalcal |              |  |

| Bits3-2: | CP0HYP1-0                      |                          |          |           | is Control Bi  | ts.          |          |              |  |

|          | 00: Positive                   |                          |          |           |                |              |          |              |  |

|          | 01: Positive                   | Hysteresis               | = 5 mV.  |           |                |              |          |              |  |

|          | 10: Positive                   | Hysteresis               | = 10 mV. |           |                |              |          |              |  |

|          | 11: Positive                   |                          |          |           |                |              |          |              |  |

| Bits1–0: | CP0HYN1-0                      | •                        | •        |           | sis Control E  | Bits.        |          |              |  |

|          | 00: Negative                   | •                        |          |           |                |              |          |              |  |

|          | 01: Negative                   |                          |          |           |                |              |          |              |  |

|          | 10: Negative                   |                          |          |           |                |              |          |              |  |

|          | 11: Negative                   | Hysteresis               | = 20 mV. |           |                |              |          |              |  |

|          |                                |                          |          |           |                |              |          |              |  |

### 11.8. Software Reset

Software may force a reset by writing a 1 to the SWRSF bit (RSTSRC.4). The SWRSF bit will read 1 following a software forced reset. The state of the RST pin is unaffected by this reset.

## 12. Flash Memory

On-chip, re-programmable Flash memory is included for program code and non-volatile data storage. The Flash memory can be programmed in-system through the C2 interface or by software using the MOVX write instruction. Once cleared to logic 0, a Flash bit must be erased to set it back to logic 1. Flash bytes would typically be erased (set to 0xFF) before being reprogrammed. The write and erase operations are automatically timed by hardware for proper execution; data polling to determine the end of the write/erase operations is not required. Code execution is stalled during Flash write/erase operations. Refer to Table 2.9 on page 33 for complete Flash memory electrical characteristics.

### 12.1. Programming The Flash Memory

The simplest means of programming the Flash memory is through the C2 interface using programming tools provided by Silicon Laboratories or a third party vendor. This is the only means for programming a non-initialized device. For details on the C2 commands to program Flash memory, see Section "21. C2 Interface" on page 214.

To protect the integrity of Flash contents, the  $V_{DD}$  monitor must be enabled to the higher setting (VDMLVL = '1') and selected as a reset source if software contains routines which erase or write Flash memory. If the  $V_{DD}$  monitor is not enabled, any erase or write performed on Flash memory will cause a Flash Error device reset. See Section "11.2. Power-Fail Reset / VDD Monitors (VDDMON0 and VDD-MON1)" on page 108 for more information regarding the VDD monitor and the high threshold setting.

The V<sub>DD</sub> monitor must be enabled before it is selected as a reset source. Selecting the V<sub>DD</sub> monitor as a reset source before it is enabled and stabilized may cause a system reset. The procedure for reenabling the V<sub>DD</sub> monitor and configuring the V<sub>DD</sub> monitor as a reset source is shown below:

- 1. Enable the  $V_{DD}$  monitor (VDMEN bit in VDDMON = 1).

- Wait for the V<sub>DD</sub> monitor to stabilize (see Table 2.8 on page 32 for the V<sub>DD</sub> Monitor turn-on time). Note: This delay should be omitted if software contains routines which write or erase Flash memory.

- 3. Select the  $V_{DD}$  monitor as a reset source (PORSF bit in RSTSRC = 1).

**Note:** 8-bit MOVX instructions cannot be used to erase or write to Flash memory at addresses higher than 0x00FF.

Important Note: For -I (industrial Grade) parts, flash should be programmed (erase/write) at a minimum temperature of 0 °C for reliable flash operation across the entire temperature range of -40 to +125 °C. This minimum programming temperature does not apply to -A (Automotive Grade) parts.

### 12.1.1. Flash Lock and Key Functions

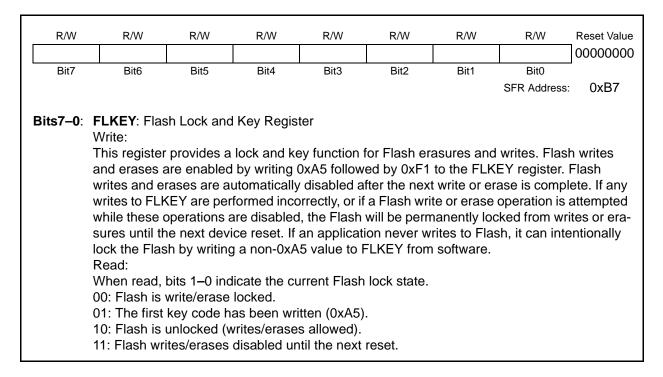

Flash writes and erases by user software are protected with a lock and key function. The Flash Lock and Key Register (FLKEY) must be written with the correct key codes, in sequence, before Flash operations may be performed. The key codes are: 0xA5, 0xF1. The timing does not matter, but the codes must be written in order. If the key codes are written out of order, or the wrong codes are written, Flash writes and erases will be disabled until the next system reset. Flash writes and erases will also be disabled if a Flash write or erase is attempted before the key codes have been written properly. The Flash lock resets after each write or erase; the key codes must be written again before a following Flash operation can be performed. The FLKEY register is detailed in SFR Definition 12.2.

### SFR Definition 12.1. PSCTL: Program Store R/W Control

| R                 | R                                                                                                                                                                                                                                                                                                                                                                                             | R    | R    | R    | R            | R/W                                 | R/W                    | Reset Value |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--------------|-------------------------------------|------------------------|-------------|--|

| —                 | —                                                                                                                                                                                                                                                                                                                                                                                             | —    | —    | —    | _            | PSEE                                | PSWE                   | 00000000    |  |

| Bit7              | Bit6                                                                                                                                                                                                                                                                                                                                                                                          | Bit5 | Bit4 | Bit3 | Bit2         | Bit1                                | Bit0                   |             |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                               |      |      |      |              |                                     | SFR Address            | s: 0x8F     |  |

| Bits7–2:<br>Bit1: | Setting this bit (in combination with PSWE) allows an entire page of Flash program memory                                                                                                                                                                                                                                                                                                     |      |      |      |              |                                     |                        |             |  |

|                   | to be erased. If this bit is logic 1 and Flash writes are enabled (PSWE is logic 1), a write to<br>Flash memory using the MOVX instruction will erase the entire page that contains the loca-<br>tion addressed by the MOVX instruction. The value of the data byte written does not matter.<br>0: Flash program memory erasure disabled.<br>1: Flash program memory erasure enabled.         |      |      |      |              |                                     |                        |             |  |

| Bit0:             | <ul> <li>PSWE: Program Store Write Enable</li> <li>Setting this bit allows writing a byte of data to the Flash program memory using the MOVX write instruction. The Flash location should be erased before writing data.</li> <li>0: Writes to Flash program memory disabled.</li> <li>1: Writes to Flash program memory enabled; the MOVX write instruction targets Flash memory.</li> </ul> |      |      |      |              |                                     |                        |             |  |

| Note: See         | Section "12.1.<br>requirements                                                                                                                                                                                                                                                                                                                                                                |      | -    | -    | page 113 for | <sup>-</sup> minimum V <sub>I</sub> | <sub>DD</sub> and temp | erature     |  |

### SFR Definition 12.2. FLKEY: Flash Lock and Key

### SFR Definition 13.5. P0MDOUT: Port0 Output Mode

### SFR Definition 13.6. P0SKIP: Port0 Skip

#### SFR Definition 15.1. SCON0: Serial Port 0 Control R/W R/W R/W Reset Value R R/W R/W R/W R/W SOMODE RI0 01000000 -MCE0 REN0 TB80 **RB80** TI0 Bit Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Addressable SFR Address: 0x98 Bit7: SOMODE: Serial Port 0 Operation Mode. This bit selects the UART0 Operation Mode. 0: 8-bit UART with Variable Baud Rate. 1: 9-bit UART with Variable Baud Rate. Bit6: **UNUSED**. Read = 1b. Write = don't care. Bit5: MCE0: Multiprocessor Communication Enable. The function of this bit is dependent on the Serial Port 0 Operation Mode. SOMODE = 0: Checks for valid stop bit. 0: Logic level of stop bit is ignored. 1: RIO will only be activated if stop bit is logic level 1. S0MODE = 1: Multiprocessor Communications Enable. 0: Logic level of ninth bit is ignored. 1: RI0 is set and an interrupt is generated only when the ninth bit is logic 1. Bit4: **REN0:** Receive Enable. This bit enables/disables the UART receiver. 0: UART0 reception disabled. 1: UART0 reception enabled. Bit3: TB80: Ninth Transmission Bit. The logic level of this bit will be assigned to the ninth transmission bit in 9-bit UART Mode. It is not used in 8-bit UART Mode. Set or cleared by software as required. Bit2: RB80: Ninth Receive Bit. RB80 is assigned the value of the STOP bit in Mode 0; it is assigned the value of the 9th data bit in Mode 1. Bit1: TIO: Transmit Interrupt Flag. Set by hardware when a byte of data has been transmitted by UART0 (after the 8th bit in 8bit UART Mode, or at the beginning of the STOP bit in 9-bit UART Mode). When the UART0 interrupt is enabled, setting this bit causes the CPU to vector to the UART0 interrupt service routine. This bit must be cleared manually by software. Bit0: RIO: Receive Interrupt Flag. Set to 1 by hardware when a byte of data has been received by UART0 (set at the STOP bit sampling time). When the UART0 interrupt is enabled, setting this bit to 1 causes the CPU to vector to the UART0 interrupt service routine. This bit must be cleared manually by software.

Figure 16.2. Multiple-Master Mode Connection Diagram

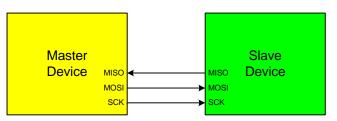

Figure 16.3. 3-Wire Single Master and Slave Mode Connection Diagram

### 16.3. SPI0 Slave Mode Operation

When SPI0 is enabled and not configured as a master, it will operate as a SPI slave. As a slave, bytes are shifted in through the MOSI pin and out through the MISO pin by a master device controlling the SCK signal. A bit counter in the SPI0 logic counts SCK edges. When 8 bits have been shifted into the shift register, the SPIF flag is set to logic 1, and the byte is copied into the receive buffer. Data is read from the receive buffer by reading SPI0DAT. A slave device cannot initiate transfers. Data to be transferred to the master device is pre-loaded into the shift register by writing to SPI0DAT. Writes to SPI0DAT are double-buffered, and are placed in the transmit buffer first. If the shift register is empty, the contents of the transmit buffer will immediately be transferred into the shift register. When the shift register already contains data, the SPI will load the shift register with the transmit buffer's contents after the last SCK edge of the next (or current) SPI transfer.

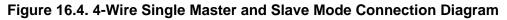

### 16.5. Serial Clock Timing

Four combinations of serial clock phase and polarity can be selected using the clock control bits in the SPI0 Configuration Register (SPI0CFG). The CKPHA bit (SPI0CFG.5) selects one of two clock phases (edge used to latch the data). The CKPOL bit (SPI0CFG.4) selects between a rising edge or a falling edge. Both master and slave devices must be configured to use the same clock phase and polarity. SPI0 should be disabled (by clearing the SPIEN bit, SPI0CN.0) when changing the clock phase or polarity. The clock and data line relationships are shown in Figure 16.5.

The SPI0 Clock Rate Register (SPI0CKR) as shown in SFR Definition 16.3 controls the master mode serial clock frequency. This register is ignored when operating in slave mode. When the SPI is configured as a master, the maximum data transfer rate (bits/sec) is one-half the system clock frequency or 12.5 MHz, whichever is slower. When the SPI is configured as a slave, the maximum data transfer rate (bits/sec) for full-duplex operation is 1/10 the system clock frequency, provided that the master issues SCK, NSS (in 4-wire slave mode), and the serial input data synchronously with the slave's system clock. If the master issues SCK, NSS, and the serial input data asynchronously, the maximum data transfer rate (bits/sec) must be less than 1/10 the system clock frequency. In the special case where the master only wants to transmit data to the slave and does not need to receive data from the slave (i.e. half-duplex operation), the SPI slave can receive data at a maximum data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data synchronously with the slave's system clock frequency.

### 16.6. SPI Special Function Registers

SPI0 is accessed and controlled through four special function registers in the system controller: SPI0CN Control Register, SPI0DAT Data Register, SPI0CFG Configuration Register, and SPI0CKR Clock Rate Register. The four special function registers related to the operation of the SPI0 Bus are described in the following figures.

### 17.1. Software Interface with the LIN Peripheral

The selection of the mode (Master or Slave) and the automatic baud rate feature are done though the LIN0 Control Mode (LIN0CF) register. The other LIN registers are accessed indirectly through the two SFRs LIN0 Address (LINADDR) and LIN0 Data (LINDATA). The LINADDR register selects which LIN register is targeted by reads/writes of the LINDATA register. The full list of indirectly-accessible LIN register is given in Table 17.4 on page 174.

### 17.2. LIN Interface Setup and Operation

The hardware based LIN peripheral allows for the implementation of both Master and Slave nodes with minimal firmware overhead and complete control of the interface status while allowing for interrupt and polled mode operation.

The first step to use the peripheral is to define the basic characteristics of the node:

- Mode—Master or Slave

- Baud Rate—Either defined manually or using the autobaud feature (slave mode only).

- Checksum Type—Select between classic or enhanced checksum, both of which are implemented in hardware.

### 17.2.1. Mode Definition

Following the LIN specification, the peripheral implements both the Slave and Master operating modes in hardware. The mode is configured using the MODE bit (LIN0CF.6).

### 17.2.2. Baud Rate Options: Manual or Autobaud

The LIN peripheral can be selected to have its baud rate calculated manually or automatically. A master node must always have its baud rate set manually, but slave nodes can choose between a manual or automatic setup. The configuration is selected using the ABAUD bit (LIN0CF.5).

Both the manual and automatic baud rate configurations require additional setup. The following sections explain the different options available and their relation with the baud rate, along with the steps necessary to achieve the required baud rate.

### 17.2.3. Baud Rate Calculations—Manual Mode

The baud rate used by the peripheral is a function of the System Clock (SYSCLK) and the bit-timing Registers according to the following equation:

$$baud\_rate = \frac{SYSCLK}{2^{(prescaler + 1)} \times divider \times (multiplier + 1)}$$

The prescaler, divider and multiplier factors are part of the LIN0DIV and LIN0MUL registers and can assume values in the following range:

#### 18.1.2. Mode 1: 16-bit Counter/Timer

Mode 1 operation is the same as Mode 0, except that the counter/timer registers use all 16 bits. The counter/timers are enabled and configured in Mode 1 in the same manner as for Mode 0.

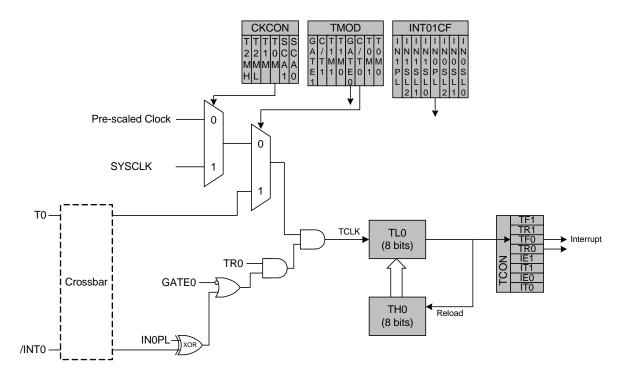

#### 18.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload

Mode 2 configures Timer 0 and Timer 1 to operate as 8-bit counter/timers with automatic reload of the start value. TL0 holds the count and TH0 holds the reload value. When the counter in TL0 overflows from all ones to 0x00, the timer overflow flag TF0 (TCON.5) is set and the counter in TL0 is reloaded from TH0. If Timer 0 interrupts are enabled, an interrupt will occur when the TF0 flag is set. The reload value in TH0 is not changed. TL0 must be initialized to the desired value before enabling the timer for the first count to be correct. When in Mode 2, Timer 1 operates identically to Timer 0.

Both counter/timers are enabled and configured in Mode 2 in the same manner as Mode 0. Setting the TR0 bit (TCON.4) enables the timer when either GATE0 (TMOD.3) is logic 0 or when the input signal INT0 is active as defined by bit IN0PL in register IT01CF (see Section "10.5. External Interrupts" on page 104 for details on the external input signals INT0 and INT0).

Figure 18.2. T0 Mode 2 Block Diagram

| R/W               | R/W                                                                                                                                                                                                                            | R/W                                                                                                                                         | R/W                                                                                                                                                                               | R/W                                                                                                                                              | R/W                                                                                              | R/W                                                                    | R/W                        | Reset Value |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------|-------------|--|--|

| GATE1             | C/T1                                                                                                                                                                                                                           | T1M1                                                                                                                                        | T1M0                                                                                                                                                                              | GATE0                                                                                                                                            | C/T0                                                                                             | T0M1                                                                   | T0M0                       | 0000000     |  |  |

| Bit7              | Bit6                                                                                                                                                                                                                           | Bit5                                                                                                                                        | Bit4                                                                                                                                                                              | Bit3                                                                                                                                             | Bit2                                                                                             | Bit1                                                                   | Bit0<br>SFR Address:       | 0x89        |  |  |

|                   | <b>GATE1</b> : Timer 1 Gate Control.<br>0: Timer 1 enabled when TR1 = 1 irrespective of $\overline{INT0}$ logic level.                                                                                                         |                                                                                                                                             |                                                                                                                                                                                   |                                                                                                                                                  |                                                                                                  |                                                                        |                            |             |  |  |

|                   | 1: Timer 1                                                                                                                                                                                                                     | enabled or                                                                                                                                  | nly when TR1                                                                                                                                                                      | = 1 AND INT                                                                                                                                      | 0 is active                                                                                      | as defined                                                             |                            | •           |  |  |

|                   | <b>C/T1</b> : Cou                                                                                                                                                                                                              |                                                                                                                                             | finition 10.5.<br>1 Select                                                                                                                                                        | TIUICE. IN                                                                                                                                       |                                                                                                  | Shinguration                                                           | i on page to               | 5).         |  |  |

|                   |                                                                                                                                                                                                                                |                                                                                                                                             | mer 1 increme                                                                                                                                                                     | ented by cloo                                                                                                                                    | ck defined b                                                                                     | by T1M bit                                                             | (CKCON.4).                 |             |  |  |

|                   |                                                                                                                                                                                                                                |                                                                                                                                             | Timer 1 increi                                                                                                                                                                    |                                                                                                                                                  |                                                                                                  |                                                                        |                            | iput pin    |  |  |

|                   | (T1).                                                                                                                                                                                                                          |                                                                                                                                             |                                                                                                                                                                                   |                                                                                                                                                  |                                                                                                  |                                                                        |                            |             |  |  |

|                   |                                                                                                                                                                                                                                |                                                                                                                                             | 1 Mode Select                                                                                                                                                                     |                                                                                                                                                  |                                                                                                  |                                                                        |                            |             |  |  |

|                   | These bits                                                                                                                                                                                                                     | select the                                                                                                                                  | Timer 1 opera                                                                                                                                                                     | ation mode.                                                                                                                                      |                                                                                                  |                                                                        |                            |             |  |  |

|                   | T1M1                                                                                                                                                                                                                           | T1M0                                                                                                                                        |                                                                                                                                                                                   | Mode                                                                                                                                             | ;                                                                                                |                                                                        |                            |             |  |  |

|                   | 0                                                                                                                                                                                                                              | 0                                                                                                                                           | Mode 0: 13-bi                                                                                                                                                                     | it counter/tin                                                                                                                                   | ner                                                                                              |                                                                        |                            |             |  |  |

|                   | 0 1 Mode 1: 16-bit counter/timer                                                                                                                                                                                               |                                                                                                                                             |                                                                                                                                                                                   |                                                                                                                                                  |                                                                                                  |                                                                        |                            |             |  |  |

|                   | •                                                                                                                                                                                                                              | I                                                                                                                                           | Node 1: 16-bi                                                                                                                                                                     | it counter/tin                                                                                                                                   | ner                                                                                              |                                                                        |                            |             |  |  |

|                   | 1                                                                                                                                                                                                                              |                                                                                                                                             | Mode 1: 16-bit<br>Mode 2: 8-bit                                                                                                                                                   |                                                                                                                                                  |                                                                                                  | -reload                                                                |                            |             |  |  |

|                   | -                                                                                                                                                                                                                              | 0                                                                                                                                           |                                                                                                                                                                                   | counter/time                                                                                                                                     |                                                                                                  | o-reload                                                               |                            |             |  |  |

| D:40.             | 1                                                                                                                                                                                                                              | 0<br>1                                                                                                                                      | Mode 2: 8-bit<br>Mode 3: Time                                                                                                                                                     | counter/time                                                                                                                                     |                                                                                                  | o-reload                                                               |                            |             |  |  |

|                   | 1<br>1<br>GATE0: T                                                                                                                                                                                                             | 0<br>1<br>mer 0 Gate                                                                                                                        | Mode 2: 8-bit<br>Mode 3: Time<br>e Control.                                                                                                                                       | counter/time<br>r 1 inactive                                                                                                                     | er with auto                                                                                     |                                                                        |                            |             |  |  |

|                   | <b>GATE0</b> : T<br>0: Timer 0                                                                                                                                                                                                 | 0<br>1<br>mer 0 Gate<br>enabled w                                                                                                           | Mode 2: 8-bit<br>Mode 3: Time<br>e Control.<br>hen TR0 = 1 i                                                                                                                      | counter/time<br>r 1 inactive<br>rrespective                                                                                                      | er with auto                                                                                     | ic level.                                                              | by bit IN0PL               | in register |  |  |

|                   | 1<br>1<br>0: Timer 0<br>1: Timer 0                                                                                                                                                                                             | 0<br>1<br>mer 0 Gate<br>enabled w<br>enabled or                                                                                             | Mode 2: 8-bit<br>Mode 3: Time<br>e Control.                                                                                                                                       | counter/time<br>r 1 inactive<br>rrespective<br>= 1 AND INT                                                                                       | er with auto<br>of INTO log<br>T0 is active                                                      | ic level.<br>as defined                                                |                            |             |  |  |

| Bit2:             | <b>GATE0</b> : T<br>0: Timer 0<br>1: Timer 0<br>IT01CF (s<br><b>C/T0</b> : Cou                                                                                                                                                 | 0<br>1<br>mer 0 Gate<br>enabled w<br>enabled or<br>ee SFR De<br>nter/Timer                                                                  | Mode 2: 8-bit<br>Mode 3: Time<br>e Control.<br>then TR0 = 1 i<br>hly when TR0<br>finition 10.5.<br>Select.                                                                        | counter/time<br>r 1 inactive<br>rrespective<br>= 1 AND INT<br>"IT01CF: IN                                                                        | er with auto<br>of INTO log<br>TO is active<br>TO/INT1 Co                                        | ic level.<br>as defined<br>onfiguratior                                | n" on page 10              |             |  |  |

| Bit2:             | <b>GATE0</b> : T<br>0: Timer 0<br>1: Timer 0<br>IT01CF (s<br><b>C/T0</b> : Cou<br>0: Timer F                                                                                                                                   | 0<br>1<br>enabled w<br>enabled or<br>ee SFR De<br>nter/Timer<br>unction: Ti                                                                 | Mode 2: 8-bit<br>Mode 3: Time<br>e Control.<br>then TR0 = 1 i<br>hly when TR0<br>finition 10.5.<br>Select.<br>mer 0 increme                                                       | counter/time<br>r 1 inactive<br>rrespective<br>= 1 AND INT<br>"IT01CF: IN<br>ented by cloo                                                       | er with auto<br>of INTO log<br>TO is active<br>TO/INT1 Co<br>ck defined b                        | ic level.<br>as defined<br>onfiguration<br>by TOM bit                  | " on page 10<br>(CKCON.3). | 5).         |  |  |

| Bit2:             | <b>GATE0</b> : T<br>0: Timer 0<br>1: Timer 0<br>IT01CF (s<br><b>C/T0</b> : Cou<br>0: Timer F<br>1: Counter                                                                                                                     | 0<br>1<br>enabled w<br>enabled or<br>ee SFR De<br>nter/Timer<br>unction: Ti                                                                 | Mode 2: 8-bit<br>Mode 3: Time<br>e Control.<br>then TR0 = 1 i<br>hly when TR0<br>finition 10.5.<br>Select.                                                                        | counter/time<br>r 1 inactive<br>rrespective<br>= 1 AND INT<br>"IT01CF: IN<br>ented by cloo                                                       | er with auto<br>of INTO log<br>TO is active<br>TO/INT1 Co<br>ck defined b                        | ic level.<br>as defined<br>onfiguration<br>by TOM bit                  | " on page 10<br>(CKCON.3). | 5).         |  |  |

| Bit2:             | <b>GATE0</b> : T<br>0: Timer 0<br>1: Timer 0<br>IT01CF (s<br><b>C/T0</b> : Cou<br>0: Timer F<br>1: Counter<br>(T0).                                                                                                            | 0<br>1<br>mer 0 Gate<br>enabled w<br>enabled or<br>ee SFR De<br>nter/Timer<br>unction: Ti<br>Function: Ti                                   | Mode 2: 8-bit<br>Mode 3: Time<br>e Control.<br>then TR0 = 1 in<br>hy when TR0<br>efinition 10.5.<br>Select.<br>mer 0 increme<br>Timer 0 increme                                   | counter/time<br>r 1 inactive<br>= 1 AND INT<br>"IT01CF: IN<br>ented by cloomented by h                                                           | er with auto<br>of INTO log<br>TO is active<br>TO/INT1 Co<br>ck defined b                        | ic level.<br>as defined<br>onfiguration<br>by TOM bit                  | " on page 10<br>(CKCON.3). | 5).         |  |  |

| Bit2:<br>Bits1–0: | <b>GATE0</b> : T<br>0: Timer 0<br>1: Timer 0<br>IT01CF (s<br><b>C/T0</b> : Cou<br>0: Timer F<br>1: Counter<br>(T0).<br><b>T0M1–T0</b>                                                                                          | 0<br>1<br>mer 0 Gate<br>enabled w<br>enabled or<br>ee SFR De<br>nter/Timer<br>unction: Ti<br>Function: Ti                                   | Mode 2: 8-bit<br>Mode 3: Time<br>e Control.<br>then TR0 = 1 i<br>hly when TR0<br>finition 10.5.<br>Select.<br>mer 0 increme                                                       | counter/time<br>r 1 inactive<br>= 1 AND INT<br>"IT01CF: IN<br>ented by cloo<br>mented by h                                                       | er with auto<br>of INTO log<br>TO is active<br>TO/INT1 Co<br>ck defined b                        | ic level.<br>as defined<br>onfiguration<br>by TOM bit                  | " on page 10<br>(CKCON.3). | 5).         |  |  |

| Bit2:<br>Bits1–0: | <b>GATE0</b> : T<br>0: Timer 0<br>1: Timer 0<br>IT01CF (s<br><b>C/T0</b> : Cou<br>0: Timer F<br>1: Counter<br>(T0).<br><b>T0M1–T0</b>                                                                                          | 0<br>1<br>mer 0 Gate<br>enabled or<br>ee SFR De<br>nter/Timer<br>unction: Ti<br>Function:<br><b>M0</b> : Timer (<br>select the              | Mode 2: 8-bit<br>Mode 3: Time<br>e Control.<br>then TR0 = 1 i<br>hly when TR0<br>finition 10.5.<br>Select.<br>mer 0 increme<br>Timer 0 increme                                    | counter/time<br>r 1 inactive<br>= 1 AND INT<br>"IT01CF: IN<br>ented by cloo<br>mented by h<br>t.<br>ation mode.                                  | er with auto<br>of INTO log<br>TO is active<br>TO/INT1 Co<br>ck defined k<br>igh-to-low t        | ic level.<br>as defined<br>onfiguration<br>by TOM bit                  | " on page 10<br>(CKCON.3). | 5).         |  |  |

| Bit2:<br>Bits1–0: | 1           1           0: Timer 0           1: Timer 0           101CF (s           C/T0: Cou           0: Timer F           1: Counter           (T0).           TOM1-TOI           These bits                               | 0<br>1<br>mer 0 Gate<br>enabled or<br>ee SFR De<br>nter/Timer<br>unction: Ti<br>Function:<br>W0: Timer (<br>select the<br>T0M0              | Mode 2: 8-bit<br>Mode 3: Time<br>e Control.<br>then TR0 = 1 i<br>hly when TR0<br>finition 10.5.<br>Select.<br>mer 0 increme<br>Timer 0 increme<br>D Mode Select<br>Timer 0 opera  | counter/time<br>r 1 inactive<br>= 1 AND INT<br>"IT01CF: IN<br>ented by cloo<br>mented by h<br>t.<br>ation mode.                                  | er with auto<br>of INTO log<br>TO is active<br>TO/INT1 Co<br>ck defined to<br>igh-to-low to<br>e | ic level.<br>as defined<br>onfiguration<br>by TOM bit                  | " on page 10<br>(CKCON.3). | 5).         |  |  |

| Bit2:<br>Bits1–0: | 1           1           0: Timer 0           1: Timer 0           IT01CF (s           C/T0: Courd           0: Timer F           1: Counter           (T0).           TOM1-TOI           These bits                            | 0<br>1<br>mer 0 Gate<br>enabled w<br>enabled or<br>ee SFR De<br>nter/Timer<br>unction: Ti<br>Function: Ti<br>Select the<br><b>TOM0</b><br>0 | Mode 2: 8-bit<br>Mode 3: Time<br>e Control.<br>then TR0 = 1 i<br>hly when TR0<br>efinition 10.5.<br>Select.<br>mer 0 increme<br>Timer 0 increme<br>D Mode Select<br>Timer 0 opera | counter/time<br>r 1 inactive<br>= 1 AND INT<br>"IT01CF: IN<br>ented by cloo<br>mented by h<br>t.<br>ation mode.<br><b>Mode</b><br>it counter/tim | er with auto                                                                                     | ic level.<br>as defined<br>onfiguration<br>by TOM bit                  | " on page 10<br>(CKCON.3). | 5).         |  |  |

| Bit2:<br>Bits1–0: | 1           1           0: Timer 0           1: Timer 0           1T01CF (s           C/T0: Could           0: Timer F           1: Counter           (T0).           TOM1-T0I           These bits           T0M1           0 | 0<br>1<br>mer 0 Gate<br>enabled or<br>ee SFR De<br>nter/Timer<br>unction: Ti<br>Function:<br>Select the<br><b>TOM0</b><br>0<br>1            | Mode 2: 8-bit<br>Mode 3: Time<br>e Control.<br>then TR0 = 1 i<br>hly when TR0<br>finition 10.5.<br>Select.<br>mer 0 increme<br>Timer 0 increme<br>D Mode Select<br>Timer 0 opera  | counter/time<br>r 1 inactive<br>= 1 AND INT<br>"IT01CF: IN<br>ented by cloo<br>mented by h<br>t.<br>ation mode.<br><b>Mode</b><br>it counter/tim | er with auto                                                                                     | ic level.<br>as defined<br>onfiguration<br>by TOM bit<br>transitions o | " on page 10<br>(CKCON.3). | 5).         |  |  |

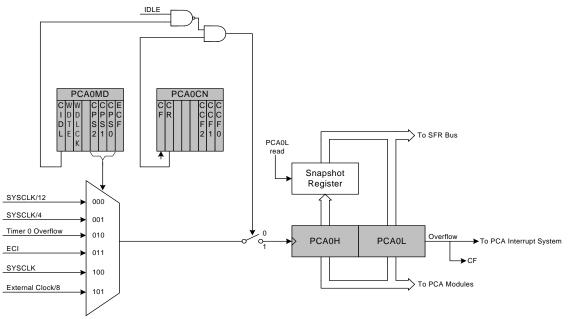

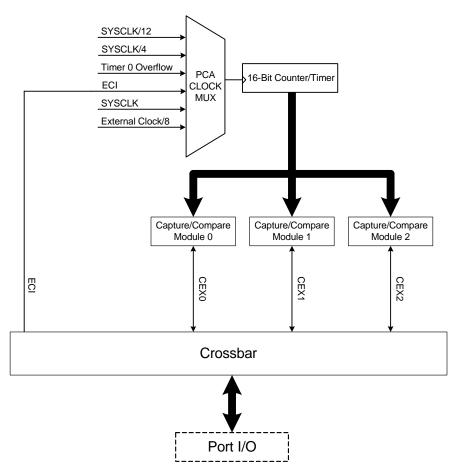

## **19. Programmable Counter Array (PCA0)**

The Programmable Counter Array (PCA0) provides enhanced timer functionality while requiring less CPU intervention than the standard 8051 counter/timers. The PCA consists of a dedicated 16-bit counter/timer and three 16-bit capture/compare modules. Each capture/compare module has its own associated I/O line (CEXn) which is routed through the Crossbar to Port I/O when enabled (See Section "13.1. Priority Cross-bar Decoder" on page 122 for details on configuring the Crossbar). The counter/timer is driven by a programmable timebase that can select between six sources: system clock, system clock divided by four, system clock divided by twelve, the external oscillator clock source divided by 8, Timer 0 overflow, or an external clock signal on the ECI input pin. Each capture/compare module may be configured to operate independently in one of three modes: Edge-Triggered Capture, Software Timer, High-Speed Output, Frequency Output, 8-Bit PWM, or 16-Bit PWM (each mode is described in Section "19.2. Capture/Compare Modules" on page 197). The PCA is configured and controlled through the system controller's Special Function Registers. The PCA block diagram is shown in Figure 19.1.

**Important Note:** The PCA Module 2 may be used as a watchdog timer (WDT), and is enabled in this mode following a system reset. Access to certain PCA registers is restricted while WDT mode is enabled. See Section "19.3. Watchdog Timer Mode" on page 203 for details.

Figure 19.1. PCA Block Diagram

### **19.1. PCA Counter/Timer**

The 16-bit PCA counter/timer consists of two 8-bit SFRs: PCA0L and PCA0H. PCA0H is the high byte (MSB) of the 16-bit counter/timer and PCA0L is the low byte (LSB). Reading PCA0L automatically latches the value of PCA0H into a "snapshot" register; the following PCA0H read accesses this "snapshot" register. **Reading the PCA0L Register first guarantees an accurate reading of the entire 16-bit PCA0 counter.** Reading PCA0H or PCA0L does not disturb the counter operation. The CPS2-CPS0 bits in the PCA0MD register select the timebase for the counter/timer as shown in Table 19.1.

When the counter/timer overflows from 0xFFFF to 0x0000, the Counter Overflow Flag (CF) in PCA0MD is set to logic 1 and an interrupt request is generated if CF interrupts are enabled. Setting the ECF bit in PCA0MD to logic 1 enables the CF flag to generate an interrupt request. The CF bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software (Note: PCA0 interrupts must be globally enabled before CF interrupts are recognized. PCA0 interrupts are globally enabled by setting the EA bit (IE.7) and the EPCA0 bit in EIE1 to logic 1). Clearing the CIDL bit in the PCA0MD register allows the PCA to continue normal operation while the CPU is in Idle mode.

| CPS2 | CPS1 | CPS0 | Timebase                                                              |

|------|------|------|-----------------------------------------------------------------------|

| 0    | 0    | 0    | System clock divided by 12                                            |

| 0    | 0    | 1    | System clock divided by 4                                             |

| 0    | 1    | 0    | Timer 0 overflow                                                      |

| 0    | 1    | 1    | High-to-low transitions on ECI (max rate = system clock divided by 4) |

| 1    | 0    | 0    | System clock                                                          |

| 1    | 0    | 1    | External oscillator source divided by 8*                              |

### Table 19.1. PCA Timebase Input Options

**Note:** External clock divided by 8 is synchronized with the system clock.