# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                            |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | LINbus, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                |

| Number of I/O              | 16                                                                |

| Program Memory Size        | 4KB (4K x 8)                                                      |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 256 x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.25V                                                        |

| Data Converters            | A/D 16x12b                                                        |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                   |

| Supplier Device Package    | 20-TSSOP                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f533-c-itr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| SFR Definition 13.13. P0SKIP: Port0 Skip                           | 134 |

|--------------------------------------------------------------------|-----|

| SFR Definition 13.14. P1MAT: Port1 Match                           | 134 |

| SFR Definition 13.15. P1MASK: Port1 Mask                           |     |

| SFR Definition 14.1. OSCICN: Internal Oscillator Control           |     |

| SFR Definition 14.2. OSCICL: Internal Oscillator Calibration       | 138 |

| SFR Definition 14.3. OSCIFIN: Internal Fine Oscillator Calibration |     |

| SFR Definition 14.4. OSCXCN: External Oscillator Control           | 142 |

| SFR Definition 14.5. CLKSEL: Clock Select                          |     |

| SFR Definition 15.1. SCON0: Serial Port 0 Control                  | 149 |

| SFR Definition 15.2. SBUF0: Serial (UART0) Port Data Buffer        |     |

| SFR Definition 16.1. SPI0CFG: SPI0 Configuration                   | 157 |

| SFR Definition 16.2. SPI0CN: SPI0 Control                          |     |

| SFR Definition 16.3. SPI0CKR: SPI0 Clock Rate                      |     |

| SFR Definition 16.4. SPI0DAT: SPI0 Data                            |     |

| SFR Definition 17.1. LINADDR: Indirect Address Register            |     |

| SFR Definition 17.2. LINDATA: LIN Data Register                    |     |

| SFR Definition 17.3. LINCF Control Mode Register                   |     |

| SFR Definition 17.4. LIN0DT1: LIN0 Data Byte 1                     |     |

| SFR Definition 17.5. LIN0DT2: LIN0 Data Byte 2                     |     |

| SFR Definition 17.6. LIN0DT3: LIN0 Data Byte 3                     |     |

| SFR Definition 17.7. LIN0DT4: LIN0 Data Byte 4                     |     |

| SFR Definition 17.8. LIN0DT5: LIN0 Data Byte 5                     | 176 |

| SFR Definition 17.9. LIN0DT6: LIN0 Data Byte 6                     |     |

| SFR Definition 17.10. LIN0DT7: LIN0 Data Byte 7                    |     |

| SFR Definition 17.11. LIN0DT8: LIN0 Data Byte 8                    |     |

| SFR Definition 17.12. LIN0CTRL: LIN0 Control Register              |     |

| SFR Definition 17.13. LIN0ST: LIN0 STATUS Register                 |     |

| SFR Definition 17.14. LIN0ERR: LIN0 ERROR Register                 |     |

| SFR Definition 17.15. LINOSIZE: LINO Message Size Register         | 180 |

| SFR Definition 17.16. LIN0DIV: LIN0 Divider Register               |     |

| SFR Definition 17.17. LIN0MUL: LIN0 Multiplier Register            |     |

| SFR Definition 17.18. LIN0ID: LIN0 ID Register                     |     |

| SFR Definition 18.1. TCON: Timer Control                           |     |

| SFR Definition 18.2. TMOD: Timer Mode                              |     |

| SFR Definition 18.3. CKCON: Clock Control                          |     |

| SFR Definition 18.4. TL0: Timer 0 Low Byte                         |     |

| SFR Definition 18.5. TL1: Timer 1 Low Byte                         |     |

| SFR Definition 18.6. TH0: Timer 0 High Byte                        |     |

| SFR Definition 18.7. TH1: Timer 1 High Byte                        |     |

| SFR Definition 18.8. TMR2CN: Timer 2 Control                       |     |

| SFR Definition 18.9. TMR2RLL: Timer 2 Reload Register Low Byte     |     |

| SFR Definition 18.10. TMR2RLH: Timer 2 Reload Register High Byte   |     |

| SFR Definition 18.11. TMR2L: Timer 2 Low Byte                      |     |

| SFR Definition 18.12. TMR2H Timer 2 High Byte                      | 194 |

| SFR Definition 19.1. PCA0CN: PCA Control                           | 206 |

|                                                                    |     |

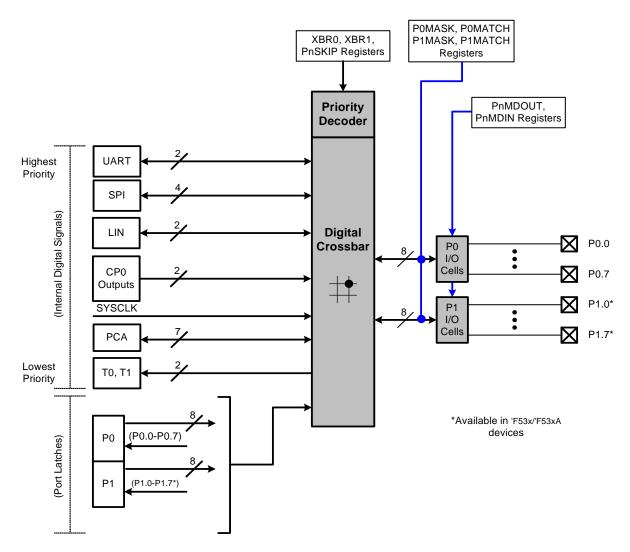

#### 1.9. Port Input/Output

C8051F52x/F52xA/F53x/F53xA devices include up to 16 I/O pins. Port pins are organized as two bytewide ports. The port pins behave like typical 8051 ports with a few enhancements. Each port pin can be configured as a digital or analog I/O pin. Pins selected as digital I/O can be configured for push-pull or open-drain operation. The "weak pullups" that are fixed on typical 8051 devices may be globally disabled to save power.

The Digital Crossbar allows mapping of internal digital system resources to port I/O pins. On-chip counter/timers, serial buses, hardware interrupts, and other digital signals can be configured to appear on the port pins using the Crossbar control registers. This allows the user to select the exact mix of general-purpose port I/O, digital, and analog resources needed for the application.

Figure 1.9. Port I/O Functional Block Diagram

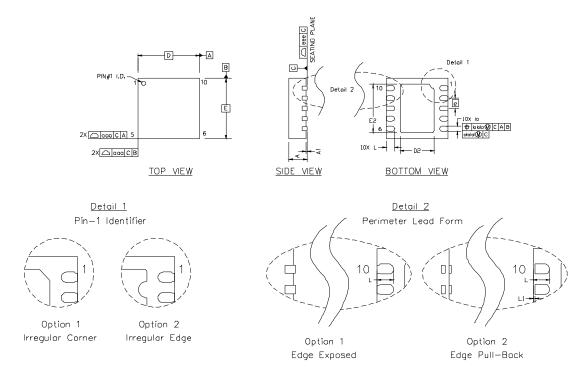

Figure 3.2. DFN-10 Package Diagram

| Dimension | Min       | Nom      | Max  |  |  |  |

|-----------|-----------|----------|------|--|--|--|

| Α         | 0.80      | 0.90     | 1.00 |  |  |  |

| A1        | 0.00      | 0.02     | 0.05 |  |  |  |

| b         | 0.18      | 0.25     | 0.30 |  |  |  |

| D         | 3.00 BSC. |          |      |  |  |  |

| D2        | 1.50      | 1.65     | 1.80 |  |  |  |

| е         | 0.50 BSC. |          |      |  |  |  |

| E         | 3.00 BSC. |          |      |  |  |  |

| E2        | 2.23      | 2.38     | 2.53 |  |  |  |

| L         | 0.30      | 0.40     | 0.50 |  |  |  |

| L1        | 0.00      | —        | 0.15 |  |  |  |

| aaa       | —         | —        | 0.15 |  |  |  |

| bbb       | —         | — — 0.15 |      |  |  |  |

| ddd       | —         | —        | 0.05 |  |  |  |

| eee       |           | —        | 0.08 |  |  |  |

#### Table 3.2. DFN-10 Package Diagram Dimensions

Notes:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- **3.** This drawing conforms to JEDEC outline MO-220, variation VEED except for custom features D2, E2, and L, which are toleranced per supplier designation.

- **4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

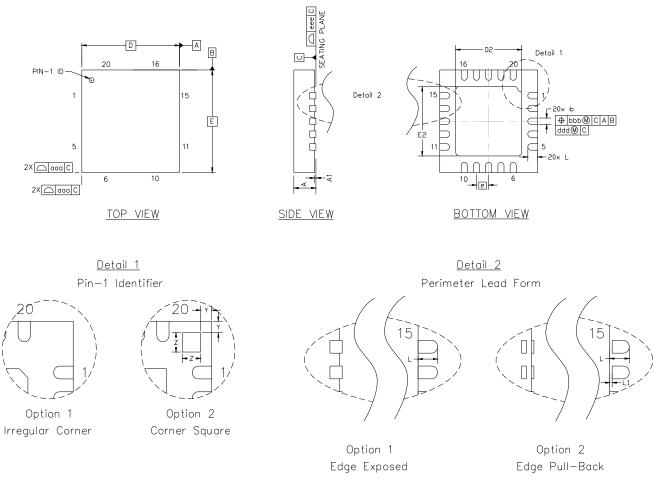

Figure 3.8. QFN-20 Package Diagram\*

\*Note: The Package Dimensions are given in Table 3.8, "QFN-20 Package Diagram Dimensions," on page 49.

| Co        | nvert Start — | ≻ |    |                   |         |      |      |        |          |        |         |        |      |     |  |

|-----------|---------------|---|----|-------------------|---------|------|------|--------|----------|--------|---------|--------|------|-----|--|

|           |               |   |    | Pre-Tracking Mode |         |      |      |        |          |        |         |        |      |     |  |

| (         | Time          |   | F  | S1                | S2      | ] .  | [    | S12    | S13      | F      |         |        |      |     |  |

| ł         | ADC0 State    |   |    |                   |         | Con  | ver  | t      |          |        |         |        |      |     |  |

|           | AD0INT Flag   |   |    |                   |         |      |      |        |          |        |         |        |      |     |  |

|           |               |   |    | F                 | Post-Tr | acki | ng d | or Dua | Il-Track | ing Mc | odes (A | D0TK = | = '0 | 0') |  |

| ſ         | Time          |   | F  | S1                | S2      | F    | F    | S1     | S2       | ]      | S12     | S13    | F    |     |  |

| $\langle$ | ADC0 State    |   |    | Tra               | ack     |      |      |        |          | Convei | rt      |        |      |     |  |

| Ĺ         | AD0INT Flag   |   |    |                   |         |      |      |        |          |        |         |        |      |     |  |

|           |               |   | Ke | y<br>]            | Equal   | to c | one  | period | of FCL   | _K.    |         |        |      |     |  |

F

Sn

Each Sn is equal to one period of the SAR clock.

Figure 4.4. 12-Bit ADC Tracking Mode Example

#### **10.5. External Interrupts**

The INTO and INTO external interrupt sources are configurable as active high or low, edge or level sensitive. The INOPL (INTO Polarity) and IN1PL (INTO Polarity) bits in the IT01CF register select active high or active low; the IT0 and IT1 bits in TCON (Section "18.1. Timer 0 and Timer 1" on page 182) select level or edge sensitive. The table below lists the possible configurations.

| IT0 | IN0PL | INT0 Interrupt               |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

| IT1 | IN1PL | INT1 Interrupt               |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

INTO and INTO are assigned to Port pins as defined in the ITO1CF register (see SFR Definition 10.5). Note that INTO and INTO Port pin assignments are independent of any Crossbar assignments. INTO and INTO will monitor their assigned Port pins without disturbing the peripheral that was assigned the Port pin via the Crossbar. To assign a Port pin only to INTO and/or INTO, configure the Crossbar to skip the selected pin(s). This is accomplished by setting the associated bit in register XBRO (see Section "13.1. Priority Crossbar Decoder" on page 122 for complete details on configuring the Crossbar).

In the typical configuration, the external interrupt pins should be skipped in the crossbar and configured as open-drain with the pin latch set to 1. See Section "13. Port Input/Output" on page 120 for more information.

IE0 (TCON.1) and IE1 (TCON.3) serve as the interrupt-pending flags for the INT0 and INT0 external interrupts, respectively. If an INT0 or INT0 external interrupt is configured as edge-sensitive, the corresponding interrupt-pending flag is automatically cleared by the hardware when the CPU vectors to the ISR. When configured as level sensitive, the interrupt-pending flag remains logic 1 while the input is active as defined by the corresponding polarity bit (IN0PL or IN1PL); the flag remains logic 0 while the input is inactive. The external interrupt source must hold the input active until the interrupt request is recognized. It must then deactivate the interrupt request before execution of the ISR completes or another interrupt request will be generated.

| FR Defi     | nition 10.5. IT01C                                 | F: INT0/INT1 Configurat               | ion                                                 |  |  |  |  |

|-------------|----------------------------------------------------|---------------------------------------|-----------------------------------------------------|--|--|--|--|

| R/W         | R/W R/W                                            | R/W R/W F                             | /W R/W R/W Reset Value                              |  |  |  |  |

| IN1PL       | IN1SL2 IN1SL <sup>2</sup>                          | I IN1SLO IN0PL IN0                    | SL2 INOSL1 INOSL0 00000001                          |  |  |  |  |

| Bit7        | Bit6 Bit5                                          | Bit4 Bit3 E                           | it2 Bit1 Bit0                                       |  |  |  |  |

|             |                                                    |                                       | SFR Address: 0xE4                                   |  |  |  |  |

| Note: Refer | to SFR Definition 18.1. "To                        | CON: Timer Control" on page 186 for I | NT0/1 edge- or level-sensitive interrupt selection. |  |  |  |  |

|             |                                                    |                                       |                                                     |  |  |  |  |

| Bit 7:      | IN1PL: INTO Polarity                               |                                       |                                                     |  |  |  |  |

|             | 0: INTO input is active<br>1: INTO input is active |                                       |                                                     |  |  |  |  |

| Bits 6–4:   | IN1SL2–0: INTO Port                                |                                       |                                                     |  |  |  |  |

|             |                                                    |                                       | . Note that this pin assignment is inde-            |  |  |  |  |

|             |                                                    |                                       | ned Port pin without disturbing the                 |  |  |  |  |

|             |                                                    |                                       | ne Crossbar. The Crossbar will not                  |  |  |  |  |

|             |                                                    |                                       | o skip the selected pin (accomplished by            |  |  |  |  |

|             | -                                                  | sponding bit in register POSKIF       | ').<br>                                             |  |  |  |  |

|             | IN1SL2-0                                           | INT1 Port Pin                         |                                                     |  |  |  |  |

|             | 000                                                | P0.0                                  |                                                     |  |  |  |  |

|             | 001                                                | P0.1                                  |                                                     |  |  |  |  |

|             | 010                                                | P0.2                                  |                                                     |  |  |  |  |

|             | 011                                                | P0.3                                  |                                                     |  |  |  |  |

|             | 100                                                | P0.4                                  |                                                     |  |  |  |  |

|             | 101                                                | P0.5                                  |                                                     |  |  |  |  |

|             | 110                                                | P0.6*                                 |                                                     |  |  |  |  |

|             | 111                                                | P0.7*                                 |                                                     |  |  |  |  |

|             | Note: Available in the                             | C80151F53x/C8051F53xA parts.          |                                                     |  |  |  |  |

| Bit 3:      | INOPL: INTO Polarity                               |                                       | _                                                   |  |  |  |  |

|             | 0: INTO interrupt is ac                            |                                       |                                                     |  |  |  |  |

|             | 1: INTO interrupt is ac                            |                                       |                                                     |  |  |  |  |

| Bits 2–0:   | INTOSL2-0: INTO Po                                 |                                       | Note that this pin assignment is inde-              |  |  |  |  |

|             |                                                    |                                       | and Port pin without disturbing the                 |  |  |  |  |

|             |                                                    |                                       | ne Crossbar. The Crossbar will not                  |  |  |  |  |

|             | <b>e</b> 1                                         |                                       | o skip the selected pin (accomplished by            |  |  |  |  |

|             | setting to 1 the corres                            | sponding bit in register P0SKIF       | 2).                                                 |  |  |  |  |

|             | IN0SL2-0                                           | INT0 Port Pin                         |                                                     |  |  |  |  |

|             | 000                                                | P0.0                                  | 7                                                   |  |  |  |  |

|             | 001                                                | P0.1                                  | 7                                                   |  |  |  |  |

|             | 010                                                | P0.2                                  |                                                     |  |  |  |  |

|             | 011                                                | P0.3                                  | 7                                                   |  |  |  |  |

|             | 100                                                | P0.4                                  |                                                     |  |  |  |  |

|             | 101                                                | P0.5                                  | 1                                                   |  |  |  |  |

|             | 110                                                | P0.6*                                 |                                                     |  |  |  |  |

|             | 111                                                | P0.7*                                 | 1                                                   |  |  |  |  |

|             | Note: Available in the                             | C80151F53x/C8051F53xA parts.          |                                                     |  |  |  |  |

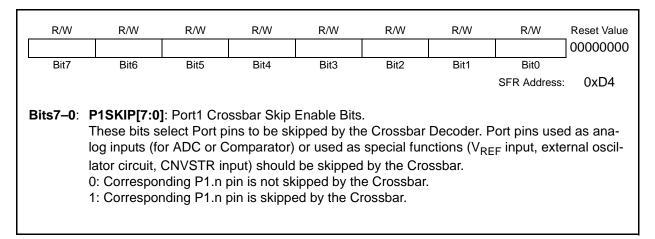

#### SFR Definition 13.13. P0SKIP: Port0 Skip

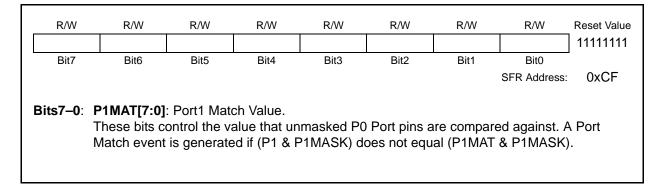

#### SFR Definition 13.14. P1MAT: Port1 Match

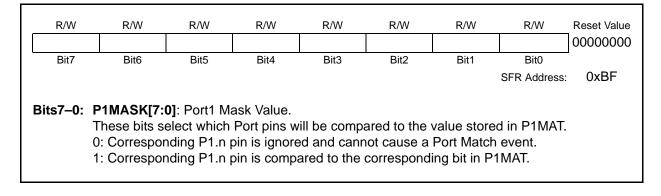

#### SFR Definition 13.15. P1MASK: Port1 Mask

#### 16.2. SPI0 Master Mode Operation

A SPI master device initiates all data transfers on a SPI bus. SPI0 is placed in master mode by setting the Master Enable flag (MSTEN, SPI0CN.6). Writing a byte of data to the SPI0 data register (SPI0DAT) when in master mode writes to the transmit buffer. If the SPI shift register is empty, the byte in the transmit buffer is moved to the shift register, and a data transfer begins. The SPI0 master immediately shifts out the data serially on the MOSI line while providing the serial clock on SCK. The SPIF (SPI0CN.7) flag is set to logic 1 at the end of the transfer. If interrupts are enabled, an interrupt request is generated when the SPIF flag is set. While the SPI0 master transfers data to a slave on the MOSI line, the addressed SPI slave device simultaneously transfers data to the SPI master on the MISO line in a full-duplex operation. Therefore, the SPIF flag serves as both a transmit-complete and receive-data-ready flag. The data byte received from the slave is transferred MSB-first into the master's shift register. When a byte is fully shifted into the register, it is moved to the receive buffer where it can be read by the processor by reading SPI0DAT.

When configured as a master, SPI0 can operate in one of three different modes: multi-master mode, 3-wire single-master mode, and 4-wire single-master mode. The default, multi-master mode is active when NSS-MD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 1. In this mode, NSS is an input to the device, and is used to disable the master SPI0 when another master is accessing the bus. When NSS is pulled low in this mode, MSTEN (SPI0CN.6) and SPIEN (SPI0CN.0) are set to 0 to disable the SPI master device, and a Mode Fault is generated (MODF, SPI0CN.5 = 1). Mode Fault will generate an interrupt if enabled. SPI0 must be manually re-enabled in software under these circumstances. In multi-master systems, devices will typically default to being slave devices while they are not acting as the system master device. In multi-master mode, slave devices can be addressed individually (if needed) using general-purpose I/O pins. Figure 16.2 shows a connection diagram between two master devices in multiple-master mode.

3-wire single-master mode is active when NSSMD1 (SPI0CN.3) = 0 and NSSMD0 (SPI0CN.2) = 0. In this mode, NSS is not used and is not mapped to an external port pin through the crossbar. Any slave devices that must be addressed in this mode should be selected using general-purpose I/O pins. Figure 16.3 shows a connection diagram between a master device in 3-wire master mode and a slave device.

4-wire single-master mode is active when NSSMD1 (SPI0CN.3) = 1. In this mode, NSS is configured as an output pin and can be used as a slave-select signal for a single SPI device. In this mode, the output value of NSS is controlled (in software) with the bit NSSMD0 (SPI0CN.2). Additional slave devices can be addressed using general-purpose I/O pins. Figure 16.4 shows a connection diagram for a master device in 4-wire master mode and two slave devices.

### SFR Definition 16.1. SPI0CFG: SPI0 Configuration

| R          | R/W                           | R/W               | R/W         | R            | R            | R             | R              | Reset Value |  |

|------------|-------------------------------|-------------------|-------------|--------------|--------------|---------------|----------------|-------------|--|

| SPIBSY     | MSTEN                         | CKPHA             | CKPOL       | SLVSEL       | NSSIN        | SRMT          | RXBMT          | 00000111    |  |

| Bit7       | Bit6                          | Bit5              | Bit4        | Bit3         | Bit2         | Bit1          | Bit0           |             |  |

|            |                               | SFR Address: 0xA1 |             |              |              |               |                |             |  |

|            |                               |                   |             |              |              |               |                |             |  |

| Bit 7:     | SPIBSY: SP                    |                   | • /         |              |              |               |                |             |  |

| D:4 C.     | This bit is se<br>MSTEN: Ma   |                   |             | transfer is  | in progress  | (Master or    | Slave Mode     | e).         |  |

| Bit 6:     | 0: Disable m                  |                   |             | n clava mod  | 0            |               |                |             |  |

|            | 1: Enable ma                  |                   |             |              | е.           |               |                |             |  |

| Bit 5:     | CKPHA: SP                     |                   |             | s a master.  |              |               |                |             |  |

| Dit J.     | This bit cont                 |                   |             | ise          |              |               |                |             |  |

|            | 0: Data cent                  |                   |             |              |              |               |                |             |  |

|            | 1: Data cent                  |                   |             |              | d.*          |               |                |             |  |

| Bit 4:     | CKPOL: SP                     |                   |             |              |              |               |                |             |  |

|            | This bit cont                 |                   |             | arity.       |              |               |                |             |  |

|            | 0: SCK line I                 | ow in idle s      | tate.       |              |              |               |                |             |  |

|            | 1: SCK line h                 | high in idle s    | state.      |              |              |               |                |             |  |

| Bit 3:     | SLVSEL: Sla                   | ave Selecte       | d Flag (rea | d only).     |              |               |                |             |  |

|            | This bit is se                | •                 |             |              |              | •             |                |             |  |

|            | is cleared to                 |                   |             |              |              |               |                |             |  |

|            | instantaneou                  |                   |             |              |              | ed version of | of the pin in  | put.        |  |

| Bit 2:     | NSSIN: NSS                    |                   |             | •            | • /          |               |                |             |  |

|            | This bit mim                  |                   |             |              | •            | the NSS po    | ort pin at the | e time that |  |

| <b>-</b>   | the register i                |                   | •           | •            |              |               |                |             |  |

| Bit 1:     | SRMT: Shift                   |                   |             |              |              |               |                |             |  |

|            | This bit will b               |                   |             |              |              |               |                | •           |  |

|            | and there is                  |                   |             |              |              |               |                |             |  |

|            | receive buffe<br>the transmit |                   |             |              | byte is trai | isiened to t  | ne sniit regi  | ster nom    |  |

|            | NOTE: SRM                     |                   |             |              |              |               |                |             |  |

| Bit 0:     | RXBMT: Red                    |                   |             |              | Mode read    | l only)       |                |             |  |

| Dit V.     | This bit will b               |                   |             |              |              |               | nd contains    | no new      |  |

|            | information.                  |                   |             |              |              |               |                |             |  |

|            | this bit will re              |                   |             | lon availabl |              |               |                | boomroad    |  |

|            | NOTE: RXB                     | 0                 |             | r Mode.      |              |               |                |             |  |

|            |                               |                   |             |              |              |               |                |             |  |

| ote: See T | able 16.1 for ti              | ming parame       | eters.      |              |              |               |                |             |  |

|            |                               | • •               |             |              |              |               |                |             |  |

### SFR Definition 16.2. SPI0CN: SPI0 Control

| R/W      | R/W                                                                                                                                    | R/W          | R/W          | R/W         | R/W         | R                                      | R/W         | Reset Value        |  |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|-------------|-------------|----------------------------------------|-------------|--------------------|--|--|

| SPIF     | WCOL                                                                                                                                   | MODF         | RXOVRN       | NSSMD1      | NSSMD0      | TXBMT                                  | SPIEN       | 00000110           |  |  |

| Bit7     | Bit6                                                                                                                                   | Bit5         | Bit4         | Bit3        | Bit2        | Bit1                                   | Bit0        | Bit<br>Addressable |  |  |

|          |                                                                                                                                        |              |              |             |             |                                        | SFR Addres  |                    |  |  |

|          |                                                                                                                                        |              |              |             |             |                                        |             |                    |  |  |

| Bit7:    | <b>SPIF</b> : SPI0 Interrupt Flag.<br>This bit is set to logic 1 by hardware at the end of a data transfer. If interrupts are enabled, |              |              |             |             |                                        |             |                    |  |  |

|          | setting this b                                                                                                                         | •            |              |             |             |                                        | •           |                    |  |  |

|          | automatically                                                                                                                          |              |              |             |             |                                        |             |                    |  |  |

| Bit6:    | WCOL: Write                                                                                                                            | e Collision  | Flag.        |             |             |                                        |             |                    |  |  |

|          | This bit is se attempted w                                                                                                             | -            | •            | · •         |             | • •                                    |             |                    |  |  |

|          | occurs, the v                                                                                                                          |              |              |             |             |                                        |             |                    |  |  |

|          | bit is not aut                                                                                                                         | omatically o | cleared by h | •           |             |                                        |             |                    |  |  |

| Bit5:    | MODF: Mod                                                                                                                              | •            |              |             |             | 0 :::::::::::::::::::::::::::::::::::: |             |                    |  |  |

|          | This bit is se collision is de                                                                                                         |              |              |             |             |                                        |             |                    |  |  |

|          | matically cle                                                                                                                          | •            |              |             |             | /                                      |             |                    |  |  |

| Bit4:    | RXOVRN: R                                                                                                                              |              | <b>U</b> (   |             | • /         |                                        |             |                    |  |  |

|          | This bit is se<br>fer still holds                                                                                                      | •            |              | · •         |             | • •                                    |             |                    |  |  |

|          | shifted into t                                                                                                                         |              |              |             |             |                                        |             |                    |  |  |

|          | be cleared b                                                                                                                           | y software.  | -            |             |             |                                        | •           |                    |  |  |

| Bits3-2: | NSSMD1-N                                                                                                                               |              |              |             | madaa.      |                                        |             |                    |  |  |

|          | Selects betw<br>(See Section                                                                                                           |              | •            | •           |             | e 153 and \$                           | Section "16 | .3. SPI0           |  |  |

|          | Slave Mode                                                                                                                             |              |              | •           |             |                                        |             |                    |  |  |

|          | 00: 3-Wire S                                                                                                                           |              |              |             |             |                                        |             |                    |  |  |

|          | 01: 4-Wire S<br>1x: 4-Wire S                                                                                                           |              |              |             |             |                                        |             |                    |  |  |

|          | assume the                                                                                                                             |              |              | o signal is | mapped do t | anoutputn                              |             |                    |  |  |

| Bit1:    | TXBMT: Tra                                                                                                                             |              |              |             |             |                                        |             |                    |  |  |

|          | This bit will b<br>data in the tr                                                                                                      |              |              |             |             |                                        |             |                    |  |  |

|          | indicating the                                                                                                                         |              |              |             | -           |                                        |             |                    |  |  |

| Bit0:    | SPIEN: SPIC                                                                                                                            | ) Enable.    |              |             |             |                                        |             |                    |  |  |

|          | This bit enab                                                                                                                          |              | s the SPI.   |             |             |                                        |             |                    |  |  |

|          | 0: SPI disabl<br>1: SPI enabl                                                                                                          |              |              |             |             |                                        |             |                    |  |  |

|          |                                                                                                                                        |              |              |             |             |                                        |             |                    |  |  |

### SFR Definition 17.3. LINCF Control Mode Register

| R/W   | R/W           | R/W                                                                                                           | R/W        | R/W         | R/W          | R/W       | R/W          | Reset Value |  |  |

|-------|---------------|---------------------------------------------------------------------------------------------------------------|------------|-------------|--------------|-----------|--------------|-------------|--|--|

| LINEN | MODE          | ABAUD                                                                                                         |            |             |              |           |              | 00000000    |  |  |

| Bit7  | Bit6          | Bit5                                                                                                          | Bit4       | Bit3        | Bit2         | Bit1      | Bit0         | ,<br>,      |  |  |

|       |               |                                                                                                               |            |             |              |           | SFR Address: | 0x95        |  |  |

| Bit7: | LINEN: LIN    |                                                                                                               | nable bit  |             |              |           |              |             |  |  |

|       | 0: LINO is di |                                                                                                               |            |             |              |           |              |             |  |  |

| -     | 1: LIN0 is er |                                                                                                               |            |             |              |           |              |             |  |  |

| Bit6: | MODE: LIN     |                                                                                                               |            |             |              |           |              |             |  |  |

|       | 0: LIN0 oper  |                                                                                                               |            |             |              |           |              |             |  |  |

|       | 1: LIN0 oper  | rates in Mas                                                                                                  | ter mode.  |             |              |           |              |             |  |  |

| Bit5: | ABAUD: LIN    | Mode Auto                                                                                                     | omatic Bau | d Rate Sele | ction (slave | e mode or | nly).        |             |  |  |

|       |               | ABAUD: LIN Mode Automatic Baud Rate Selection (slave mode only).<br>0: Manual baud rate selection is enabled. |            |             |              |           |              |             |  |  |

|       | 1. Automatic  | 1: Automatic baud rate selection is enabled.                                                                  |            |             |              |           |              |             |  |  |

|       |               |                                                                                                               |            |             |              |           |              |             |  |  |

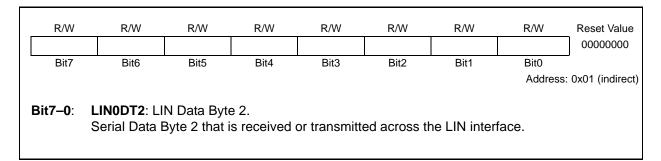

### SFR Definition 17.5. LIN0DT2: LIN0 Data Byte 2

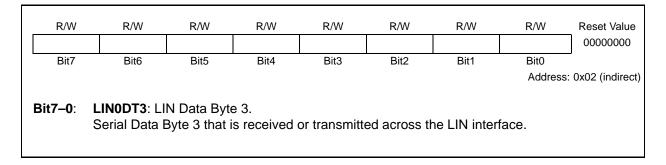

### SFR Definition 17.6. LIN0DT3: LIN0 Data Byte 3

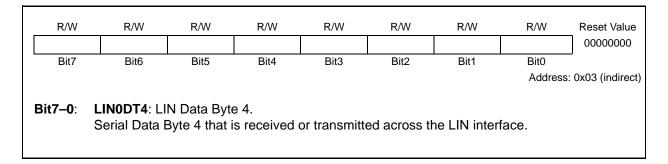

### SFR Definition 17.7. LIN0DT4: LIN0 Data Byte 4

### SFR Definition 17.13. LIN0ST: LIN0 STATUS Register

| R      | R                             | R     | R           | R/W           | R             | R               | R            | Reset Value       |  |

|--------|-------------------------------|-------|-------------|---------------|---------------|-----------------|--------------|-------------------|--|

| ACTIVE | IDLTOUT                       | ABORT | DTREQ       | LININT        | ERROR         | WAKEUP          | DONE         | 00000000          |  |

| Bit7   | Bit6                          | Bit5  | Bit4        | Bit3          | Bit2          | Bit1            | Bit0         | _                 |  |

|        |                               |       |             |               |               |                 | Address      | : 0x09 (indirect) |  |

|        |                               |       |             |               |               |                 |              |                   |  |

| Bit7:  | ACTIVE: LIN Bus Activity Bit. |       |             |               |               |                 |              |                   |  |

|        | 0: No transm                  |       |             |               |               |                 |              |                   |  |

| 5.40   | 1: Transmiss                  |       |             |               |               |                 |              |                   |  |

| Bit6:  | IDLTOUT: B                    |       | •           |               | only).        |                 |              |                   |  |

|        | 0: The bus h                  |       |             |               | oconde bu     | t the bus is n  | at vot in Sl | oon modo          |  |

| Bit5:  | ABORT: Abo                    |       |             |               |               |                 | or yer in Si | eep mode.         |  |

| Dito.  |                               |       |             |               |               | topped. This    | bit is reset | to 0 after        |  |

|        |                               |       |             |               |               | ding transmis   |              |                   |  |

|        |                               |       |             |               |               | st transmissi   |              | STOP bit          |  |

|        | (LIN0CTRL.                    | ,     |             |               |               |                 |              |                   |  |

| Bit4:  | DTREQ: Dat                    |       |             |               |               |                 |              |                   |  |

|        | 0: Data ident                 |       |             |               |               |                 |              |                   |  |

| D:40.  | 1: Data ident                 |       |             | J.            |               |                 |              |                   |  |

| Bit3:  | LININT: Inter                 |       |             | hit is cloars | d by cottin   | g RSTINT (L     |              | 2)                |  |

|        | 1: There is a                 |       |             |               | su by setting | g KSTINT (L     |              | )                 |  |

| Bit2:  | ERROR: Co                     |       |             |               |               |                 |              |                   |  |

|        |                               |       |             |               | ed by setti   | ng RSTERR       | (LIN0CTR     | L.2)              |  |

|        | 1: An error h                 |       |             |               |               | C               | ·            | ,                 |  |

| Bit1:  | WAKEUP: V                     | •     |             |               |               |                 |              |                   |  |

|        |                               |       |             |               |               | een received    | ł.           |                   |  |

| D'40   | 1: A wakeup                   |       |             |               | been recei    | ived.           |              |                   |  |

| Bit0:  | DONE: Tran                    |       |             |               | haan atarta   | d This hit is   | alcored at   | the start of      |  |

|        | a transmissi                  |       | in progress | or nas not    | Deen starte   | ed. This bit is | cleared at   | the start of      |  |

|        | 1: The current                |       | sion is com | nlete         |               |                 |              |                   |  |

|        |                               |       |             |               |               |                 |              |                   |  |

|        |                               |       |             |               |               |                 |              |                   |  |

|        |                               |       |             |               |               |                 |              |                   |  |

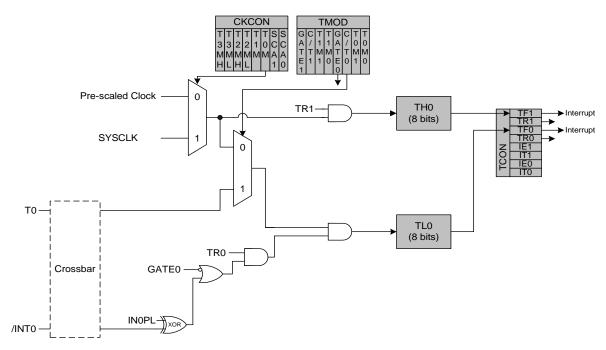

#### 18.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)

In Mode 3, Timer 0 is configured as two separate 8-bit counter/timers held in TL0 and TH0. The counter/timer in TL0 is controlled using the Timer 0 control/status bits in TCON and TMOD: TR0, C/T0, GATE0 and TF0. TL0 can use either the system clock or an external input signal as its timebase. The TH0 register is restricted to a timer function sourced by the system clock or prescaled clock. TH0 is enabled using the Timer 1 run control bit TR1. TH0 sets the Timer 1 overflow flag TF1 on overflow and thus controls the Timer 1 interrupt.

Timer 1 is inactive in Mode 3. When Timer 0 is operating in Mode 3, Timer 1 can be operated in Modes 0, 1 or 2, but cannot be clocked by external signals nor set the TF1 flag and generate an interrupt. However, the Timer 1 overflow can be used to generate baud rates for the SMBus and UART. While Timer 0 is operating in Mode 3, Timer 1 run control is handled through its mode settings. To run Timer 1 while Timer 0 is in Mode 3, set the Timer 1 Mode as 0, 1, or 2. To disable Timer 1, configure it for Mode 3.

Figure 18.3. T0 Mode 3 Block Diagram

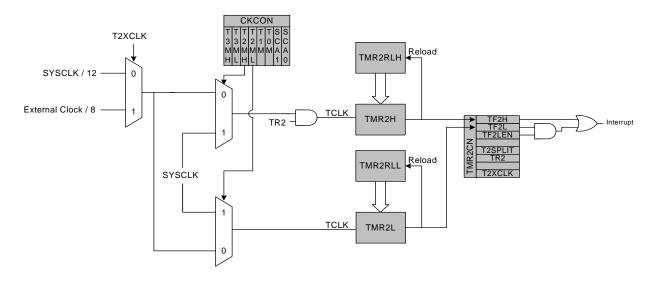

#### 18.2.2. 8-bit Timers with Auto-Reload

When T2SPLIT is set, Timer 2 operates as two 8-bit timers (TMR2H and TMR2L). Both 8-bit timers operate in auto-reload mode as shown in Figure 18.5. TMR2RLL holds the reload value for TMR2L; TMR2RLH holds the reload value for TMR2H. The TR2 bit in TMR2CN handles the run control for TMR2H. TMR2L is always running when configured for 8-bit Mode.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. The Timer 2 Clock Select bits (T2MH and T2ML in CKCON) select either SYSCLK or the clock defined by the Timer 2 External Clock Select bit (T2XCLK in TMR2CN), as follows:

| T2MH | T2XCLK | TMR2H Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | Х      | SYSCLK             |

| T2ML | T2XCLK | TMR2L Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | Х      | SYSCLK             |

The TF2H bit is set when TMR2H overflows from 0xFF to 0x00; the TF2L bit is set when TMR2L overflows from 0xFF to 0x00. When Timer 2 interrupts are enabled (IE.5), an interrupt is generated each time TMR2H overflows. If Timer 2 interrupts are enabled and TF2LEN (TMR2CN.5) is set, an interrupt is generated each time either TMR2L or TMR2H overflows. When TF2LEN is enabled, software must check the TF2H and TF2L flags to determine the source of the Timer 2 interrupt. The TF2H and TF2L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 18.5. Timer 2 8-Bit Mode Block Diagram

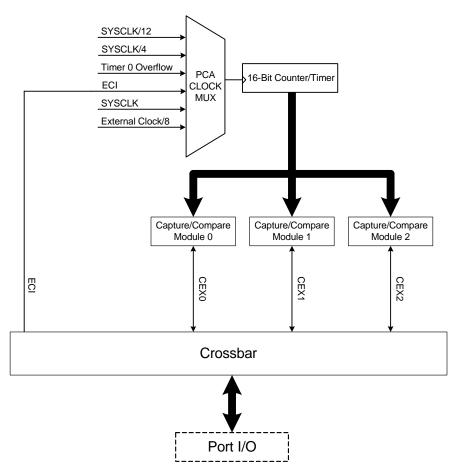

### **19. Programmable Counter Array (PCA0)**

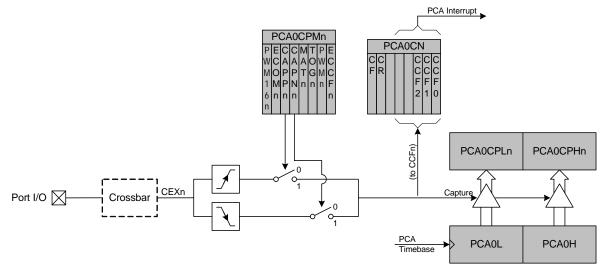

The Programmable Counter Array (PCA0) provides enhanced timer functionality while requiring less CPU intervention than the standard 8051 counter/timers. The PCA consists of a dedicated 16-bit counter/timer and three 16-bit capture/compare modules. Each capture/compare module has its own associated I/O line (CEXn) which is routed through the Crossbar to Port I/O when enabled (See Section "13.1. Priority Cross-bar Decoder" on page 122 for details on configuring the Crossbar). The counter/timer is driven by a programmable timebase that can select between six sources: system clock, system clock divided by four, system clock divided by twelve, the external oscillator clock source divided by 8, Timer 0 overflow, or an external clock signal on the ECI input pin. Each capture/compare module may be configured to operate independently in one of three modes: Edge-Triggered Capture, Software Timer, High-Speed Output, Frequency Output, 8-Bit PWM, or 16-Bit PWM (each mode is described in Section "19.2. Capture/Compare Modules" on page 197). The PCA is configured and controlled through the system controller's Special Function Registers. The PCA block diagram is shown in Figure 19.1.

**Important Note:** The PCA Module 2 may be used as a watchdog timer (WDT), and is enabled in this mode following a system reset. Access to certain PCA registers is restricted while WDT mode is enabled. See Section "19.3. Watchdog Timer Mode" on page 203 for details.

Figure 19.1. PCA Block Diagram

#### 19.2.1. Edge-triggered Capture Mode

In this mode, a valid transition on the CEXn pin causes the PCA to capture the value of the PCA counter/timer and load it into the corresponding module's 16-bit capture/compare register (PCA0CPLn and PCA0CPHn). The CAPPn and CAPNn bits in the PCA0CPMn register are used to select the type of transition that triggers the capture: low-to-high transition (positive edge), high-to-low transition (negative edge), or either transition (positive or negative edge). When a capture occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1 and an interrupt request is generated if CCF interrupts are enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. If both CAPPn and CAPNn bits are set to logic 1, then the state of the Port pin associated with CEXn can be read directly to determine whether a rising-edge or falling-edge caused the capture.

Figure 19.4. PCA Capture Mode Diagram

Note: The CEXn input signal must remain high or low for at least 2 system clock cycles to be recognized by the hardware.

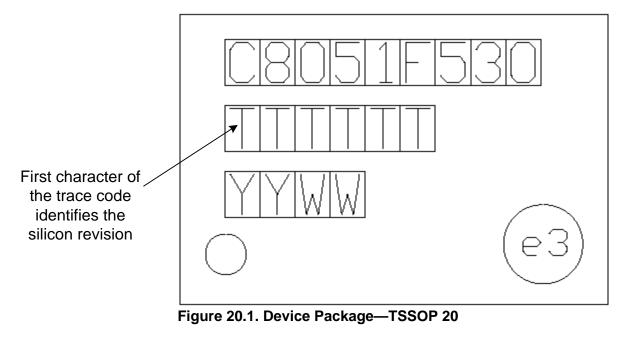

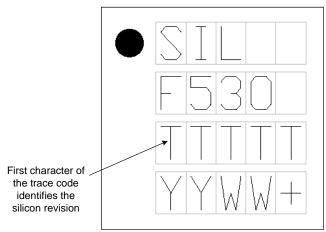

### 20. Device Specific Behavior

This chapter contains behavioral differences between the silicon revisions of C8051F52x/52xA/F53x/53xA devices.

These differences do not affect the functionality or performance of most systems and are described below.

### 20.1. Device Identification

The Part Number Identifier on the top side of the device package can be used for decoding device information. The first character of the trace code identifies the silicon revision. On C8051F52x-C/53x-C devices, the trace code (second line on the TSSOP-20 and DFN-10 packages; third line on the QFN-20 package) will begin with the letter "C". The "A" suffix at the end of the part number such as "C8051F530A" is only present on Revision B devices. All other revisions do not include this suffix. Figures 20.1, 20.2, and 20.3 show how to find the part number on the top side of the device package.

Figure 20.2. Device Package—QFN 20

- Replaced minimum VDD value for Flash write/erase operations in Table 2.9 on page 33 with references to the V<sub>RST-HIGH</sub> theshold specified in Table 2.8 on page 32.

- Removed Output Low Voltage values for condition 'V<sub>REGIN</sub> = 1.8 V' from Table 2.10, "Port I/O DC Electrical Characteristics," on page 33.

- Corrected minor typo ("IFCN = 111b") in Table 2.11, "Internal Oscillator Electrical Characteristics," on page 34.

- Removed the typical value and added the maximum value for the 'Wake-up Time From Suspend' specification with the 'ZTCEN = 0' condition in Table 2.11, "Internal Oscillator Electrical Characteristics," on page 34.

- Added Internal Oscillator Supply current values at specific temperatures for conditions 'ZTCEN = 1' and 'ZTCEN = 0' in Table 2.11, "Internal Oscillator Electrical Characteristics," on page 34. Also updated the table name to clarify that the specifications apply to the internal oscillator.

- Updated Section "1.1. Ordering Information" on page 14 and Table 1.1 with new C8051F52x-C/F53x-C part numbers.

- Updated Table 1.2, "Product Selection Guide (Not Recommended for New Designs)," on page 15 to include C8051F52xA/F53xA part numbers.

- Updated Figure 1.1, Figure 1.2, Figure 1.3, and Figure 1.4 titles to clarify applicable silicon revisions.

- Added figure references to pinout diagrams (Figure 3.1, Figure 3.4, and Figure 3.7) and updated labels to clarify applicable part numbers.

- Updated Table 3.1, Table 3.4, and Table 3.7 to indicate pinouts applicable to C8051F52x-C/F53x-C devices.

- Added note in Section "6. Voltage Regulator (REG0)" on page 74 to indicate the need for bypass capacitors for voltage regulator stability.

- Updated Figure 11.1 on Page 106 and text in Section "11.1. Power-On Reset" on page 107 and Section "11.2. Power-Fail Reset / VDD Monitors (VDDMON0 and VDDMON1)" on page 108 to describe the new level-sensitive V<sub>DD</sub> monitor (VDDMON1).

- Updated SFR Definition 11.1. "VDDMON: VDD Monitor Control" on page 109 to include the VDM1EN bit (bit 4) that controls the new level-sensitive V<sub>DD</sub> monitor (VDDMON1).

- Added notes in Section 11.1 on page 107, Section 11.2 on page 108, and Section 11.3 on page 110 with references to relevant parts of Section "20. Device Specific Behavior" on page 210.

- Moved some notes related to VDD Monitor (VDDMON0) High Threshold setting (V<sub>RST-HIGH</sub>) from Section 11.2 on page 108 to Section 20.5 on page 212 in Section "20. Device Specific Behavior".

- Added Section "11.2.1. VDD Monitor Thresholds and Minimum VDD" on page 108 to describe the recommendations for minimum V<sub>DD</sub> as it relates to the V<sub>DD</sub> monitor thresholds.

- Clarified text in Section "11.7. Flash Error Reset" on page 110.

- Clarified text in items 2, 3 and 4 in Section "12.2.1. V<sub>DD</sub> Maintenance and the V<sub>DD</sub> monitor" on page 115 to reference appropriate specification tables and specify "VDDMON0".