Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                 |

|----------------------------|-----------------------------------------------------------------|

| Product Status             | Active                                                          |

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | LINbus, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT              |

| Number of I/O              | 16                                                              |

| Program Memory Size        | 4KB (4K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 256 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                    |

| Data Converters            | A/D 16x12b                                                      |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                              |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 20-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 20-QFN (4x4)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f533a-im |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## List of Figures

| Figure 1.1. C8051F53xA/F53x-C Block Diagram                          | . 16 |

|----------------------------------------------------------------------|------|

| Figure 1.2. C8051F52xA/F52x-C Block Diagram                          | . 16 |

| Figure 1.3. C8051F53x Block Diagram (Silicon Revision A)             | . 17 |

| Figure 1.4. C8051F52x Block Diagram (Silicon Revision A)             | . 17 |

| Figure 1.5. Development/In-System Debug Diagram                      |      |

| Figure 1.6. Memory Map                                               |      |

| Figure 1.7. 12-Bit ADC Block Diagram                                 | . 22 |

| Figure 1.8. Comparator Block Diagram                                 |      |

| Figure 1.9. Port I/O Functional Block Diagram                        |      |

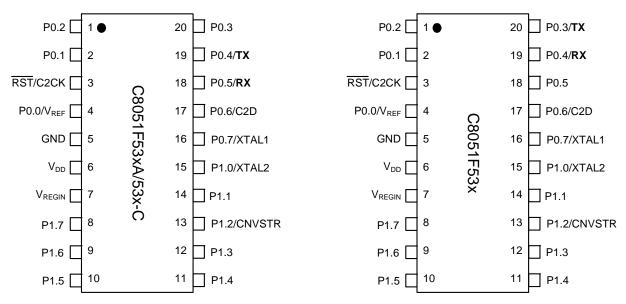

| Figure 3.1. DFN-10 Pinout Diagram (Top View)                         | . 35 |

| Figure 3.2. DFN-10 Package Diagram                                   |      |

| Figure 3.3. DFN-10 Landing Diagram                                   | . 39 |

| Figure 3.4. TSSOP-20 Pinout Diagram (Top View)                       | . 40 |

| Figure 3.5. TSSOP-20 Package Diagram                                 |      |

| Figure 3.6. TSSOP-20 Landing Diagram                                 | . 44 |

| Figure 3.7. QFN-20 Pinout Diagram (Top View)                         | . 45 |

| Figure 3.8. QFN-20 Package Diagram*                                  |      |

| Figure 3.9. QFN-20 Landing Diagram*                                  | . 50 |

| Figure 4.1. ADC0 Functional Block Diagram                            |      |

| Figure 4.2. Typical Temperature Sensor Transfer Function             | . 53 |

| Figure 4.3. ADC0 Tracking Modes                                      |      |

| Figure 4.4. 12-Bit ADC Tracking Mode Example                         |      |

| Figure 4.5. 12-Bit ADC Burst Mode Example with Repeat Count Set to 4 | . 58 |

| Figure 4.6. ADC0 Equivalent Input Circuits                           | . 60 |

| Figure 4.7. ADC Window Compare Example:                              |      |

| Right-Justified Single-Ended Data                                    | . 71 |

| Figure 4.8. ADC Window Compare Example:                              |      |

| Left-Justified Single-Ended Data                                     |      |

| Figure 5.1. Voltage Reference Functional Block Diagram               |      |

| Figure 6.1. External Capacitors for Voltage Regulator Input/Output   |      |

| Figure 7.1. Comparator Functional Block Diagram                      |      |

| Figure 7.2. Comparator Hysteresis Plot                               | . 77 |

| Figure 8.1. CIP-51 Block Diagram                                     |      |

| Figure 9.1. Memory Map                                               |      |

| Figure 11.1. Reset Sources                                           |      |

| Figure 11.2. Power-On and V <sub>DD</sub> Monitor Reset Timing       |      |

| Figure 12.1. Flash Program Memory Map                                | 117  |

| Figure 13.1. Port I/O Functional Block Diagram                       |      |

| Figure 13.2. Port I/O Cell Block Diagram                             | 121  |

| Figure 13.3. Crossbar Priority Decoder with No Pins Skipped          |      |

| (TSSOP 20 and QFN 20)                                                | 122  |

| Figure 13.4. Crossbar Priority Decoder with Crystal Pins Skipped     |      |

| (TSSOP 20 and QFN 20)                                                | 123  |

#### **Table 2.7. Comparator Electrical Characteristics**

$V_{\text{REGIN}} = 2.7-5.25$  V, -40 to +125 °C unless otherwise noted.

All specifications apply to both Comparator0 and Comparator1 unless otherwise noted.

| Parameter                                                      | Conditions            | Min   | Тур  | Max                    | Units |

|----------------------------------------------------------------|-----------------------|-------|------|------------------------|-------|

| Response Time:                                                 | CP0+ - CP0- = 100 mV  |       | 780  | —                      | ns    |

| Mode 0, Vcm <sup>1</sup> = 1.5 V                               | CP0+ - CP0- = -100 mV |       | 980  | _                      | ns    |

| Response Time:                                                 | CP0+ - CP0- = 100 mV  |       | 850  | _                      | ns    |

| Mode 1, Vcm <sup>1</sup> = 1.5 V                               | CP0+ - CP0- = -100 mV | —     | 1120 | —                      | ns    |

| Response Time:                                                 | CP0+ - CP0- = 100 mV  | —     | 870  | —                      | ns    |

| Mode 2, Vcm <sup>1</sup> = 1.5 V                               | CP0+ - CP0- = -100 mV |       | 1310 | —                      | ns    |

| Response Time:                                                 | CP0+ - CP0- = 100 mV  |       | 1980 | —                      | ns    |

| Mode 3, Vcm <sup>1</sup> = 1.5 V                               | CP0+ - CP0- = -100 mV |       | 4770 | —                      | ns    |

| Common-Mode Rejection<br>Ratio                                 |                       |       | 3    | 9                      | mV/V  |

| Positive Hysteresis 1                                          | CP0HYP1-0 = 00        |       | 0.7  | 2                      | mV    |

| Positive Hysteresis 2                                          | CP0HYP1-0 = 01        | 2     | 5    | 10                     | mV    |

| Positive Hysteresis 3                                          | CP0HYP1-0 = 10        | 5     | 10   | 20                     | mV    |

| Positive Hysteresis 4                                          | CP0HYP1-0 = 11        | 13    | 20   | 40                     | mV    |

| Negative Hysteresis 1                                          | CP0HYN1-0 = 00        |       | 0.7  | 2                      | mV    |

| Negative Hysteresis 2                                          | CP0HYN1-0 = 01        | 2     | 5    | 10                     | mV    |

| Negative Hysteresis 3                                          | CP0HYN1-0 = 10        | 5     | 10   | 20                     | mV    |

| Negative Hysteresis 4                                          | CP0HYN1-0 = 11        | 13    | 20   | 40                     | mV    |

| Inverting or Non-Inverting<br>Input Voltage Range <sup>2</sup> |                       | -0.25 |      | V <sub>DD</sub> + 0.25 | V     |

| Input Capacitance <sup>2</sup>                                 |                       | —     | 4    | —                      | pF    |

| Input Bias Current                                             |                       |       | 0.5  | —                      | nA    |

| Input Offset Voltage                                           |                       | -15   | —    | 15                     | mV    |

| Input Impedance                                                |                       |       | 1.5  | _                      | kΩ    |

| Power Supply                                                   |                       |       |      |                        |       |

| Power Supply Rejection <sup>2</sup>                            |                       | _     | 0.2  | 4                      | mV/V  |

| Power-up Time                                                  |                       | — —   | 2.3  | —                      | μs    |

|                                                                | Mode 0                | — —   | 6    | 30                     | μA    |

| Supply Current at DC                                           | Mode 1                |       | 3    | 15                     | μA    |

| Supply Current at DC                                           | Mode 2                | — —   | 2    | 7.5                    | μA    |

|                                                                | Mode 3                |       | 0.3  | 3.8                    | μA    |

1. Vcm is the common-mode voltage on CP0+ and CP0-.

2. Guaranteed by design and/or characterization.

#### **Table 2.8. Reset Electrical Characteristics**

-40 to +125 °C unless otherwise specified.

| Parameter                                              | Conditions                                                                                                                                | Min                         | Тур                     | Мах                         | Units                |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------|-----------------------------|----------------------|

| RST Output Low Voltage                                 | I <sub>OL</sub> = 8.5 mA, V <sub>DD</sub> =<br>2.1 V                                                                                      | _                           | _                       | 0.8                         | V                    |

| RST Input High Voltage                                 |                                                                                                                                           | 0.7 x<br>V <sub>REGIN</sub> |                         |                             | V                    |

| RST Input Low Voltage                                  |                                                                                                                                           |                             |                         | 0.3 x<br>V <sub>REGIN</sub> | V                    |

| RST Input Pullup Impedance                             | $V_{\text{REGIN}} = 1.8 \text{ V}$ $V_{\text{REGIN}} = 2.7 \text{ V}$ $V_{\text{REGIN}} = 3.3 \text{ V}$ $V_{\text{REGIN}} = 5 \text{ V}$ |                             | 330<br>160<br>130<br>80 |                             | kΩ<br>kΩ<br>kΩ<br>kΩ |

| Missing Clock Detector Timeout                         | Time from last system<br>clock rising edge to reset<br>initiation                                                                         | 100                         | 350                     | 650                         | μs                   |

| Reset Time Delay (T <sub>PORDelay</sub> ) <sup>1</sup> | Delay between release<br>of any reset source and<br>code execution at loca-<br>tion 0x0000                                                |                             |                         | 350                         | μs                   |

| Minimum RST Low Time to Generate a System Reset        |                                                                                                                                           | 10                          | _                       | _                           | μs                   |

| V <sub>DD</sub> Monitor (VDDMON0)                      |                                                                                                                                           |                             |                         | •                           |                      |

| Low Threshold (V <sub>RST-LOW</sub> ) <sup>1,2,3</sup> | C8051F52x/53x<br>C8051F52xA/53xA<br>C8051F52x-C/53x-C                                                                                     | 1.8<br>1.65<br>1.65         | 1.9<br>1.75<br>1.75     | 2.0<br>1.8<br>1.8           | V<br>V<br>V          |

| High Threshold (V <sub>RST-HIGH</sub> ) <sup>3</sup>   | C8051F52x/53x<br>C8051F52xA/53xA<br>C8051F52x-C/53x-C                                                                                     | 2.1<br>2.25<br>2.25         | 2.2<br>2.3<br>2.3       | 2.3<br>2.4<br>2.45          | V<br>V<br>V          |

| Turn-on Time                                           |                                                                                                                                           | _                           | 83                      |                             | μs                   |

| Supply Current                                         | V <sub>DD</sub> = 2.1 V                                                                                                                   | _                           | 1                       | 2                           | μA                   |

| Level-Sensitive V <sub>DD</sub> Monitor (VDDMC         | <b>DN1</b> ) <sup>1</sup>                                                                                                                 |                             |                         | •                           |                      |

| Threshold (V <sub>RST1</sub> ) <sup>1,2,3</sup>        | C8051F52x-C/53x-C                                                                                                                         | 1.6                         | 1.75                    | 1.9                         | V                    |

| Supply Current                                         | C8051F52x-C/53x-C                                                                                                                         |                             | 3                       | 6                           | μA                   |

| Notes:<br>1. Refer to Section "20. Device Specific     | Behavior" on page 210.                                                                                                                    |                             |                         |                             |                      |

- Refer to Section "20. Device Specific Behavior" on page 210.

The POR threshold (V<sub>RST</sub>) is V<sub>RST-LOW</sub> or V<sub>RST1</sub>, whichever is higher.

The V<sub>RST</sub> threshold for power fail / brownout is the higher of VDDMON0 and VDDMON1 thresholds, if both are enabled.

| Table 3.4. Pin Definitions for the C8051F53x and C805153xA | (TSSOP 20) |

|------------------------------------------------------------|------------|

|                                                            | (10001 20) |

| Name            | Pin Numbers       |          | Туре             | Description                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------|-------------------|----------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | 'F53xA<br>'F53x-C |          |                  |                                                                                                                                                                                                                                                                                                                                                                               |

| P0.2            | 1                 | 1        | D I/O or<br>A In | Port 0.2. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                    |

| P0.1            | 2                 | 2        | D I/O or<br>A In | Port 0.1. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                    |

| RST/<br>C2CK    | 3                 | 3        | D I/O<br>D I/O   | Device Reset. Open-drain output of internal POR or $V_{DD}$ monitor.<br>An external source can initiate a system reset by driving this pin<br>low for at least the minimum RST low time to generate a system<br>reset, as defined in Table 2.8 on page 32. A 1 k $\Omega$ pullup to<br>$V_{REGIN}$ is recommended. See Reset Sources Section for a com-<br>plete description. |

|                 |                   |          |                  | Clock signal for the C2 Debug Interface.                                                                                                                                                                                                                                                                                                                                      |

| P0.0/           | 4                 | 4        | D I/O or<br>A In | Port 0.0. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                    |

| $V_{REF}$       |                   |          | A O or<br>D In   | External V <sub>REF</sub> Input. See V <sub>REF</sub> Section.                                                                                                                                                                                                                                                                                                                |

| GND             | 5                 | 5        |                  | Ground.                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>DD</sub> | 6                 | 6        |                  | Core Supply Voltage.                                                                                                                                                                                                                                                                                                                                                          |

|                 | e refer to S      | ection " | 20. Device       | Specific Behavior" on page 210.                                                                                                                                                                                                                                                                                                                                               |

### Table 3.7. Pin Definitions for the C8051F53x and C805153xA (QFN 20)

| Name               | Pin Nun           | nbers | Туре             | Description                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------|-------------------|-------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | ʻF53xA<br>ʻF53x-C | 'F53x |                  |                                                                                                                                                                                                                                                                                                                                                                             |

| RST/<br>C2CK       | 1                 | 1     | D I/O<br>D I/O   | Device Reset. Open-drain output of internal POR or $V_{DD}$ monitor<br>An external source can initiate a system reset by driving this pin<br>low for at least the minimum RST low time to generate a system<br>reset, as defined in Table 2.8 on page 32. A 1 k $\Omega$ pullup to<br>$V_{REGIN}$ is recommended. See Reset Sources Section for a com<br>plete description. |

|                    |                   |       |                  | Clock signal for the C2 Debug Interface.                                                                                                                                                                                                                                                                                                                                    |

| P0.0/              | 2                 | 2     | D I/O or<br>A In | Port 0.0. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                  |

| $V_{REF}$          |                   |       | A O or<br>D In   | External V <sub>REF</sub> Input. See V <sub>REF</sub> Section.                                                                                                                                                                                                                                                                                                              |

| GND                | 3                 | 3     |                  | Ground.                                                                                                                                                                                                                                                                                                                                                                     |

| V <sub>DD</sub>    | 4                 | 4     |                  | Core Supply Voltage.                                                                                                                                                                                                                                                                                                                                                        |

| V <sub>REGIN</sub> | 5                 | 5     |                  | On-Chip Voltage Regulator Input.                                                                                                                                                                                                                                                                                                                                            |

| P1.7               | 6                 | 6     | D I/O or<br>A In | Port 1.7. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                  |

| P1.6               | 7                 | 7     | D I/O or<br>A In | Port 1.6. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                  |

| P1.5               | 8                 | 8     | D I/O or<br>A In | Port 1.5. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                  |

| P1.4               | 9                 | 9     | D I/O or<br>A In | Port 1.4. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                  |

| P1.3               | 10                | 10    | D I/O or<br>A In | Port 1.3. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                  |

| P1.2/              | 11                | 11    | D I/O or<br>A In | Port 1.2. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                  |

| CNVSTR             |                   |       | D In             | External Converter start input for the ADC0, see Section "4. 12-<br>Bit ADC (ADC0)" on page 52 for a complete description.                                                                                                                                                                                                                                                  |

| P1.1               | 12                | 12    | D I/O or<br>A In | Port 1.1. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                  |

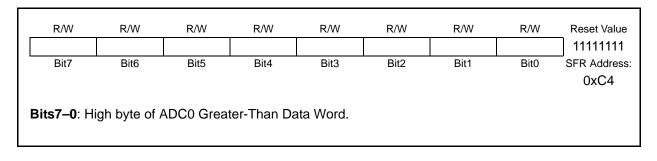

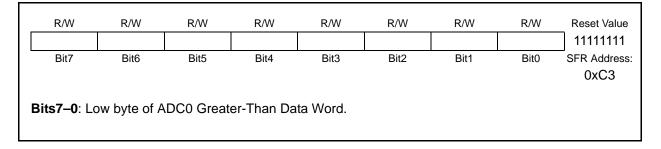

### 4.5. Programmable Window Detector

The ADC Programmable Window Detector continuously compares the ADC0 output registers to user-programmed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD0WINT in register ADC0CN) can also be used in polled mode. The ADC0 Greater-Than (ADC0GTH, ADC0GTL) and Less-Than (ADC0LTH, ADC0LTL) registers hold the comparison values. The window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC0 Less-Than and ADC0 Greater-Than registers.

## SFR Definition 4.10. ADC0GTH: ADC0 Greater-Than Data High Byte

## SFR Definition 4.11. ADC0GTL: ADC0 Greater-Than Data Low Byte

### **10.4.** Interrupt Register Descriptions

The SFRs used to enable the interrupt sources and set their priority level are described below. Refer to the data sheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

### SFR Definition 10.1. IE: Interrupt Enable

| R/W    | R/W                            | R/W           | R/W          | R/W           | R/W            | R/W           | R/W          | Reset Value  |

|--------|--------------------------------|---------------|--------------|---------------|----------------|---------------|--------------|--------------|

| EA     | ESPI0                          | ET2           | ES0          | ET1           | EX1            | ET0           | EX0          | 00000000     |

| Bit7   | Bit6                           | Bit5          | Bit4         | Bit3          | Bit2           | Bit1          | Bit0         | Bit          |

|        |                                |               |              |               |                |               |              | Addressable  |

|        |                                |               |              |               |                |               | SFR Addres   | s: 0xA8      |

| Bit7:  | EA: Global I                   | nterrunt En   | able         |               |                |               |              |              |

| Biti . | This bit glob                  |               |              | ll interrupts | . It override: | s the individ | dual interru | pt mask set- |

|        | tings.                         |               |              |               |                |               |              |              |

|        | 0: Disable al                  | l interrupt s | ources.      |               |                |               |              |              |

|        | 1: Enable ea                   |               | •            |               |                | •             |              |              |

| Bit6:  | ESPI0: Enat                    |               | •            | · ·           | <i>,</i> .     |               |              |              |

|        | This bit sets                  |               | •            | 10 interrupts | S.             |               |              |              |

|        | 0: Disable al                  |               |              |               | _              |               |              |              |

| D:45   | 1: Enable int                  |               |              | ated by SPI   | J.             |               |              |              |

| Bit5:  | ET2: Enable                    |               | •            | or 2 intorru  | nt             |               |              |              |

|        | This bit sets<br>0: Disable Ti |               |              |               | pı.            |               |              |              |

|        | 1: Enable int                  |               |              | ated by the   | TE2L or TE     | 2H flags      |              |              |

| Bit4:  | ES0: Enable                    |               | •            |               |                | Li i nago.    |              |              |

| 2      | This bit sets                  |               |              | RT0 interru   | pt.            |               |              |              |

|        | 0: Disable U                   |               | •            |               | r ·            |               |              |              |

|        | 1: Enable UA                   | ART0 interr   | upt.         |               |                |               |              |              |

| Bit3:  | ET1: Enable                    | Timer 1 Int   | errupt.      |               |                |               |              |              |

|        | This bit sets                  |               | •            | ner 1 interru | pt.            |               |              |              |

|        | 0: Disable al                  |               |              |               |                |               |              |              |

| -      | 1: Enable int                  |               |              | ated by the   | TF1 flag.      |               |              |              |

| Bit2:  | EX1: Enable                    |               | •            | 1             |                |               |              |              |

|        | This bit sets                  |               |              | ernal interri | JPt 1.         |               |              |              |

|        | 0: Disable ex<br>1: Enable ex  |               | •            | te            |                |               |              |              |

| Bit1:  | ETO: Enable                    |               |              | ιο.           |                |               |              |              |

| Ditt.  | This bit sets                  |               | •            | ner 0 interru | nt             |               |              |              |

|        | 0: Disable al                  |               | •            |               | pu             |               |              |              |

|        | 1: Enable int                  |               | •            | ated by the   | TF0 flag.      |               |              |              |

| Bit0:  | EX0: Enable                    |               |              |               | U              |               |              |              |

|        | This bit sets                  | the maskin    | g of the ext | ernal interro | upt 0.         |               |              |              |

|        | 0: Disable ex                  |               | •            |               |                |               |              |              |

|        | 1: Enable ex                   | tern interru  | pt 0 reques  | ts.           |                |               |              |              |

|        |                                |               |              |               |                |               |              |              |

## SFR Definition 10.4. EIP1: Extended Interrupt Priority 1

| R/W   | R/W                            | R/W           | R/W           | R/W           | R/W            | R/W          | R/W          | Reset Value |

|-------|--------------------------------|---------------|---------------|---------------|----------------|--------------|--------------|-------------|

| PMAT  | PREG0                          | PLIN          | PCPR          | PCPF          | PPAC0          | PREG0        | PWADC0       | 0000000     |

| Bit7  | Bit6                           | Bit5          | Bit4          | Bit3          | Bit2           | Bit1         | Bit0         | _           |

|       |                                |               |               |               |                |              | SFR Address: | 0xF6        |

| Bit7: | PMAT. Port M                   |               |               |               |                |              |              |             |

|       | This bit sets                  |               |               |               | rupt.          |              |              |             |

|       | 0: Port Match                  |               |               |               |                |              |              |             |

| Bit6: | 1: Port Match                  |               | • •           |               |                |              |              |             |

| 5110  | PREG0: Volt                    | 0 0           |               |               |                |              |              |             |

|       | This bit sets<br>0: Voltage Re |               |               | • •           | •              |              |              |             |

|       | 1: Voltage Re                  | •             | •             | •             |                |              |              |             |

| Bit5: | PLIN: LIN Int                  | •             | •             | • •           | ty level.      |              |              |             |

| Bito. | This bit sets                  | •             |               |               |                |              |              |             |

|       | 0: LIN interru                 |               |               |               |                |              |              |             |

|       | 1: LIN interru                 |               |               |               |                |              |              |             |

| Bit4: | PCPR: Com                      |               |               |               | ritv Control.  |              |              |             |

|       | This bit sets                  |               |               |               |                |              |              |             |

|       | 0: Comparate                   |               |               |               |                |              |              |             |

|       | 1: Comparate                   | or interrupt  | set to high   | priority leve | el.            |              |              |             |

| Bit3: | PCPF: Comp                     | parator falli | ng Edge Int   | errupt Prior  | ity Control.   |              |              |             |

|       | This bit sets                  | the priority  | of the Fallin | ng Edge Co    | mparator in    | terrupt.     |              |             |

|       | 0: Comparate                   |               |               |               |                |              |              |             |

|       | 1: Comparate                   |               |               |               |                |              |              |             |

| Bit2: | PPAC0: Prog                    |               |               | • • •         | Interrupt P    | riority Cont | rol.         |             |

|       | This bit sets                  |               |               |               |                |              |              |             |

|       | 0: PCA0 inte                   |               |               |               |                |              |              |             |

|       | 1: PCA0 inte                   |               |               |               |                |              |              |             |

| Bit1: | PREGO: ADO                     |               |               |               |                |              |              |             |

|       | This bit sets                  |               |               |               | •              | •            |              |             |

|       | 0: ADC0 Cor                    |               |               |               |                |              |              |             |

| D:40. | 1: ADC0 Cor                    |               |               | •             | • • •          |              |              |             |

| Bit0: | PWADC0: A                      |               |               |               |                |              |              |             |

|       | This bit sets                  |               |               |               |                |              |              |             |

|       | 0: ADC0 Win                    |               |               | •             |                |              |              |             |

|       | 1: ADC0 Win                    | noom comp     | ansoninter    | rupt set to   | ingri priority | ievei.       |              |             |

## SFR Definition 11.2. RSTSRC: Reset Source

| R/W      | R                         | R/W          | R/W          | R                          | R/W           | R/W          | R Reset Value                   |

|----------|---------------------------|--------------|--------------|----------------------------|---------------|--------------|---------------------------------|

|          | FERROR                    | CORSEF       | SWRSF        | WDTRSF                     | MCDRSF        | PORSF        | PINRSF Variable                 |

| Bit7     | Bit6                      | Bit5         | Bit4         | Bit3                       | Bit2          | Bit1         | Bit0                            |

|          |                           |              |              |                            |               |              | SFR Address: 0xEF               |

|          |                           |              |              |                            |               |              |                                 |

| Note: So | oftware should            | avoid read   | modify wri   | te instructio              | ns when wri   | ting values  | to RSTSRC.                      |

| Bit7:    | UNUSED. R                 | ead = 1 Wi   | rite = don't | care                       |               |              |                                 |

| Bit6:    | FERROR: F                 |              |              | ouro.                      |               |              |                                 |

|          | 0: Source of              |              |              | lash read/w                | rite/erase er | ror.         |                                 |

|          | 1: Source of              | last reset w | as a Flash   | read/write/                | erase error.  |              |                                 |

| Bit5:    | CORSEF: Co                | •            |              |                            | -             |              |                                 |

|          | 0: <b>Read:</b> So        |              |              | •                          | ator0.        |              |                                 |

|          |                           | mparator0 i  |              |                            | •             |              |                                 |

|          | 1: Read: So               |              |              | comparator<br>ource (activ |               |              |                                 |

| Bit4:    | SWRSF: Sol                | •            |              | · ·                        | e-10w).       |              |                                 |

| DRT.     | 0: <b>Read:</b> So        |              |              | •                          | o the SWRS    | F bit.       |                                 |

|          | Write: No                 |              |              |                            |               |              |                                 |

|          | 1: Read: So               | urce of last | reset was    | a write to th              | e SWRSF bi    | it.          |                                 |

|          |                           | rces a syste |              |                            |               |              |                                 |

| Bit3:    | WDTRSF: W                 |              |              |                            |               |              |                                 |

|          | 0: Source of              |              |              |                            | •             |              |                                 |

| Bit2:    | 1: Source of<br>MCDRSF: M |              |              |                            |               |              |                                 |

| DILZ.    | 0: Read: So               | -            |              | -                          | a Clock Det   | ector time   | tuc                             |

|          |                           | ssing Clock  |              |                            | 9 010011 001  |              | 541.                            |

|          | 1: Read: So               | -            |              |                            | lock Detecto  | or timeout.  |                                 |

|          | Write: Mis                | ssing Clock  | Detector e   | nabled; trig               | gers a reset  | if a missin  | g clock condition is            |

|          | detected.                 |              | _            |                            |               |              |                                 |

| Bit1:    | PORSF: Pov                |              |              |                            | \\/           |              |                                 |

|          |                           |              |              |                            |               |              | es/disables the V <sub>DD</sub> |

|          |                           |              |              |                            | -             |              | efore the V <sub>DD</sub> moni- |

|          | Definition 11             |              | mzeu ma      | y cause a s                | ystem rese    | L See regi   | ster VDDMON (SFR                |

|          | 0: Read: Las              | ,            | not a pow    | er-on or V <sub>D</sub>    | monitor re    | set.         |                                 |

|          |                           |              |              | ) is not a re              | -             |              |                                 |

|          |                           |              |              |                            |               | all other re | eset flags indetermi-           |

|          | nate.                     |              | •            |                            | ,             |              | č                               |

|          | Write: V <sub>D</sub>     | D monitor (  | /DDMON0      | ) is a reset :             | source.       |              |                                 |

| Bit0:    | PINRSF: HV                | V Pin Reset  | Flag.        |                            |               |              |                                 |

|          | 0: Source of              |              |              |                            |               |              |                                 |

|          | 1: Source of              | last reset w | as RST pi    | n.                         |               |              |                                 |

|          |                           |              |              |                            |               |              |                                 |

|          |                           |              |              |                            |               |              |                                 |

|          |                           |              |              |                            |               |              |                                 |

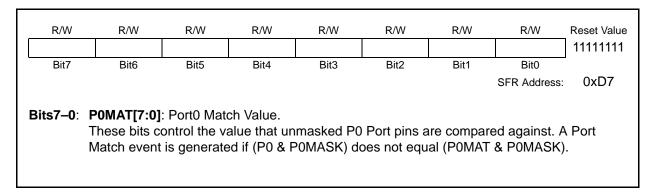

## SFR Definition 13.7. P0MAT: Port0 Match

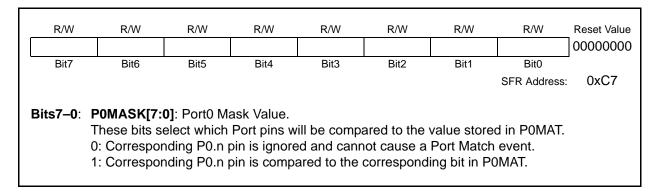

#### SFR Definition 13.8. P0MASK: Port0 Mask

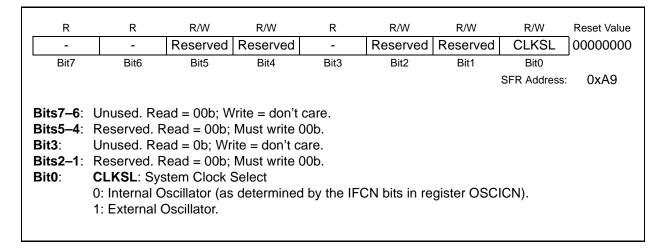

## 14.3. System Clock Selection

The internal oscillator requires little start-up time and may be selected as the system clock immediately following the OSCICN write that enables the internal oscillator. External crystals and ceramic resonators typically require a start-up time before they are settled and ready for use. The Crystal Valid Flag (XTLVLD in register OSCXCN) is set to 1 by hardware when the external oscillator is settled. **To avoid reading a false XTLVLD in crystal mode, the software should delay at least 1 ms between enabling the external oscillator and checking XTLVLD.** RC and C modes typically require no startup time.

The CLKSL bit in register CLKSEL selects which oscillator source is used as the system clock. CLKSL must be set to 1 for the system clock to run from the external oscillator; however the external oscillator may still clock certain peripherals (timers, PCA) when another oscillator is selected as the system clock. The system clock may be switched on-the-fly between the internal oscillator and external oscillator, as long as the selected clock source is enabled and has settled.

### SFR Definition 14.5. CLKSEL: Clock Select

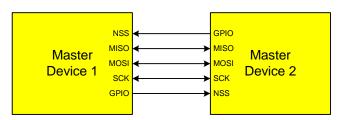

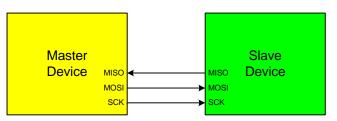

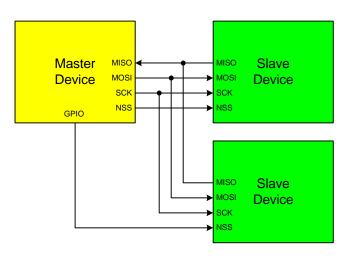

Figure 16.2. Multiple-Master Mode Connection Diagram

Figure 16.3. 3-Wire Single Master and Slave Mode Connection Diagram

### 16.3. SPI0 Slave Mode Operation

When SPI0 is enabled and not configured as a master, it will operate as a SPI slave. As a slave, bytes are shifted in through the MOSI pin and out through the MISO pin by a master device controlling the SCK signal. A bit counter in the SPI0 logic counts SCK edges. When 8 bits have been shifted into the shift register, the SPIF flag is set to logic 1, and the byte is copied into the receive buffer. Data is read from the receive buffer by reading SPI0DAT. A slave device cannot initiate transfers. Data to be transferred to the master device is pre-loaded into the shift register by writing to SPI0DAT. Writes to SPI0DAT are double-buffered, and are placed in the transmit buffer first. If the shift register is empty, the contents of the transmit buffer will immediately be transferred into the shift register. When the shift register already contains data, the SPI will load the shift register with the transmit buffer's contents after the last SCK edge of the next (or current) SPI transfer.

## SFR Definition 16.3. SPI0CKR: SPI0 Clock Rate

| 544        | <b>D</b> 444  | 5 444                         | 5 444                    | 544          | 544         | D 444       | D 444               |             |

|------------|---------------|-------------------------------|--------------------------|--------------|-------------|-------------|---------------------|-------------|

| R/W        | R/W           | R/W                           | R/W                      | R/W          | R/W         | R/W         | R/W                 | Reset Value |

| SCR7       | SCR6          | SCR5                          | SCR4                     | SCR3         | SCR2        | SCR1        | SCR0                | 00000000    |

| Bit7       | Bit6          | Bit5                          | Bit4                     | Bit3         | Bit2        | Bit1        | Bit0<br>SFR Address | 0v A 2      |

|            |               |                               |                          |              |             |             | SFR Address         | S. UXAZ     |

| Bits7–0: S | SCR7-SCR      | 0: SPI0 Clo                   | ck Rate.                 |              |             |             |                     |             |

|            | These bits d  |                               |                          | of the SCK   | Coutput whe | en the SPI0 | module is           | configured  |

|            | or master m   |                               |                          |              |             |             |                     | •           |

|            | clock, and is |                               |                          |              |             |             |                     |             |

| a          | and SPIOCK    | R is the 8-b                  | oit value hel            | d in the SPI | 0CKR regis  | ster.       |                     |             |

|            |               |                               |                          |              |             |             |                     |             |

|            |               |                               |                          |              |             |             |                     |             |

|            | £             | S                             | YSCLK                    |              |             |             |                     |             |

|            | JSCK          | $-\frac{1}{2 \times (SH)}$    | $\frac{YSCLK}{PI0CKR +}$ | 1)           |             |             |                     |             |

|            |               | × ×                           |                          | ,            |             |             |                     |             |

|            |               |                               |                          |              |             |             |                     |             |

|            |               |                               |                          |              |             |             |                     |             |

| f          | or 0 <= SPI   | )CKR <= 2                     | 55                       |              |             |             |                     |             |

|            |               |                               |                          |              |             |             |                     |             |

| Example: I | f SYSCLK =    | 2 MHz and                     | d SPI0CKR                | = 0x04,      |             |             |                     |             |

|            |               |                               |                          |              |             |             |                     |             |

|            |               |                               |                          |              |             |             |                     |             |

|            | C             | 200000                        | 00                       |              |             |             |                     |             |

|            | $f_{SCK}$ =   | $=\frac{200000}{2\times(4+)}$ | 1)                       |              |             |             |                     |             |

|            |               |                               | -)                       |              |             |             |                     |             |

|            |               |                               |                          |              |             |             |                     |             |

|            |               |                               |                          |              |             |             |                     |             |

|            | $f_{SCV} =$   | 200 <i>kHz</i>                |                          |              |             |             |                     |             |

|            | JOLV          |                               |                          |              |             |             |                     |             |

|            |               |                               |                          |              |             |             |                     |             |

|            |               |                               |                          |              |             |             |                     |             |

|            |               |                               |                          |              |             |             |                     |             |

| Parameter          | Description                                                                                                                                        | Min                     | Max                     | Units |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------|-------|--|

| Master Mode        | Timing* (See Figure 16.6 and Figure 16.7)                                                                                                          |                         | 1                       | 1     |  |

| т <sub>мскн</sub>  | SCK High Time                                                                                                                                      | 1 x T <sub>SYSCLK</sub> | —                       | ns    |  |

| T <sub>MCKL</sub>  | SCK Low Time                                                                                                                                       | 1 x T <sub>SYSCLK</sub> | —                       | ns    |  |

| T <sub>MIS</sub>   | MISO Valid to SCK Sample Edge                                                                                                                      | 20                      | —                       | ns    |  |

| т <sub>мін</sub>   | SCK Sample Edge to MISO Change                                                                                                                     | 0                       | —                       | ns    |  |

| Slave Mode T       | iming* (See Figure 16.8 and Figure 16.9)                                                                                                           | ·                       |                         |       |  |

| T <sub>SE</sub>    | NSS Falling to First SCK Edge                                                                                                                      | 2 x T <sub>SYSCLK</sub> | —                       | ns    |  |

| T <sub>SD</sub>    | Last SCK Edge to NSS Rising                                                                                                                        | 2 x T <sub>SYSCLK</sub> | —                       | ns    |  |

| T <sub>SEZ</sub>   | NSS Falling to MISO Valid                                                                                                                          | —                       | 4 x T <sub>SYSCLK</sub> | ns    |  |

| T <sub>SDZ</sub>   | NSS Rising to MISO High-Z                                                                                                                          | —                       | 4 x T <sub>SYSCLK</sub> | ns    |  |

| тскн               | SCK High Time                                                                                                                                      | 5 x T <sub>SYSCLK</sub> | —                       | ns    |  |

| T <sub>CKL</sub>   | SCK Low Time                                                                                                                                       | 5 x T <sub>SYSCLK</sub> | —                       | ns    |  |

| T <sub>SIS</sub>   | MOSI Valid to SCK Sample Edge                                                                                                                      | 2 x T <sub>SYSCLK</sub> | —                       | ns    |  |

| T <sub>SIH</sub>   | SCK Sample Edge to MOSI Change                                                                                                                     | 2 x T <sub>SYSCLK</sub> | —                       | ns    |  |

| Т <sub>SOH</sub>   | SCK Shift Edge to MISO Change                                                                                                                      | -                       | 4 x T <sub>SYSCLK</sub> | ns    |  |

| The max<br>Transmi | is equal to one period of the device system clock (SYS<br>imum possible frequency of the SPI can be calculated<br>ssion: SYSCLK/2<br>on: SYSCLK/10 |                         |                         |       |  |

## Table 16.1. SPI Slave Timing Parameters

## SFR Definition 17.3. LINCF Control Mode Register

| R/W   | R/W                                                              | R/W   | R/W       | R/W  | R/W  | R/W  | R/W          | Reset Value |  |  |  |

|-------|------------------------------------------------------------------|-------|-----------|------|------|------|--------------|-------------|--|--|--|

| LINEN | I MODE                                                           | ABAUD |           |      |      |      |              | 0000000     |  |  |  |

| Bit7  | Bit6                                                             | Bit5  | Bit4      | Bit3 | Bit2 | Bit1 | Bit0         | •           |  |  |  |

|       |                                                                  |       |           |      |      |      | SFR Address: | 0x95        |  |  |  |

| Bit7: | LINEN: LIN                                                       |       | nable bit |      |      |      |              |             |  |  |  |

|       | 0: LIN0 is disabled.<br>1: LIN0 is enabled.                      |       |           |      |      |      |              |             |  |  |  |

| -     |                                                                  |       |           |      |      |      |              |             |  |  |  |

| Bit6: | MODE: LIN Mode Selection                                         |       |           |      |      |      |              |             |  |  |  |

|       | 0: LIN0 operates in Slave mode.                                  |       |           |      |      |      |              |             |  |  |  |

|       | 1: LIN0 operates in Master mode.                                 |       |           |      |      |      |              |             |  |  |  |

| Bit5: | ABAUD: LIN Mode Automatic Baud Rate Selection (slave mode only). |       |           |      |      |      |              |             |  |  |  |

|       | 0: Manual baud rate selection is enabled.                        |       |           |      |      |      |              |             |  |  |  |

|       | 1: Automatic baud rate selection is enabled.                     |       |           |      |      |      |              |             |  |  |  |

|       |                                                                  |       |           |      |      |      |              |             |  |  |  |

## SFR Definition 17.14. LIN0ERR: LIN0 ERROR Register

| R        | R                                                                                                                                                                        | R           | R                  | R          | R            | R            | R             | Reset Value |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------|------------|--------------|--------------|---------------|-------------|--|--|--|

| ĸ        | ĸ                                                                                                                                                                        | ĸ           | SYNCH              | PRTY       | TOUT         | СНК          | BITERR        |             |  |  |  |

|          |                                                                                                                                                                          |             |                    |            |              | -            |               | 00000000    |  |  |  |

| Bit7     | Bit6                                                                                                                                                                     | Bit5        | Bit4               | Bit3       | Bit2         | Bit1         | Bit0          |             |  |  |  |

|          | Address: 0x0A (indi                                                                                                                                                      |             |                    |            |              |              |               |             |  |  |  |

| Dito7 5  | UNUSED. R                                                                                                                                                                | aad - 000k  | $\sim M/rito - dc$ | n't coro   |              |              |               |             |  |  |  |

| Bit4:    | •••==                                                                                                                                                                    | 000         |                    |            | la anlu)     |              |               |             |  |  |  |

| DIL4.    | SYNCH: Synchronization Error Bit (slave mode only).<br>0: No error with the SYNCH FIELD has been detected.                                                               |             |                    |            |              |              |               |             |  |  |  |

|          | 1: Edges of the SYNCH FIELD are outside of the maximum tolerance.                                                                                                        |             |                    |            |              |              |               |             |  |  |  |

| Bit3:    | <b>PRTY</b> : Parity Error Bit ( <b>slave mode only</b> ).                                                                                                               |             |                    |            |              |              |               |             |  |  |  |

| Dito.    | 0: No parity error has been detected.                                                                                                                                    |             |                    |            |              |              |               |             |  |  |  |

|          | 1: A parity error has been detected.                                                                                                                                     |             |                    |            |              |              |               |             |  |  |  |

| Bit2:    | TOUT: Time                                                                                                                                                               |             |                    | •          |              |              |               |             |  |  |  |

| <b>_</b> | 0: A timeout error has not been detected.                                                                                                                                |             |                    |            |              |              |               |             |  |  |  |

|          | 1: A timeout error has been detected. This error is detected whenever one of the fol conditions is met:                                                                  |             |                    |            |              |              |               |             |  |  |  |

|          |                                                                                                                                                                          |             |                    |            |              |              |               |             |  |  |  |

|          | •The master is expecting data from a slave and the slave does not respond.<br>•The slave is expecting data but no data is transmitted on the bus.                        |             |                    |            |              |              |               |             |  |  |  |

|          |                                                                                                                                                                          |             |                    |            |              |              |               |             |  |  |  |

|          | •A frame is not finished within the maximum frame length.                                                                                                                |             |                    |            |              |              |               |             |  |  |  |

|          | <ul> <li>The application does not set the DTACK bit (LIN0CTRL.4) or STOP bit (LIN0CTRL.7) us<br/>end of the reception of the first byte after the identifier.</li> </ul> |             |                    |            |              |              |               |             |  |  |  |

| Bit1:    | CHK: Check                                                                                                                                                               | •           |                    | -          |              |              |               |             |  |  |  |

|          | 0: Checksum error has not been detected.                                                                                                                                 |             |                    |            |              |              |               |             |  |  |  |

|          | 1: Checksun                                                                                                                                                              | n error has | been detect        | ted.       |              |              |               |             |  |  |  |

| Bit0:    | BITERR: Bit                                                                                                                                                              | Transmiss   | ion Error Bit      | t.         |              |              |               |             |  |  |  |

|          | 0: No error in                                                                                                                                                           | n transmiss | sion has bee       | n detected |              |              |               |             |  |  |  |

|          | 1: The bit va                                                                                                                                                            | lue monito  | red during tr      | ansmissior | is different | than the bit | t value sent. |             |  |  |  |

|          |                                                                                                                                                                          |             | -                  |            |              |              |               |             |  |  |  |

|          |                                                                                                                                                                          |             |                    |            |              |              |               |             |  |  |  |

|          |                                                                                                                                                                          |             |                    |            |              |              |               |             |  |  |  |

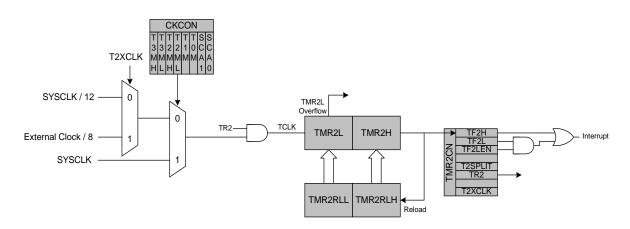

### 18.2. Timer 2

Timer 2 is a 16-bit timer formed by two 8-bit SFRs: TMR2L (low byte) and TMR2H (high byte). Timer 2 may operate in 16-bit auto-reload mode or (split) 8-bit auto-reload mode. The T2SPLIT bit (TMR2CN.3) defines the Timer 2 operation mode. Timer 2 can also be used in Capture Mode to measure the RTC0 clock frequency or the External Oscillator clock frequency.

Timer 2 may be clocked by the system clock, the system clock divided by 12, or the external oscillator source divided by 8. The external oscillator source divided by 8 is synchronized with the system clock.

#### 18.2.1. 16-bit Timer with Auto-Reload

When T2SPLIT (TMR2CN.3) is zero, Timer 2 operates as a 16-bit timer with auto-reload. Timer 2 can be clocked by SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. As the 16-bit timer register increments and overflows from 0xFFFF to 0x0000, the 16-bit value in the Timer 2 reload registers (TMR2RLH and TMR2RLL) is loaded into the Timer 2 register as shown in Figure 18.4, and the Timer 2 High Byte Overflow Flag (TMR2CN.7) is set. If Timer 2 interrupts are enabled (if IE.5 is set), an interrupt will be generated on each Timer 2 overflow. Additionally, if Timer 2 interrupts are enabled and the TF2LEN bit is set (TMR2CN.5), an interrupt will be generated each time the lower 8 bits (TMR2L) overflow from 0xFF to 0x00.

Figure 18.4. Timer 2 16-Bit Mode Block Diagram

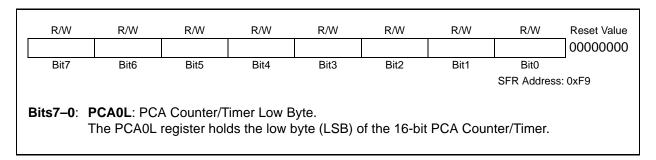

#### SFR Definition 19.4. PCA0L: PCA Counter/Timer Low Byte

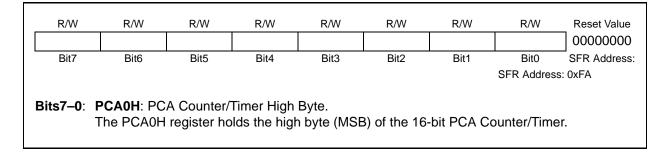

#### SFR Definition 19.5. PCA0H: PCA Counter/Timer High Byte

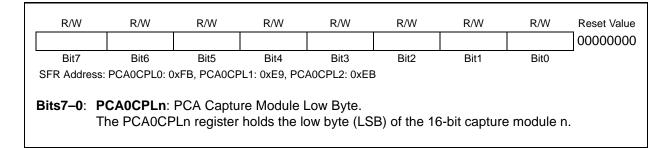

## SFR Definition 19.6. PCA0CPLn: PCA Capture Module Low Byte

## SFR Definition 19.7. PCA0CPHn: PCA Capture Module High Byte

#### 20.8. UART Pins

The location of the pins used by the serial UART interface differs between the silicon revisions of C8051F52x/52xA/F53x/F53xA devices.

On Revision A devices, the TX and RX pins used by the UART interface are mapped to the P0.3 (TX) and P0.4 (RX) pins. Beginning with Revision B devices, the TX and RX pins used by the UART interface are mapped to the P0.4 (TX) and P0.5 (RX) pins.

**Important Note:** On Revision B and newer devices, the UART pins must be skipped if the UART is enabled in order for peripherals to appear on port pins beyond the UART on the crossbar. For example, with the SPI and UART enabled on the crossbar with the SPI on P1.0-P1.3, the UART pins must be skipped using P0SKIP for the SPI pins to appear correctly.

#### 20.9. LIN

The LIN peripheral behavior differs between the silicon revisions of C8051F52x/52xA/F53x/F53xA devices. The differences are:

#### 20.9.1. Stop Bit Check

On Revision A devices, the stop bits of the fields in the LIN frame are not checked and no error is generated if the stop bits could not be sent or received correctly. On Revision B and Revision C devices, the stop bits are checked, and an error will be generated if the stop bit was not sent or received correctly.

#### 20.9.2. Synch Break and Synch Field Length Check

On Revision A devices, the check of sync field length versus sync break length is incorrect. On Revision B and Revision C devices, the sync break length must be larger than 10 bit times (of the measured bit time) to enable the synchronization.

#### Disclaimer