# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                            |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | SPI, UART/USART                                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                |

| Number of I/O              | 16                                                                |

| Program Memory Size        | 4KB (4K x 8)                                                      |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 256 x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.25V                                                        |

| Data Converters            | A/D 16x12b                                                        |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                   |

| Supplier Device Package    | 20-TSSOP                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f534-c-itr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| SFR Definition 19.2. PCA0MD: PCA Mode                            | 207 |

|------------------------------------------------------------------|-----|

| SFR Definition 19.3. PCA0CPMn: PCA Capture/Compare Mode          | 208 |

| SFR Definition 19.4. PCA0L: PCA Counter/Timer Low Byte           | 209 |

| SFR Definition 19.5. PCA0H: PCA Counter/Timer High Byte          | 209 |

| SFR Definition 19.6. PCA0CPLn: PCA Capture Module Low Byte       | 209 |

| SFR Definition 19.7. PCA0CPHn: PCA Capture Module High Byte      | 209 |

| C2 Register Definition 21.1. C2ADD: C2 Address                   | 214 |

| C2 Register Definition 21.2. DEVICEID: C2 Device ID              | 214 |

| C2 Register Definition 21.3. REVID: C2 Revision ID               |     |

| C2 Register Definition 21.4. FPCTL: C2 Flash Programming Control | 215 |

| C2 Register Definition 21.5. FPDAT: C2 Flash Programming Data    | 215 |

|                                                                  |     |

| Name          | Pin Numbers       |          | Туре             | Description                                                |

|---------------|-------------------|----------|------------------|------------------------------------------------------------|

|               | ʻF53xA<br>ʻF53x-C |          |                  |                                                            |

| P0.4/TX*      | 19                |          | D I/O or<br>A In | Port 0.4. See Port I/O Section for a complete description. |

| P0.4/RX*      | —                 | 19       | D I/O or<br>A In | Port 0.4. See Port I/O Section for a complete description. |

| P0.3          | 20                | _        | D I/O or<br>A In | Port 0.3. See Port I/O Section for a complete description. |

| P0.3/TX*      |                   | 20       | D I/O or<br>A In | Port 0.3. See Port I/O Section for a complete description. |

| *Note: Please | refer to S        | ection " | 20. Device       | Specific Behavior" on page 210.                            |

#### Table 3.4. Pin Definitions for the C8051F53x and C805153xA (TSSOP 20) (Continued)

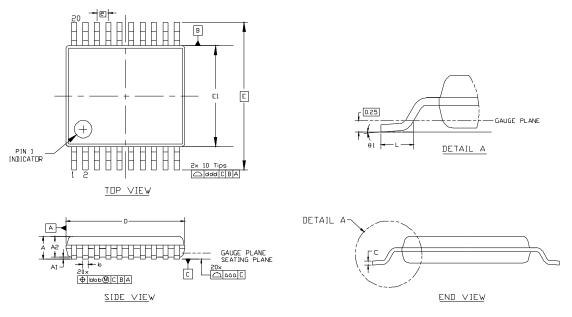

#### Figure 3.5. TSSOP-20 Package Diagram

| Symbol | Min  | Nom       | Мах  |

|--------|------|-----------|------|

| A      |      |           | 1.20 |

| A1     | 0.05 |           | 0.15 |

| A2     | 0.80 | 1.00      | 1.05 |

| b      | 0.19 |           | 0.30 |

| С      | 0.09 | —         | 0.20 |

| D      | 6.40 | 6.50      | 6.60 |

| е      |      | 0.65 BSC. |      |

| E      |      | 6.40 BSC. |      |

| E1     | 4.30 | 4.40      | 4.50 |

| L      | 0.45 | 0.60      | 0.75 |

| θ1     | 0°   | —         | 8°   |

| aaa    |      | 0.10      |      |

| bbb    |      | 0.10      |      |

| ddd    |      | 0.20      |      |

| otes:  |      |           |      |

#### Table 3.5. TSSOP-20 Package Diagram Dimensions

1. All dimensions shown are in millimeters (mm).

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This drawing conforms to JEDEC outline MO-153, variation AC.

**4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

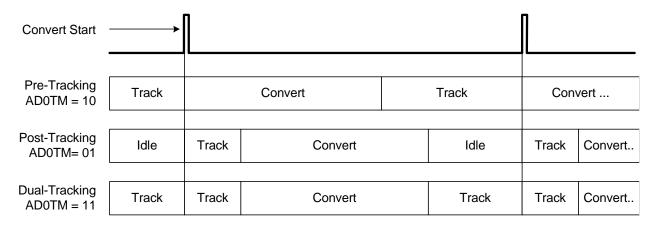

Post-Tracking Mode is selected when AD0TM is set to 01b. A programmable tracking time based on AD0TK is started immediately following the convert start signal. Conversions are started after the programmed tracking time ends. After a conversion is complete, ADC0 does not track the input. Rather, the sampling capacitor remains disconnected from the input making the input pin high-impedance until the next convert start signal.

Dual-Tracking Mode is selected when AD0TM is set to 11b. A programmable tracking time based on AD0TK is started immediately following the convert start signal. Conversions are started after the programmed tracking time ends. After a conversion is complete, ADC0 tracks continuously until the next conversion is started.

Depending on the output connected to the ADC input, additional tracking time, more than is specified in Table 2.3 on page 28, may be required after changing MUX settings. See the settling time requirements described in Section "4.3.6. Settling Time Requirements" on page 60.

#### 4.3.3. Timing

ADC0 has a maximum conversion speed specified in Table 2.3 on page 28. ADC0 is clocked from the ADC0 Subsystem Clock (FCLK). The source of FCLK is selected based on the BURSTEN bit. When BURSTEN is logic 0, FCLK is derived from the current system clock. When BURSTEN is logic 1, FCLK is derived from the Burst Mode Oscillator, which is an independent clock source whose maximum frequency is specified in Table 2.3 on page 28.

When ADC0 is performing a conversion, it requires a clock source that is typically slower than FCLK. The ADC0 SAR conversion clock (SAR clock) is a divided version of FCLK. The divide ratio can be configured using the AD0SC bits in the ADC0CF register. The maximum SAR clock frequency is listed in Table 2.3 on page 28.

ADC0 can be in one of three states at any given time: tracking, converting, or idle. Tracking time depends on the tracking mode selected. For Pre-Tracking Mode, tracking is managed by software and ADC0 starts conversions immediately following the convert start signal. For Post-Tracking and Dual-Tracking Modes, the tracking time after the convert start signal is equal to the value determined by the AD0TK bits plus 2 FCLK cycles. Tracking is immediately followed by a conversion. The ADC0 conversion time is always 13 SAR clock cycles plus an additional 2 FCLK cycles to start and complete a conversion. Figure 4.4 shows timing diagrams for a conversion in Pre-Tracking Mode and tracking plus conversion in Post-Tracking or Dual-Tracking Mode. In this example, repeat count is set to one.

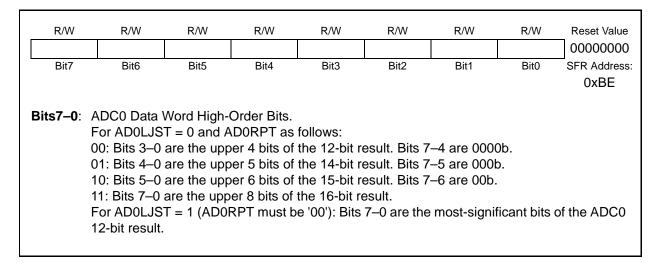

### SFR Definition 4.6. ADC0H: ADC0 Data Word MSB

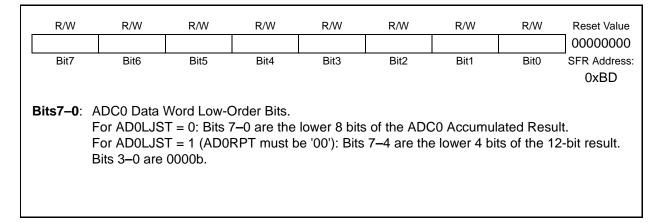

#### SFR Definition 4.7. ADC0L: ADC0 Data Word LSB

## 8. CIP-51 Microcontroller

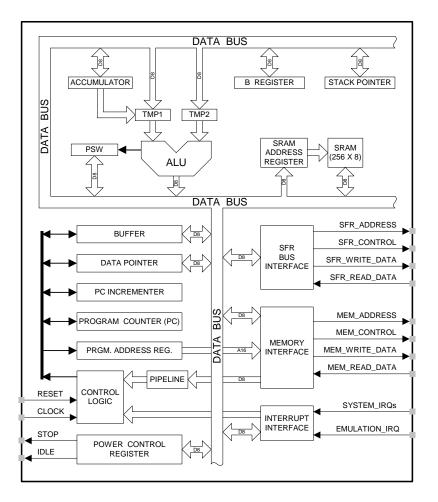

The MCU system controller core is the CIP-51 microcontroller. The CIP-51 is fully compatible with the MCS-51<sup>™</sup> instruction set. Standard 803x/805x assemblers and compilers can be used to develop software. The C8051F52x/F52xA/F53x/F53xA family has a superset of all the peripherals included with a standard 8051. See Section "1. System Overview" on page 13 for more information about the available peripherals. The CIP-51 includes on-chip debug hardware which interfaces directly with the analog and digital subsystems, providing a complete data acquisition or control-system solution in a single integrated circuit.

The CIP-51 Microcontroller core implements the standard 8051 organization and peripherals as well as additional custom peripherals and functions to extend its capability (see Figure 8.1 for a block diagram). The CIP-51 core includes the following features:

- Fully Compatible with MCS-51 Instruction Set

- 25 MIPS Peak Throughput

- 256 Bytes of Internal RAM

- Extended Interrupt Handler

- Reset Input

- Power Management Modes

- Integrated Debug Logic

- Program and Data Memory Security

Figure 8.1. CIP-51 Block Diagram

#### Performance

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute, and usually have a maximum system clock of 12 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with no instructions taking more than eight system clock cycles.

With the CIP-51's system clock running at 25 MHz, it has a peak throughput of 25 MIPS. The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute      | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

|------------------------|----|----|-----|----|-----|---|-----|---|---|

| Number of Instructions | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

#### **Programming and Debugging Support**

In-system programming of the Flash program memory and communication with on-chip debug support logic is accomplished via the Silicon Labs 2-Wire (C2) interface. Note that the re-programmable Flash can also be read and written a single byte at a time by the application software using the MOVC and MOVX instructions. This feature allows program memory to be used for non-volatile data storage as well as updating program code under software control.

The on-chip debug support logic facilitates full speed in-circuit debugging, allowing the setting of hardware breakpoints, starting, stopping and single stepping through program execution (including interrupt service routines), examination of the program's call stack, and reading/writing the contents of registers and memory. This method of on-chip debugging is completely non-intrusive, requiring no RAM, Stack, timers, or other on-chip resources.

The CIP-51 is supported by development tools from Silicon Laboratories, Inc. and third party vendors. Silicon Laboratories provides an integrated development environment (IDE) including editor, evaluation compiler, assembler, debugger and programmer. The IDE's debugger and programmer interface to the CIP-51 via the on-chip debug logic to provide fast and efficient in-system device programming and debugging. Third party macro assemblers and C compilers are also available.

#### 8.1. Instruction Set

The instruction set of the CIP-51 System Controller is fully compatible with the standard MCS-51<sup>™</sup> instruction set. Standard 8051 development tools can be used to develop software for the CIP-51. All CIP-51 instructions are the binary and functional equivalent of their MCS-51<sup>™</sup> counterparts, including opcodes, addressing modes and effect on PSW flags. However, instruction timing is different than that of the standard 8051.

#### 8.1.1. Instruction and CPU Timing

In many 8051 implementations, a distinction is made between machine cycles and clock cycles, with machine cycles varying from 2 to 12 clock cycles in length. However, the CIP-51 implementation is based solely on clock cycle timing. All instruction timings are specified in terms of clock cycles.

Due to the pipelined architecture of the CIP-51, most instructions execute in the same number of clock cycles as there are program bytes in the instruction. Conditional branch instructions take one less clock cycle to complete when the branch is not taken as opposed to when the branch is taken. Table 8.1 is the CIP-51 Instruction Set Summary, which includes the mnemonic, number of bytes, and number of clock cycles for each instruction.

### SFR Definition 10.4. EIP1: Extended Interrupt Priority 1

| R/W   | R/W                            | R/W           | R/W           | R/W           | R/W            | R/W          | R/W          | Reset Value |

|-------|--------------------------------|---------------|---------------|---------------|----------------|--------------|--------------|-------------|

| PMAT  | PREG0                          | PLIN          | PCPR          | PCPF          | PPAC0          | PREG0        | PWADC0       | 0000000     |

| Bit7  | Bit6                           | Bit5          | Bit4          | Bit3          | Bit2           | Bit1         | Bit0         |             |

|       |                                |               |               |               |                |              | SFR Address: | 0xF6        |

| Bit7: | PMAT. Port M                   |               |               |               |                |              |              |             |

|       | This bit sets                  |               |               |               | rupt.          |              |              |             |

|       | 0: Port Match                  |               |               |               |                |              |              |             |

| Bit6: | 1: Port Match                  |               | • •           |               |                |              |              |             |

| 5110  | PREG0: Volt                    | 0 0           |               |               |                |              |              |             |

|       | This bit sets<br>0: Voltage Re |               |               | • •           | •              |              |              |             |

|       | 1: Voltage Re                  | •             | •             | •             |                |              |              |             |

| Bit5: | PLIN: LIN Int                  | •             | •             | • •           | ty level.      |              |              |             |

| Bito. | This bit sets                  | •             |               |               |                |              |              |             |

|       | 0: LIN interru                 |               |               |               |                |              |              |             |

|       | 1: LIN interru                 |               |               |               |                |              |              |             |

| Bit4: | PCPR: Com                      |               |               |               | ritv Control.  |              |              |             |

|       | This bit sets                  |               |               |               |                |              |              |             |

|       | 0: Comparate                   |               |               |               |                |              |              |             |

|       | 1: Comparate                   | or interrupt  | set to high   | priority leve | el.            |              |              |             |

| Bit3: | PCPF: Comp                     | parator falli | ng Edge Int   | errupt Prior  | ity Control.   |              |              |             |

|       | This bit sets                  | the priority  | of the Fallin | ng Edge Co    | mparator in    | terrupt.     |              |             |

|       | 0: Comparate                   |               |               |               |                |              |              |             |

|       | 1: Comparate                   |               |               |               |                |              |              |             |

| Bit2: | PPAC0: Prog                    |               |               | • • •         | Interrupt P    | riority Cont | rol.         |             |

|       | This bit sets                  |               |               |               |                |              |              |             |

|       | 0: PCA0 inte                   |               |               |               |                |              |              |             |

|       | 1: PCA0 inte                   |               |               |               |                |              |              |             |

| Bit1: | PREGO: ADO                     |               |               |               |                |              |              |             |

|       | This bit sets                  |               |               |               | •              | •            |              |             |

|       | 0: ADC0 Cor                    |               |               |               |                |              |              |             |

| D:40. | 1: ADC0 Cor                    |               |               | •             | • • •          |              |              |             |

| Bit0: | PWADC0: A                      |               |               |               |                |              |              |             |

|       | This bit sets                  |               |               |               |                |              |              |             |

|       | 0: ADC0 Win                    |               |               | •             |                |              |              |             |

|       | 1: ADC0 Win                    | noom comp     | ansoninter    | rupt set to   | ingri priority | ievei.       |              |             |

ramp or during a brownout condition even when  $V_{DD}$  is below the specified minimum of 2.0 V. There are two possible ways to handle this transitional period as described below:

If using the on-chip regulator (REG0) at the 2.6 V setting (default), it is recommended that user software set the VDDMON0 threshold to its high setting ( $V_{RST-HIGH}$ ) as soon as possible after reset by setting the VDMLVL bit to 1 in SFR Definition 11.1 (VDDMON). In this typical configuration, no external hardware or additional software routines are necessary to monitor the  $V_{DD}$  level.

**Note:** Please refer to Section "20.5. VDD Monitor (VDDMON0) High Threshold Setting" on page 212 for important notes related to the VDD Monitor high threshold setting in older silicon revisions A and B.

If using the on-chip regulator (REG0) at the 2.1 V setting or if directly driving  $V_{DD}$  with REG0 disabled, the user system (software/hardware) should monitor  $V_{DD}$  at power-on and also during device operation. The two key parameters that can be affected when  $V_{DD} < 2.0$  V are: internal oscillator frequency (Table 2.11 on page 34) and minimum ADC tracking time (Table 2.3 on page 28).

#### SFR Definition 11.1. VDDMON: V<sub>DD</sub> Monitor Control

| R/W           | R                          | R/W                     | R                      | R               | R                       | R                          | R                    | Reset Value       |  |  |  |

|---------------|----------------------------|-------------------------|------------------------|-----------------|-------------------------|----------------------------|----------------------|-------------------|--|--|--|

| VDMEN         | VDDSTAT                    | VDMLVL                  | VDM1EN                 | Reserved        | Reserved                | Reserved                   | Reserved             | 1v010000          |  |  |  |

| Bit7          | Bit6                       | Bit5                    | Bit4                   | Bit3            | Bit2                    | Bit1                       | Bit0                 |                   |  |  |  |

|               |                            | SFR Address: 0xFF       |                        |                 |                         |                            |                      |                   |  |  |  |

|               |                            |                         |                        |                 |                         |                            |                      |                   |  |  |  |

| Bit7:         | VDMEN: V <sub>DI</sub>     | -                       |                        |                 | .,                      |                            |                      |                   |  |  |  |

|               | This bit turns             |                         |                        |                 |                         |                            |                      |                   |  |  |  |

|               | resets until it            |                         |                        |                 |                         |                            |                      |                   |  |  |  |

|               | The V <sub>DD</sub> Mo     |                         |                        |                 |                         |                            |                      |                   |  |  |  |

|               | ing the V <sub>DD</sub>    |                         |                        |                 |                         |                            |                      | a system          |  |  |  |

|               | reset. See T               |                         |                        | r the minim     | um V <sub>DD</sub> Mo   | nitor turn-o               | n time.              |                   |  |  |  |

|               | 0: V <sub>DD</sub> Monit   |                         |                        |                 |                         |                            |                      |                   |  |  |  |

|               | 1: V <sub>DD</sub> Monit   |                         | (default).             |                 |                         |                            |                      |                   |  |  |  |

| Bit6:         | VDDSTAT: V                 | 66                      |                        |                 |                         |                            |                      |                   |  |  |  |

|               | This bit indic             |                         | •                      |                 |                         | •                          | t).                  |                   |  |  |  |

|               | 0: V <sub>DD</sub> is at o |                         |                        |                 |                         | nold.                      |                      |                   |  |  |  |

|               | 1: V <sub>DD</sub> is abo  | ove the V <sub>DE</sub> | Monitor (V             | /DDMON0)        | Threshold.              |                            |                      |                   |  |  |  |

| Bit5:         | VDMLVL: V                  | <sub>DD</sub> Level Se  | lect.                  |                 |                         |                            |                      |                   |  |  |  |

|               | 0: V <sub>DD</sub> Monit   |                         |                        |                 |                         |                            |                      |                   |  |  |  |

|               | 1: V <sub>DD</sub> Monit   | tor (VDDM0              | ON0) Thres             | hold is set to  | o V <sub>RST-HIGH</sub> | <sub>I</sub> . This settir | ng is <b>require</b> | <b>∍d</b> for any |  |  |  |

|               | system that i              | includes co             | de that write          | es to and/or    | erases Fla              | sh.                        |                      |                   |  |  |  |

| Bit4:         | VDM1EN <sup>*</sup> : L    | evel-sensit             | ive V <sub>DD</sub> Mo | nitor Enable    | e (VDDMON               | <b>I</b> 1).               |                      |                   |  |  |  |

|               | This bit turns             | s the V <sub>DD</sub> m | ionitor circu          | it on/off. If t | urned on, it            | is also sele               | ected as a re        | eset              |  |  |  |

|               | source, and                | can genera              | te a system            | n reset.        |                         |                            |                      |                   |  |  |  |

|               | 0: Level-sen               |                         |                        |                 |                         |                            |                      |                   |  |  |  |

|               | 1: Level-sen               |                         |                        | •               | ,                       |                            |                      |                   |  |  |  |

| Bits3–0:      | RESERVED                   | . Read = Va             | ariable. Writ          | e = don't ca    | ire.                    |                            |                      |                   |  |  |  |

| *Note: Availa | able only on the           | e C8051F52              | <-C/F53x-C c           | levices         |                         |                            |                      |                   |  |  |  |

5. Add address bounds checking to the routines that write or erase Flash memory to ensure that a routine called with an illegal address does not result in modification of the Flash.

#### 12.2.3. System Clock

- 1. If operating from an external crystal, be advised that crystal performance is susceptible to electrical interference and is sensitive to layout and to changes in temperature. If the system is operating in an electrically noisy environment, use the internal oscillator or use an external CMOS clock.

- 2. If operating from the external oscillator, switch to the internal oscillator during Flash write or erase operations. The external oscillator can continue to run, and the CPU can switch back to the external oscillator after the Flash operation has completed.

Additional Flash recommendations and example code can be found in application note "AN201: Writing to Flash from Firmware," available from the Silicon Laboratories website.

### SFR Definition 12.1. PSCTL: Program Store R/W Control

| R                 | R                                                                                                     | R                                                        | R                                                  | R                                                       | R            | R/W                                 | R/W                    | Reset Value  |

|-------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------|--------------|-------------------------------------|------------------------|--------------|

| —                 | —                                                                                                     | —                                                        | —                                                  | —                                                       | _            | PSEE                                | PSWE                   | 00000000     |

| Bit7              | Bit6                                                                                                  | Bit5                                                     | Bit4                                               | Bit3                                                    | Bit2         | Bit1                                | Bit0                   |              |

|                   |                                                                                                       |                                                          |                                                    |                                                         |              |                                     | SFR Address            | s: 0x8F      |

| Bits7–2:<br>Bit1: | UNUSED: R<br>PSEE: Progr<br>Setting this b<br>to be erased                                            | am Store Ei<br>bit (in combir                            | rase Enabl<br>nation with                          | e<br>PSWE) allo                                         | ws an entir  |                                     |                        |              |

|                   | Flash memo<br>tion addresse<br>0: Flash prog<br>1: Flash prog                                         | ry using the<br>ed by the Mo<br>gram memol<br>gram memol | MOVX ins<br>OVX instru<br>ry erasure<br>ry erasure | truction will<br>iction. The v<br>disabled.<br>enabled. | erase the e  | entire page                         | that contair           | ns the loca- |

| Bit0:             | <b>PSWE</b> : Prog<br>Setting this b<br>write instruct<br>0: Writes to F<br>1: Writes to F<br>memory. | bit allows wri<br>ion. The Fla<br>Flash progra           | iting a byte<br>ish locatior<br>am memory          | e of data to th<br>n should be<br>y disabled.           | erased befo  | ore writing o                       | data.                  |              |

| Note: See         | Section "12.1.<br>requirements                                                                        |                                                          | -                                                  | -                                                       | page 113 for | <sup>-</sup> minimum V <sub>l</sub> | <sub>DD</sub> and temp | erature      |

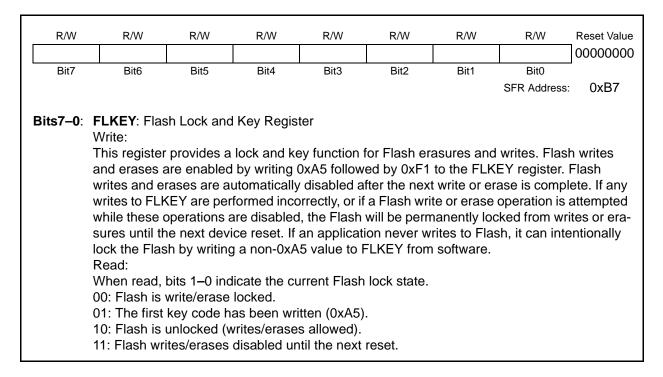

### SFR Definition 12.2. FLKEY: Flash Lock and Key

| SF Signals DFN10 | ΈF       |   | XTAL1 | XTAL2 |   | CNVSTR             |

|------------------|----------|---|-------|-------|---|--------------------|

| PIN I/O          | <u>ч</u> | 1 | 2     | 3     | 4 | <del>້ວ</del><br>5 |

| TX0              |          |   | _     |       |   |                    |

| RX0              |          |   |       |       |   |                    |

| ТХО              | -        |   |       |       |   |                    |

| RX0              |          |   |       |       |   |                    |

| SCK              |          |   |       |       |   |                    |

| MISO             |          |   | l     |       |   |                    |

| MOSI             |          |   |       |       |   |                    |

| NSS*             |          |   |       |       |   |                    |

| LIN-TX           |          |   |       |       |   |                    |

| LIN_RX           |          |   | l     |       |   |                    |

| CP0              |          |   |       |       |   |                    |

| CP0A             |          |   |       |       |   |                    |

| /SYSCLK          |          |   |       |       |   |                    |

| CEX0             |          |   |       |       |   |                    |

| CEX1             |          |   |       |       |   |                    |

| CEX2             |          |   |       |       |   |                    |

| ECI              |          |   |       |       |   |                    |

| Т0               |          |   |       |       |   |                    |

| T1               |          |   |       |       |   |                    |

|                  | 0        | 0 | 0     | 0     | 0 | 0                  |

Note: 4-Wire SPI Only.

#### Figure 13.5. Crossbar Priority Decoder with No Pins Skipped (DFN 10)

**Important Note:** The SPI can be operated in either 3-wire or 4-wire modes, depending on the state of the NSSMD1–NSSMD0 bits in register SPI0CN. According to the SPI mode, the NSS signal may or may not be routed to a Port pin.

### 13.2. Port I/O Initialization

Port I/O initialization consists of the following steps:

- 1. Select the input mode (analog or digital) for all Port pins, using the Port Input Mode register (PnMDIN).

- 2. Select the output mode (open-drain or push-pull) for all Port pins, using the Port Output Mode register (PnMDOUT).

- 3. Select any pins to be skipped by the I/O Crossbar using the Port Skip registers (PnSKIP).

- 4. Assign Port pins to desired peripherals using the XBRn registers.

- 5. Enable the Crossbar (XBARE = 1).

All Port pins must be configured as either analog or digital inputs. Any pins to be used as Comparator or ADC inputs should be configured as an analog inputs. When a pin is configured as an analog input, its weak pullup, digital driver, and digital receiver are disabled. This process saves power and reduces noise on the analog input. Pins configured as digital inputs may still be used by analog peripherals; however, this practice is not recommended.

Additionally, all analog input pins should be configured to be skipped by the Crossbar (accomplished by setting the associated bits in PnSKIP). Port input mode is set in the PnMDIN register, where a 1 indicates a digital input, and a 0 indicates an analog input. All pins default to digital inputs on reset. See SFR Definition 13.4 for the PnMDIN register details.

Important Note: Port 0 and Port 1 pins are 5.25 V tolerant across the operating range of V<sub>REGIN</sub>.

The output driver characteristics of the I/O pins are defined using the Port Output Mode registers (PnMD-OUT). Each Port Output driver can be configured as either open drain or push-pull. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. When the WEAKPUD bit in XBR1 is 0, a weak pullup is enabled for all Port I/O configured as open-drain. WEAKPUD does not affect the push-pull Port I/O. Furthermore, the weak pullup is turned off on an output that is driving a 0 and for pins configured for analog input mode to avoid unnecessary power dissipation.

Registers XBR0 and XBR1 must be loaded with the appropriate values to select the digital I/O functions required by the design. Setting the XBARE bit in XBR1 to 1 enables the Crossbar. Until the Crossbar is enabled, the external pins remain as standard Port I/O (in input mode), regardless of the XBRn Register settings. For given XBRn Register settings, one can determine the I/O pin-out using the Priority Decode Table.

The Crossbar must be enabled to use Port pins as standard Port I/O in output mode. **Port output drivers** are disabled while the Crossbar is disabled.

### SFR Definition 14.4. OSCXCN: External Oscillator Control

| R        | R/W                                                                                        | R/W                                                                                                | R/W                                                         | R/W                  | R/W                  | R/W      | R/W             | Reset Value |  |  |  |  |

|----------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------|----------------------|----------|-----------------|-------------|--|--|--|--|

| XTLVLD   |                                                                                            | XOSCMD1 X                                                                                          |                                                             | eserved              | XFCN2                | XFCN1    | XFCN0           | 00000000    |  |  |  |  |

| Bit7     | Bit6                                                                                       | Bit5                                                                                               | Bit4                                                        | Bit3                 | Bit2                 | Bit1     | Bit0            |             |  |  |  |  |

|          |                                                                                            |                                                                                                    |                                                             |                      |                      |          | SFR Address     | :: 0xB1     |  |  |  |  |

| Bit7:    | 0: Crystal O<br>1: Crystal O                                                               | ystal Oscillat<br>scillator is un<br>scillator is rur                                              | used or not y<br>nning and sta                              | /et stable.<br>able. |                      | (OSCMD : | = 11x.)         |             |  |  |  |  |

| Bits6–4: | <b>XOSCMD2–0</b> : External Oscillator Mode Bits.<br>00x: External Oscillator circuit off. |                                                                                                    |                                                             |                      |                      |          |                 |             |  |  |  |  |

| B:42     | 010: Externa<br>011: Externa<br>100: RC Ose<br>101: Capaci<br>110: Crystal<br>111: Crystal | al CMOS Cloo<br>al CMOS Cloo<br>cillator Mode.<br>tor Oscillator<br>Oscillator Mo<br>Oscillator Mo | ck Mode.<br>ck Mode with<br>Mode.<br>ode.<br>ode with divid | de by 2 sta          | -                    |          |                 |             |  |  |  |  |

| Bita2    |                                                                                            | P. Read = 0b;                                                                                      |                                                             |                      | al Dita              |          |                 |             |  |  |  |  |

| Bits2–0: |                                                                                            | External Oscil<br>e table below                                                                    | •                                                           | ncy Contr            | ol Bits.             |          |                 |             |  |  |  |  |

|          | XFCN                                                                                       | Crystal (XC                                                                                        | SCMD = 11                                                   | x) RC                | (XOSCMD              | = 10x)   | C (XOSCM        | /ID = 10x)  |  |  |  |  |

|          | 000                                                                                        | f ≤ 2                                                                                              | 20 kHz                                                      |                      | f ≤ 25 kH            | lz       | K Factor = 0.87 |             |  |  |  |  |

|          | 001                                                                                        | 20 kHz <                                                                                           | < f ≤ 58 kHz                                                | 25                   | kHz < f ≤ 5          | 50 kHz   | K Factor = 2.6  |             |  |  |  |  |

|          | 010                                                                                        | 58 kHz <                                                                                           | $f \le 155 \text{ kHz}$                                     | 50 I                 | $Hz < f \le 1$       | 00 kHz   | K Factor = 7.7  |             |  |  |  |  |

|          | 011                                                                                        | 155 kHz <                                                                                          | < f ≤ 415 kHz                                               | 100                  | kHz < f ≤ 2          | 200 kHz  | K Factor = 22   |             |  |  |  |  |

|          | 100                                                                                        | 415 kHz <                                                                                          | : f ≤ 1.1 MHz                                               | 200                  | kHz < f ≤ 4          | l00 kHz  | K Facto         | or = 65     |  |  |  |  |

|          | 101                                                                                        | 1.1 MHz <                                                                                          | < f ≤ 3.1 MHz                                               | 400                  | $kHz < f \le 8$      | 800 kHz  | K Facto         | r = 180     |  |  |  |  |

|          | 110                                                                                        | 3.1 MHz <                                                                                          | < f ≤ 8.2 MHz                                               | 800                  | $kHz < f \le 1$      | .6 MHz   | K Factor = 664  |             |  |  |  |  |

|          | 111                                                                                        | 8.2 MHz «                                                                                          | < f ≤ 25 MHz                                                | 1.6                  | ИHz < f ≤ З          | 3.2 MHz  | K Factor        | = 1590      |  |  |  |  |

| -        | Choose XFC<br>(Circuit from                                                                | from Figure 1<br>CN value to m<br>n Figure 14.1,                                                   | natch crystal<br>Option 2; X                                | or resona<br>OSCMD = | tor freque<br>= 10x) | ncy.     |                 |             |  |  |  |  |

|          | _                                                                                          | CN value to m                                                                                      | •                                                           | ncy range            | :                    |          |                 |             |  |  |  |  |

|          | •                                                                                          | )/(R x C), w                                                                                       |                                                             |                      |                      |          |                 |             |  |  |  |  |

|          | •                                                                                          | y of clock in N<br>or value in pF                                                                  |                                                             |                      |                      |          |                 |             |  |  |  |  |

|          | •                                                                                          | esistor value                                                                                      |                                                             |                      |                      |          |                 |             |  |  |  |  |

| C Mode ( | Circuit from I                                                                             | -igure 14.1, C                                                                                     | Option 3; XO                                                |                      | ,                    |          |                 |             |  |  |  |  |

|          |                                                                                            | actor (KF) for                                                                                     |                                                             | on freque            | ncy desire           | d:       |                 |             |  |  |  |  |

|          | -                                                                                          | x V <sub>DD</sub> ), where<br>y of clock in N                                                      |                                                             |                      |                      |          |                 |             |  |  |  |  |

|          |                                                                                            | or value the X                                                                                     |                                                             | ρF                   |                      |          |                 |             |  |  |  |  |

|          | •                                                                                          | r Supply on N                                                                                      | •                                                           | F                    |                      |          |                 |             |  |  |  |  |

|          |                                                                                            |                                                                                                    |                                                             |                      |                      |          |                 |             |  |  |  |  |

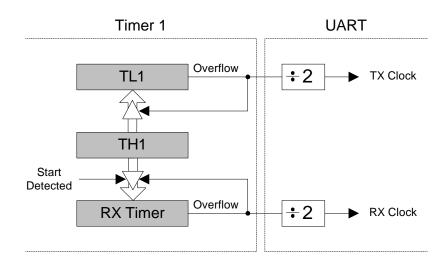

### 15.1. Enhanced Baud Rate Generation

The UART0 baud rate is generated by Timer 1 in 8-bit auto-reload mode. The TX clock is generated by TL1; the RX clock is generated by a copy of TL1 (shown as RX Timer in Figure 15.2), which is not useraccessible. Both TX and RX Timer overflows are divided by two to generate the TX and RX baud rates. The RX Timer runs when Timer 1 is enabled, and uses the same reload value (TH1). However, an RX Timer reload is forced when a START condition is detected on the RX pin. This allows a receive to begin any time a START is detected, independent of the TX Timer state.

Figure 15.2. UART0 Baud Rate Logic

Timer 1 should be configured for Mode 2, 8-bit auto-reload (see Section "18.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload" on page 184). The Timer 1 reload value should be set so that overflows will occur at two times the desired UART baud rate frequency. Note that Timer 1 may be clocked by one of six sources: SYSCLK, SYSCLK / 4, SYSCLK / 12, SYSCLK / 48, the external oscillator clock / 8, or an external input T1. The UART0 baud rate is determined by Equation 15.1-A and Equation 15.1-B.

A) UartBaudRate =

$$\frac{1}{2} \times T1_Overflow_Rate$$

B) T1\_Overflow\_Rate =  $\frac{T1_{CLK}}{256 - TH1}$

#### Equation 15.1. UART0 Baud Rate

Where  $T1_{CLK}$  is the frequency of the clock supplied to Timer 1, and T1H is the high byte of Timer 1 (8-bit auto-reload mode reload value). Timer 1 clock frequency is selected as described in Section "18. Timers" on page 182. A quick reference for typical baud rates and system clock frequencies is given in Table 15.1. Note that the internal oscillator may still generate the system clock when the external oscillator is driving Timer 1.

### SFR Definition 17.14. LIN0ERR: LIN0 ERROR Register

| R       | R                                                                                                          | R           | R                              | R             | R             | R            | R             | Reset Value    |  |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------|-------------|--------------------------------|---------------|---------------|--------------|---------------|----------------|--|--|--|--|--|

| K       |                                                                                                            | n           | SYNCH                          | PRTY          | TOUT          | СНК          | BITERR        |                |  |  |  |  |  |

| D'17    | Dite                                                                                                       | Dite        | Bit4                           | Bit3          | Bit2          | Bit1         |               | 0000000        |  |  |  |  |  |

| Bit7    | Bit6                                                                                                       | Bit5        | Bit0                           |               |               |              |               |                |  |  |  |  |  |

|         | Address: 0x0A (indire                                                                                      |             |                                |               |               |              |               |                |  |  |  |  |  |

| Rite7_5 | UNUSED. R                                                                                                  | aad - 000k  | o. Write − de                  | n't care      |               |              |               |                |  |  |  |  |  |

| Bit4:   | •••••                                                                                                      | 000         |                                |               | le only)      |              |               |                |  |  |  |  |  |

| DIL4.   | SYNCH: Synchronization Error Bit (slave mode only).<br>0: No error with the SYNCH FIELD has been detected. |             |                                |               |               |              |               |                |  |  |  |  |  |

|         | 1: Edges of t                                                                                              |             | -                              |               |               | m tolerance  | <b>`</b>      |                |  |  |  |  |  |

| Bit3:   | PRTY: Parity                                                                                               |             |                                |               |               |              |               |                |  |  |  |  |  |

| Bito.   | 0: No parity                                                                                               |             |                                |               |               |              |               |                |  |  |  |  |  |

|         | 1: A parity er                                                                                             |             |                                |               |               |              |               |                |  |  |  |  |  |

| Bit2:   | TOUT: Time                                                                                                 |             |                                | •             |               |              |               |                |  |  |  |  |  |

|         | 0: A timeout                                                                                               | error has r | not been det                   | ected.        |               |              |               |                |  |  |  |  |  |

|         | 1: A timeout                                                                                               | error has b | been detecte                   | ed. This erro | or is detecte | d wheneve    | r one of the  | followina      |  |  |  |  |  |

|         | conditions is                                                                                              |             |                                |               |               |              |               | 5              |  |  |  |  |  |

|         | •The master                                                                                                | is expectir | ng data from                   | a slave an    | d the slave   | does not re  | spond.        |                |  |  |  |  |  |

|         | •The slave is                                                                                              | •           | -                              |               |               |              | •             |                |  |  |  |  |  |

|         | •A frame is r                                                                                              |             |                                |               |               |              |               |                |  |  |  |  |  |

|         | •The applica<br>end of th                                                                                  |             | ot set the D<br>n of the first |               |               |              | it (LIN0CTR   | L.7) until the |  |  |  |  |  |

| Bit1:   | CHK: Check                                                                                                 | •           |                                |               |               |              |               |                |  |  |  |  |  |

|         | 0: Checksun                                                                                                | n error has | not been de                    | etected.      |               |              |               |                |  |  |  |  |  |

|         | 1: Checksun                                                                                                | n error has | been detect                    | ted.          |               |              |               |                |  |  |  |  |  |

| Bit0:   | BITERR: Bit                                                                                                | Transmiss   | ion Error Bit                  | t.            |               |              |               |                |  |  |  |  |  |

|         | 0: No error ir                                                                                             | n transmiss | sion has bee                   | n detected    |               |              |               |                |  |  |  |  |  |

|         | 1: The bit va                                                                                              | lue monito  | red during tr                  | ansmissior    | is different  | than the bit | t value sent. |                |  |  |  |  |  |

|         |                                                                                                            |             | -                              |               |               |              |               |                |  |  |  |  |  |

|         |                                                                                                            |             |                                |               |               |              |               |                |  |  |  |  |  |

|         |                                                                                                            |             |                                |               |               |              |               |                |  |  |  |  |  |

### SFR Definition 18.3. CKCON: Clock Control

| R/W                  | R/W                                                                                                                                                                                          | R/W      | R/W           | R/W        | R/W          | R/W          | R/W          | Reset Value |  |  |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------|------------|--------------|--------------|--------------|-------------|--|--|--|

| —                    | _                                                                                                                                                                                            | T2MH     | T2ML          | T1M        | TOM          | SCA1         | SCA0         | 00000000    |  |  |  |

| Bit7                 | Bit6                                                                                                                                                                                         | Bit5     | Bit4          | Bit3       | Bit2         | Bit1         | Bit0         |             |  |  |  |

|                      |                                                                                                                                                                                              |          |               |            |              |              | SFR Addres   | s: 0x8E     |  |  |  |

|                      |                                                                                                                                                                                              |          |               |            |              |              |              |             |  |  |  |

| Bit7–6:              | <b>RESERVED</b> . Read = 0b; Must write 0b.                                                                                                                                                  |          |               |            |              |              |              |             |  |  |  |

| Bit5:                | <b>T2MH</b> : Timer 2 High Byte Clock Select.                                                                                                                                                |          |               |            |              |              |              |             |  |  |  |

|                      | This bit selects the clock supplied to the Timer 2 high byte if Timer 2 is configured in split 8-<br>bit timer mode. T2MH is ignored if Timer 2 is in any other mode.                        |          |               |            |              |              |              |             |  |  |  |

|                      | bit timer mode. T2MH is ignored if Timer 2 is in any other mode.<br>0: Timer 2 high byte uses the clock defined by the T2XCLK bit in TMR2CN.                                                 |          |               |            |              |              |              |             |  |  |  |

|                      | 1: Timer 2 high byte uses the system clock.<br><b>T2ML</b> : Timer 2 Low Byte Clock Select.<br>This bit selects the clock supplied to Timer 2. If Timer 2 is configured in split 8-bit timer |          |               |            |              |              |              |             |  |  |  |

| Bit4:                |                                                                                                                                                                                              |          |               |            |              |              |              |             |  |  |  |

|                      |                                                                                                                                                                                              |          |               |            |              |              |              |             |  |  |  |

|                      | mode, this bit selects the clock supplied to the lower 8-bit timer.                                                                                                                          |          |               |            |              |              |              |             |  |  |  |

|                      | 0: Timer 2 low byte uses the clock defined by the T2XCLK bit in TMR2CN.                                                                                                                      |          |               |            |              |              |              |             |  |  |  |

| Bit3:                | 1: Timer 2 low byte uses the system clock.                                                                                                                                                   |          |               |            |              |              |              |             |  |  |  |

| DILJ.                | <b>T1M</b> : Timer 1 Clock Select.<br>This select the clock source supplied to Timer 1. T1M is ignored when C/T1 is set to logic 1.                                                          |          |               |            |              |              |              |             |  |  |  |

|                      | 0: Timer 1 uses the clock defined by the prescale bits, SCA1–SCA0.                                                                                                                           |          |               |            |              |              |              |             |  |  |  |

|                      | 1: Timer 1 uses the system clock.                                                                                                                                                            |          |               |            |              |              |              |             |  |  |  |

| Bit2:                | TOM: Timer 0 Clock Select.                                                                                                                                                                   |          |               |            |              |              |              |             |  |  |  |

|                      | This bit selects the clock source supplied to Timer 0. T0M is ignored when C/T0 is set to                                                                                                    |          |               |            |              |              |              |             |  |  |  |

|                      | logic 1.                                                                                                                                                                                     | <b>-</b> |               | 1.0.11     |              |              | 0040         |             |  |  |  |

|                      | 0: Counter/Timer 0 uses the clock defined by the prescale bits, SCA1–SCA0.                                                                                                                   |          |               |            |              |              |              |             |  |  |  |

| Bits1_0 <sup>.</sup> | 1: Counter/Timer 0 uses the system clock.<br><b>SCA1–SCA0</b> : Timer 0/1 Prescale Bits.                                                                                                     |          |               |            |              |              |              |             |  |  |  |

| Bitor o.             |                                                                                                                                                                                              |          |               |            | plied to Tin | ner 0 and Ti | mer 1 if cor | nfigured to |  |  |  |

|                      | These bits control the division of the clock supplied to Timer 0 and Timer 1 if configured to use prescaled clock inputs.                                                                    |          |               |            |              |              |              |             |  |  |  |

|                      |                                                                                                                                                                                              |          |               |            |              |              |              |             |  |  |  |

|                      | SCA1                                                                                                                                                                                         | SCA0     | Presc         | aled Clock |              |              |              |             |  |  |  |

|                      | 0                                                                                                                                                                                            | 0 S      | ystem clock   | divided by | 12           |              |              |             |  |  |  |

|                      | 0                                                                                                                                                                                            | 1 S      | ystem clock   | divided by | 4            |              |              |             |  |  |  |

|                      | 1                                                                                                                                                                                            | 0 S      | ystem clock   | divided by | 48           |              |              |             |  |  |  |

|                      | 1                                                                                                                                                                                            | 1 E      | xternal clock | divided by | 8            |              |              |             |  |  |  |

|                      | Note: External clock divided by 8 is synchronized with                                                                                                                                       |          |               |            |              |              |              |             |  |  |  |

|                      | the system clock.                                                                                                                                                                            |          |               |            |              |              |              |             |  |  |  |

|                      |                                                                                                                                                                                              |          |               |            |              |              |              |             |  |  |  |

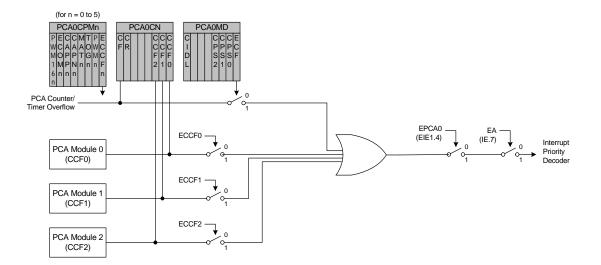

#### **19.2. Capture/Compare Modules**

Each module can be configured to operate independently in one of six operation modes: Edge-triggered Capture, Software Timer, High Speed Output, Frequency Output, 8-Bit Pulse Width Modulator, or 16-Bit Pulse Width Modulator. Each module has Special Function Registers (SFRs) associated with it in the CIP-51 system controller. These registers are used to exchange data with a module and configure the module's mode of operation.

Table 19.2 summarizes the bit settings in the PCA0CPMn registers used to select the PCA capture/compare module's operating modes. Setting the ECCFn bit in a PCA0CPMn register enables the module's CCFn interrupt. Note that PCA0 interrupts must be globally enabled before individual CCFn interrupts are recognized. PCA0 interrupts are globally enabled by setting the EA bit and the EPCA0 bit to logic 1. See Figure 19.3 for details on the PCA interrupt configuration.

| PWM16          | ECOM | CAPP | CAPN | MAT | TOG | PWM | ECCF | Operation Mode                             |  |

|----------------|------|------|------|-----|-----|-----|------|--------------------------------------------|--|

| Х              | Х    | 1    | 0    | 0   | 0   | 0   | Х    | Capture triggered by positive edge on CEXn |  |

| Х              | Х    | 0    | 1    | 0   | 0   | 0   | Х    | Capture triggered by negative edge on CEXn |  |

| Х              | Х    | 1    | 1    | 0   | 0   | 0   | Х    | Capture triggered by transition on<br>CEXn |  |

| Х              | 1    | 0    | 0    | 1   | 0   | 0   | Х    | Software Timer                             |  |

| Х              | 1    | 0    | 0    | 1   | 1   | 0   | Х    | High Speed Output                          |  |

| Х              | 1    | 0    | 0    | Х   | 1   | 1   | Х    | Frequency Output                           |  |

| 0              | 1    | 0    | 0    | Х   | 0   | 1   | Х    | 8-Bit Pulse Width Modulator                |  |

| 1              | 1    | 0    | 0    | Х   | 0   | 1   | Х    | 16-Bit Pulse Width Modulator               |  |

| X = Don't Care |      |      |      |     |     |     |      |                                            |  |

Table 19.2. PCA0CPM Register Settings for PCA Capture/Compare Modules

Figure 19.3. PCA Interrupt Block Diagram

## **DOCUMENT CHANGE LIST**

#### Revision 0.3 to 0.4

- Updated all specification tables.

- Added 'F52xA and 'F53xA information.

- Updated the Selectable Gain section in the ADC section.

- Updated the External Crystal Example in the Oscillators section.

- Updated the LIN section.

#### Revision 0.4 to 0.5

- Updated all specification tables.

- Updated Figures 1.1, 1.2, 1.3, and 1.4.

- Updated Section 4 pinout diagrams and tables.

#### Revision 0.5 to 1.0

- Updated all specification tables and moved them to one section.

- Added Figure 3.1 and Figure 3.2.

- Updated Section 4 pinout diagrams and tables.

- Updated Figure 5.6.

- Added Figure 15.3.

- Updated equations in Section 17.

- Updated Figure 21.3.

### Revision 1.0 to 1.1

- Updated Table 2.3, "ADC0 Electrical Characteristics," on page 28 with new Burst Mode Oscillator specification, new Power Supply Current maximum, and made corrections to Temperature Sensor Offset and Offset Error conditions.

- Updated Table 2.9, "Flash Electrical Characteristics," on page 33 with new Flash Write and Erase timing.

- Made correction in Equivalent Gain table in Section "4.4. Selectable Gain" on page 60.

- Updated Section "11.2. Power-Fail Reset / VDD Monitors (VDDMON0 and VDDMON1)" on page 108 regarding higher V<sub>DD</sub> monitor threshold.

#### Revision 1.1 to 1.2

- Updated "Ordering Information" on page 14 and Table 1.1, "Product Selection Guide (Recommended for New Designs)," on page 14 to include -A (Automotive) devices and automotive qualification information.

- Updated Table 2.3, "ADC0 Electrical Characteristics," on page 28 to include Temperature Sensor tracking time requirement and update INL maximum specification.

- Updated Figure 3.2. 'DFN-10 Package Diagram' on page 38 with new Pin-1 detail drawing.

- Updated Table 8.1, "CIP-51 Instruction Set Summary," on page 83 with correct CJNE and CPL timing.

- Updated "Power-Fail Reset / VDD Monitors (VDDMON0 and VDDMON1)" on page 108 to clarify the recommendations for the VDD monitor.

Note: All items from the C8051F52xA-F53xA Errata dated August 26, 2009 are incorporated into this data sheet.

- Replaced minimum VDD value for Flash write/erase operations in Table 2.9 on page 33 with references to the V<sub>RST-HIGH</sub> theshold specified in Table 2.8 on page 32.

- Removed Output Low Voltage values for condition 'V<sub>REGIN</sub> = 1.8 V' from Table 2.10, "Port I/O DC Electrical Characteristics," on page 33.

- Corrected minor typo ("IFCN = 111b") in Table 2.11, "Internal Oscillator Electrical Characteristics," on page 34.

- Removed the typical value and added the maximum value for the 'Wake-up Time From Suspend' specification with the 'ZTCEN = 0' condition in Table 2.11, "Internal Oscillator Electrical Characteristics," on page 34.

- Added Internal Oscillator Supply current values at specific temperatures for conditions 'ZTCEN = 1' and 'ZTCEN = 0' in Table 2.11, "Internal Oscillator Electrical Characteristics," on page 34. Also updated the table name to clarify that the specifications apply to the internal oscillator.

- Updated Section "1.1. Ordering Information" on page 14 and Table 1.1 with new C8051F52x-C/F53x-C part numbers.

- Updated Table 1.2, "Product Selection Guide (Not Recommended for New Designs)," on page 15 to include C8051F52xA/F53xA part numbers.

- Updated Figure 1.1, Figure 1.2, Figure 1.3, and Figure 1.4 titles to clarify applicable silicon revisions.

- Added figure references to pinout diagrams (Figure 3.1, Figure 3.4, and Figure 3.7) and updated labels to clarify applicable part numbers.

- Updated Table 3.1, Table 3.4, and Table 3.7 to indicate pinouts applicable to C8051F52x-C/F53x-C devices.

- Added note in Section "6. Voltage Regulator (REG0)" on page 74 to indicate the need for bypass capacitors for voltage regulator stability.

- Updated Figure 11.1 on Page 106 and text in Section "11.1. Power-On Reset" on page 107 and Section "11.2. Power-Fail Reset / VDD Monitors (VDDMON0 and VDDMON1)" on page 108 to describe the new level-sensitive V<sub>DD</sub> monitor (VDDMON1).

- Updated SFR Definition 11.1. "VDDMON: VDD Monitor Control" on page 109 to include the VDM1EN bit (bit 4) that controls the new level-sensitive V<sub>DD</sub> monitor (VDDMON1).

- Added notes in Section 11.1 on page 107, Section 11.2 on page 108, and Section 11.3 on page 110 with references to relevant parts of Section "20. Device Specific Behavior" on page 210.

- Moved some notes related to VDD Monitor (VDDMON0) High Threshold setting (V<sub>RST-HIGH</sub>) from Section 11.2 on page 108 to Section 20.5 on page 212 in Section "20. Device Specific Behavior".

- Added Section "11.2.1. VDD Monitor Thresholds and Minimum VDD" on page 108 to describe the recommendations for minimum V<sub>DD</sub> as it relates to the V<sub>DD</sub> monitor thresholds.

- Clarified text in Section "11.7. Flash Error Reset" on page 110.

- Clarified text in items 2, 3 and 4 in Section "12.2.1. V<sub>DD</sub> Maintenance and the V<sub>DD</sub> monitor" on page 115 to reference appropriate specification tables and specify "VDDMON0".