Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                  |

|----------------------------|------------------------------------------------------------------|

| Product Status             | Active                                                           |

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | LINbus, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT               |

| Number of I/O              | 16                                                               |

| Program Memory Size        | 2KB (2K x 8)                                                     |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 256 x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.25V                                                       |

| Data Converters            | A/D 16x12b                                                       |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                               |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 20-VFQFN Exposed Pad                                             |

| Supplier Device Package    | 20-QFN (4x4)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f536-c-im |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table 2.8. Reset Electrical Characteristics**

-40 to +125 °C unless otherwise specified.

| Parameter                                              | Conditions                                                                                                                                | Min                         | Тур                     | Мах                         | Units                |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------|-----------------------------|----------------------|

| RST Output Low Voltage                                 | I <sub>OL</sub> = 8.5 mA, V <sub>DD</sub> =<br>2.1 V                                                                                      | _                           | _                       | 0.8                         | V                    |

| RST Input High Voltage                                 |                                                                                                                                           | 0.7 x<br>V <sub>REGIN</sub> |                         |                             | V                    |

| RST Input Low Voltage                                  |                                                                                                                                           |                             |                         | 0.3 x<br>V <sub>REGIN</sub> | V                    |

| RST Input Pullup Impedance                             | $V_{\text{REGIN}} = 1.8 \text{ V}$ $V_{\text{REGIN}} = 2.7 \text{ V}$ $V_{\text{REGIN}} = 3.3 \text{ V}$ $V_{\text{REGIN}} = 5 \text{ V}$ |                             | 330<br>160<br>130<br>80 |                             | kΩ<br>kΩ<br>kΩ<br>kΩ |

| Missing Clock Detector Timeout                         | Time from last system<br>clock rising edge to reset<br>initiation                                                                         | 100                         | 350                     | 650                         | μs                   |

| Reset Time Delay (T <sub>PORDelay</sub> ) <sup>1</sup> | Delay between release<br>of any reset source and<br>code execution at loca-<br>tion 0x0000                                                |                             |                         | 350                         | μs                   |

| Minimum RST Low Time to Generate a System Reset        |                                                                                                                                           | 10                          | _                       | _                           | μs                   |

| V <sub>DD</sub> Monitor (VDDMON0)                      |                                                                                                                                           |                             |                         | •                           |                      |

| Low Threshold (V <sub>RST-LOW</sub> ) <sup>1,2,3</sup> | C8051F52x/53x<br>C8051F52xA/53xA<br>C8051F52x-C/53x-C                                                                                     | 1.8<br>1.65<br>1.65         | 1.9<br>1.75<br>1.75     | 2.0<br>1.8<br>1.8           | V<br>V<br>V          |

| High Threshold (V <sub>RST-HIGH</sub> ) <sup>3</sup>   | C8051F52x/53x<br>C8051F52xA/53xA<br>C8051F52x-C/53x-C                                                                                     | 2.1<br>2.25<br>2.25         | 2.2<br>2.3<br>2.3       | 2.3<br>2.4<br>2.45          | V<br>V<br>V          |

| Turn-on Time                                           |                                                                                                                                           | _                           | 83                      |                             | μs                   |

| Supply Current                                         | V <sub>DD</sub> = 2.1 V                                                                                                                   | _                           | 1                       | 2                           | μA                   |

| Level-Sensitive V <sub>DD</sub> Monitor (VDDMC         | <b>DN1</b> ) <sup>1</sup>                                                                                                                 |                             |                         | •                           |                      |

| Threshold (V <sub>RST1</sub> ) <sup>1,2,3</sup>        | C8051F52x-C/53x-C                                                                                                                         | 1.6                         | 1.75                    | 1.9                         | V                    |

| Supply Current                                         | C8051F52x-C/53x-C                                                                                                                         |                             | 3                       | 6                           | μA                   |

| Notes:<br>1. Refer to Section "20. Device Specific     | Behavior" on page 210.                                                                                                                    |                             |                         |                             |                      |

- Refer to Section "20. Device Specific Behavior" on page 210.

The POR threshold (V<sub>RST</sub>) is V<sub>RST-LOW</sub> or V<sub>RST1</sub>, whichever is higher.

The V<sub>RST</sub> threshold for power fail / brownout is the higher of VDDMON0 and VDDMON1 thresholds, if both are enabled.

### Table 3.1. Pin Definitions for the C8051F52x and C8051F52xA (DFN 10)

| Name               | Pin Nun           | nbers     | Туре             | Description                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|--------------------|-------------------|-----------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                    | 'F52xA<br>'F52x-C | 'F52x     |                  |                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| RST/<br>C2CK       | 1                 | 1         | D I/O<br>D I/O   | Device Reset. Open-drain output of internal POR or $V_{DD}$ monitor.<br>An external source can initiate a system reset by driving this pin<br>low for at least the minimum RST low time to generate a system<br>reset, as defined in Table 2.8 on page 32. A 1 k $\Omega$ pullup to<br>$V_{REGIN}$ is recommended. See Reset Sources Section for a com-<br>plete description. |  |  |  |

|                    |                   |           |                  | Clock signal for the C2 Debug Interface.                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| P0.0/              | 2                 | 2         | D I/O or<br>A In | Port 0.0. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                    |  |  |  |

| V <sub>REF</sub>   |                   |           | A O or<br>D In   | External V <sub>REF</sub> Input. See V <sub>REF</sub> Section.                                                                                                                                                                                                                                                                                                                |  |  |  |

| GND                | 3                 | 3         |                  | Ground.                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| V <sub>DD</sub>    | 4                 | 4         |                  | Core Supply Voltage.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| V <sub>REGIN</sub> | 5                 | 5         |                  | On-Chip Voltage Regulator Input.                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| P0.5/RX*/          | 6                 |           | D I/O or<br>A In | Port 0.5. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                    |  |  |  |

| CNVSTR             |                   |           | D In             | External Converter start input for the ADC0, see Section "4. 12-<br>Bit ADC (ADC0)" on page 52 for a complete description.                                                                                                                                                                                                                                                    |  |  |  |

| P0.5/              |                   | 6         | D I/O or<br>A In | Port 0.5. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                    |  |  |  |

| CNVSTR             |                   |           | D In             | External Converter start input for the ADC0, see Section "4. 12-<br>Bit ADC (ADC0)" on page 52 for a complete description.                                                                                                                                                                                                                                                    |  |  |  |

| P0.4/TX*           | 7                 |           | D I/O or<br>A In | Port 0.4. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                    |  |  |  |

| P0.4/RX*           | _                 | 7         | D I/O or<br>A In | Port 0.4. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                    |  |  |  |

| P0.3               | 8                 |           | D I/O or<br>A In | Port 0.3. See Port I/O Section for a complete description.                                                                                                                                                                                                                                                                                                                    |  |  |  |

| XTAL2              |                   |           | D I/O            | External Clock Output. For an external crystal or resonator, this pin is the excitation driver. This pin is the external clock input for CMOS, capacitor, or RC oscillator configurations. See Section "14. Oscillators" on page 135.                                                                                                                                         |  |  |  |

| Note: Please       | refer to Se       | ection "2 | 0. Device S      | pecific Behavior" on page 210.                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| Name          | Pin Numbers                                                                |    | Pin Numbers      |                                                            | Туре | Description |  |  |  |

|---------------|----------------------------------------------------------------------------|----|------------------|------------------------------------------------------------|------|-------------|--|--|--|

|               | ʻF53xA<br>ʻF53x-C                                                          |    |                  |                                                            |      |             |  |  |  |

| P0.4/TX*      | 19                                                                         |    | D I/O or<br>A In | Port 0.4. See Port I/O Section for a complete description. |      |             |  |  |  |

| P0.4/RX*      | —                                                                          | 19 | D I/O or<br>A In | Port 0.4. See Port I/O Section for a complete description. |      |             |  |  |  |

| P0.3          | 20                                                                         | _  | D I/O or<br>A In | Port 0.3. See Port I/O Section for a complete description. |      |             |  |  |  |

| P0.3/TX*      |                                                                            | 20 | D I/O or<br>A In | Port 0.3. See Port I/O Section for a complete description. |      |             |  |  |  |

| *Note: Please | *Note: Please refer to Section "20. Device Specific Behavior" on page 210. |    |                  |                                                            |      |             |  |  |  |

### Table 3.4. Pin Definitions for the C8051F53x and C805153xA (TSSOP 20) (Continued)

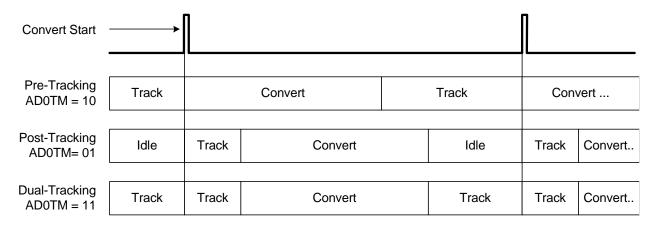

Post-Tracking Mode is selected when AD0TM is set to 01b. A programmable tracking time based on AD0TK is started immediately following the convert start signal. Conversions are started after the programmed tracking time ends. After a conversion is complete, ADC0 does not track the input. Rather, the sampling capacitor remains disconnected from the input making the input pin high-impedance until the next convert start signal.

Dual-Tracking Mode is selected when AD0TM is set to 11b. A programmable tracking time based on AD0TK is started immediately following the convert start signal. Conversions are started after the programmed tracking time ends. After a conversion is complete, ADC0 tracks continuously until the next conversion is started.

Depending on the output connected to the ADC input, additional tracking time, more than is specified in Table 2.3 on page 28, may be required after changing MUX settings. See the settling time requirements described in Section "4.3.6. Settling Time Requirements" on page 60.

### 4.3.3. Timing

ADC0 has a maximum conversion speed specified in Table 2.3 on page 28. ADC0 is clocked from the ADC0 Subsystem Clock (FCLK). The source of FCLK is selected based on the BURSTEN bit. When BURSTEN is logic 0, FCLK is derived from the current system clock. When BURSTEN is logic 1, FCLK is derived from the Burst Mode Oscillator, which is an independent clock source whose maximum frequency is specified in Table 2.3 on page 28.

When ADC0 is performing a conversion, it requires a clock source that is typically slower than FCLK. The ADC0 SAR conversion clock (SAR clock) is a divided version of FCLK. The divide ratio can be configured using the AD0SC bits in the ADC0CF register. The maximum SAR clock frequency is listed in Table 2.3 on page 28.

ADC0 can be in one of three states at any given time: tracking, converting, or idle. Tracking time depends on the tracking mode selected. For Pre-Tracking Mode, tracking is managed by software and ADC0 starts conversions immediately following the convert start signal. For Post-Tracking and Dual-Tracking Modes, the tracking time after the convert start signal is equal to the value determined by the AD0TK bits plus 2 FCLK cycles. Tracking is immediately followed by a conversion. The ADC0 conversion time is always 13 SAR clock cycles plus an additional 2 FCLK cycles to start and complete a conversion. Figure 4.4 shows timing diagrams for a conversion in Pre-Tracking Mode and tracking plus conversion in Post-Tracking or Dual-Tracking Mode. In this example, repeat count is set to one.

#### 4.3.5. Output Conversion Code

The registers ADC0H and ADC0L contain the high and low bytes of the output conversion code. When the repeat count is set to 1, conversion codes are represented in 12-bit unsigned integer format and the output conversion code is updated after each conversion. Inputs are measured from 0 to  $V_{REF} \times 4095/4096$ . Data can be right-justified or left-justified, depending on the setting of the AD0LJST bit (ADC0CN.2). Unused bits in the ADC0H and ADC0L registers are set to 0. Example codes are shown below for both right-justified and left-justified data.

| Input Voltage                | Right-Justified ADC0H:ADC0L<br>(AD0LJST = 0) | Left-Justified ADC0H:ADC0L<br>(AD0LJST = 1) |

|------------------------------|----------------------------------------------|---------------------------------------------|

| V <sub>REF</sub> x 4095/4096 | 0x0FFF                                       | 0xFFF0                                      |

| V <sub>REF</sub> x 2048/4096 | 0x0800                                       | 0x8000                                      |

| V <sub>REF</sub> x 2047/4096 | 0x07FF                                       | 0x7FF0                                      |

| 0                            | 0x0000                                       | 0x0000                                      |

When the ADC0 Repeat Count is greater than 1, the output conversion code represents the accumulated result of the conversions performed and is updated after the last conversion in the series is finished. Sets of 4, 8, or 16 consecutive samples can be accumulated and represented in unsigned integer format. The repeat count can be selected using the AD0RPT bits in the ADC0CF register. The value must be right-justified (AD0LJST = "0"), and unused bits in the ADC0H and ADC0L registers are set to '0'. The following example shows right-justified codes for repeat counts greater than 1. Notice that accumulating  $2^n$  samples is equivalent to left-shifting by *n* bit positions when all samples returned from the ADC have the same value.

| Input Voltage                | Repeat Count = 4 | Repeat Count = 8 | Repeat Count = 16 |

|------------------------------|------------------|------------------|-------------------|

| V <sub>REF</sub> x 4095/4096 | 0x3FFC           | 0x7FF8           | 0xFFF0            |

| V <sub>REF</sub> x 2048/4096 | 0x2000           | 0x4000           | 0x8000            |

| V <sub>REF</sub> x 2047/4096 | 0x1FFC           | 0x3FF8           | 0x7FF0            |

| 0                            | 0x0000           | 0x0000           | 0x0000            |

| R/W                                | R/W                                              | R/W                 | R/W                | R/W       | R/W                                            | R/W        | R/W          | Reset Value                                          |  |  |  |  |  |  |  |  |  |

|------------------------------------|--------------------------------------------------|---------------------|--------------------|-----------|------------------------------------------------|------------|--------------|------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Reserve                            | -                                                | CPORIE              | CP0FIE             |           |                                                | CP0MD1     | CP0MD0       | 00000010                                             |  |  |  |  |  |  |  |  |  |

| Bit7                               | Bit6                                             | Bit5                | Bit4               | Bit3      | Bit2                                           | Bit1       | Bit0         | SFR Address:                                         |  |  |  |  |  |  |  |  |  |

|                                    |                                                  |                     |                    |           |                                                |            |              | 0x9D                                                 |  |  |  |  |  |  |  |  |  |

|                                    |                                                  |                     |                    |           |                                                |            |              |                                                      |  |  |  |  |  |  |  |  |  |

| Bit7:                              | RESERVE                                          | <b>)</b> . Read = 0 | b. Must write      | e 0b.     |                                                |            |              |                                                      |  |  |  |  |  |  |  |  |  |

| Bit6:                              | UNUSED.                                          | Read = 0b. V        | Write = don't      | care.     |                                                |            |              |                                                      |  |  |  |  |  |  |  |  |  |

| Bit5:                              | CPORIE: Comparator Rising-Edge Interrupt Enable. |                     |                    |           |                                                |            |              |                                                      |  |  |  |  |  |  |  |  |  |

|                                    | 0: Comparator rising-edge interrupt disabled.    |                     |                    |           |                                                |            |              |                                                      |  |  |  |  |  |  |  |  |  |

|                                    |                                                  | •                   | dge interrupt      |           |                                                |            |              |                                                      |  |  |  |  |  |  |  |  |  |

| Bit4:                              |                                                  |                     | alling-Edge l      |           | able.                                          |            |              |                                                      |  |  |  |  |  |  |  |  |  |

|                                    |                                                  |                     | dge interrupt      |           |                                                |            |              |                                                      |  |  |  |  |  |  |  |  |  |

|                                    |                                                  |                     | dge interrupt      |           |                                                |            |              |                                                      |  |  |  |  |  |  |  |  |  |

|                                    |                                                  | ecessary to         | enable both        | CP0xIE an | d the corres                                   | spondent E | CPx bit loca | ted in EIE1                                          |  |  |  |  |  |  |  |  |  |

| <b>D</b> <sup>1</sup> / <b>D D</b> | SFR.                                             |                     |                    |           |                                                |            |              |                                                      |  |  |  |  |  |  |  |  |  |

|                                    |                                                  |                     | . Write = don      |           |                                                |            |              |                                                      |  |  |  |  |  |  |  |  |  |

| BIts1-0:                           |                                                  |                     | omparator0 N       |           |                                                |            |              |                                                      |  |  |  |  |  |  |  |  |  |

|                                    |                                                  |                     | sponse ume         |           | 181010.                                        |            |              | These bits select the response time for Comparator0. |  |  |  |  |  |  |  |  |  |

|                                    |                                                  |                     |                    |           |                                                |            |              |                                                      |  |  |  |  |  |  |  |  |  |

|                                    | Mode                                             | CP0MD1              | CP0MD0             | CP0 Fall  | ina Edae I                                     | Response   |              |                                                      |  |  |  |  |  |  |  |  |  |

|                                    | Mode                                             | CP0MD1              | CP0MD0             | CP0 Fall  | ing Edge I<br>Time (TYP                        | •          |              |                                                      |  |  |  |  |  |  |  |  |  |

|                                    | Mode<br>0                                        | <b>CP0MD1</b>       | <b>CP0MD0</b><br>0 |           |                                                | ')         |              |                                                      |  |  |  |  |  |  |  |  |  |

|                                    | 0                                                |                     |                    |           | Time (TYP                                      | ')         |              |                                                      |  |  |  |  |  |  |  |  |  |

|                                    | 0<br>1<br>2                                      | 0                   | 0                  |           | Time (TYP                                      | ')         | _            |                                                      |  |  |  |  |  |  |  |  |  |

|                                    | 0                                                | 0                   | 0                  | Faste     | Time (TYP                                      | e Time     |              |                                                      |  |  |  |  |  |  |  |  |  |

|                                    | 0<br>1<br>2                                      | 0<br>0<br>1         | 0<br>1<br>0        | Faste     | Time (TYP<br>st Respons<br>—<br>—              | e Time     |              |                                                      |  |  |  |  |  |  |  |  |  |

|                                    | 0<br>1<br>2<br>3<br>Note: Rising                 | 0<br>0<br>1<br>1    | 0<br>1<br>0        | Faste     | Time (TYP<br>st Respons<br>—<br>—<br>Power Con | e Time     | ng Edge re   | sponse                                               |  |  |  |  |  |  |  |  |  |

|                                    | 0<br>1<br>2<br>3                                 | 0<br>0<br>1<br>1    | 0<br>1<br>0<br>1   | Faste     | Time (TYP<br>st Respons<br>—<br>—<br>Power Con | e Time     | ng Edge re   | sponse                                               |  |  |  |  |  |  |  |  |  |

|                                    | 0<br>1<br>2<br>3<br>Note: Rising                 | 0<br>0<br>1<br>1    | 0<br>1<br>0<br>1   | Faste     | Time (TYP<br>st Respons<br>—<br>—<br>Power Con | e Time     | ng Edge re   | sponse                                               |  |  |  |  |  |  |  |  |  |

#### Performance

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute, and usually have a maximum system clock of 12 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with no instructions taking more than eight system clock cycles.

With the CIP-51's system clock running at 25 MHz, it has a peak throughput of 25 MIPS. The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute      | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

|------------------------|----|----|-----|----|-----|---|-----|---|---|

| Number of Instructions | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

#### **Programming and Debugging Support**

In-system programming of the Flash program memory and communication with on-chip debug support logic is accomplished via the Silicon Labs 2-Wire (C2) interface. Note that the re-programmable Flash can also be read and written a single byte at a time by the application software using the MOVC and MOVX instructions. This feature allows program memory to be used for non-volatile data storage as well as updating program code under software control.

The on-chip debug support logic facilitates full speed in-circuit debugging, allowing the setting of hardware breakpoints, starting, stopping and single stepping through program execution (including interrupt service routines), examination of the program's call stack, and reading/writing the contents of registers and memory. This method of on-chip debugging is completely non-intrusive, requiring no RAM, Stack, timers, or other on-chip resources.

The CIP-51 is supported by development tools from Silicon Laboratories, Inc. and third party vendors. Silicon Laboratories provides an integrated development environment (IDE) including editor, evaluation compiler, assembler, debugger and programmer. The IDE's debugger and programmer interface to the CIP-51 via the on-chip debug logic to provide fast and efficient in-system device programming and debugging. Third party macro assemblers and C compilers are also available.

### 8.1. Instruction Set

The instruction set of the CIP-51 System Controller is fully compatible with the standard MCS-51<sup>™</sup> instruction set. Standard 8051 development tools can be used to develop software for the CIP-51. All CIP-51 instructions are the binary and functional equivalent of their MCS-51<sup>™</sup> counterparts, including opcodes, addressing modes and effect on PSW flags. However, instruction timing is different than that of the standard 8051.

#### 8.1.1. Instruction and CPU Timing

In many 8051 implementations, a distinction is made between machine cycles and clock cycles, with machine cycles varying from 2 to 12 clock cycles in length. However, the CIP-51 implementation is based solely on clock cycle timing. All instruction timings are specified in terms of clock cycles.

Due to the pipelined architecture of the CIP-51, most instructions execute in the same number of clock cycles as there are program bytes in the instruction. Conditional branch instructions take one less clock cycle to complete when the branch is not taken as opposed to when the branch is taken. Table 8.1 is the CIP-51 Instruction Set Summary, which includes the mnemonic, number of bytes, and number of clock cycles for each instruction.

## SFR Definition 8.7. PCON: Power Control

| R/W                  | R/W            | R/W          | R/W           | R/W           | R/W           | R/W            | R/W           | Reset Value |

|----------------------|----------------|--------------|---------------|---------------|---------------|----------------|---------------|-------------|

| Reserved             | d Reserved     | Reserved     | Reserved      | Reserved      | Reserved      | STOP           | IDLE          | 00000000    |

| Bit7                 | Bit6           | Bit5         | Bit4          | Bit3          | Bit2          | Bit1           | Bit0          | _           |

|                      |                |              |               |               |               |                | SFR Address   | : 0x87      |

| Rits7_2 <sup>.</sup> | RESERVED       |              |               |               |               |                |               |             |

|                      | STOP: STOP     | •            | oot           |               |               |                |               |             |

| DILI.                |                |              |               |               |               |                |               |             |

|                      | Writing a 1 to |              | •             |               |               |                |               | ead 0.      |

|                      | 1: CIP-51 for  | ced into po  | wer-down r    | node. (Turn   | s off interna | al oscillator) | ).            |             |

| Bit0:                | IDLE: IDLE I   | Mode Selec   | :t.           |               |               | ,              |               |             |

|                      | Writing a 1 to | thic bit wil | l placa tha ( | CID 51 into   |               | Thic bit w     | ill always ro | ad 0        |

|                      | •              |              | •             |               |               |                | •             |             |

|                      | 1: CIP-51 for  |              | `             | Shuts off clo | ock to CPU,   | but clock t    | o Timers, In  | iterrupts,  |

|                      | and all perip  | herals rema  | ain active.)  |               |               |                |               |             |

|                      |                |              | ,             |               |               |                |               |             |

|                      |                |              |               |               |               |                |               |             |

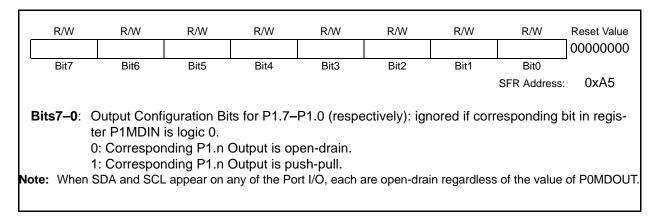

## SFR Definition 13.11. P1MDOUT: Port1 Output Mode

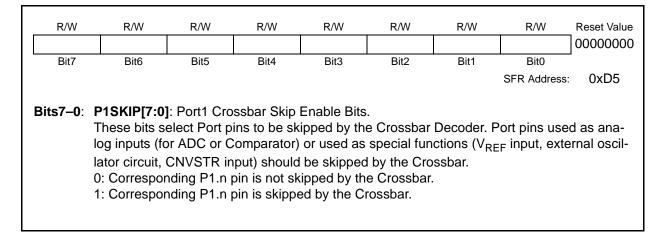

## SFR Definition 13.12. P1SKIP: Port1 Skip

### SFR Definition 15.2. SBUF0: Serial (UART0) Port Data Buffer

# Table 15.1. Timer Settings for Standard Baud RatesUsing the Internal Oscillator

|                   | Frequency: 24.5 MHz          |                      |                                |                       |                                     |      |                                  |  |  |  |  |

|-------------------|------------------------------|----------------------|--------------------------------|-----------------------|-------------------------------------|------|----------------------------------|--|--|--|--|

|                   | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscillator<br>Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select)* | T1M* | Timer 1<br>Reload<br>Value (hex) |  |  |  |  |

|                   | 230400                       | -0.32%               | 106                            | SYSCLK                | XX                                  | 1    | 0xCB                             |  |  |  |  |

|                   | 115200                       | -0.32%               | 212                            | SYSCLK                | XX                                  | 1    | 0x96                             |  |  |  |  |

|                   | 57600                        | 0.15%                | 426                            | SYSCLK                | XX                                  | 1    | 0x2B                             |  |  |  |  |

| from<br>Sc.       | 28800                        | -0.32%               | 848                            | SYSCLK/4              | 01                                  | 0    | 0x96                             |  |  |  |  |

| < fror<br>Osc.    | 14400                        | 0.15%                | 1704                           | SYSCLK / 12           | 00                                  | 0    | 0xB9                             |  |  |  |  |

| <u> </u>          | 9600                         | -0.32%               | 2544                           | SYSCLK / 12           | 00                                  | 0    | 0x96                             |  |  |  |  |

| SYSCL<br>Internal | 2400                         | -0.32%               | 10176                          | SYSCLK / 48           | 10                                  | 0    | 0x96                             |  |  |  |  |

| SY<br>Int         | 1200                         | 0.15%                | 20448                          | SYSCLK / 48           | 10                                  | 0    | 0x2B                             |  |  |  |  |

X = Don't care

**Note:** SCA1–SCA0 and T1M bit definitions can be found in Section 18.1.

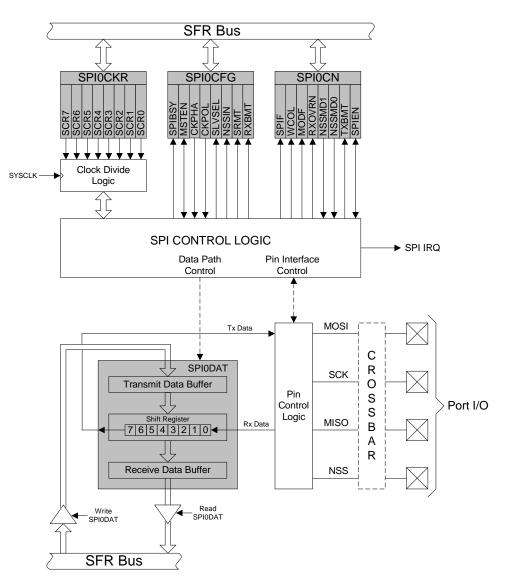

## 16. Enhanced Serial Peripheral Interface (SPI0)

The Serial Peripheral Interface (SPI0) provides access to a flexible, full-duplex synchronous serial bus. SPI0 can operate as a master or slave device in both 3-wire or 4-wire modes, and supports multiple masters and slaves on a single SPI bus. The slave-select (NSS) signal can be configured as an input to select SPI0 in slave mode, or to disable Master Mode operation in a multi-master environment, avoiding contention on the SPI bus when more than one master attempts simultaneous data transfers. NSS can also be configured as a chip-select output in master mode, or disabled for 3-wire operation. Additional general purpose port I/O pins can be used to select multiple slave devices in master mode.

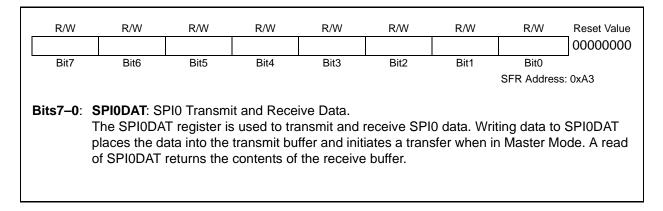

## SFR Definition 16.4. SPI0DAT: SPI0 Data

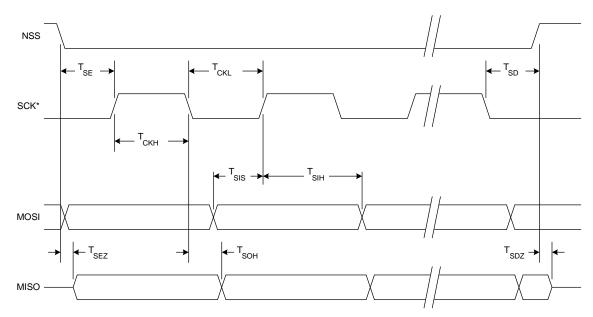

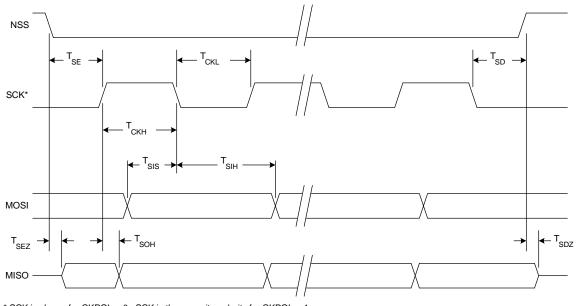

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

### Figure 16.9. SPI Slave Timing (CKPHA = 1)

## SFR Definition 17.3. LINCF Control Mode Register

| R/W   | R/W                                                              | R/W R/W      |           | R/W  | R/W  | R/W  | R/W          | Reset Value |  |  |

|-------|------------------------------------------------------------------|--------------|-----------|------|------|------|--------------|-------------|--|--|

| LINEN | I MODE                                                           | ABAUD        |           |      |      |      |              | 00000000    |  |  |

| Bit7  | Bit6                                                             | Bit5         | Bit4      | Bit3 | Bit2 | Bit1 | Bit0         | •           |  |  |

|       |                                                                  |              |           |      |      |      | SFR Address: | 0x95        |  |  |

| Bit7: |                                                                  |              |           |      |      |      |              |             |  |  |

|       | 0: LIN0 is disabled.                                             |              |           |      |      |      |              |             |  |  |

| -     | 1: LINO is enabled.                                              |              |           |      |      |      |              |             |  |  |

| Bit6: | MODE: LIN Mode Selection                                         |              |           |      |      |      |              |             |  |  |

|       | 0: LIN0 oper                                                     |              |           |      |      |      |              |             |  |  |

|       | 1: LIN0 oper                                                     | rates in Mas | ter mode. |      |      |      |              |             |  |  |

| Bit5: | ABAUD: LIN Mode Automatic Baud Rate Selection (slave mode only). |              |           |      |      |      |              |             |  |  |

|       | 0: Manual baud rate selection is enabled.                        |              |           |      |      |      |              |             |  |  |

|       | 1: Automatic baud rate selection is enabled.                     |              |           |      |      |      |              |             |  |  |

|       |                                                                  |              |           |      |      |      |              |             |  |  |

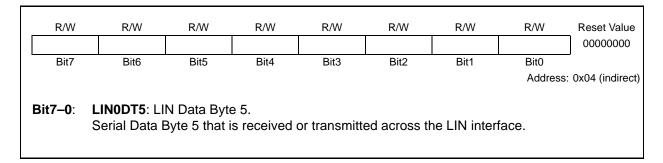

### SFR Definition 17.8. LIN0DT5: LIN0 Data Byte 5

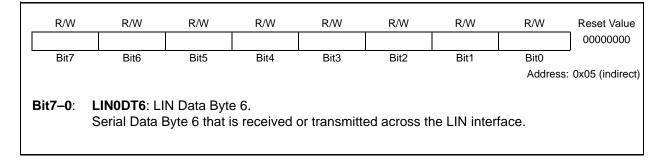

## SFR Definition 17.9. LIN0DT6: LIN0 Data Byte 6

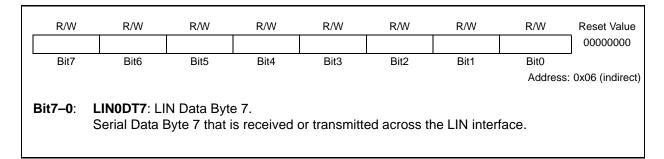

## SFR Definition 17.10. LIN0DT7: LIN0 Data Byte 7

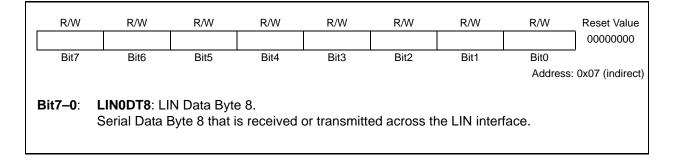

## SFR Definition 17.11. LIN0DT8: LIN0 Data Byte 8

| SFR Defi | nition 18.8                                                                                                                                                                         | . TMR2C      | N: Timer    | 2 Contro      |                |              |                               |             |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------|---------------|----------------|--------------|-------------------------------|-------------|--|--|--|

| R/W      | R/W R/W R/W                                                                                                                                                                         |              | R/W R/W     |               | R/W            | R/W          | R/W                           | Reset Value |  |  |  |

| TF2H     | TF2L                                                                                                                                                                                | TF2LEN       | TF2CEN      | T2SPLIT       | TR2            | _            | T2XCLK                        | 00000000    |  |  |  |

| Bit7     | Bit6                                                                                                                                                                                | Bit5         | Bit4        | Bit3          | Bit2           | Bit1         | Bit0                          | Bit         |  |  |  |

|          |                                                                                                                                                                                     |              |             |               |                |              | Addressable SFR Address: 0xC8 |             |  |  |  |

|          |                                                                                                                                                                                     |              |             |               |                |              | SI IT Address                 | . 0700      |  |  |  |

| Bit7:    | TF2H: Timer                                                                                                                                                                         | r 2 High Byt | e Overflow  | Flag.         |                |              |                               |             |  |  |  |

|          | Set by hardware when the Timer 2 high byte overflows from 0xFF to 0x00. In 16 bit mode, this will occur when Timer 2 overflows from 0xFFFF to 0x0000. When the Timer 2 interrupt is |              |             |               |                |              |                               |             |  |  |  |

|          |                                                                                                                                                                                     |              |             |               |                |              |                               |             |  |  |  |

|          | enabled, set<br>TF2H is not                                                                                                                                                         |              |             |               |                |              |                               |             |  |  |  |

| Bit6:    | TF2L: Timer                                                                                                                                                                         |              | •           | •             |                |              | by sonware                    | •           |  |  |  |

|          | Set by hardw                                                                                                                                                                        | vare when t  | he Timer 2  | low byte ov   |                |              |                               |             |  |  |  |

|          | set, an interr                                                                                                                                                                      |              | -           |               |                |              | •                             |             |  |  |  |

|          | will set wher<br>ically cleared                                                                                                                                                     |              |             | s regardless  | of the Time    | er 2 mode.   | I his bit is n                | ot automat- |  |  |  |

| Bit5:    | TF2LEN: Tir                                                                                                                                                                         |              |             | ot Enable.    |                |              |                               |             |  |  |  |

|          | This bit enab                                                                                                                                                                       |              | •           |               | errupts. If Th | F2LEN is s   | set and Time                  | er 2 inter- |  |  |  |

|          | rupts are en                                                                                                                                                                        |              |             |               |                |              | of Timer 2 ov                 | verflows.   |  |  |  |

|          | This bit shou<br>0: Timer 2 Lo                                                                                                                                                      |              |             | •             | er 2 in 16-bi  | it mode.     |                               |             |  |  |  |

|          | 1: Timer 2 Lo                                                                                                                                                                       | •            | •           |               |                |              |                               |             |  |  |  |

| Bit4:    | TF2CEN. Tir                                                                                                                                                                         | •            | •           |               |                |              |                               |             |  |  |  |

|          | 0: Timer 2 ca                                                                                                                                                                       | •            |             |               |                |              |                               |             |  |  |  |

| D:40.    | 1: Timer 2 ca                                                                                                                                                                       | •            |             |               |                |              |                               |             |  |  |  |

| Bit3:    | T2SPLIT: Tir                                                                                                                                                                        | •            |             |               | hit timers w   | /ith auto-re | aload                         |             |  |  |  |

|          | When this bit is set, Timer 2 operates as two 8-bit timers with auto-reload.<br>0: Timer 2 operates in 16-bit auto-reload mode.                                                     |              |             |               |                |              |                               |             |  |  |  |

|          | 1: Timer 2 of                                                                                                                                                                       | perates as t | wo 8-bit au |               |                |              |                               |             |  |  |  |

| Bit2:    | TR2: Timer 2                                                                                                                                                                        |              |             |               |                |              |                               |             |  |  |  |

|          | This bit enab<br>TMR2L is al                                                                                                                                                        |              |             |               | e, this bit er | ables/disa   | ables TMR2                    | - oniy;     |  |  |  |

|          | 0: Timer 2 di                                                                                                                                                                       | •            |             | oue.          |                |              |                               |             |  |  |  |

|          | 1: Timer 2 ei                                                                                                                                                                       |              |             |               |                |              |                               |             |  |  |  |

| Bit1:    | Unused. Re                                                                                                                                                                          |              |             |               |                |              |                               |             |  |  |  |

| Bit0:    | T2XCLK: Tir                                                                                                                                                                         |              |             |               | mor 2 If Tin   | oor 2 io in  | 9 hit mada                    | thic hit    |  |  |  |

|          | This bit selects the e                                                                                                                                                              |              |             |               |                |              |                               |             |  |  |  |

|          |                                                                                                                                                                                     |              |             |               |                | •            |                               |             |  |  |  |

|          | Select bits (T2MH and T2ML in register CKCON) may still be used to select between the<br>external clock and the system clock for either timer.                                      |              |             |               |                |              |                               |             |  |  |  |

|          | <ul><li>0: Timer 2 external clock selection is the system clock divided by 12.</li><li>1: Timer 2 external clock selection is the external clock divided by 8.</li></ul>            |              |             |               |                |              |                               |             |  |  |  |

|          | 1: Timer 2 ex                                                                                                                                                                       | xternal cioc | K SEIECTION | is the extern | Iai CIOCK div  | idea by 8.   |                               |             |  |  |  |

|          |                                                                                                                                                                                     |              |             |               |                |              |                               |             |  |  |  |

|          |                                                                                                                                                                                     |              |             |               |                |              |                               |             |  |  |  |

|          |                                                                                                                                                                                     |              |             |               |                |              |                               |             |  |  |  |

|          |                                                                                                                                                                                     |              |             |               |                |              |                               |             |  |  |  |

|          |                                                                                                                                                                                     |              |             |               |                |              |                               |             |  |  |  |

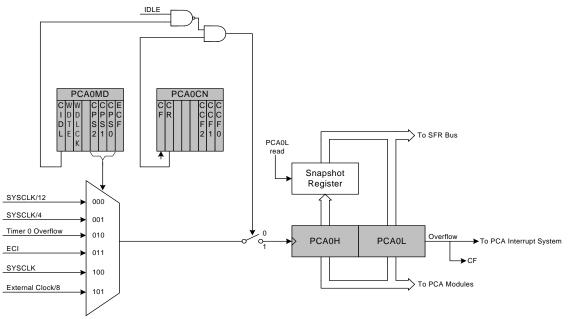

## **19.1. PCA Counter/Timer**

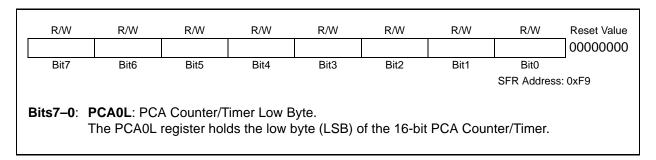

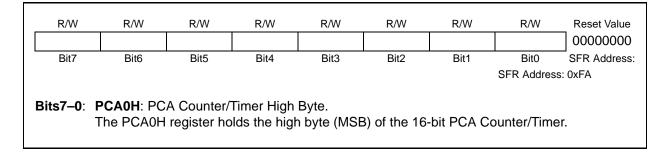

The 16-bit PCA counter/timer consists of two 8-bit SFRs: PCA0L and PCA0H. PCA0H is the high byte (MSB) of the 16-bit counter/timer and PCA0L is the low byte (LSB). Reading PCA0L automatically latches the value of PCA0H into a "snapshot" register; the following PCA0H read accesses this "snapshot" register. **Reading the PCA0L Register first guarantees an accurate reading of the entire 16-bit PCA0 counter.** Reading PCA0H or PCA0L does not disturb the counter operation. The CPS2-CPS0 bits in the PCA0MD register select the timebase for the counter/timer as shown in Table 19.1.

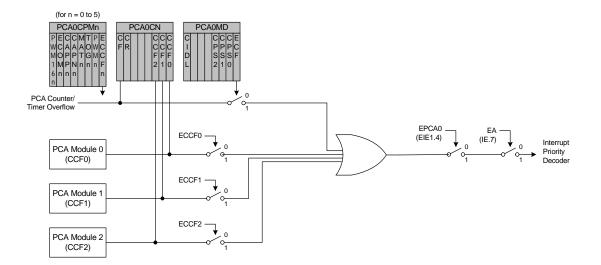

When the counter/timer overflows from 0xFFFF to 0x0000, the Counter Overflow Flag (CF) in PCA0MD is set to logic 1 and an interrupt request is generated if CF interrupts are enabled. Setting the ECF bit in PCA0MD to logic 1 enables the CF flag to generate an interrupt request. The CF bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software (Note: PCA0 interrupts must be globally enabled before CF interrupts are recognized. PCA0 interrupts are globally enabled by setting the EA bit (IE.7) and the EPCA0 bit in EIE1 to logic 1). Clearing the CIDL bit in the PCA0MD register allows the PCA to continue normal operation while the CPU is in Idle mode.

| CPS2 | CPS1 | CPS0 | Timebase                                                              |

|------|------|------|-----------------------------------------------------------------------|

| 0    | 0    | 0    | System clock divided by 12                                            |

| 0    | 0    | 1    | System clock divided by 4                                             |

| 0    | 1    | 0    | Timer 0 overflow                                                      |

| 0    | 1    | 1    | High-to-low transitions on ECI (max rate = system clock divided by 4) |

| 1    | 0    | 0    | System clock                                                          |

| 1    | 0    | 1    | External oscillator source divided by 8*                              |

#### Table 19.1. PCA Timebase Input Options

**Note:** External clock divided by 8 is synchronized with the system clock.

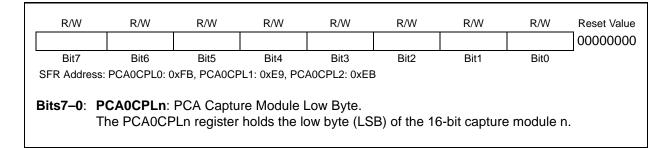

### **19.2. Capture/Compare Modules**

Each module can be configured to operate independently in one of six operation modes: Edge-triggered Capture, Software Timer, High Speed Output, Frequency Output, 8-Bit Pulse Width Modulator, or 16-Bit Pulse Width Modulator. Each module has Special Function Registers (SFRs) associated with it in the CIP-51 system controller. These registers are used to exchange data with a module and configure the module's mode of operation.

Table 19.2 summarizes the bit settings in the PCA0CPMn registers used to select the PCA capture/compare module's operating modes. Setting the ECCFn bit in a PCA0CPMn register enables the module's CCFn interrupt. Note that PCA0 interrupts must be globally enabled before individual CCFn interrupts are recognized. PCA0 interrupts are globally enabled by setting the EA bit and the EPCA0 bit to logic 1. See Figure 19.3 for details on the PCA interrupt configuration.

| PWM16    | ECOM           | CAPP | CAPN | MAT | TOG | PWM | ECCF | Operation Mode                             |  |

|----------|----------------|------|------|-----|-----|-----|------|--------------------------------------------|--|

| Х        | Х              | 1    | 0    | 0   | 0   | 0   | Х    | Capture triggered by positive edge on CEXn |  |

| Х        | Х              | 0    | 1    | 0   | 0   | 0   | Х    | Capture triggered by negative edge on CEXn |  |

| Х        | Х              | 1    | 1    | 0   | 0   | 0   | Х    | Capture triggered by transition on<br>CEXn |  |

| Х        | 1              | 0    | 0    | 1   | 0   | 0   | Х    | Software Timer                             |  |

| Х        | 1              | 0    | 0    | 1   | 1   | 0   | Х    | High Speed Output                          |  |

| Х        | 1              | 0    | 0    | Х   | 1   | 1   | Х    | Frequency Output                           |  |

| 0        | 1              | 0    | 0    | Х   | 0   | 1   | Х    | 8-Bit Pulse Width Modulator                |  |

| 1        | 1              | 0    | 0    | Х   | 0   | 1   | Х    | 16-Bit Pulse Width Modulator               |  |

| X = Don' | X = Don't Care |      |      |     |     |     |      |                                            |  |

Table 19.2. PCA0CPM Register Settings for PCA Capture/Compare Modules

Figure 19.3. PCA Interrupt Block Diagram

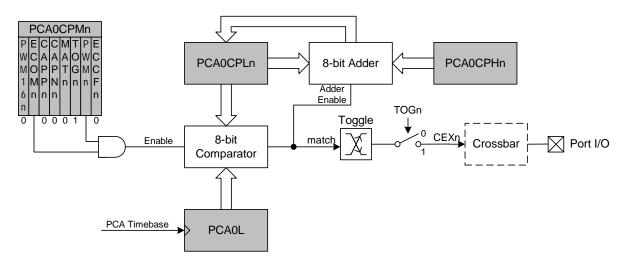

#### 19.2.4. Frequency Output Mode

Frequency Output Mode produces a programmable-frequency square wave on the module's associated CEXn pin. The capture/compare module high byte holds the number of PCA clocks to count before the output is toggled. The frequency of the square wave is then defined by Equation 19.1.

$$F_{CEXn} = \frac{F_{PCA}}{2 \times PCA0CPHn}$$

**Note:** A value of 0x00 in the PCA0CPHn register is equal to 256 for this equation.

#### Equation 19.1. Square Wave Frequency Output

Where  $F_{PCA}$  is the frequency of the clock selected by the CPS2-0 bits in the PCA mode register, PCA0MD. The lower byte of the capture/compare module is compared to the PCA counter low byte; on a match, CEXn is toggled and the offset held in the high byte is added to the matched value in PCA0CPLn. Frequency Output Mode is enabled by setting the ECOMn, TOGn, and PWMn bits in the PCA0CPMn register.

Figure 19.7. PCA Frequency Output Mode

### SFR Definition 19.4. PCA0L: PCA Counter/Timer Low Byte

### SFR Definition 19.5. PCA0H: PCA Counter/Timer High Byte

## SFR Definition 19.6. PCA0CPLn: PCA Capture Module Low Byte

## SFR Definition 19.7. PCA0CPHn: PCA Capture Module High Byte