# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                           |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | LINbus, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT               |

| Number of I/O              | 16                                                               |

| Program Memory Size        | 2KB (2K x 8)                                                     |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 256 x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.25V                                                       |

| Data Converters            | A/D 16x12b                                                       |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                               |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                  |

| Supplier Device Package    | 20-TSSOP                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f536-c-it |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

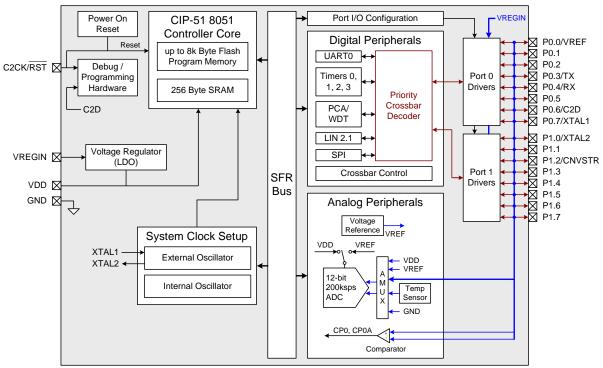

Figure 1.3. C8051F53x Block Diagram (Silicon Revision A)

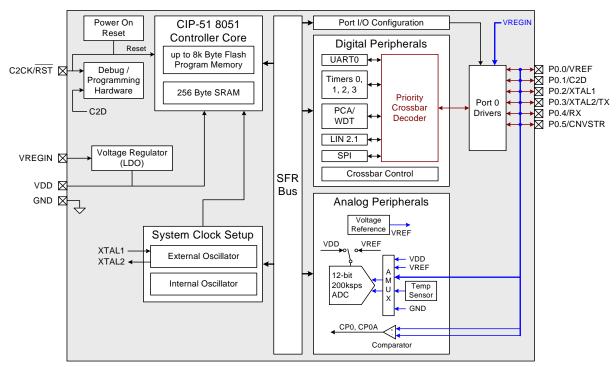

Figure 1.4. C8051F52x Block Diagram (Silicon Revision A)

#### **Table 2.4. Temperature Sensor Electrical Characteristics**

$V_{DD}$  = 2.1 V,  $V_{REF}$  = 1.5 V (REFSL=0), -40 to +125 °C unless otherwise specified.

| Parameter                           | Conditions                     | Min | Тур  | Max | Units |

|-------------------------------------|--------------------------------|-----|------|-----|-------|

| Linearity <sup>1</sup>              |                                | —   | 0.1  |     | °C    |

| Gain <sup>1</sup>                   |                                | —   | 3.33 | —   | mV/°C |

| Gain Error <sup>2</sup>             |                                | —   | ±100 |     | µV/°C |

| Offset <sup>1</sup>                 | Temp = 0 °C                    | —   | 890  | —   | mV    |

| Offset Error <sup>2</sup>           | Temp = 0 °C                    | —   | ±15  | —   | mV    |

| Tracking Time                       |                                | 12  | —    |     | μs    |

| Power Supply Current                |                                | —   | 17   |     | μA    |

| Notes:<br>1. Includes ADC offset. g | ain. and linearity variations. | ·   | •    | •   |       |

Includes ADC offset, gain, and linearity variations.

Performance and standard deviation from the mean

2. Represents one standard deviation from the mean.

#### Table 2.5. Voltage Reference Electrical Characteristics

$V_{DD} = 2.1 \text{ V}; -40 \text{ to } +125 \text{ °C}$  unless otherwise specified.

| Parameter                                | Conditions                                                                      | Min          | Тур        | Max             | Units  |

|------------------------------------------|---------------------------------------------------------------------------------|--------------|------------|-----------------|--------|

| Internal Reference (REFBE =              | 1)                                                                              |              |            |                 |        |

| Output Voltage                           | $I_{DD} \approx$ 1 mA; No load on VREF pin and all other GPIO pins.             |              |            |                 |        |

|                                          | 25 °C ambient (REFLV = 0)<br>25 °C ambient (REFLV = 1), V <sub>DD</sub> = 2.6 V | 1.45<br>2.15 | 1.5<br>2.2 | 1.55<br>2.25    | V      |

| V <sub>REF</sub> Short-Circuit Current   |                                                                                 |              | 2.5        |                 | mA     |

| V <sub>REF</sub> Temperature Coefficient |                                                                                 |              | 33         |                 | ppm/°C |

| Load Regulation                          | Load = 0 to 200 µA to GND                                                       | —            | 10         | —               | ppm/µA |

| V <sub>REF</sub> Turn-on Time 1          | 4.7 μF, 0.1 μF bypass                                                           | —            | 21         |                 | ms     |

| V <sub>REF</sub> Turn-on Time 2          | 0.1 μF bypass                                                                   |              | 230        |                 | μs     |

| Power Supply Rejection                   |                                                                                 | —            | 2.1        | —               | mV/V   |

| External Reference (REFBE =              | = 0)                                                                            |              |            |                 |        |

| Input Voltage Range                      |                                                                                 | 0            | —          | V <sub>DD</sub> | V      |

| Input Current                            | Sample Rate = 200 ksps; V <sub>REF</sub> = 1.5 V                                |              | 2.4        |                 | μA     |

| Bias Generators                          |                                                                                 |              | -          |                 |        |

| ADC Bias Generator                       | BIASE = 1                                                                       |              | 22         |                 | μA     |

| Power Consumption (Internal)             |                                                                                 | —            | 35         | —               | μA     |

#### **Table 2.8. Reset Electrical Characteristics**

-40 to +125 °C unless otherwise specified.

| Parameter                                              | Conditions                                                                                                                                | Min                         | Тур                     | Мах                         | Units                |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------|-----------------------------|----------------------|

| RST Output Low Voltage                                 | I <sub>OL</sub> = 8.5 mA, V <sub>DD</sub> =<br>2.1 V                                                                                      | _                           | _                       | 0.8                         | V                    |

| RST Input High Voltage                                 |                                                                                                                                           | 0.7 x<br>V <sub>REGIN</sub> |                         |                             | V                    |

| RST Input Low Voltage                                  |                                                                                                                                           |                             |                         | 0.3 x<br>V <sub>REGIN</sub> | V                    |

| RST Input Pullup Impedance                             | $V_{\text{REGIN}} = 1.8 \text{ V}$ $V_{\text{REGIN}} = 2.7 \text{ V}$ $V_{\text{REGIN}} = 3.3 \text{ V}$ $V_{\text{REGIN}} = 5 \text{ V}$ |                             | 330<br>160<br>130<br>80 |                             | kΩ<br>kΩ<br>kΩ<br>kΩ |

| Missing Clock Detector Timeout                         | Time from last system<br>clock rising edge to reset<br>initiation                                                                         | 100                         | 350                     | 650                         | μs                   |

| Reset Time Delay (T <sub>PORDelay</sub> ) <sup>1</sup> | Delay between release<br>of any reset source and<br>code execution at loca-<br>tion 0x0000                                                |                             |                         | 350                         | μs                   |

| Minimum RST Low Time to Generate a System Reset        |                                                                                                                                           | 10                          | _                       | _                           | μs                   |

| V <sub>DD</sub> Monitor (VDDMON0)                      |                                                                                                                                           |                             |                         | •                           |                      |

| Low Threshold (V <sub>RST-LOW</sub> ) <sup>1,2,3</sup> | C8051F52x/53x<br>C8051F52xA/53xA<br>C8051F52x-C/53x-C                                                                                     | 1.8<br>1.65<br>1.65         | 1.9<br>1.75<br>1.75     | 2.0<br>1.8<br>1.8           | V<br>V<br>V          |

| High Threshold (V <sub>RST-HIGH</sub> ) <sup>3</sup>   | C8051F52x/53x<br>C8051F52xA/53xA<br>C8051F52x-C/53x-C                                                                                     | 2.1<br>2.25<br>2.25         | 2.2<br>2.3<br>2.3       | 2.3<br>2.4<br>2.45          | V<br>V<br>V          |

| Turn-on Time                                           |                                                                                                                                           | _                           | 83                      |                             | μs                   |

| Supply Current                                         | V <sub>DD</sub> = 2.1 V                                                                                                                   | _                           | 1                       | 2                           | μA                   |

| Level-Sensitive V <sub>DD</sub> Monitor (VDDMC         | <b>DN1</b> ) <sup>1</sup>                                                                                                                 |                             |                         | •                           |                      |

| Threshold (V <sub>RST1</sub> ) <sup>1,2,3</sup>        | C8051F52x-C/53x-C                                                                                                                         | 1.6                         | 1.75                    | 1.9                         | V                    |

| Supply Current                                         | C8051F52x-C/53x-C                                                                                                                         |                             | 3                       | 6                           | μA                   |

| Notes:<br>1. Refer to Section "20. Device Specific     | Behavior" on page 210.                                                                                                                    |                             |                         |                             |                      |

- Refer to Section "20. Device Specific Behavior" on page 210.

The POR threshold (V<sub>RST</sub>) is V<sub>RST-LOW</sub> or V<sub>RST1</sub>, whichever is higher.

The V<sub>RST</sub> threshold for power fail / brownout is the higher of VDDMON0 and VDDMON1 thresholds, if both are enabled.

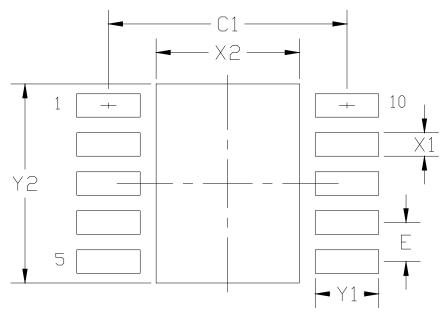

Figure 3.3. DFN-10 Landing Diagram

|                   | Dimension                                                                              | Min                                                                                                | Max                                          |

|-------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------|

|                   | C1                                                                                     | 2.90                                                                                               | 3.00                                         |

|                   | E                                                                                      | 0.50                                                                                               | BSC.                                         |

|                   | X1                                                                                     | 0.20                                                                                               | 0.30                                         |

|                   | X2                                                                                     | 1.70                                                                                               | 1.80                                         |

|                   | Y1                                                                                     | 0.70                                                                                               | 0.80                                         |

|                   | Y2                                                                                     | 2.45                                                                                               | 2.55                                         |

| 2.                | This land pattern desig                                                                | are in millimeters (mm) unles                                                                      |                                              |

| 3.<br><u>Sten</u> | All metal pads are to be<br>between the solder ma<br>way around the pad.<br>cil Design | pe non-solder mask defined (N<br>ask and the metal pad is to be<br>r-cut and electro-polished ster | NSMD). Clearance<br>ε 60 μm minimum, all the |

**9.** The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## SFR Definition 6.1. REG0CN: Regulator Control

| R/W      | R/W            | R            | R/W           | R            | R       | R    | R            | Reset Value |

|----------|----------------|--------------|---------------|--------------|---------|------|--------------|-------------|

| REGDIS   | 8 Reserved     |              | REG0MD        |              |         |      | DROPOUT      | 01010000    |

| Bit7     | Bit6           | Bit5         | Bit4          | Bit3         | Bit2    | Bit1 | Bit0         |             |

|          |                |              |               |              |         |      | SFR Address: | 0xC9        |

|          |                |              |               |              |         |      |              |             |

| Bit7:    | REGDIS: Vo     | Itage Regu   | lator Disable | e Bit.       |         |      |              |             |

|          | This bit disat | oles/enable  | s the Voltag  | e Regulato   | r.      |      |              |             |

|          | 0: Voltage Ro  | egulator Er  | abled.        |              |         |      |              |             |

|          | 1: Voltage Re  | egulator Di  | sabled.       |              |         |      |              |             |

| Bit6:    | RESERVED       | . Read = 11  | o. Must write | e 1b.        |         |      |              |             |

| Bit5:    | UNUSED. R      | ead = 0b. V  | Vrite = don't | care.        |         |      |              |             |

| Bit4:    | REGOMD: V      | oltage Reg   | ulator Mode   | Select Bit.  |         |      |              |             |

|          | This bit selec | cts the Volt | age Regulat   | or output vo | oltage. |      |              |             |

|          | 0: Voltage R   | egulator ou  | tput is 2.1 V |              |         |      |              |             |

|          | 1: Voltage R   | egulator ou  | tput is 2.6 V | ' (default). |         |      |              |             |

| Bits3–1: | UNUSED. R      | ead = 000b   | o. Write = do | n't care.    |         |      |              |             |

| Bit0:    | DROPOUT:       | Voltage Re   | gulator Drop  | out Indicat  | or Bit. |      |              |             |

|          | 0: Voltage R   | egulator is  | not in dropo  | ut.          |         |      |              |             |

|          | 1: Voltage R   | egulator is  | in or near dı | ropout.      |         |      |              |             |

|          |                |              |               |              |         |      |              |             |

#### 12.1.2. Flash Erase Procedure

The Flash memory can be programmed by software using the MOVX write instruction with the address and data byte to be programmed provided as normal operands. Before writing to Flash memory using MOVX, Flash write operations must be enabled by: (1) setting the PSWE Program Store Write Enable bit (PSCTL.0) to logic 1 (this directs the MOVX writes to target Flash memory); and (2) Writing the Flash key codes in sequence to the Flash Lock register (FLKEY). The PSWE bit remains set until cleared by software.

A write to Flash memory can clear bits to logic 0 but cannot set them; only an erase operation can set bits to logic 1 in Flash. A byte location to be programmed should be erased before a new value is written. The Flash memory is organized in 512-byte pages. The erase operation applies to an entire page (setting all bytes in the page to 0xFF). To erase an entire 512-byte page, perform the following steps:

- 1. Disable interrupts (recommended).

- 2. Write the first key code to FLKEY: 0xA5.

- 3. Write the second key code to FLKEY: 0xF1.

- 4. Set the PSEE bit (register PSCTL).

- 5. Set the PSWE bit (register PSCTL).

- 6. Using the MOVX instruction, write a data byte to any location within the 512-byte page to be erased.

- 7. Clear the PSWE and PSEE bits.

- 8. Re-enable interrupts.

- 12.1.3. Flash Write Procedure

Flash bytes are programmed by software with the following sequence:

- 1. Disable interrupts.

- 2. Write the first key code to FLKEY: 0xA5.

- 3. Write the second key code to FLKEY: 0xF1.

- 4. Set the PSWE bit (register PSCTL).

- 5. Clear the PSEE bit (register PSCTL).

- 6. Using the MOVX instruction, write a single data byte to the desired location within the 512-byte sector.

- 7. Clear the PSWE bit.

- 8. Re-enable interrupts.

Steps 2–7 must be repeated for each byte to be written. After Flash writes are complete, PSWE should be cleared so that MOVX instructions do not target program memory.

5. Add address bounds checking to the routines that write or erase Flash memory to ensure that a routine called with an illegal address does not result in modification of the Flash.

#### 12.2.3. System Clock

- 1. If operating from an external crystal, be advised that crystal performance is susceptible to electrical interference and is sensitive to layout and to changes in temperature. If the system is operating in an electrically noisy environment, use the internal oscillator or use an external CMOS clock.

- 2. If operating from the external oscillator, switch to the internal oscillator during Flash write or erase operations. The external oscillator can continue to run, and the CPU can switch back to the external oscillator after the Flash operation has completed.

Additional Flash recommendations and example code can be found in application note "AN201: Writing to Flash from Firmware," available from the Silicon Laboratories website.

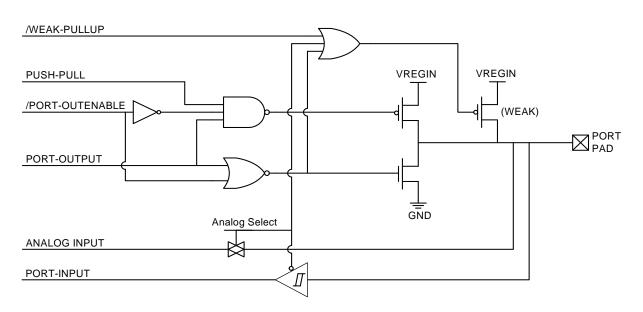

Figure 13.2. Port I/O Cell Block Diagram

|                   |      |        | P       | <b>0</b> |          |                                                     |

|-------------------|------|--------|---------|----------|----------|-----------------------------------------------------|

| SF Signals DFN 10 | VREF |        | o XTAL1 | XTAL2    | CNVSTR   |                                                     |

| PIN I/O           | 0    | 1      | 2       | 3        | 4 5      |                                                     |

| ТХ0               |      |        |         |          |          | C8051F52xA/F52x-C                                   |

| RX0               |      |        |         |          |          | devices                                             |

| ТХ0               |      |        |         |          |          | C8051F52x devices                                   |

| RX0               |      |        |         |          |          | Coustin S2X devices                                 |

| SCK               |      |        |         |          |          |                                                     |

| MISO              |      |        |         |          |          |                                                     |

| MOSI              |      |        |         |          |          |                                                     |

| NSS*              |      |        |         |          |          |                                                     |

| LIN-TX            |      |        |         |          |          |                                                     |

| LIN-RX            |      |        |         |          |          |                                                     |

| CP0               |      |        |         |          |          |                                                     |

| CP0A              |      |        |         |          |          |                                                     |

| /SYSCLK           |      |        |         |          |          |                                                     |

| CEX0              |      |        |         |          |          |                                                     |

| CEX1              |      |        |         |          |          |                                                     |

| CEX2              |      |        |         |          |          |                                                     |

| ECI               |      |        |         |          |          |                                                     |

| ТО                |      |        |         |          |          |                                                     |

| T1                |      |        |         |          |          |                                                     |

|                   | 0    | 1      | 1       | 0        | 0 0      |                                                     |

|                   | -    |        |         |          | = 0x06   |                                                     |

|                   |      |        | . [9    |          |          | 1                                                   |

|                   | Poi  | rt pir | n pot   | tenti    | ally as  | ignable to peripheral                               |

| SF Signals        | Spe  | ecial  | Fur     | nctio    | on Signa | als are not assigned by the crossbar.               |

|                   | Wr   | nen t  | hese    | e sig    | gnals ar | e enabled, the Crossbar must be manually configured |

|                   |      |        |         |          |          | ding port pins.                                     |

Note: 4-Wire SPI Only.

#### Figure 13.6. Crossbar Priority Decoder with Some Pins Skipped (DFN 10)

Registers XBR0 and XBR1 are used to assign the digital I/O resources to the physical I/O Port pins. Note that when the SMBus is selected, the Crossbar assigns both pins associated with the SMBus (SDA and SCL); when the UART is selected, the Crossbar assigns both pins associated with the UART (TX and RX). UART0 pin assignments are fixed for bootloading purposes: UART TX0 is always assigned to P0.3 or P0.4\*; UART RX0 is always assigned to P0.4 or P0.5\*. Standard Port I/Os appear contiguously starting at P0.0 after prioritized functions and skipped pins are assigned.

**Note:** Refer to Section "20. Device Specific Behavior" on page 210.

In addition to performing general purpose I/O, P0 and P1 can generate a port match event if the logic levels of the Port's input pins match a software controlled value. A port match event is generated if (P0 & P0MASK) does not equal (P0MATCH & P0MASK) or if (P1 & P1MASK) does not equal (P1MATCH & P1MASK). This allows Software to be notified if a certain change or pattern occurs on P0 or P1 input pins regardless of the XBRn settings. A port match event can cause an interrupt if EMAT (EIE2.1) is set to 1 or cause the internal oscillator to awaken from SUSPEND mode. See Section "14.1.1. Internal Oscillator Suspend Mode" on page 136 for more information.

### SFR Definition 13.3. P0: Port0

| R/W      | R/W                                                                                                                                  | R/W                                                                    | R/W                                          | R/W                           | R/W        | R/W      | R/W          | Reset Value        |

|----------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------|-------------------------------|------------|----------|--------------|--------------------|

| P0.7     | P0.6                                                                                                                                 | P0.5                                                                   | P0.4                                         | P0.3                          | P0.2       | P0.1     | P0.0         |                    |

| Bit7     | Bit6                                                                                                                                 | Bit5                                                                   | Bit4                                         | Bit3                          | Bit2       | Bit1     | Bit0         | Bit<br>Addressable |

|          |                                                                                                                                      |                                                                        |                                              |                               |            |          | SFR Address: | 0x80               |

| Bits7–0: | <b>P0.[7:0]</b><br>Write - Outpu<br>0: Logic Low<br>1: Logic High<br>Read - Alwa<br>pin when con<br>0: P0.n pin is<br>1: P0.n pin is | y Output.<br>h Output (hi<br>ys reads 0<br>nfigured as<br>s logic low. | gh impedar<br>if selected a<br>digital input | nce if corres<br>as analog in | ponding PC | )MDOUT.n | ,            | ads Port           |

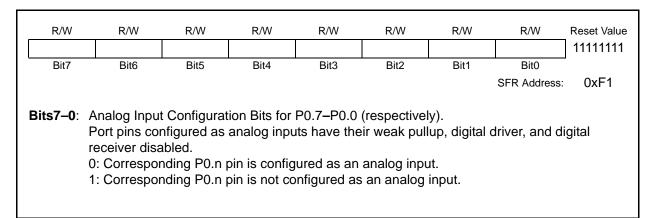

### SFR Definition 13.4. P0MDIN: Port0 Input Mode

## 14. Oscillators

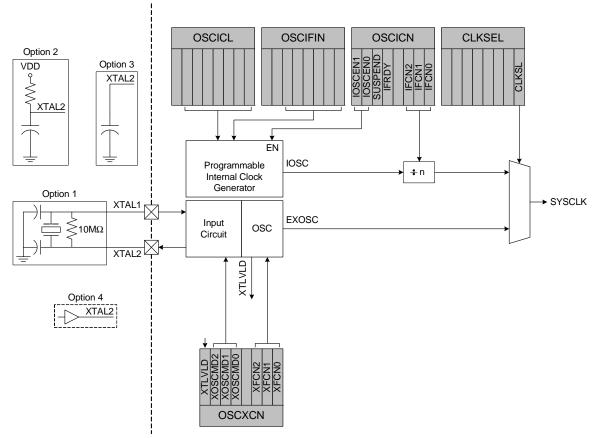

C8051F52x/F52xA/F53x/F53xA devices include a programmable internal oscillator, an external oscillator drive circuit. The internal oscillator can be enabled/disabled and calibrated using the OSCICN and OSCICL registers, as shown in Figure 14.1. The system clock (SYSCLK) can be derived from the internal oscillator, external oscillator circuit. Oscillator electrical specifications are given in Table 2.11 on page 34.

### 14.1. Programmable Internal Oscillator

All C8051F52x/53x devices include a programmable internal oscillator that defaults as the system clock after a system reset. The internal oscillator period can be programmed via the OSCICL and OSCIFIN registers, shown in SFR Definition 14.2 and SFR Definition 14.3. On C8051F52x/53x devices, OSCICL and OSCIFIN are factory calibrated to obtain a 24.5 MHz frequency.

Electrical specifications for the precision internal oscillator are given in Table 2.11 on page 34. Note that the system clock may be derived from the programmed internal oscillator divided by 1, 2, 4, 8, 16, 32, 64, or 128 as defined by the IFCN bits in register OSCICN. The divide value defaults to 128 following a reset.

### SFR Definition 14.1. OSCICN: Internal Oscillator Control

| R/W      | R/W                                                                                                                                                   | R/W                                             | R                                                                                              | R                                                                                | R/W                                                                                                          | R/W                                 | R/W          | Reset Value |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------|-------------|--|

| IOSCEN   | 1 IOSCEN0                                                                                                                                             | SUSPEND                                         | IFRDY                                                                                          |                                                                                  | IFCN2                                                                                                        | IFCN1                               | IFCN0        | 11000000    |  |

| Bit7     | Bit6                                                                                                                                                  | Bit5                                            | Bit4                                                                                           | Bit3                                                                             | Bit2                                                                                                         | Bit1                                | Bit0         |             |  |

|          |                                                                                                                                                       |                                                 |                                                                                                |                                                                                  |                                                                                                              |                                     | SFR Address: | 0xB2        |  |

| Bits7–6: | <ul> <li>-6: IOSCEN[1:0]: Internal Oscillator Enable Bits.</li> <li>00: Oscillator Disabled.</li> <li>01: Reserved.</li> <li>10: Reserved.</li> </ul> |                                                 |                                                                                                |                                                                                  |                                                                                                              |                                     |              |             |  |

|          | 10: Reserve                                                                                                                                           |                                                 |                                                                                                | ada and Di                                                                       | ablad in C                                                                                                   |                                     | ala          |             |  |

| Bit5:    | 11: Oscillato<br>SUSPEND:<br>Setting this b<br>lator resume                                                                                           | Internal Osci<br>pit to logic 1 p               | llator Susp<br>places the                                                                      | end Enable                                                                       | e Bit.<br>cillator in Sl                                                                                     | USPEND r                            | node. The in |             |  |

| Bit4:    | IFRDY: Inter<br>0: Internal O                                                                                                                         | nal Oscillato                                   | r Frequenc                                                                                     | cy Ready Fl<br>at program                                                        | ag.<br>ned freque                                                                                            | ncy.                                | C            |             |  |

| Bit3:    | UNUSED. R                                                                                                                                             |                                                 |                                                                                                |                                                                                  |                                                                                                              |                                     |              |             |  |

| Bits2–0: | 101: SYSCL<br>110: SYSCL                                                                                                                              | K derived fro<br>K derived fro<br>K derived fro | m Internal<br>m Internal<br>m Internal<br>m Internal<br>m Internal<br>m Internal<br>m Internal | Oscillator<br>Oscillator<br>Oscillator<br>Oscillator<br>Oscillator<br>Oscillator | divided by a<br>divided by a<br>divided by a<br>divided by a<br>divided by a<br>divided by a<br>divided by a | 64.<br>32.<br>16.<br>8.<br>4.<br>2. | lt).         |             |  |

|          |                                                                                                                                                       |                                                 |                                                                                                |                                                                                  |                                                                                                              |                                     |              |             |  |

## SFR Definition 17.3. LINCF Control Mode Register

| R/W   | R/W                                          | R/W          | R/W        | R/W         | R/W          | R/W       | R/W          | Reset Value |  |  |

|-------|----------------------------------------------|--------------|------------|-------------|--------------|-----------|--------------|-------------|--|--|

| LINEN | MODE                                         | ABAUD        |            |             |              |           |              | 00000000    |  |  |

| Bit7  | Bit6                                         | Bit5         | Bit4       | Bit3        | Bit2         | Bit1      | Bit0         | ,<br>,      |  |  |

|       |                                              |              |            |             |              |           | SFR Address: | 0x95        |  |  |

| Bit7: |                                              |              |            |             |              |           |              |             |  |  |

|       | 0: LINO is di                                |              |            |             |              |           |              |             |  |  |

| -     | 1: LIN0 is er                                |              |            |             |              |           |              |             |  |  |

| Bit6: | MODE: LIN                                    |              |            |             |              |           |              |             |  |  |

|       | 0: LIN0 oper                                 |              |            |             |              |           |              |             |  |  |

|       | 1: LIN0 oper                                 | rates in Mas | ter mode.  |             |              |           |              |             |  |  |

| Bit5: | ABAUD: LIN                                   | Mode Auto    | omatic Bau | d Rate Sele | ction (slave | e mode or | nly).        |             |  |  |

|       | 0: Manual b                                  |              |            |             | ,            |           | • /          |             |  |  |

|       |                                              |              |            |             |              |           |              |             |  |  |

|       | 1: Automatic baud rate selection is enabled. |              |            |             |              |           |              |             |  |  |

### SFR Definition 17.13. LIN0ST: LIN0 STATUS Register

| R      | R              | R     | R           | R/W           | R             | R               | R            | Reset Value       |  |

|--------|----------------|-------|-------------|---------------|---------------|-----------------|--------------|-------------------|--|

| ACTIVE | IDLTOUT        | ABORT | DTREQ       | LININT        | ERROR         | WAKEUP          | DONE         | 00000000          |  |

| Bit7   | Bit6           | Bit5  | Bit4        | Bit3          | Bit2          | Bit1            | Bit0         | _                 |  |

|        |                |       |             |               |               |                 | Address      | : 0x09 (indirect) |  |

|        |                |       |             |               |               |                 |              |                   |  |

| Bit7:  |                |       |             |               |               |                 |              |                   |  |

|        | 0: No transm   |       |             |               |               |                 |              |                   |  |

| 5.40   | 1: Transmiss   |       |             |               |               |                 |              |                   |  |

| Bit6:  | IDLTOUT: B     |       | •           |               | only).        |                 |              |                   |  |

|        | 0: The bus h   |       |             |               | oconde bu     | t the bus is n  | at vot in Sl | oon modo          |  |

| Bit5:  | ABORT: Abo     |       |             |               |               |                 | or yer in Si | eep mode.         |  |

| Dito.  |                |       |             |               |               | topped. This    | bit is reset | to 0 after        |  |

|        |                |       |             |               |               | ding transmis   |              |                   |  |

|        |                |       |             |               |               | st transmissi   |              | STOP bit          |  |

|        | (LIN0CTRL.     | ,     |             |               |               |                 |              |                   |  |

| Bit4:  | DTREQ: Dat     |       |             |               |               |                 |              |                   |  |

|        | 0: Data ident  |       |             |               |               |                 |              |                   |  |

| D:40.  | 1: Data ident  |       |             | J.            |               |                 |              |                   |  |

| Bit3:  | LININT: Inter  |       |             | hit is cloars | d by cottin   | g RSTINT (L     |              | 2)                |  |

|        | 1: There is a  |       |             |               | su by setting | g KSTINT (L     |              | )                 |  |

| Bit2:  | ERROR: Co      |       |             |               |               |                 |              |                   |  |

|        |                |       |             |               | ed by setti   | ng RSTERR       | (LIN0CTR     | L.2)              |  |

|        | 1: An error h  |       |             |               |               | C               | ·            | ,                 |  |

| Bit1:  | WAKEUP: V      | •     |             |               |               |                 |              |                   |  |

|        |                |       |             |               |               | een received    | ł.           |                   |  |

| D'40   | 1: A wakeup    |       |             |               | been recei    | ived.           |              |                   |  |

| Bit0:  | DONE: Tran     |       |             |               | haan atarta   | d This hit is   | alcored at   | the start of      |  |

|        | a transmissi   |       | in progress | or nas not    | Deen starte   | ed. This bit is | cleared at   | the start of      |  |

|        | 1: The current |       | sion is com | nlete         |               |                 |              |                   |  |

|        |                |       |             |               |               |                 |              |                   |  |

|        |                |       |             |               |               |                 |              |                   |  |

|        |                |       |             |               |               |                 |              |                   |  |

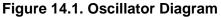

#### 18.1.2. Mode 1: 16-bit Counter/Timer

Mode 1 operation is the same as Mode 0, except that the counter/timer registers use all 16 bits. The counter/timers are enabled and configured in Mode 1 in the same manner as for Mode 0.

#### 18.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload

Mode 2 configures Timer 0 and Timer 1 to operate as 8-bit counter/timers with automatic reload of the start value. TL0 holds the count and TH0 holds the reload value. When the counter in TL0 overflows from all ones to 0x00, the timer overflow flag TF0 (TCON.5) is set and the counter in TL0 is reloaded from TH0. If Timer 0 interrupts are enabled, an interrupt will occur when the TF0 flag is set. The reload value in TH0 is not changed. TL0 must be initialized to the desired value before enabling the timer for the first count to be correct. When in Mode 2, Timer 1 operates identically to Timer 0.

Both counter/timers are enabled and configured in Mode 2 in the same manner as Mode 0. Setting the TR0 bit (TCON.4) enables the timer when either GATE0 (TMOD.3) is logic 0 or when the input signal INT0 is active as defined by bit IN0PL in register IT01CF (see Section "10.5. External Interrupts" on page 104 for details on the external input signals INT0 and INT0).

Figure 18.2. T0 Mode 2 Block Diagram

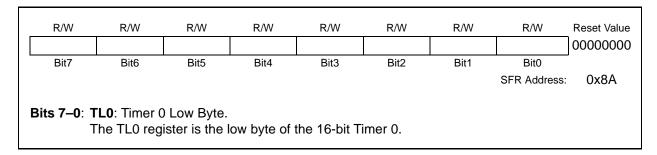

### SFR Definition 18.4. TL0: Timer 0 Low Byte

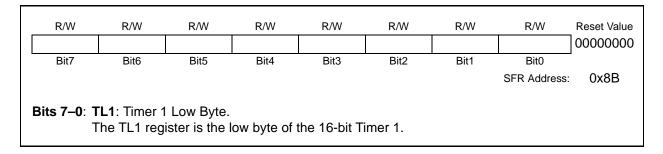

### SFR Definition 18.5. TL1: Timer 1 Low Byte

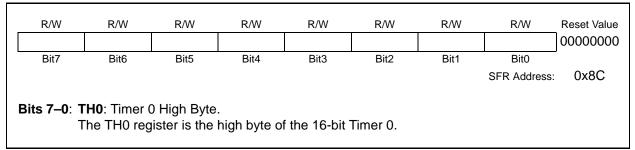

### SFR Definition 18.6. TH0: Timer 0 High Byte

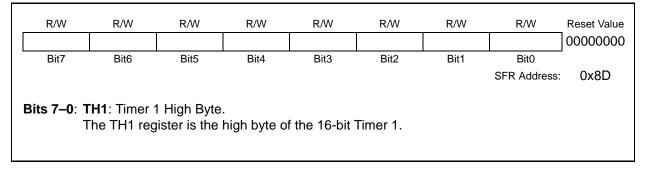

### SFR Definition 18.7. TH1: Timer 1 High Byte

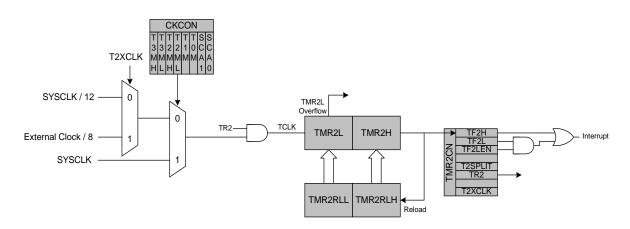

### 18.2. Timer 2

Timer 2 is a 16-bit timer formed by two 8-bit SFRs: TMR2L (low byte) and TMR2H (high byte). Timer 2 may operate in 16-bit auto-reload mode or (split) 8-bit auto-reload mode. The T2SPLIT bit (TMR2CN.3) defines the Timer 2 operation mode. Timer 2 can also be used in Capture Mode to measure the RTC0 clock frequency or the External Oscillator clock frequency.

Timer 2 may be clocked by the system clock, the system clock divided by 12, or the external oscillator source divided by 8. The external oscillator source divided by 8 is synchronized with the system clock.

#### 18.2.1. 16-bit Timer with Auto-Reload

When T2SPLIT (TMR2CN.3) is zero, Timer 2 operates as a 16-bit timer with auto-reload. Timer 2 can be clocked by SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. As the 16-bit timer register increments and overflows from 0xFFFF to 0x0000, the 16-bit value in the Timer 2 reload registers (TMR2RLH and TMR2RLL) is loaded into the Timer 2 register as shown in Figure 18.4, and the Timer 2 High Byte Overflow Flag (TMR2CN.7) is set. If Timer 2 interrupts are enabled (if IE.5 is set), an interrupt will be generated on each Timer 2 overflow. Additionally, if Timer 2 interrupts are enabled and the TF2LEN bit is set (TMR2CN.5), an interrupt will be generated each time the lower 8 bits (TMR2L) overflow from 0xFF to 0x00.

Figure 18.4. Timer 2 16-Bit Mode Block Diagram

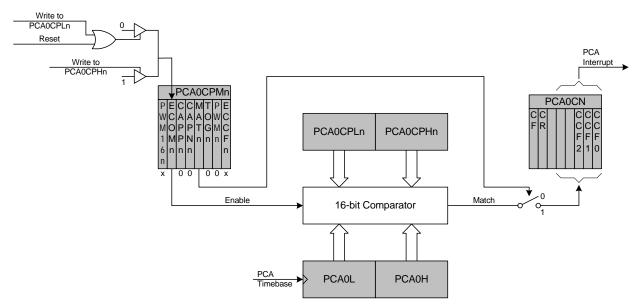

#### 19.2.2. Software Timer (Compare) Mode

In Software Timer mode, the PCA counter/timer value is compared to the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1 and an interrupt request is generated if CCF interrupts are enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Setting the ECOMn and MATn bits in the PCA0CPMn register enables Software Timer mode.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to 0; writing to PCA0CPHn sets ECOMn to 1.

Figure 19.5. PCA Software Timer Mode Diagram

#### 19.3.2. Watchdog Timer Usage

To configure the WDT, perform the following tasks:

- Disable the WDT by writing a 0 to the WDTE bit.

- Select the desired PCA clock source (with the CPS2-CPS0 bits).

- Load PCA0CPL2 with the desired WDT update offset value.

- Configure the PCA Idle mode (set CIDL if the WDT should be suspended while the CPU is in Idle mode).

- Enable the WDT by setting the WDTE bit to 1.

The PCA clock source and Idle mode select cannot be changed while the WDT is enabled. The watchdog timer is enabled by setting the WDTE or WDLCK bits in the PCA0MD register. When WDLCK is set, the WDT cannot be disabled until the next system reset. If WDLCK is not set, the WDT is disabled by clearing the WDTE bit.

The WDT is enabled following any reset. The PCA0 counter clock defaults to the system clock divided by 12, PCA0L defaults to 0x00, and PCA0CPL2 defaults to 0x00. Using Equation 19.4, this results in a WDT timeout interval of 3072 system clock cycles. Table 19.3 lists some example timeout intervals for typical system clocks.

| System Clock (Hz)                                     | PCA0CPL2 | Timeout Interval (ms) |

|-------------------------------------------------------|----------|-----------------------|

| 24,500,000                                            | 255      | 32.1                  |

| 24,500,000                                            | 128      | 16.2                  |

| 24,500,000                                            | 32       | 4.1                   |

| 18,432,000                                            | 255      | 42.7                  |

| 18,432,000                                            | 128      | 21.5                  |

| 18,432,000                                            | 32       | 5.5                   |

| 11,059,200                                            | 255      | 71.1                  |

| 11,059,200                                            | 128      | 35.8                  |

| 11,059,200                                            | 32       | 9.2                   |

| 3,062,500                                             | 255      | 257                   |

| 3,062,500                                             | 128      | 129.5                 |

| 3,062,500                                             | 32       | 33.1                  |

| 191,406 <sup>2</sup>                                  | 255      | 4109                  |

| 191,406 <sup>2</sup>                                  | 128      | 2070                  |

| 191,406 <sup>2</sup>                                  | 32       | 530                   |

| 32,000                                                | 255      | 24576                 |

| 32,000                                                | 128      | 12384                 |

| 32,000                                                | 32       | 3168                  |

| Notes:<br>1. Assumes SYSCLK /<br>value of 0x00 at the |          | k source, and a PCA0L |

#### Table 19.3. Watchdog Timer Timeout Intervals<sup>1</sup>

2. Internal oscillator reset frequency.

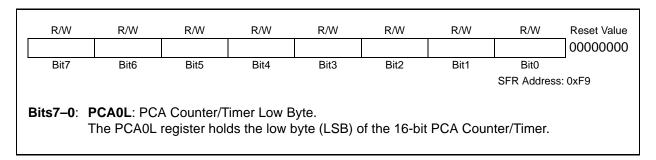

#### SFR Definition 19.4. PCA0L: PCA Counter/Timer Low Byte

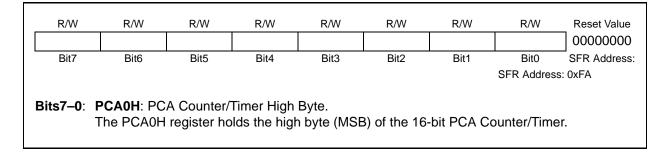

#### SFR Definition 19.5. PCA0H: PCA Counter/Timer High Byte

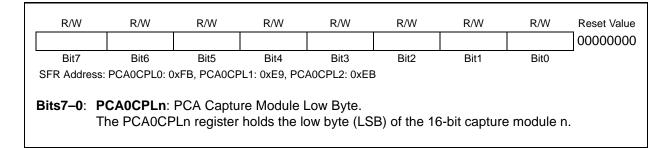

### SFR Definition 19.6. PCA0CPLn: PCA Capture Module Low Byte

### SFR Definition 19.7. PCA0CPHn: PCA Capture Module High Byte