# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                           |

|----------------------------|------------------------------------------------------------------|

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | LINbus, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT               |

| Number of I/O              | 16                                                               |

| Program Memory Size        | 2KB (2K x 8)                                                     |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 256 x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.25V                                                     |

| Data Converters            | A/D 16x12b                                                       |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                               |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                  |

| Supplier Device Package    | 20-TSSOP                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f536a-itr |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 8.3.2. Stop Mode                                                    | 90  |

|---------------------------------------------------------------------|-----|

| 8.3.3. Suspend Mode                                                 |     |

| 9. Memory Organization and SFRs                                     | 92  |

| 9.1. Program Memory                                                 |     |

| 9.2. Data Memory                                                    |     |

| 9.3. General Purpose Registers                                      | 93  |

| 9.4. Bit Addressable Locations                                      | 93  |

| 9.5. Stack                                                          | 93  |

| 9.6. Special Function Registers                                     | 93  |

| 10. Interrupt Handler                                               | 98  |

| 10.1. MCU Interrupt Sources and Vectors                             | 98  |

| 10.2. Interrupt Priorities                                          |     |

| 10.3. Interrupt Latency                                             | 98  |

| 10.4. Interrupt Register Descriptions                               | 100 |

| 10.5. External Interrupts                                           | 104 |

| 11. Reset Sources                                                   |     |

| 11.1. Power-On Reset                                                |     |

| 11.2. Power-Fail Reset / VDD Monitors (VDDMON0 and VDDMON1)         | 108 |

| 11.2.1. VDD Monitor Thresholds and Minimum VDD                      | 108 |

| 11.3. External Reset                                                |     |

| 11.4. Missing Clock Detector Reset                                  |     |

| 11.5. Comparator Reset                                              | 110 |

| 11.6. PCA Watchdog Timer Reset                                      | 110 |

| 11.7. Flash Error Reset                                             | 110 |

| 11.8. Software Reset                                                | 111 |

| 12. Flash Memory                                                    | 113 |

| 12.1. Programming The Flash Memory                                  |     |

| 12.1.1. Flash Lock and Key Functions                                |     |

| 12.1.2. Flash Erase Procedure                                       |     |

| 12.1.3. Flash Write Procedure                                       |     |

| 12.2. Flash Write and Erase Guidelines                              | -   |

| 12.2.1. V <sub>DD</sub> Maintenance and the V <sub>DD</sub> monitor |     |

| 12.2.2. PSWE Maintenance                                            |     |

| 12.2.3. System Clock                                                |     |

| 12.3. Non-volatile Data Storage                                     |     |

| 12.4. Security Options                                              |     |

| 13. Port Input/Output                                               |     |

| 13.1. Priority Crossbar Decoder                                     |     |

| 13.2. Port I/O Initialization                                       |     |

| 13.3. General Purpose Port I/O                                      |     |

| 14. Oscillators                                                     |     |

| 14.1. Programmable Internal Oscillator                              |     |

| 14.1.1. Internal Oscillator Suspend Mode                            |     |

| 14.2. External Oscillator Drive Circuit                             |     |

| 14.2.1. Clocking Timers Directly Through the External Oscillator    | 139 |

#### 1.9. Port Input/Output

C8051F52x/F52xA/F53x/F53xA devices include up to 16 I/O pins. Port pins are organized as two bytewide ports. The port pins behave like typical 8051 ports with a few enhancements. Each port pin can be configured as a digital or analog I/O pin. Pins selected as digital I/O can be configured for push-pull or open-drain operation. The "weak pullups" that are fixed on typical 8051 devices may be globally disabled to save power.

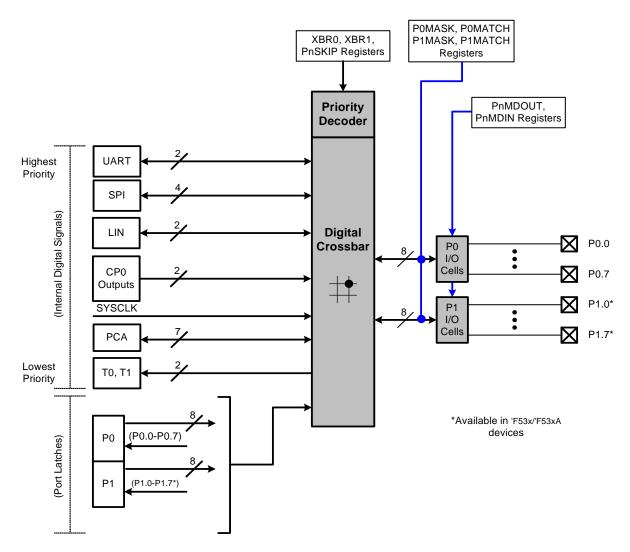

The Digital Crossbar allows mapping of internal digital system resources to port I/O pins. On-chip counter/timers, serial buses, hardware interrupts, and other digital signals can be configured to appear on the port pins using the Crossbar control registers. This allows the user to select the exact mix of general-purpose port I/O, digital, and analog resources needed for the application.

Figure 1.9. Port I/O Functional Block Diagram

#### Table 2.6. Voltage Regulator Electrical Specifications

$V_{DD}$  = 2.1 or 2.6 V; -40 to +125 °C unless otherwise specified.

| Parameter                                                                    | Conditions                                                                                                                                     | Min                      | Тур  | Max  | Units |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|------|-------|

| Input Voltage Range (V <sub>REGIN</sub> )                                    | C8051F52x/53x<br>C8051F52xA/53xA                                                                                                               | 2.7 <sup>1</sup>         | _    | 5.25 | V     |

|                                                                              | V <sub>DD</sub> connected to V <sub>REGIN</sub>                                                                                                | 1.8                      | —    | 2.7  |       |

|                                                                              | V <sub>DD</sub> not connected to V <sub>REGIN</sub><br>C8051F52x-C/53x-C                                                                       | 2.2 <sup>2</sup>         | —    | 5.25 |       |

|                                                                              | V <sub>DD</sub> connected to V <sub>REGIN</sub>                                                                                                | 2.0                      | _    | 2.75 |       |

|                                                                              | V <sub>DD</sub> not connected to V <sub>REGIN</sub>                                                                                            | 2.2 <sup>2</sup>         | —    | 5.25 |       |

| Dropout Voltage (V <sub>DO</sub> )                                           | Output Current = 1-50 mA                                                                                                                       | —                        | 10   |      | mV/mA |

| Output Voltage (V <sub>DD</sub> )                                            | Output Current = 1 to 50 mA                                                                                                                    |                          |      |      | V     |

|                                                                              | REG0MD = 0                                                                                                                                     | 2.0                      | 2.1  | 2.25 |       |

|                                                                              | REG0MD = 1                                                                                                                                     | 2.5                      | 2.6  | 2.75 |       |

| Bias Current                                                                 | 2.1 V operation<br>(REG0MD = 0; T = 25 °C)                                                                                                     | —                        | 1    | 5    | μA    |

|                                                                              | 2.6 V operation<br>(REG0MD = 1; T = 25 °C)                                                                                                     | _                        | 1    | 5    |       |

| Dropout Indicator Detection<br>Threshold                                     |                                                                                                                                                | —                        | 75   | _    | mV    |

| Output Voltage Temperature<br>Coefficient                                    |                                                                                                                                                | —                        | 0.25 | _    | mV/ºC |

| VREG Settling Time                                                           | 50 mA load with $V_{REGIN}$ = 2.4 V and $V_{DD}$ load capacitor of 4.8 µF                                                                      | —                        | 250  | _    | μs    |

| Notes:<br>1. The minimum input voltage is<br>2. The minimum input voltage is | s 2.7 V or V <sub>DD</sub> + V <sub>DO</sub> (max load), whichever is<br>s 2.2 V or V <sub>DD</sub> + V <sub>DO</sub> (max load), whichever is | s greater.<br>s greater. |      |      |       |

#### **Table 2.7. Comparator Electrical Characteristics**

$V_{\text{REGIN}} = 2.7-5.25$  V, -40 to +125 °C unless otherwise noted.

All specifications apply to both Comparator0 and Comparator1 unless otherwise noted.

| Parameter                                                      | Conditions            | Min   | Тур  | Max                    | Units |

|----------------------------------------------------------------|-----------------------|-------|------|------------------------|-------|

| Response Time:                                                 | CP0+ - CP0- = 100 mV  |       | 780  | —                      | ns    |

| Mode 0, Vcm <sup>1</sup> = 1.5 V                               | CP0+ - CP0- = -100 mV | _     | 980  | _                      | ns    |

| Response Time:                                                 | CP0+ - CP0- = 100 mV  | _     | 850  | _                      | ns    |

| Mode 1, Vcm <sup>1</sup> = 1.5 V                               | CP0+ - CP0- = -100 mV | —     | 1120 | —                      | ns    |

| Response Time:                                                 | CP0+ - CP0- = 100 mV  | —     | 870  | —                      | ns    |

| Mode 2, Vcm <sup>1</sup> = 1.5 V                               | CP0+ - CP0- = -100 mV | _     | 1310 | —                      | ns    |

| Response Time:                                                 | CP0+ - CP0- = 100 mV  | _     | 1980 | —                      | ns    |

| Mode 3, Vcm <sup>1</sup> = 1.5 V                               | CP0+ - CP0- = -100 mV | _     | 4770 | —                      | ns    |

| Common-Mode Rejection<br>Ratio                                 |                       |       | 3    | 9                      | mV/V  |

| Positive Hysteresis 1                                          | CP0HYP1-0 = 00        | _     | 0.7  | 2                      | mV    |

| Positive Hysteresis 2                                          | CP0HYP1-0 = 01        | 2     | 5    | 10                     | mV    |

| Positive Hysteresis 3                                          | CP0HYP1-0 = 10        | 5     | 10   | 20                     | mV    |

| Positive Hysteresis 4                                          | CP0HYP1-0 = 11        | 13    | 20   | 40                     | mV    |

| Negative Hysteresis 1                                          | CP0HYN1-0 = 00        |       | 0.7  | 2                      | mV    |

| Negative Hysteresis 2                                          | CP0HYN1-0 = 01        | 2     | 5    | 10                     | mV    |

| Negative Hysteresis 3                                          | CP0HYN1-0 = 10        | 5     | 10   | 20                     | mV    |

| Negative Hysteresis 4                                          | CP0HYN1-0 = 11        | 13    | 20   | 40                     | mV    |

| Inverting or Non-Inverting<br>Input Voltage Range <sup>2</sup> |                       | -0.25 |      | V <sub>DD</sub> + 0.25 | V     |

| Input Capacitance <sup>2</sup>                                 |                       | —     | 4    | —                      | pF    |

| Input Bias Current                                             |                       | _     | 0.5  | —                      | nA    |

| Input Offset Voltage                                           |                       | -15   |      | 15                     | mV    |

| Input Impedance                                                |                       | _     | 1.5  | —                      | kΩ    |

| Power Supply                                                   |                       |       |      |                        |       |

| Power Supply Rejection <sup>2</sup>                            |                       | _     | 0.2  | 4                      | mV/V  |

| Power-up Time                                                  |                       | -     | 2.3  | —                      | μs    |

|                                                                | Mode 0                | — —   | 6    | 30                     | μA    |

| Supply Current at DC                                           | Mode 1                | —     | 3    | 15                     | μA    |

| Supply Current at DC                                           | Mode 2                | — —   | 2    | 7.5                    | μA    |

|                                                                | Mode 3                |       | 0.3  | 3.8                    | μA    |

1. Vcm is the common-mode voltage on CP0+ and CP0-.

2. Guaranteed by design and/or characterization.

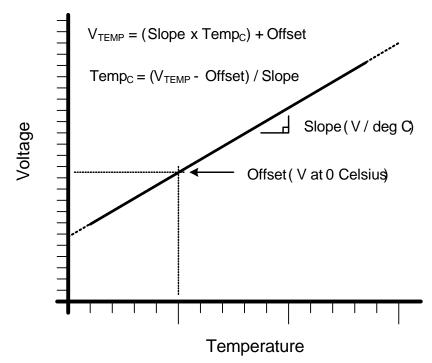

#### 4.2. Temperature Sensor

An on-chip temperature sensor is included on the C8051F52x/F52xA/F53x/F53xA devices which can be directly accessed via the ADC0 multiplexer. To use ADC0 to measure the temperature sensor, the ADC multiplexer channel should be configured to connect to the temperature sensor. The temperature sensor transfer function is shown in Figure 5.2. The output voltage ( $V_{TEMP}$ ) is the positive ADC input selected by bits AD0MX[4:0] in register ADC0MX. The TEMPE bit in register REF0CN enables/disables the temperature sensor, as described in SFR Definition 5.1. While disabled, the temperature sensor defaults to a high impedance state and any ADC measurements performed on the sensor will result in meaningless data. Refer to Table 5.1 for the slope and offset parameters of the temperature sensor.

Figure 4.2. Typical Temperature Sensor Transfer Function

### SFR Definition 4.8. ADC0CN: ADC0 Control

| R/W      | R/W                                                             | R/W          | R/W           | R/W                                                            | R/W          | R/W            | R/W           | Reset Value  |  |  |  |  |  |

|----------|-----------------------------------------------------------------|--------------|---------------|----------------------------------------------------------------|--------------|----------------|---------------|--------------|--|--|--|--|--|

| AD0EN    |                                                                 | ADOINT       | ADOBUSY       |                                                                | ADOLJST      | AD0CM1         | AD0CM0        | 00000000     |  |  |  |  |  |

| Bit7     | Bit6                                                            | Bit5         | Bit4          | Bit3                                                           | Bit2         | Bit1           | Bit0          | SFR Address: |  |  |  |  |  |

| Ditt     | (bit addressable) 0xE8                                          |              |               |                                                                |              |                |               |              |  |  |  |  |  |

|          |                                                                 |              |               |                                                                |              |                |               |              |  |  |  |  |  |

| Bit7:    | ADOEN: ADO                                                      | 0 Enable     | Bit           |                                                                |              |                |               |              |  |  |  |  |  |

| 2        | 0: ADC0 Disabled. ADC0 is in low-power shutdown.                |              |               |                                                                |              |                |               |              |  |  |  |  |  |

|          | 1: ADC0 Enabled. ADC0 is active and ready for data conversions. |              |               |                                                                |              |                |               |              |  |  |  |  |  |

| Bit6:    | BURSTEN: A                                                      |              |               |                                                                |              |                |               |              |  |  |  |  |  |

|          | 0: ADC0 Bur                                                     | st Mode Di   | isabled.      |                                                                |              |                |               |              |  |  |  |  |  |

|          | 1: ADC0 Bur                                                     | st Mode Er   | nabled.       |                                                                |              |                |               |              |  |  |  |  |  |

| Bit5:    | ADOINT: ADO                                                     | C0 Conver    | sion Comple   | ete Interrup                                                   | t Flag.      |                |               |              |  |  |  |  |  |

|          | 0: ADC0 has                                                     | not compl    | eted a data   | conversion                                                     | since the la | ast time AD    | DINT was cl   | eared.       |  |  |  |  |  |

|          | 1: ADC0 has                                                     |              |               | version.                                                       |              |                |               |              |  |  |  |  |  |

| Bit4:    | AD0BUSY: A                                                      | ADC0 Busy    | / Bit.        |                                                                |              |                |               |              |  |  |  |  |  |

|          | Read:                                                           |              | _             |                                                                | _            |                |               |              |  |  |  |  |  |

|          | 0: ADC0 con                                                     |              |               |                                                                | on is not cu | rrently in pro | ogress. AD    | DINT is set  |  |  |  |  |  |

|          | to logic 1 on                                                   |              |               |                                                                |              |                |               |              |  |  |  |  |  |

|          | 1: ADC0 con<br>Write:                                           | version is i | n progress.   |                                                                |              |                |               |              |  |  |  |  |  |

|          | 0: No Effect.                                                   |              |               |                                                                |              |                |               |              |  |  |  |  |  |

|          | 1: Initiates Al                                                 |              | arcian if AD  | $0 \le 1 \le $ | <b>10</b> h  |                |               |              |  |  |  |  |  |

| Bit3:    | ADOWINT: A                                                      |              |               |                                                                |              |                |               |              |  |  |  |  |  |

| Dito.    | This bit must                                                   |              |               |                                                                | lug.         |                |               |              |  |  |  |  |  |

|          | 0: ADC0 Win                                                     |              |               |                                                                | not occurre  | ed since this  | s flag was la | ast cleared. |  |  |  |  |  |

|          | 1: ADC0 Win                                                     |              |               |                                                                |              |                | - J           |              |  |  |  |  |  |

| Bit2:    | ADOLJST: A                                                      |              |               |                                                                |              |                |               |              |  |  |  |  |  |

|          | 0: Data in AD                                                   | COH:ADC      | 0L registers  | s is right just                                                | tified.      |                |               |              |  |  |  |  |  |

|          | 1: Data in AD                                                   | C0H:ADC      | 0L registers  | s is left justif                                               | ied. This op | tion should    | not be use    | d with a     |  |  |  |  |  |

|          | repeat count                                                    | -            | •             |                                                                |              | b, or 11b).    |               |              |  |  |  |  |  |

| Bits1-0: | AD0CM1-0:                                                       |              |               |                                                                |              |                |               |              |  |  |  |  |  |

|          | 00: ADC0 co                                                     |              |               |                                                                |              | BUSY.          |               |              |  |  |  |  |  |

|          | 01: ADC0 co                                                     |              |               |                                                                |              |                |               |              |  |  |  |  |  |

|          | 10: ADC0 co                                                     |              |               |                                                                |              | INVSTR.        |               |              |  |  |  |  |  |

|          | 11: ADC0 co                                                     | nversion in  | intiated on o | vertiow of 1                                                   | imer 2.      |                |               |              |  |  |  |  |  |

|          |                                                                 |              |               |                                                                |              |                |               |              |  |  |  |  |  |

|          |                                                                 |              |               |                                                                |              |                |               |              |  |  |  |  |  |

|          |                                                                 |              |               |                                                                |              |                |               |              |  |  |  |  |  |

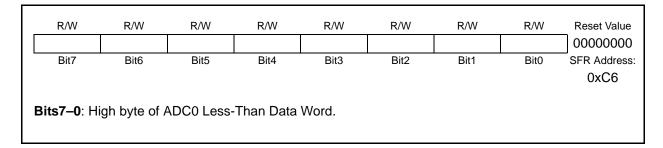

#### SFR Definition 4.12. ADC0LTH: ADC0 Less-Than Data High Byte

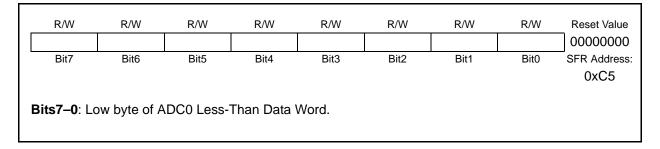

### SFR Definition 4.13. ADC0LTL: ADC0 Less-Than Data Low Byte

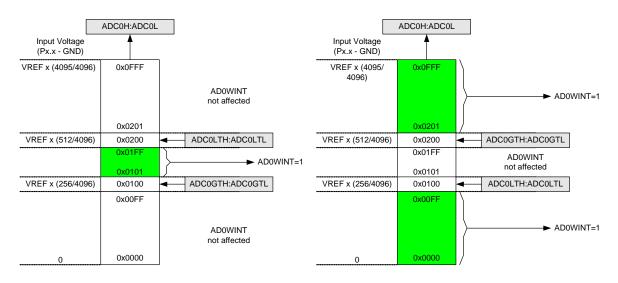

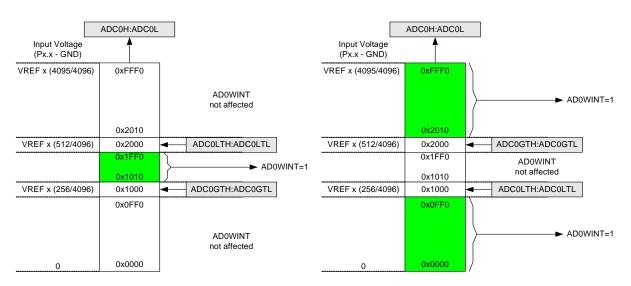

#### 4.5.1. Window Detector In Single-Ended Mode

Figure 4.7 shows two example window comparisons for right-justified data with ADC0LTH:ADC0LTL = 0x0200 (512d) and ADC0GTH:ADC0GTL = 0x0100 (256d). The input voltage can range from 0 to V<sub>RFF</sub> x (4095/4096) with respect to GND, and is represented by a 12-bit unsigned integer value. The repeat count is set to one. In the left example, an AD0WINT interrupt will be generated if the ADC0 conversion word (ADC0H:ADC0L) is within the range defined by ADC0GTH:ADC0GTL and ADC0LTH:ADC0LTL (if 0x0100 < ADC0H:ADC0L < 0x0200). In the right example, and AD0WINT interrupt will be generated if the ADC0 conversion word is outside of the range defined by the ADC0GT and ADC0LT registers (if ADC0H:ADC0L < 0x0100 or ADC0H:ADC0L > 0x0200). Figure 4.8 shows an example using left-justified data with the same comparison values.

Figure 4.7. ADC Window Compare Example: Right-Justified Single-Ended Data

Figure 4.8. ADC Window Compare Example: Left-Justified Single-Ended Data

#### 8.3.1. Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the CIP-51 to halt the CPU and enter Idle mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during Idle mode.

Idle mode is terminated when an enabled interrupt is asserted or a reset occurs. The assertion of an enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU to resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

If enabled, the Watchdog Timer (WDT) will eventually cause an internal watchdog reset and thereby terminate the Idle mode. This feature protects the system from an unintended permanent shutdown in the event of an inadvertent write to the PCON register. If this behavior is not desired, the WDT may be disabled by software prior to entering the Idle mode if the WDT was initially configured to allow this operation. This provides the opportunity for additional power savings, allowing the system to remain in the Idle mode indefinitely, waiting for an external stimulus to wake up the system.

#### 8.3.2. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the CIP-51 to enter Stop mode as soon as the instruction that sets the bit completes execution. In Stop mode the internal oscillator, CPU, and all digital peripherals are stopped; the state of the external oscillator circuit is not affected. Each analog peripheral (including the external oscillator circuit) may be shut down individually prior to entering Stop Mode. Stop mode can only be terminated by an internal or external reset. On reset, the CIP-51 performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to in STOP mode for longer than the MCD timeout period of 100  $\mu$ s.

#### 8.3.3. Suspend Mode

The C8051F52x/F52xA/F53x/F53xA devices feature a low-power Suspend mode, which stops the internal oscillator until a wakening event occurs. See Section Section "14.1.1. Internal Oscillator Suspend Mode" on page 136 for more information.

Note: When entering Suspend mode, firmware must set the ZTCEN bit in REF0CN (SFR Definition 5.1).

### SFR Definition 10.4. EIP1: Extended Interrupt Priority 1

| R/W    | R/W                          | R/W           | R/W           | R/W           | R/W            | R/W          | R/W          | Reset Value |

|--------|------------------------------|---------------|---------------|---------------|----------------|--------------|--------------|-------------|

| PMAT   | PREG0                        | PLIN          | PCPR          | PCPF          | PPAC0          | PREG0        | PWADC0       | 0000000     |

| Bit7   | Bit6                         | Bit5          | Bit4          | Bit3          | Bit2           | Bit1         | Bit0         |             |

|        |                              |               |               |               |                |              | SFR Address: | 0xF6        |

| Bit7:  | PMAT. Port M                 |               |               |               |                |              |              |             |

|        | This bit sets                |               |               |               | rupt.          |              |              |             |

|        | 0: Port Match                |               |               |               |                |              |              |             |

| Bit6:  | 1: Port Match<br>PREG0: Volt |               | • •           |               |                |              |              |             |

| 5110.  | This bit sets                | 0 0           |               | •             |                |              |              |             |

|        | 0: Voltage Re                |               |               | • •           | •              |              |              |             |

|        | 1: Voltage Re                | •             | •             | •             |                |              |              |             |

| Bit5:  | PLIN: LIN Int                | •             | •             | • •           | ty level.      |              |              |             |

| Bitto. | This bit sets                | •             |               |               |                |              |              |             |

|        | 0: LIN interru               |               |               |               |                |              |              |             |

|        | 1: LIN interru               |               |               |               |                |              |              |             |

| Bit4:  | PCPR: Com                    |               |               |               | rity Control.  |              |              |             |

|        | This bit sets                |               |               |               |                |              |              |             |

|        | 0: Comparate                 |               |               |               |                |              |              |             |

|        | 1: Comparate                 | or interrupt  | set to high   | priority leve | el.            |              |              |             |

| Bit3:  | PCPF: Comp                   | parator falli | ng Edge Int   | errupt Prior  | ity Control.   |              |              |             |

|        | This bit sets                | the priority  | of the Fallin | ng Edge Co    | mparator in    | terrupt.     |              |             |

|        | 0: Comparate                 |               |               |               |                |              |              |             |

|        | 1: Comparate                 |               |               |               |                |              |              |             |

| Bit2:  | PPAC0: Prog                  |               |               | ,             | Interrupt P    | riority Cont | rol.         |             |

|        | This bit sets                |               |               |               |                |              |              |             |

|        | 0: PCA0 inte                 |               |               |               |                |              |              |             |

|        | 1: PCA0 inte                 |               |               |               |                |              |              |             |

| Bit1:  | PREGO: ADO                   |               |               |               |                |              |              |             |

|        | This bit sets                |               |               |               | •              | •            |              |             |

|        | 0: ADC0 Cor                  |               |               | •             |                |              |              |             |

| D:40.  | 1: ADC0 Cor                  |               |               | •             | • • •          |              |              |             |

| Bit0:  | PWADC0: A                    |               |               |               |                |              |              |             |

|        | This bit sets                |               |               |               |                |              |              |             |

|        | 0: ADC0 Win                  |               |               | •             |                |              |              |             |

|        | 1: ADC0 Win                  | noom comp     | ansoninter    | rupt set to   | ingri priority | ievei.       |              |             |

| FR Defi               | nition 10.5. IT01C                                                                      | F: INT0/INT1 Configurat               | ion                                                 |  |  |  |  |  |  |  |  |  |

|-----------------------|-----------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------------------|--|--|--|--|--|--|--|--|--|

| R/W                   | R/W R/W                                                                                 | R/W R/W R                             | W R/W R/W Reset Value                               |  |  |  |  |  |  |  |  |  |

| IN1PL                 | IN1SL2 IN1SL1                                                                           | IN1SLO INOPL INO                      | SL2 IN0SL1 IN0SL0 0000001                           |  |  |  |  |  |  |  |  |  |

| Bit7                  | Bit6 Bit5                                                                               | Bit4 Bit3 B                           | it2 Bit1 Bit0                                       |  |  |  |  |  |  |  |  |  |

|                       |                                                                                         |                                       | SFR Address: 0xE4                                   |  |  |  |  |  |  |  |  |  |

| Note: Refer           | to SFR Definition 18.1. "TO                                                             | CON: Timer Control" on page 186 for I | NT0/1 edge- or level-sensitive interrupt selection. |  |  |  |  |  |  |  |  |  |

|                       |                                                                                         |                                       |                                                     |  |  |  |  |  |  |  |  |  |

| Bit 7:                | IN1PL: INTO Polarity                                                                    |                                       |                                                     |  |  |  |  |  |  |  |  |  |

|                       | 0: INTO input is active<br>1: INTO input is active                                      |                                       |                                                     |  |  |  |  |  |  |  |  |  |

| Bits 6–4 <sup>.</sup> | IN1SL2–0: INTO Port                                                                     |                                       |                                                     |  |  |  |  |  |  |  |  |  |

|                       |                                                                                         |                                       | . Note that this pin assignment is inde-            |  |  |  |  |  |  |  |  |  |

|                       | pendent of the Crossbar; INTO will monitor the assigned Port pin without disturbing the |                                       |                                                     |  |  |  |  |  |  |  |  |  |

|                       |                                                                                         |                                       | ne Crossbar. The Crossbar will not                  |  |  |  |  |  |  |  |  |  |

|                       |                                                                                         |                                       | skip the selected pin (accomplished by              |  |  |  |  |  |  |  |  |  |

|                       |                                                                                         | ponding bit in register P0SKIP        | ').<br>_                                            |  |  |  |  |  |  |  |  |  |

|                       | IN1SL2-0                                                                                | INT1 Port Pin                         |                                                     |  |  |  |  |  |  |  |  |  |

|                       | 000                                                                                     | P0.0                                  |                                                     |  |  |  |  |  |  |  |  |  |

|                       | 001                                                                                     | P0.1                                  | _                                                   |  |  |  |  |  |  |  |  |  |

|                       | 010                                                                                     | P0.2                                  | _                                                   |  |  |  |  |  |  |  |  |  |

|                       | 011                                                                                     | P0.3                                  | _                                                   |  |  |  |  |  |  |  |  |  |

|                       | 100                                                                                     | P0.4                                  | _                                                   |  |  |  |  |  |  |  |  |  |

|                       | 101                                                                                     | P0.5                                  | _                                                   |  |  |  |  |  |  |  |  |  |

|                       | 110                                                                                     | P0.6*                                 | _                                                   |  |  |  |  |  |  |  |  |  |

|                       | 111                                                                                     | P0.7*                                 | _                                                   |  |  |  |  |  |  |  |  |  |

|                       | Note: Available in the                                                                  | C80151F53x/C8051F53xA parts.          |                                                     |  |  |  |  |  |  |  |  |  |

| Bit 3:                | INOPL: INTO Polarity                                                                    |                                       |                                                     |  |  |  |  |  |  |  |  |  |

|                       | 0: INTO interrupt is ac                                                                 |                                       |                                                     |  |  |  |  |  |  |  |  |  |

| D:40 0 0.             | 1: INT0 interrupt is ac<br>INT0SL2-0: INT0 Po                                           |                                       |                                                     |  |  |  |  |  |  |  |  |  |

| BITS Z-U              |                                                                                         |                                       | . Note that this pin assignment is inde-            |  |  |  |  |  |  |  |  |  |

|                       |                                                                                         | ¥                                     | ned Port pin without disturbing the                 |  |  |  |  |  |  |  |  |  |

|                       |                                                                                         |                                       | ne Crossbar. The Crossbar will not                  |  |  |  |  |  |  |  |  |  |

|                       | <b>e</b> .                                                                              |                                       | skip the selected pin (accomplished by              |  |  |  |  |  |  |  |  |  |

|                       | setting to 1 the corres                                                                 | ponding bit in register P0SKIP        | ).                                                  |  |  |  |  |  |  |  |  |  |

|                       | IN0SL2-0                                                                                | INT0 Port Pin                         |                                                     |  |  |  |  |  |  |  |  |  |

|                       | 000                                                                                     | P0.0                                  |                                                     |  |  |  |  |  |  |  |  |  |

|                       | 001                                                                                     | P0.1                                  |                                                     |  |  |  |  |  |  |  |  |  |

|                       | 010                                                                                     | P0.2                                  |                                                     |  |  |  |  |  |  |  |  |  |

|                       | 011                                                                                     | P0.3                                  |                                                     |  |  |  |  |  |  |  |  |  |

|                       | 100                                                                                     | P0.4                                  |                                                     |  |  |  |  |  |  |  |  |  |

|                       | 101                                                                                     | P0.5                                  |                                                     |  |  |  |  |  |  |  |  |  |

|                       | 110                                                                                     | P0.6*                                 |                                                     |  |  |  |  |  |  |  |  |  |

|                       | 111                                                                                     | P0.7*                                 |                                                     |  |  |  |  |  |  |  |  |  |

|                       | Note: Available in the                                                                  | C80151F53x/C8051F53xA parts.          |                                                     |  |  |  |  |  |  |  |  |  |

### SFR Definition 13.2. XBR1: Port I/O Crossbar Register 1

| R/W      | R/W                            | R/W                  | R/W         | R/W         | R/W            | R/W       | R/W           | Reset Value |

|----------|--------------------------------|----------------------|-------------|-------------|----------------|-----------|---------------|-------------|

| WEAKPL   | JD XBARE                       | T1E                  | TOE         | ECIE        | Reserved       | PC        | AOME          | 00000000    |

| Bit7     | Bit6                           | Bit5                 | Bit4        | Bit3        | Bit2           | Bit1      | Bit0          |             |

|          |                                |                      |             |             |                |           | SFR Address   | s: 0xE2     |

|          |                                |                      |             |             |                |           |               |             |

| Bit7:    | WEAKPUD:                       |                      |             |             |                |           |               |             |

|          | 0: Weak Pull                   | •                    | • •         | or Ports wh | nose I/O are c | onfigured | l as analog i | nput).      |

| 5.40     | 1: Weak Pull                   | •                    |             |             |                |           |               |             |

| Bit6:    | XBARE: Cro                     |                      | le.         |             |                |           |               |             |

|          | 0: Crossbar o<br>1: Crossbar e |                      |             |             |                |           |               |             |

| Bit5:    | <b>T1E</b> : T1 Enal           |                      |             |             |                |           |               |             |

| DILJ.    | 0: T1 unavail                  |                      | t nin       |             |                |           |               |             |

|          | 1: T1 routed                   |                      | , pin       |             |                |           |               |             |

| Bit4:    | TOE: TO Enal                   | •                    |             |             |                |           |               |             |

|          | 0: T0 unavail                  | able at Por          | t pin.      |             |                |           |               |             |

|          | 1: T0 routed                   | to Port pin.         | •           |             |                |           |               |             |

| Bit3:    | ECIE: PCA0                     | External Co          | ounter Inpu | t Enable    |                |           |               |             |

|          | 0: ECI unava                   | ilable at Po         | rt pin.     |             |                |           |               |             |

|          | 1: ECI routed                  |                      |             |             |                |           |               |             |

| Bit2:    | Reserved. M                    |                      | ~ .         |             |                |           |               |             |

| Bits1–0: | PCA0ME: PC                     |                      |             |             |                |           |               |             |

|          | 00: All PCA I                  |                      |             | pins.       |                |           |               |             |

|          | 01: CEX0 rou                   |                      |             | •           |                |           |               |             |

|          | 10: CEX0, CI<br>11: CEX0, CI   |                      |             |             |                |           |               |             |

|          |                                | $_{\Lambda 1}, OLAZ$ |             | ort pins.   |                |           |               |             |

|          |                                |                      |             |             |                |           |               |             |

#### 13.3. General Purpose Port I/O

Port pins that remain unassigned by the Crossbar and are not used by analog peripherals can be used for general purpose I/O. Ports P0–P1 are accessed through corresponding special function registers (SFRs) that are both byte addressable and bit addressable. When writing to a Port, the value written to the SFR is latched to maintain the output data value at each pin. When reading, the logic levels of the Port's input pins are returned regardless of the XBRn settings (i.e., even when the pin is assigned to another signal by the Crossbar, the Port register can always read its corresponding Port I/O pin). The exception to this is the execution of the read-modify-write instructions that target a Port Latch register as the destination. The read-modify-write instructions when operating on a Port SFR are the following: ANL, ORL, XRL, JBC, CPL, INC, DEC, DJNZ and MOV, CLR or SETB, when the destination is an individual bit in a Port SFR. For these instructions, the value of the latch register (not the pin) is read, modified, and written back to the SFR.

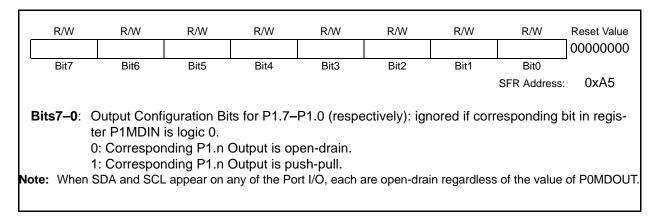

### SFR Definition 13.11. P1MDOUT: Port1 Output Mode

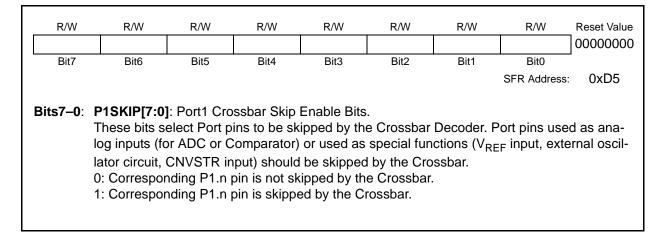

### SFR Definition 13.12. P1SKIP: Port1 Skip

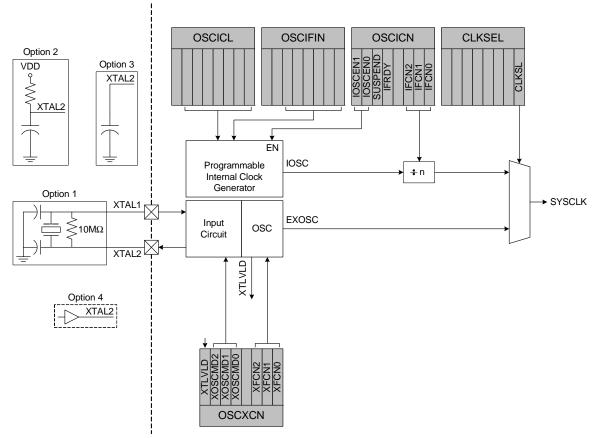

### 14. Oscillators

C8051F52x/F52xA/F53x/F53xA devices include a programmable internal oscillator, an external oscillator drive circuit. The internal oscillator can be enabled/disabled and calibrated using the OSCICN and OSCICL registers, as shown in Figure 14.1. The system clock (SYSCLK) can be derived from the internal oscillator, external oscillator circuit. Oscillator electrical specifications are given in Table 2.11 on page 34.

#### 14.1. Programmable Internal Oscillator

All C8051F52x/53x devices include a programmable internal oscillator that defaults as the system clock after a system reset. The internal oscillator period can be programmed via the OSCICL and OSCIFIN registers, shown in SFR Definition 14.2 and SFR Definition 14.3. On C8051F52x/53x devices, OSCICL and OSCIFIN are factory calibrated to obtain a 24.5 MHz frequency.

Electrical specifications for the precision internal oscillator are given in Table 2.11 on page 34. Note that the system clock may be derived from the programmed internal oscillator divided by 1, 2, 4, 8, 16, 32, 64, or 128 as defined by the IFCN bits in register OSCICN. The divide value defaults to 128 following a reset.

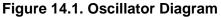

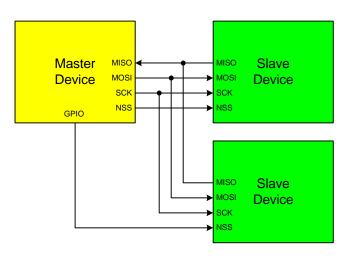

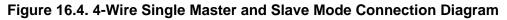

Figure 16.2. Multiple-Master Mode Connection Diagram

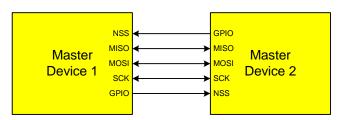

Figure 16.3. 3-Wire Single Master and Slave Mode Connection Diagram

#### 16.3. SPI0 Slave Mode Operation

When SPI0 is enabled and not configured as a master, it will operate as a SPI slave. As a slave, bytes are shifted in through the MOSI pin and out through the MISO pin by a master device controlling the SCK signal. A bit counter in the SPI0 logic counts SCK edges. When 8 bits have been shifted into the shift register, the SPIF flag is set to logic 1, and the byte is copied into the receive buffer. Data is read from the receive buffer by reading SPI0DAT. A slave device cannot initiate transfers. Data to be transferred to the master device is pre-loaded into the shift register by writing to SPI0DAT. Writes to SPI0DAT are double-buffered, and are placed in the transmit buffer first. If the shift register is empty, the contents of the transmit buffer will immediately be transferred into the shift register. When the shift register already contains data, the SPI will load the shift register with the transmit buffer's contents after the last SCK edge of the next (or current) SPI transfer.

#### 17.4. LIN Slave Mode Operation

When the device is configured for slave mode operation, it must wait for a command from a master node. Access from the firmware to data buffer and ID registers of the LIN peripheral is only possible when a data request is pending (DTREQ bit (LIN0ST.4) is 1) and also when the LIN bus is not active (ACTIVE bit (LIN0ST.7) is set to 0).

The LIN peripheral in slave mode detects the header of the message frame sent by the LIN master. If slave synchronization is enabled (autobaud), the slave synchronizes its internal bit time to the master bit time.

The LIN peripheral configured for slave mode will generated an interrupt in one of three situations:

- 1. After the reception of the IDENTIFIER FIELD.

- 2. When an error is detected.

- 3. When the message transfer is completed.

The application should perform the following steps when an interrupt is detected:

- 1. Check the status of the DTREQ bit (LIN0ST.4). This bit is set when the IDENTIFIER FIELD has been received.

- 2. If DTREQ (LIN0ST.4) is set, read the identifier from LIN0ID and process it. If DTREQ (LIN0ST.4) is not set, continue to step 7.

- 3. Set the TXRX bit (LIN0CTRL.5) to 1 if the current frame is a transmit operation for the slave and set to 0 if the current frame is a receive operation for the slave.

- 4. Load the data length into LIN0SIZE.

- 5. For a slave transmit operation, load the data to transmit into the data buffer.

- 6. Set the DTACK bit (LIN0CTRL.4). Continue to step 10.

- 7. If DTREQ (LIN0ST.4) is not set, check the DONE bit (LIN0ST.0). The transmission was successful if the DONE bit is set.

- 8. If the transmission was successful and the current frame was a receive operation for the slave, load the received data bytes from the data buffer.

- 9. If the transmission was not successful, check LIN0ERR to determine the nature of the error. Further error handling has to be done by the application.

- 10.Set the RSTINT (LIN0CTRL.3) and RSTERR bits (LIN0CTRL.2) to reset the interrupt request and the error flags.

In addition to these steps, the application should be aware of the following:

- 1. If the current frame is a transmit operation for the slave, steps 1 through 5 must be completed during the IN-FRAME RESPONSE SPACE. If it is not completed in time, a timeout will be detected by the master.

- 2. If the current frame is a receive operation for the slave, steps 1 through 5 have to be finished until the reception of the first byte after the IDENTIFIER FIELD. Otherwise, the internal receive buffer of the LIN peripheral will be overwritten and a timeout error will be detected in the LIN peripheral.

- 3. The LIN module does not directly support LIN Version 1.3 Extended Frames. If the application detects an unknown identifier (e.g. extended identifier), it has to write a 1 to the STOP bit (LINOCTRL.7) instead of setting the DTACK (LINOCTRL.4) bit. At that time, steps 2 through 5 can then be skipped. In this situation, the LIN peripheral stops the processing of the LIN communication until the next SYNC BREAK is received.

- 4. Changing the configuration of the checksum during a transaction will cause the interface to reset and the transaction to be lost. To prevent this, the checksum should not be configured while a transaction is

in progress. The same applies to changes in the LIN interface mode from slave mode to master mode and from master mode to slave mode.

#### 17.5. Sleep Mode and Wake-Up

To reduce the system's power consumption, the LIN Protocol Specification defines a Sleep Mode. The message used to broadcast a Sleep Mode request must be transmitted by the LIN master application in the same way as a normal transmit message. The LIN slave application must decode the Sleep Mode Frame from the Identifier and data bytes. After that, the LIN slave node must be put into the Sleep Mode by setting the SLEEP bit (LINOCTRL.6).

If the SLEEP bit (LIN0CTRL.6) of the LIN slave application is not set and there is no bus activity for four seconds (specified bus idle timeout), the IDLTOUT bit (LIN0ST.6) is set and an interrupt request is generated. After that the application may assume that the LIN bus is in Sleep Mode and set the SLEEP bit (LIN0CTRL.6).

Sending a Wakeup signal from the master or any slave node terminates the Sleep Mode of the LIN bus. To send a Wakeup signal, the application has to set the WUPREQ bit (LIN0CTRL.1). After successful transmission of the wakeup signal, the DONE bit (LIN0ST.0) of the master node is set and an interrupt request is generated. The LIN slave does not generate an interrupt request after successful transmission of the Wakeup signal but it generates an interrupt request if the master does not respond to the Wakeup signal within 150 milliseconds. In that case, the ERROR bit (LIN0ST.2) and TOUT bit (LIN0ERR.2) are set. The application then has to decide whether or not to transmit another Wakeup signal.

All LIN nodes that detect a wakeup signal will set the WAKEUP (LIN0ST.1) and DONE bits (LIN0ST.0) and generate an interrupt request. After that, the application has to clear the SLEEP bit (LIN0CTRL.6) in the LIN slave.

#### 17.6. Error Detection and Handling

The LIN peripheral generates an interrupt request and stops the processing of the current frame if it detects an error. The application has to check the type of error by processing LIN0ERR. After that, it has to reset the error register and the ERROR bit (LIN0ST.2) by writing a 1 to the RSTERR bit (LIN0CTRL.2). Starting a new message with the LIN peripheral selected as master or sending a Wakeup signal with the LIN peripheral selected as a master or slave is possible only if ERROR bit (LIN0ST.2) is set to 0.

### SFR Definition 17.3. LINCF Control Mode Register

| R/W   | R/W           | R/W           | R/W          | R/W         | R/W          | R/W       | R/W          | Reset Value |

|-------|---------------|---------------|--------------|-------------|--------------|-----------|--------------|-------------|

| LINEN | MODE          | ABAUD         |              |             |              |           |              | 00000000    |

| Bit7  | Bit6          | Bit5          | Bit4         | Bit3        | Bit2         | Bit1      | Bit0         | ,<br>,      |

|       |               |               |              |             |              |           | SFR Address: | 0x95        |

| Bit7: | LINEN: LIN    |               | nable bit    |             |              |           |              |             |

|       | 0: LIN0 is di |               |              |             |              |           |              |             |

| -     | 1: LIN0 is er |               |              |             |              |           |              |             |

| Bit6: | MODE: LIN     |               |              |             |              |           |              |             |

|       | 0: LIN0 ope   |               |              |             |              |           |              |             |

|       | 1: LIN0 ope   | rates in Mas  | ter mode.    |             |              |           |              |             |

| Bit5: | ABAUD: LIN    | N Mode Auto   | omatic Bau   | d Rate Sele | ction (slave | e mode or | nly).        |             |

|       | 0: Manual b   |               |              |             | ,            |           | •            |             |

|       |               | 1 1 4         |              | مممامم      |              |           |              |             |

|       | 1: Automation | c baud rate s | Selection is | enabled     |              |           |              |             |

### SFR Definition 17.12. LIN0CTRL: LIN0 Control Register

| W            | W                                                                                                                                                                                   | W            | R/W          | R/W          | R/W          | R/W            | R/W          | Reset Value    |  |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|--------------|----------------|--------------|----------------|--|--|--|--|

| STOP         | SLEEP                                                                                                                                                                               | TXRX         | DTACK        | RSTINT       | RSTERR       | WUPREQ         | STREQ        | 00000000       |  |  |  |  |

| Bit7         | Bit6                                                                                                                                                                                | Bit5         | Bit4         | Bit3         | Bit2         | Bit1           | Bit0         | 7              |  |  |  |  |

|              | Address: 0x08 (indirec                                                                                                                                                              |              |              |              |              |                |              |                |  |  |  |  |

|              |                                                                                                                                                                                     | <b>.</b> .   |              |              |              | <u>.</u> .     |              |                |  |  |  |  |

| Bit7:        | STOP: Stop                                                                                                                                                                          |              |              | •            |              | • /            |              |                |  |  |  |  |

|              | This bit is to                                                                                                                                                                      |              |              |              |              | •              |              |                |  |  |  |  |

|              | until the next SYNCH BREAK signal. It is used when the application is handling a data request interrupt and cannot use the frame content with the received identifier (always reads |              |              |              |              |                |              |                |  |  |  |  |

|              | 0).                                                                                                                                                                                 | rupt and ca  | nnot use tri | e frame cor  |              | e received ic  |              | vays reaus     |  |  |  |  |

| Bit6:        | SLEEP: Slee                                                                                                                                                                         | on Mode W    | arning       |              |              |                |              |                |  |  |  |  |

| Bitto.       | This bit is to                                                                                                                                                                      | •            | •            | on to warn t | the peripher | ral that a Sle | ep Mode F    | rame was       |  |  |  |  |

|              | received and                                                                                                                                                                        |              |              |              |              |                | •            |                |  |  |  |  |

|              | The applicat                                                                                                                                                                        |              |              | •            |              |                |              |                |  |  |  |  |

| Bit5:        | TXRX: Trans                                                                                                                                                                         | smit/Receiv  | e Selection  | Bit.         |              | -              |              |                |  |  |  |  |

|              | This bit dete                                                                                                                                                                       |              |              |              | nsmit frame  | e or a receive | e frame.     |                |  |  |  |  |

|              | 0: Current fra                                                                                                                                                                      |              |              |              |              |                |              |                |  |  |  |  |

| <b>D</b> 144 | 1: Current fra                                                                                                                                                                      |              | •            |              |              |                |              |                |  |  |  |  |

| Bit4:        | DTACK: Dat                                                                                                                                                                          |              | •            |              | • /          |                |              |                |  |  |  |  |

|              | Set to 1 after<br>matically be                                                                                                                                                      | •            |              |              | to acknowle  | edge the trai  | nster. The c | oit will auto- |  |  |  |  |

| Bit3:        | RSTINT: Inte                                                                                                                                                                        |              |              | Controller.  |              |                |              |                |  |  |  |  |

| Dito.        | This bit alwa                                                                                                                                                                       |              |              |              |              |                |              |                |  |  |  |  |

|              | 0: No effect.                                                                                                                                                                       |              |              |              |              |                |              |                |  |  |  |  |

|              | 1: Reset the                                                                                                                                                                        | LININT bit   | (LIN0ST.3)   |              |              |                |              |                |  |  |  |  |

| Bit2:        | RSTERR: EI                                                                                                                                                                          | rror Reset E | Sit.         |              |              |                |              |                |  |  |  |  |

|              | This bit alwa                                                                                                                                                                       | ys reads as  | s 0.         |              |              |                |              |                |  |  |  |  |

|              | 0: No effect.                                                                                                                                                                       |              |              |              |              |                |              |                |  |  |  |  |

|              | 1: Reset the                                                                                                                                                                        |              |              | nd LIN0ERF   | र.           |                |              |                |  |  |  |  |

| Bit1:        | WUPREQ: V                                                                                                                                                                           |              |              | P            |              |                |              | C II . I .     |  |  |  |  |

|              | Set to 1 to te                                                                                                                                                                      |              |              | y sending a  | wakeup się   | gnal. The bit  | will automa  | atically be    |  |  |  |  |

| Bit0:        | cleared to 0<br>STREQ: Sta                                                                                                                                                          |              |              | mode only    | <i>(</i> )   |                |              |                |  |  |  |  |

| DILU.        | 1: Start a LIN                                                                                                                                                                      |              |              |              |              | oading the ic  | lentifier da | ta lenath      |  |  |  |  |

|              | and data buf                                                                                                                                                                        |              |              |              | only alter i |                | ionanoi, ua  | alongin        |  |  |  |  |

|              | The bit is res                                                                                                                                                                      |              |              | sion comple  | tion or erro | r detection.   |              |                |  |  |  |  |

|              |                                                                                                                                                                                     |              |              |              |              |                |              |                |  |  |  |  |

|              |                                                                                                                                                                                     |              |              |              |              |                |              |                |  |  |  |  |

|              |                                                                                                                                                                                     |              |              |              |              |                |              |                |  |  |  |  |

### SFR Definition 17.13. LIN0ST: LIN0 STATUS Register

| R      | R                                                                                                     | R     | R           | R/W           | R             | R               | R            | Reset Value       |  |  |  |  |

|--------|-------------------------------------------------------------------------------------------------------|-------|-------------|---------------|---------------|-----------------|--------------|-------------------|--|--|--|--|

| ACTIVE | IDLTOUT                                                                                               | ABORT | DTREQ       | LININT        | ERROR         | WAKEUP          | DONE         | 00000000          |  |  |  |  |

| Bit7   | Bit6                                                                                                  | Bit5  | Bit4        | Bit3          | Bit2          | Bit1            | Bit0         | _                 |  |  |  |  |

|        |                                                                                                       |       |             |               |               |                 | Address      | : 0x09 (indirect) |  |  |  |  |

|        |                                                                                                       |       |             |               |               |                 |              |                   |  |  |  |  |

| Bit7:  | ACTIVE: LIN                                                                                           |       |             |               |               |                 |              |                   |  |  |  |  |

|        | 0: No transm                                                                                          |       |             |               |               |                 |              |                   |  |  |  |  |

| 5.40   | 1: Transmission activity detected on the LIN bus.<br>IDLTOUT: Bus Idle Timeout Bit (slave mode only). |       |             |               |               |                 |              |                   |  |  |  |  |

| Bit6:  |                                                                                                       |       | •           |               | only).        |                 |              |                   |  |  |  |  |

|        | 0: The bus h                                                                                          |       |             |               | oconde bu     | t the bus is n  | at vot in Sl | oon modo          |  |  |  |  |

| Bit5:  | ABORT: Abo                                                                                            |       |             |               |               |                 | or yer in Si | eep mode.         |  |  |  |  |

| Bito.  |                                                                                                       |       |             |               |               | topped. This    | bit is reset | to 0 after        |  |  |  |  |