Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                  |

|----------------------------|------------------------------------------------------------------|

| Product Status             | Active                                                           |

| Core Processor             | 8051                                                             |

| Core Size                  | 8-Bit                                                            |

| Speed                      | 25MHz                                                            |

| Connectivity               | SPI, UART/USART                                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT               |

| Number of I/O              | 16                                                               |

| Program Memory Size        | 2KB (2K x 8)                                                     |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 256 x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.25V                                                       |

| Data Converters            | A/D 16x12b                                                       |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                               |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 20-VFQFN Exposed Pad                                             |

| Supplier Device Package    | 20-QFN (4x4)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f537-c-im |

|                            |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 14.2.2. External Crystal Example                            | 139 |

|-------------------------------------------------------------|-----|

| 14.2.3. External RC Example                                 | 141 |

| 14.2.4. External Capacitor Example                          | 141 |

| 14.3. System Clock Selection                                | 143 |

| 15. UART0                                                   |     |

| 15.1. Enhanced Baud Rate Generation                         |     |

| 15.2. Operational Modes                                     |     |

| 15.2.1. 8-Bit UART                                          |     |

| 15.2.2. 9-Bit UART                                          |     |

| 15.3. Multiprocessor Communications                         |     |

| 16. Enhanced Serial Peripheral Interface (SPI0)             |     |

| 16.1. Signal Descriptions                                   | 152 |

| 16.1.1. Master Out, Slave In (MOSI)                         |     |

| 16.1.2. Master In, Slave Out (MISO)                         |     |

| 16.1.3. Serial Clock (SCK)                                  |     |

| 16.1.4. Slave Select (NSS)                                  |     |

| 16.2. SPI0 Master Mode Operation                            |     |

| 16.3. SPI0 Slave Mode Operation                             |     |

| 16.4. SPI0 Interrupt Sources                                |     |

| 16.5. Serial Clock Timing                                   |     |

| 16.6. SPI Special Function Registers                        |     |

| 17. LIN (C8051F520/0A/3/3A/6/6A and C8051F530/0A/3/3A/6/6A) |     |

| 17.1. Software Interface with the LIN Peripheral            |     |

| 17.2. LIN Interface Setup and Operation                     |     |

| 17.2.1. Mode Definition                                     |     |

| 17.2.2. Baud Rate Options: Manual or Autobaud               |     |

| 17.2.3. Baud Rate Calculations—Manual Mode                  |     |

| 17.2.4. Baud Rate Calculations—Automatic Mode               |     |

| 17.3. LIN Master Mode Operation                             |     |

| 17.4. LIN Slave Mode Operation                              |     |

| 17.5. Sleep Mode and Wake-Up                                |     |

| 17.6. Error Detection and Handling                          |     |

| 17.7. LIN Registers                                         |     |

| 17.7.1. LIN Direct Access SFR Registers Definition          |     |

| 17.7.2. LIN Indirect Access SFR Registers Definition        |     |

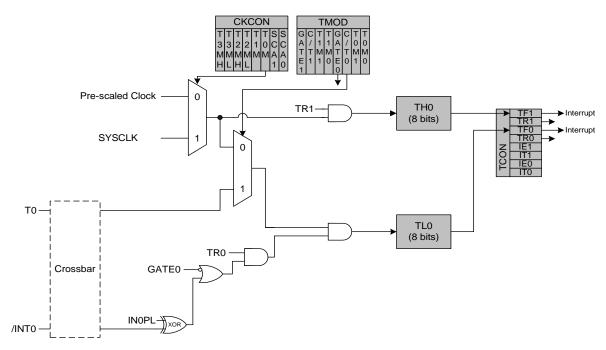

| 18. Timers                                                  |     |

| 18.1. Timer 0 and Timer 1                                   |     |

| 18.1.1. Mode 0: 13-bit Counter/Timer                        |     |

| 18.1.2. Mode 1: 16-bit Counter/Timer                        |     |

| 18.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload        |     |

| 18.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)     |     |

| 18.2. Timer 2                                               |     |

| 18.2.1. 16-bit Timer with Auto-Reload                       |     |

| 18.2.2. 8-bit Timers with Auto-Reload                       | 101 |

| 18.2.3. External Capture Mode                               |     |

| SFR Definition 13.13. P0SKIP: Port0 Skip                           | 134 |

|--------------------------------------------------------------------|-----|

| SFR Definition 13.14. P1MAT: Port1 Match                           | 134 |

| SFR Definition 13.15. P1MASK: Port1 Mask                           |     |

| SFR Definition 14.1. OSCICN: Internal Oscillator Control           |     |

| SFR Definition 14.2. OSCICL: Internal Oscillator Calibration       | 138 |

| SFR Definition 14.3. OSCIFIN: Internal Fine Oscillator Calibration |     |

| SFR Definition 14.4. OSCXCN: External Oscillator Control           | 142 |

| SFR Definition 14.5. CLKSEL: Clock Select                          |     |

| SFR Definition 15.1. SCON0: Serial Port 0 Control                  |     |

| SFR Definition 15.2. SBUF0: Serial (UART0) Port Data Buffer        |     |

| SFR Definition 16.1. SPI0CFG: SPI0 Configuration                   | 157 |

| SFR Definition 16.2. SPI0CN: SPI0 Control                          |     |

| SFR Definition 16.3. SPI0CKR: SPI0 Clock Rate                      |     |

| SFR Definition 16.4. SPI0DAT: SPI0 Data                            |     |

| SFR Definition 17.1. LINADDR: Indirect Address Register            |     |

| SFR Definition 17.2. LINDATA: LIN Data Register                    |     |

| SFR Definition 17.3. LINCF Control Mode Register                   |     |

| SFR Definition 17.4. LIN0DT1: LIN0 Data Byte 1                     |     |

| SFR Definition 17.5. LIN0DT2: LIN0 Data Byte 2                     |     |

| SFR Definition 17.6. LIN0DT3: LIN0 Data Byte 3                     |     |

| SFR Definition 17.7. LIN0DT4: LIN0 Data Byte 4                     |     |

| SFR Definition 17.8. LIN0DT5: LIN0 Data Byte 5                     | 176 |

| SFR Definition 17.9. LIN0DT6: LIN0 Data Byte 6                     |     |

| SFR Definition 17.10. LIN0DT7: LIN0 Data Byte 7                    |     |

| SFR Definition 17.11. LIN0DT8: LIN0 Data Byte 8                    |     |

| SFR Definition 17.12. LIN0CTRL: LIN0 Control Register              |     |

| SFR Definition 17.13. LIN0ST: LIN0 STATUS Register                 |     |

| SFR Definition 17.14. LIN0ERR: LIN0 ERROR Register                 |     |

| SFR Definition 17.15. LINOSIZE: LINO Message Size Register         | 180 |

| SFR Definition 17.16. LIN0DIV: LIN0 Divider Register               |     |

| SFR Definition 17.17. LIN0MUL: LIN0 Multiplier Register            |     |

| SFR Definition 17.18. LIN0ID: LIN0 ID Register                     |     |

| SFR Definition 18.1. TCON: Timer Control                           |     |

| SFR Definition 18.2. TMOD: Timer Mode                              |     |

| SFR Definition 18.3. CKCON: Clock Control                          |     |

| SFR Definition 18.4. TL0: Timer 0 Low Byte                         |     |

| SFR Definition 18.5. TL1: Timer 1 Low Byte                         |     |

| SFR Definition 18.6. TH0: Timer 0 High Byte                        |     |

| SFR Definition 18.7. TH1: Timer 1 High Byte                        |     |

| SFR Definition 18.8. TMR2CN: Timer 2 Control                       |     |

| SFR Definition 18.9. TMR2RLL: Timer 2 Reload Register Low Byte     |     |

| SFR Definition 18.10. TMR2RLH: Timer 2 Reload Register High Byte   |     |

| SFR Definition 18.11. TMR2L: Timer 2 Low Byte                      |     |

| SFR Definition 18.12. TMR2H Timer 2 High Byte                      | 194 |

| SFR Definition 19.1. PCA0CN: PCA Control                           | 206 |

|                                                                    |     |

| Ordering Part Number | Flash Memory (kB) | Port I/Os | LIN          | Package | Ordering Part Number | Flash Memory (kB) | Port I/Os | LIN          | Package  |

|----------------------|-------------------|-----------|--------------|---------|----------------------|-------------------|-----------|--------------|----------|

| C8051F520-IM         | 8                 | 6         | $\checkmark$ | DFN-10  | C8051F534-IM         | 4                 | 16        |              | QFN-20   |

| C8051F520A-IM        |                   |           |              |         | C8051F534A-IM        |                   |           |              |          |

| C8051F521-IM         | 8                 | 6         | —            | DFN-10  | C8051F536-IM         | 2                 | 16        | $\checkmark$ | QFN-20   |

| C8051F521A-IM        |                   |           |              |         | C8051F536A-IM        |                   |           |              |          |

| C8051F523-IM         | 4                 | 6         | $\checkmark$ | DFN-10  | C8051F537-IM         | 2                 | 16        | -            | QFN-20   |

| C8051F523A-IM        |                   |           |              |         | C8051F537A-IM        |                   |           |              |          |

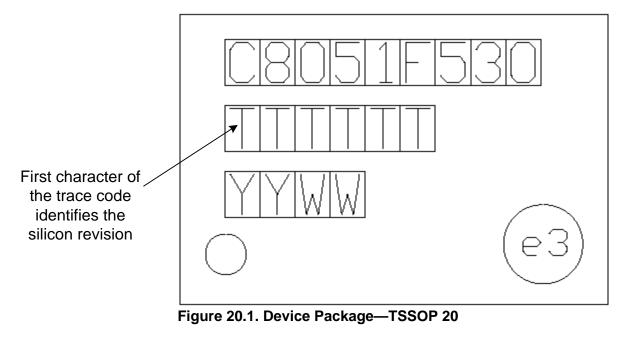

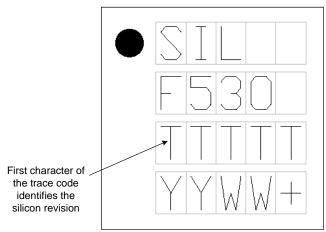

| C8051F524-IM         | 4                 | 6         | _            | DFN-10  | C8051F530-IT         | 8                 | 16        | $\checkmark$ | TSSOP-20 |

| C8051F524A-IM        |                   |           |              |         | C8051F530A-IT        |                   |           |              |          |

| C8051F526-IM         | 2                 | 6         | $\checkmark$ | DFN-10  | C8051F531-IT         | 8                 | 16        | _            | TSSOP-20 |

| C8051F526A-IM        |                   |           |              |         | C8051F531A-IT        |                   |           |              |          |

| C8051F527-IM         | 2                 | 6         | _            | DFN-10  | C8051F533-IT         | 4                 | 16        | $\checkmark$ | TSSOP-20 |

| C8051F527A-IM        |                   |           |              |         | C8051F533A-IT        |                   |           |              |          |

| C8051F530-IM         | 8                 | 16        | $\checkmark$ | QFN-20  | C8051F534-IT         | 4                 | 16        | —            | TSSOP-20 |

| C8051F530A-IM        |                   |           |              |         | C8051F534A-IT        |                   |           |              |          |

| C8051F531-IM         | 8                 | 16        | —            | QFN-20  | C8051F536-IT         | 2                 | 16        | $\checkmark$ | TSSOP-20 |

| C8051F531A-IM        |                   |           |              |         | C8051F536A-IT        |                   |           |              |          |

| C8051F533-IM         | 4                 | 16        | $\checkmark$ | QFN-20  | C8051F537-IT         | 2                 | 16        | —            | TSSOP-20 |

| C8051F533A-IM        |                   |           |              |         | C8051F537A-IT        |                   |           |              |          |

Table 1.2. Product Selection Guide (Not Recommended for New Designs)

The part numbers in Table 1.2 are not recommended for new designs. Instead, select the corresponding part number from Table 1.1 (silicon revision C) for your design. In Table 1.2, the part numbers in the format similar to C8051F520-IM are silicon revision A devices. The part numbers in the format similar to C8051F520A-IM are silicon revision B devices.

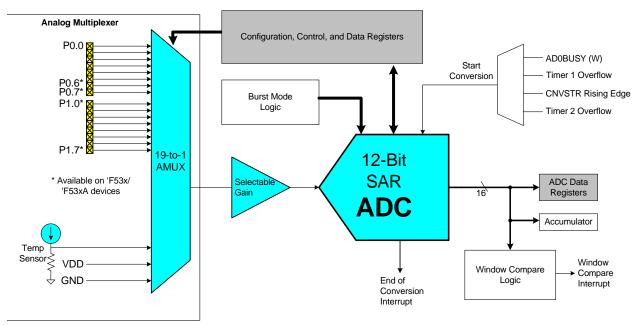

### 1.5. 12-Bit Analog to Digital Converter

The C8051F52x/F52xA/F53x/F53xA devices include an on-chip 12-bit SAR ADC with a maximum throughput of 200 ksps. The ADC system includes a configurable analog multiplexer that selects the positive ADC input, which is measured with respect to GND. Ports 0 and 1 are available as ADC inputs; additionally, the ADC includes an innovative programmable gain stage which allows the ADC to sample inputs sources greater than the VREF voltage. The on-chip Temperature Sensor output and the core supply voltage (V<sub>DD</sub>) are also available as ADC inputs. User firmware may shut down the ADC or use it in Burst Mode to save power.

Conversions can be initiated in four ways: a software command, an overflow of Timer 1, an overflow of Timer 2, or an external convert start signal. This flexibility allows the start of conversion to be triggered by software events, a periodic signal (timer overflows), or external HW signals. Conversion completions are indicated by a status bit and an interrupt (if enabled) and occur after 1, 4, 8, or 16 samples have been accumulated by a hardware accumulator. The resulting 12-bit to 16-bit data word is latched into the ADC data SFRs upon completion of a conversion. When the system clock is slow, Burst Mode allows ADC0 to automatically wake from a low power shutdown state, acquire and accumulate samples, then re-enter the low power shutdown state without CPU intervention.

Window compare registers for the ADC data can be configured to interrupt the controller when ADC data is either within or outside of a specified range. The ADC can monitor a key voltage continuously in background mode, but not interrupt the controller unless the converted data is within/outside the specified range.

Figure 1.7. 12-Bit ADC Block Diagram

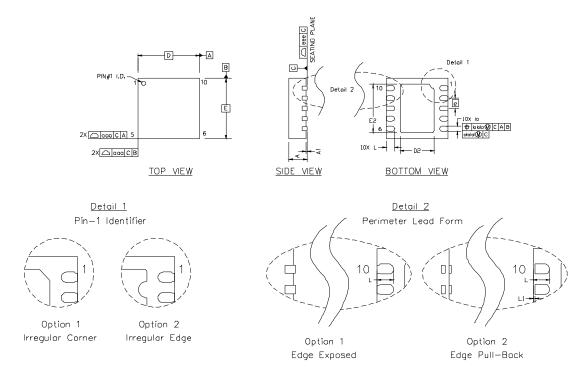

Figure 3.2. DFN-10 Package Diagram

| Dimension | Min       | Nom       | Max  |  |  |  |

|-----------|-----------|-----------|------|--|--|--|

| Α         | 0.80      | 0.90      | 1.00 |  |  |  |

| A1        | 0.00      | 0.02      | 0.05 |  |  |  |

| b         | 0.18      | 0.25      | 0.30 |  |  |  |

| D         |           | 3.00 BSC. |      |  |  |  |

| D2        | 1.50      | 1.65      | 1.80 |  |  |  |

| е         | 0.50 BSC. |           |      |  |  |  |

| E         | 3.00 BSC. |           |      |  |  |  |

| E2        | 2.23      | 2.38      | 2.53 |  |  |  |

| L         | 0.30      | 0.40      | 0.50 |  |  |  |

| L1        | 0.00      | —         | 0.15 |  |  |  |

| aaa       | —         | —         | 0.15 |  |  |  |

| bbb       | —         | —         | 0.15 |  |  |  |

| ddd       | —         | —         | 0.05 |  |  |  |

| eee       |           | —         | 0.08 |  |  |  |

#### Table 3.2. DFN-10 Package Diagram Dimensions

Notes:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- **3.** This drawing conforms to JEDEC outline MO-220, variation VEED except for custom features D2, E2, and L, which are toleranced per supplier designation.

- **4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

#### 4.3.4. Burst Mode

Burst Mode is a power saving feature that allows ADC0 to remain in a very low power state between conversions. When Burst Mode is enabled, ADC0 wakes from a very low power state, accumulates 1, 4, 8, or 16 samples using an internal Burst Mode Oscillator, then re-enters a very low power state. Since the Burst Mode clock is independent of the system clock, ADC0 can perform multiple conversions then enter a very low power state within a single system clock cycle, even if the system clock is slow (e.g. 32.768 kHz), or suspended.

Burst Mode is enabled by setting BURSTEN to logic 1. When in Burst Mode, AD0EN controls the ADC0 idle power state (i.e., the state ADC0 enters when not tracking or performing conversions). If AD0EN is set to logic 0, ADC0 is powered down after each burst. If AD0EN is set to logic 1, ADC0 remains enabled after each burst. On each convert start signal, ADC0 is awakened from its Idle Power State. If AD0C0 is powered down, it will automatically power up and wait the programmable Power-Up Time controlled by the AD0PWR bits. Otherwise, ADC0 will start tracking and converting immediately. Figure 4.5 shows an example of Burst Mode Operation with a slow system clock and a repeat count of 4.

Important Note: When Burst Mode is enabled, only Post-Tracking and Dual-Tracking modes can be used.

When Burst Mode is enabled, a single convert start will initiate a number of conversions equal to the repeat count. When Burst Mode is disabled, a convert start is required to initiate each conversion. In both modes, the ADC0 End of Conversion Interrupt Flag (AD0INT) will be set after "repeat count" conversions have been accumulated. Similarly, the Window Comparator will not compare the result to the greater-than and less-than registers until "repeat count" conversions have been accumulated.

**Note:** When using Burst Mode, care must be taken to issue a convert start signal no faster than once every four SYSCLK periods. This includes external convert start signals.

## SFR Definition 6.1. REG0CN: Regulator Control

| R/W      | R/W                                              | R                                                 | R/W           | R            | R       | R    | R            | Reset Value |  |  |  |  |  |

|----------|--------------------------------------------------|---------------------------------------------------|---------------|--------------|---------|------|--------------|-------------|--|--|--|--|--|

| REGDIS   | 8 Reserved                                       |                                                   | REG0MD        |              |         |      | DROPOUT      | 01010000    |  |  |  |  |  |

| Bit7     | Bit6                                             | Bit5                                              | Bit4          | Bit3         | Bit2    | Bit1 | Bit0         |             |  |  |  |  |  |

|          |                                                  |                                                   |               |              |         |      | SFR Address: | 0xC9        |  |  |  |  |  |

|          |                                                  |                                                   |               |              |         |      |              |             |  |  |  |  |  |

| Bit7:    |                                                  |                                                   |               |              |         |      |              |             |  |  |  |  |  |

|          | This bit disables/enables the Voltage Regulator. |                                                   |               |              |         |      |              |             |  |  |  |  |  |

|          | 0: Voltage Regulator Enabled.                    |                                                   |               |              |         |      |              |             |  |  |  |  |  |

|          | 1: Voltage Regulator Disabled.                   |                                                   |               |              |         |      |              |             |  |  |  |  |  |

| Bit6:    | <b>RESERVED</b> . Read = 1b. Must write 1b.      |                                                   |               |              |         |      |              |             |  |  |  |  |  |

| Bit5:    | UNUSED. R                                        | <b>UNUSED</b> . Read = $0b$ . Write = don't care. |               |              |         |      |              |             |  |  |  |  |  |

| Bit4:    | REGOMD: V                                        | oltage Reg                                        | ulator Mode   | Select Bit.  |         |      |              |             |  |  |  |  |  |

|          | This bit selec                                   | cts the Volt                                      | age Regulat   | or output vo | oltage. |      |              |             |  |  |  |  |  |

|          | 0: Voltage R                                     | egulator ou                                       | tput is 2.1 V |              |         |      |              |             |  |  |  |  |  |

|          | 1: Voltage R                                     | egulator ou                                       | tput is 2.6 V | ' (default). |         |      |              |             |  |  |  |  |  |

| Bits3–1: | UNUSED. R                                        | ead = 000b                                        | o. Write = do | n't care.    |         |      |              |             |  |  |  |  |  |

| Bit0:    | DROPOUT:                                         | Voltage Re                                        | gulator Drop  | out Indicat  | or Bit. |      |              |             |  |  |  |  |  |

|          | 0: Voltage R                                     | egulator is                                       | not in dropo  | ut.          |         |      |              |             |  |  |  |  |  |

|          | 1: Voltage R                                     | egulator is                                       | in or near dı | ropout.      |         |      |              |             |  |  |  |  |  |

|          |                                                  |                                                   |               |              |         |      |              |             |  |  |  |  |  |

### Table 8.1. CIP-51 Instruction Set Summary (Continued)

| Mnemonic           | Description                                | Bytes | Clock<br>Cycles |  |

|--------------------|--------------------------------------------|-------|-----------------|--|

| ORL direct, #data  | OR immediate to direct byte                | 3     | 3               |  |

| XRL A, Rn          | Exclusive-OR Register to A                 | 1     | 1               |  |

| XRL A, direct      | Exclusive-OR direct byte to A              | 2     | 2               |  |

| XRL A, @Ri         | Exclusive-OR indirect RAM to A             | 1     | 2               |  |

| XRL A, #data       | Exclusive-OR immediate to A                | 2     | 2               |  |

| XRL direct, A      | Exclusive-OR A to direct byte              | 2     | 2               |  |

| XRL direct, #data  | Exclusive-OR immediate to direct byte      | 3     | 3               |  |

| CLR A              | Clear A                                    | 1     | 1               |  |

| CPL A              | Complement A                               | 1     | 2               |  |

| RL A               | Rotate A left                              | 1     | 1               |  |

| RLC A              | Rotate A left through Carry                | 1     | 1               |  |

| RR A               | Rotate A right                             | 1     | 1               |  |

| RRC A              | Rotate A right through Carry               | 1     | 1               |  |

| SWAP A             | Swap nibbles of A                          | 1     | 1               |  |

| Data Transfer      |                                            |       |                 |  |

| MOV A, Rn          | Move Register to A                         | 1     | 1               |  |

| MOV A, direct      | Move direct byte to A                      | 2     | 2               |  |

| MOV A, @Ri         | Move indirect RAM to A                     | 1     | 2               |  |

| MOV A, #data       | Move immediate to A                        | 2     | 2               |  |

| MOV Rn, A          | Move A to Register                         | 1     | 1               |  |

| MOV Rn, direct     | Move direct byte to Register               | 2     | 2               |  |

| MOV Rn, #data      | Move immediate to Register                 | 2     | 2               |  |

| MOV direct, A      | Move A to direct byte                      | 2     | 2               |  |

| MOV direct, Rn     | Move Register to direct byte               | 2     | 2               |  |

| MOV direct, direct | Move direct byte to direct byte            | 3     | 3               |  |

| MOV direct, @Ri    | Move indirect RAM to direct byte           | 2     | 2               |  |

| MOV direct, #data  | Move immediate to direct byte              | 3     | 3               |  |

| MOV @Ri, A         | Move A to indirect RAM                     | 1     | 2               |  |

| MOV @Ri, direct    | Move direct byte to indirect RAM           | 2     | 2               |  |

| MOV @Ri, #data     | Move immediate to indirect RAM             | 2     | 2               |  |

| MOV DPTR, #data16  | Load DPTR with 16-bit constant             | 3     | 3               |  |

| MOVC A, @A+DPTR    | Move code byte relative DPTR to A          | 1     | 3               |  |

| MOVC A, @A+PC      | Move code byte relative PC to A            | 1     | 3               |  |

| MOVX A, @Ri        | Move external data (8-bit address) to A    | 1     | 3               |  |

| MOVX @Ri, A        | Move A to external data (8-bit address)    | 1     | 3               |  |

| MOVX A, @DPTR      | Move external data (16-bit address) to A   | 1     | 3               |  |

| MOVX @DPTR, A      | Move A to external data (16-bit address)   | 1     | 3               |  |

| PUSH direct        | Push direct byte onto stack                | 2     | 2               |  |

| POP direct         | Pop direct byte from stack                 | 2     | 2               |  |

| XCH A, Rn          | Exchange Register with A                   | 1     | 1               |  |

| XCH A, direct      | Exchange direct byte with A                | 2     | 2               |  |

| XCH A, @Ri         | Exchange indirect RAM with A               | 1     | 2               |  |

| XCHD A, @Ri        | Exchange low nibble of indirect RAM with A | 1     | 2               |  |

#### 8.3.1. Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the CIP-51 to halt the CPU and enter Idle mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during Idle mode.

Idle mode is terminated when an enabled interrupt is asserted or a reset occurs. The assertion of an enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU to resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

If enabled, the Watchdog Timer (WDT) will eventually cause an internal watchdog reset and thereby terminate the Idle mode. This feature protects the system from an unintended permanent shutdown in the event of an inadvertent write to the PCON register. If this behavior is not desired, the WDT may be disabled by software prior to entering the Idle mode if the WDT was initially configured to allow this operation. This provides the opportunity for additional power savings, allowing the system to remain in the Idle mode indefinitely, waiting for an external stimulus to wake up the system.

#### 8.3.2. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the CIP-51 to enter Stop mode as soon as the instruction that sets the bit completes execution. In Stop mode the internal oscillator, CPU, and all digital peripherals are stopped; the state of the external oscillator circuit is not affected. Each analog peripheral (including the external oscillator circuit) may be shut down individually prior to entering Stop Mode. Stop mode can only be terminated by an internal or external reset. On reset, the CIP-51 performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to in STOP mode for longer than the MCD timeout period of 100  $\mu$ s.

#### 8.3.3. Suspend Mode

The C8051F52x/F52xA/F53x/F53xA devices feature a low-power Suspend mode, which stops the internal oscillator until a wakening event occurs. See Section Section "14.1.1. Internal Oscillator Suspend Mode" on page 136 for more information.

Note: When entering Suspend mode, firmware must set the ZTCEN bit in REF0CN (SFR Definition 5.1).

18 system clock cycles: 1 clock cycle to detect the interrupt, 5 clock cycles to execute the RETI, 8 clock cycles to complete the DIV instruction, and 4 clock cycles to execute the LCALL to the ISR. If the CPU is executing an ISR for an interrupt with equal or higher priority, the new interrupt will not be serviced until the current ISR completes, including the RETI and following instruction.

| Table | 10.1. | Interrupt | Summary |

|-------|-------|-----------|---------|

|-------|-------|-----------|---------|

| Top<br>0<br>1<br>2<br>3<br>4<br>5<br>6 | None           IE0 (TCON.1)           TF0 (TCON.5)           IE1 (TCON.3)           TF1 (TCON.7)           RI0 (SCON0.0)           TI0 (SCON0.1)           TF2H (TMR2CN.7)           TF2L (TMR2CN.6)           SPIF (SPI0CN.7)           WCOL (SPI0CN.6)           MODF (SPI0CN.5) | N/A<br>Y<br>Y<br>Y<br>Y<br>Y<br>Y                                                           | N/A<br>Y<br>Y<br>Y<br>Y<br>N<br>N                                                                                           | Always<br>Enabled<br>EX0 (IE.0)<br>ET0 (IE.1)<br>EX1 (IE.2)<br>ET1 (IE.3)<br>ES0 (IE.4)<br>ET2 (IE.5)<br>ESPI0<br>(IE.6)                                     | Always<br>Highest<br>PX0 (IP.0)<br>PT0 (IP.1)<br>PX1 (IP.2)<br>PT1 (IP.3)<br>PS0 (IP.4)<br>PT2 (IP.5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5                  | TF0 (TCON.5)           IE1 (TCON.3)           TF1 (TCON.7)           RI0 (SCON0.0)           TI0 (SCON0.1)           TF2H (TMR2CN.7)           TF2L (TMR2CN.6)           SPIF (SPI0CN.7)           WCOL (SPI0CN.6)                                                                 | Y<br>Y<br>Y<br>Y<br>Y                                                                       | Y<br>Y<br>Y<br>N                                                                                                            | ET0 (IE.1)<br>EX1 (IE.2)<br>ET1 (IE.3)<br>ES0 (IE.4)<br>ET2 (IE.5)<br>ESPI0                                                                                  | PT0 (IP.1)<br>PX1 (IP.2)<br>PT1 (IP.3)<br>PS0 (IP.4)<br>PT2 (IP.5)<br>PSPI0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2<br>3<br>4<br>5                       | IE1 (TCON.3)<br>TF1 (TCON.7)<br>RI0 (SCON0.0)<br>TI0 (SCON0.1)<br>TF2H (TMR2CN.7)<br>TF2L (TMR2CN.6)<br>SPIF (SPI0CN.7)<br>WCOL (SPI0CN.6)                                                                                                                                         | Y<br>Y<br>Y<br>Y                                                                            | Y<br>Y<br>N<br>N                                                                                                            | EX1 (IE.2)<br>ET1 (IE.3)<br>ES0 (IE.4)<br>ET2 (IE.5)<br>ESPI0                                                                                                | PX1 (IP.2)<br>PT1 (IP.3)<br>PS0 (IP.4)<br>PT2 (IP.5)<br>PSPI0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3<br>4<br>5                            | TF1 (TCON.7)           RI0 (SCON0.0)           TI0 (SCON0.1)           TF2H (TMR2CN.7)           TF2L (TMR2CN.6)           SPIF (SPI0CN.7)           WCOL (SPI0CN.6)                                                                                                               | Y<br>Y<br>Y                                                                                 | Y<br>N<br>N                                                                                                                 | ET1 (IE.3)<br>ES0 (IE.4)<br>ET2 (IE.5)<br>ESPI0                                                                                                              | PT1 (IP.3)<br>PS0 (IP.4)<br>PT2 (IP.5)<br>PSPI0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4<br>5                                 | RI0 (SCON0.0)<br>TI0 (SCON0.1)<br>TF2H (TMR2CN.7)<br>TF2L (TMR2CN.6)<br>SPIF (SPI0CN.7)<br>WCOL (SPI0CN.6)                                                                                                                                                                         | Y<br>Y                                                                                      | N<br>N                                                                                                                      | ES0 (IE.4)<br>ET2 (IE.5)<br>ESPI0                                                                                                                            | PS0 (IP.4)<br>PT2 (IP.5)<br>PSPI0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5                                      | TI0 (SCON0.1)<br>TF2H (TMR2CN.7)<br>TF2L (TMR2CN.6)<br>SPIF (SPI0CN.7)<br>WCOL (SPI0CN.6)                                                                                                                                                                                          | Y                                                                                           | N                                                                                                                           | ET2 (IE.5)<br>ESPI0                                                                                                                                          | PT2 (IP.5)<br>PSPI0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                        | TF2L (TMR2CN.6)<br>SPIF (SPI0CN.7)<br>WCOL (SPI0CN.6)                                                                                                                                                                                                                              |                                                                                             |                                                                                                                             | ESPI0                                                                                                                                                        | PSPI0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6                                      | WCOL (SPI0CN.6)                                                                                                                                                                                                                                                                    | Y                                                                                           | Ν                                                                                                                           |                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                        | RXOVRN (SPI0CN.4)                                                                                                                                                                                                                                                                  |                                                                                             |                                                                                                                             | (IE.6)                                                                                                                                                       | (IP.6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 7                                      | ADOWINT<br>(ADC0CN.3)                                                                                                                                                                                                                                                              | Y                                                                                           | N                                                                                                                           | EWADC0<br>(EIE1.0)                                                                                                                                           | PWADC0<br>(EIP1.0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 8                                      | AD0INT (ADC0CN.5)                                                                                                                                                                                                                                                                  | Y                                                                                           | N                                                                                                                           | EADC0<br>(EIE1.1)                                                                                                                                            | PADC0<br>(EIP1.1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9                                      | CF (PCA0CN.7)<br>CCFn (PCA0CN.n)                                                                                                                                                                                                                                                   | Y                                                                                           | Ν                                                                                                                           | EPCA0<br>(EIE1.2)                                                                                                                                            | PPCA0<br>(EIP1.2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10                                     | CP0FIF (CPT0CN.4)                                                                                                                                                                                                                                                                  | N                                                                                           | Ν                                                                                                                           | ECPF<br>(EIE1.3)                                                                                                                                             | PCPF<br>(EIP1.3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 11                                     | CP0RIF (CPT0CN.5)                                                                                                                                                                                                                                                                  | Ν                                                                                           | Ν                                                                                                                           | ECPR<br>(EIE1.4)                                                                                                                                             | PCPR<br>(EIP1.4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 12                                     | LININT (LINST.3)                                                                                                                                                                                                                                                                   | N                                                                                           | N*                                                                                                                          | ELIN<br>(EIE1.5)                                                                                                                                             | PLIN<br>(EIP1.5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 13                                     | N/A                                                                                                                                                                                                                                                                                | N/A                                                                                         | N/A                                                                                                                         | EREG0<br>(EIE1.6)                                                                                                                                            | PREG0<br>(EIP1.6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |