# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

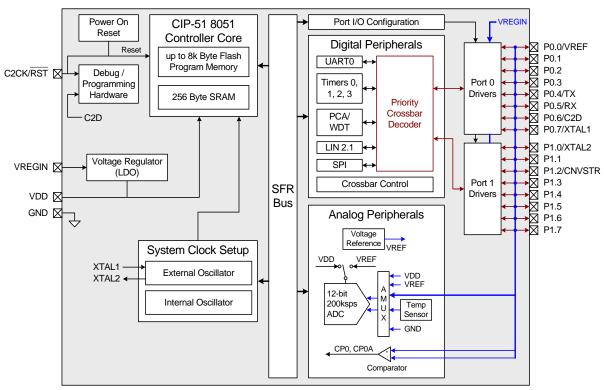

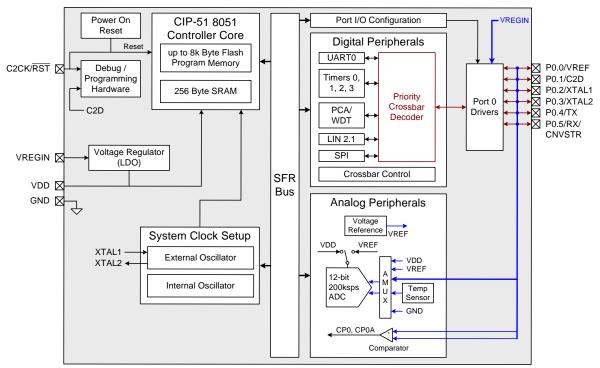

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                            |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | 8051                                                              |

| Core Size                  | 8-Bit                                                             |

| Speed                      | 25MHz                                                             |

| Connectivity               | SPI, UART/USART                                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT                |

| Number of I/O              | 16                                                                |

| Program Memory Size        | 2KB (2K x 8)                                                      |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 256 x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.25V                                                        |

| Data Converters            | A/D 16x12b                                                        |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                   |

| Supplier Device Package    | 20-TSSOP                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f537-c-itr |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table 2.2. Global DC Electrical Characteristics

-40 to +125 °C, 25 MHz System Clock unless otherwise specified. Typical values are given at 25 °C

| Parameter                                                                             | Conditions                                          | Min | Тур  | Max | Units  |  |

|---------------------------------------------------------------------------------------|-----------------------------------------------------|-----|------|-----|--------|--|

| Digital Supply Current—CPU Inactive (Idle Mode, not fetching instructions from Flash) |                                                     |     |      |     |        |  |

| Idle I <sub>DD</sub> <sup>3,4</sup>                                                   | V <sub>DD</sub> = 2.1 V:                            |     |      |     |        |  |

|                                                                                       | Clock = 32 kHz                                      | —   | 8    | —   | μA     |  |

|                                                                                       | Clock = 200 kHz                                     | —   | 22   | —   | μA     |  |

|                                                                                       | Clock = 1 MHz                                       | —   | 0.09 | —   | mA     |  |

|                                                                                       | Clock = 25 MHz                                      | —   | 2.2  | 5   | mA     |  |

|                                                                                       | V <sub>DD</sub> = 2.6 V:                            |     |      |     |        |  |

|                                                                                       | Clock = 32 kHz                                      | —   | 9    | —   | μA     |  |

|                                                                                       | Clock = 200 kHz                                     | _   | 30   | _   | μA     |  |

|                                                                                       | Clock = 1 MHz                                       | _   | 0.13 | _   | mA     |  |

|                                                                                       | Clock = 25 MHz                                      | —   | 3    | 6.5 | mA     |  |

| Idle I <sub>DD</sub> Frequency Sensitivity <sup>3,6</sup>                             | T = 25 °C:                                          |     |      |     |        |  |

|                                                                                       | V <sub>DD</sub> = 2.1 V, F <u>&lt;</u> 1 MHz        | —   | 90   | —   | µA/MHz |  |

|                                                                                       | $V_{DD} = 2.1 \text{ V}, \text{ F} > 1 \text{ MHz}$ | —   | 90   | —   | µA/MHz |  |

|                                                                                       | $V_{DD} = 2.6 V, F \le 1 MHz$                       | —   | 118  | —   | µA/MHz |  |

|                                                                                       | $V_{DD} = 2.6 \text{ V}, \text{ F} > 1 \text{ MHz}$ | —   | 118  | —   | µA/MHz |  |

| Divital Current Current <sup>3</sup>                                                  |                                                     |     |      |     |        |  |

| Digital Supply Current <sup>3</sup>                                                   | Oscillator not running,                             |     |      |     |        |  |

| (Stop or Suspend Mode)                                                                | V <sub>DD</sub> Monitor Disabled.                   |     | _    |     |        |  |

|                                                                                       | T = 25 °C                                           | —   | 2    | —   | μA     |  |

|                                                                                       | T = 60 °C                                           | —   | 3    | —   | μA     |  |

|                                                                                       | T = 125 °C                                          | —   | 50   | _   | μA     |  |

#### Notes:

- 1. For more information on  $V_{\mbox{REGIN}}$  characteristics, see Table 2.6 on page 30.

- **2.** SYSCLK must be at least 32 kHz to enable debugging.

- **3.** Based on device characterization data; Not production tested.

- 4. Does not include internal oscillator or internal regulator supply current.

- 5.  $I_{DD}$  can be estimated for frequencies <= 12 MHz by multiplying the frequency of interest by the frequency sensitivity number for that range. When using these numbers to estimate  $I_{DD}$  > 12 MHz, the estimate should be the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number. For example:  $V_{DD}$  = 2.6 V; F = 20 MHz,  $I_{DD}$  = 7.3 mA (25 MHz 20 MHz) x 0.184 mA/MHz = 6.38 mA.

- 6. Idle  $I_{DD}$  can be estimated for frequencies <= 1 MHz by multiplying the frequency of interest by the frequency sensitivity number for that range. When using these numbers to estimate  $I_{DD}$  > 1 MHz, the estimate should be the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number. For example:  $V_{DD}$  = 2.6 V; F= 5 MHz, Idle  $I_{DD}$  = 3 mA (25 MHz– 5 MHz) x 118 µA/MHz = 0.64 mA.

#### Table 2.11. Internal Oscillator Electrical Characteristics

$V_{DD}$  = 1.8 to 2.75 V, -40 to +125 °C unless otherwise specified; Using factory-calibrated settings.

| Parameter                            | Conditions                                                                                   | Min         | Тур               | Max         | Units                 |

|--------------------------------------|----------------------------------------------------------------------------------------------|-------------|-------------------|-------------|-----------------------|

| Oscillator Frequency <sup>1</sup>    | $\begin{array}{l} \text{IFCN} = 111\text{b} \\ \text{VDD} \geq \text{VREGMIN}^2 \end{array}$ | 24.5 – 0.5% | 24.5 <sup>3</sup> | 24.5 + 0.5% | MHz                   |

|                                      | IFCN = 111b<br>VDD < VREGMIN <sup>2</sup>                                                    | 24.5 – 1.0% | 24.5 <sup>3</sup> | 24.5 + 1.0% |                       |

|                                      | Oscillator On<br>OSCICN[7:6] = 11b                                                           | —           | 800               | 1100        | μA                    |

|                                      | Oscillator Suspend<br>OSCICN[7:6] = 00b<br>ZTCEN = 1                                         |             |                   |             |                       |

|                                      | T = 25 °C                                                                                    | _           | 67                | _           | μA                    |

| Oscillator Supply Current            | T = 85 °C                                                                                    | _           | 77                | —           | μA                    |

| (from V <sub>DD</sub> )              | T = 125 °C                                                                                   | _           | 117               | 300         | μA                    |

|                                      | Oscillator Suspend<br>OSCICN[7:6] = 00b<br>ZTCEN = 0                                         |             |                   |             |                       |

|                                      | T = 25 °C                                                                                    | _           | 2                 | _           | μA                    |

|                                      | T = 85 °C                                                                                    | _           | 3                 | _           | μA                    |

|                                      | T = 125 °C                                                                                   | _           | 50                | _           | μA                    |

| Wake-Up Time From Sus-<br>pend       | $\frac{\text{OSCICN[7:6]} = 00b}{\text{ZTCEN} = 0^4}$                                        | —           | _                 | 1           | μs                    |

|                                      | OSCICN[7:6] = 00b<br>ZTCEN = 1                                                               | —           | 5                 | _           | Instruction<br>Cycles |

| Power Supply Sensitivity             | Constant Temperature                                                                         |             | 0.10              |             | %/V                   |

| Temperature Sensitivity <sup>5</sup> | Constant Supply<br>TC <sub>1</sub>                                                           | _           | 5.0               | _           | ppm/°C                |

|                                      | TC <sub>2</sub>                                                                              | —           | -0.65             | —           | ppm/°C <sup>2</sup>   |

Notes:

1. See Section "11.2.1. VDD Monitor Thresholds and Minimum VDD" on page 108 for minimum  $V_{DD}$  requirements.

- VREGMIN is the minimum output of the voltage regulator for its low setting (REG0CN: REG0MD = 0b). See Table 2.6, "Voltage Regulator Electrical Specifications," on page 30.

- 3. This is the average frequency across the operating temperature range.

- 4. See "20.7. Internal Oscillator Suspend Mode" on page 212 for ZTCEN setting in older silicon revisions.

- 5. Use temperature coefficients  $TC_1$  and  $TC_2$  to calculate the new internal oscillator frequency using the following equation:

$$f(T) = f0 x (1 + TC_1 x (T - T0) + TC_2 x (T - T0)^2)$$

where f0 is the internal oscillator frequency at 25 °C and T0 is 25 °C.

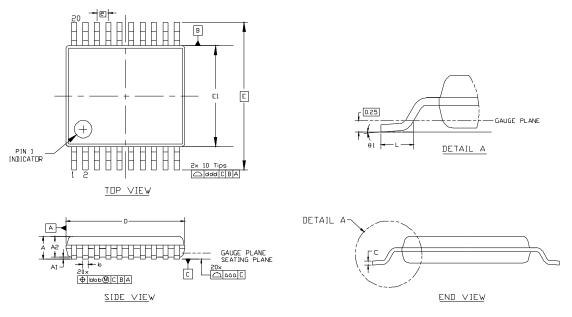

#### Figure 3.5. TSSOP-20 Package Diagram

| Symbol | Min  | Nom       | Мах  |

|--------|------|-----------|------|

| A      |      |           | 1.20 |

| A1     | 0.05 |           | 0.15 |

| A2     | 0.80 | 1.00      | 1.05 |

| b      | 0.19 |           | 0.30 |

| С      | 0.09 | —         | 0.20 |

| D      | 6.40 | 6.50      | 6.60 |

| е      |      | 0.65 BSC. |      |

| E      |      | 6.40 BSC. |      |

| E1     | 4.30 | 4.40      | 4.50 |

| L      | 0.45 | 0.60      | 0.75 |

| θ1     | 0°   | —         | 8°   |

| aaa    |      | 0.10      |      |

| bbb    |      | 0.10      |      |

| ddd    |      | 0.20      |      |

| otes:  |      |           |      |

#### Table 3.5. TSSOP-20 Package Diagram Dimensions

1. All dimensions shown are in millimeters (mm).

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This drawing conforms to JEDEC outline MO-153, variation AC.

**4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

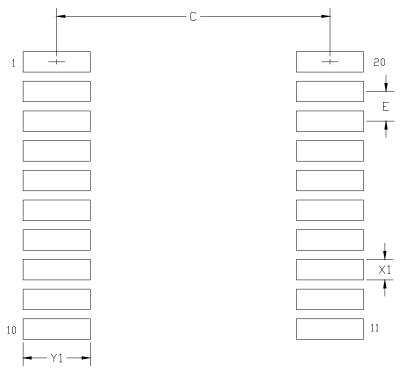

## Figure 3.6. TSSOP-20 Landing Diagram

#### Table 3.6. TSSOP-20 Landing Diagram Dimensions

|                | Symbol                                                                                                                                                                                                                                                                                                             | Min                                                                                             | Max                |  |  |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------|--|--|--|

|                | С                                                                                                                                                                                                                                                                                                                  | 5.80                                                                                            | 5.90               |  |  |  |

|                | E                                                                                                                                                                                                                                                                                                                  | 0.65 BS                                                                                         | SC.                |  |  |  |

|                | X1                                                                                                                                                                                                                                                                                                                 | 0.35                                                                                            | 0.45               |  |  |  |

|                | Y1                                                                                                                                                                                                                                                                                                                 | 1.35                                                                                            | 1.45               |  |  |  |

| Notes          | :                                                                                                                                                                                                                                                                                                                  |                                                                                                 |                    |  |  |  |

| Gene           | ral                                                                                                                                                                                                                                                                                                                |                                                                                                 |                    |  |  |  |

| 2.             |                                                                                                                                                                                                                                                                                                                    | own are in millimeters (mm) design is based on the IPC-7                                        |                    |  |  |  |

|                | between the sold<br>all the way around                                                                                                                                                                                                                                                                             | e to be non-solder mask defin<br>er mask and the metal pad is<br>d the pad.                     |                    |  |  |  |

| 4.<br>5.<br>6. | <ol> <li>A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.</li> <li>The stencil thickness should be 0.125 mm (5 mils).</li> <li>The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.</li> </ol> |                                                                                                 |                    |  |  |  |

| Card           | <u>Assembly</u>                                                                                                                                                                                                                                                                                                    |                                                                                                 |                    |  |  |  |

|                | The recommende                                                                                                                                                                                                                                                                                                     | e-3 solder paste is recommen<br>id card reflow profile is per the<br>for Small Body Components. | e JEDEC/IPC J-STD- |  |  |  |

## 6. Voltage Regulator (REG0)

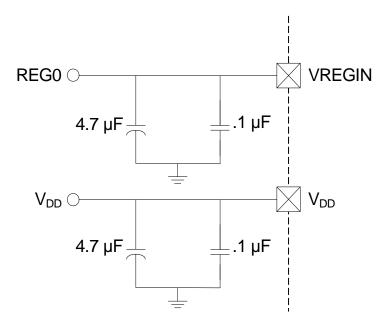

C8051F52x/F52xA/F53x/F53xAdevices include an on-chip low dropout voltage regulator (REG0). The input to REG0 at the V<sub>REGIN</sub> pin can be as high as 5.25 V. The output can be selected by software to 2.1 V or 2.6 V. When enabled, the output of REG0 appears on the V<sub>DD</sub> pin, powers the microcontroller core, and can be used to power external devices. On reset, REG0 is enabled and can be disabled by software.

The input ( $V_{REGIN}$ ) and output ( $V_{DD}$ ) of the voltage regulator should both be bypassed with a large capacitor (4.7  $\mu$ F + 0.1  $\mu$ F) to ground. These capacitors are required for regulator stability, and will eliminate power spikes and provide any immediate power required by the microcontroller. The settling time associated with the voltage regulator is shown in Table 2.6 on page 30.

#### Important Note: The bypass capacitors are required for the stability of the voltage regulator.

The voltage regulator can also generate an interrupt (if enabled by EREG0, EIE1.6) that is triggered whenever the  $V_{\text{REGIN}}$  input voltage drops below the dropout threshold (see Table 2.6 on page 30). This dropout interrupt has no pending flag. The recommended procedure to use the interrupt is as follows:

- 1. Wait enough time to ensure the V<sub>REGIN</sub> input voltage is stable.

- 2. Enable the dropout interrupt (EREG0, EIE1.6) and select the proper priority (PREG0, EIP1.6).

- 3. If triggered, disable the interrupt in the Interrupt Service Routine (clear EREG0, EIE1.6) and execute all necessary procedures to put the system in "safe mode," leaving the interrupt disabled.

- 4. The main application, now running in safe mode, should regularly check the DROPOUT bit (REG0CN.0). Once it is cleared by the regulator hardware, the application can re-enable the interrupt (EREG0, EIE1.6) and return to normal mode operation.

Figure 6.1. External Capacitors for Voltage Regulator Input/Output

#### 8.3.1. Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the CIP-51 to halt the CPU and enter Idle mode as soon as the instruction that sets the bit completes execution. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during Idle mode.

Idle mode is terminated when an enabled interrupt is asserted or a reset occurs. The assertion of an enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU to resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

If enabled, the Watchdog Timer (WDT) will eventually cause an internal watchdog reset and thereby terminate the Idle mode. This feature protects the system from an unintended permanent shutdown in the event of an inadvertent write to the PCON register. If this behavior is not desired, the WDT may be disabled by software prior to entering the Idle mode if the WDT was initially configured to allow this operation. This provides the opportunity for additional power savings, allowing the system to remain in the Idle mode indefinitely, waiting for an external stimulus to wake up the system.

#### 8.3.2. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the CIP-51 to enter Stop mode as soon as the instruction that sets the bit completes execution. In Stop mode the internal oscillator, CPU, and all digital peripherals are stopped; the state of the external oscillator circuit is not affected. Each analog peripheral (including the external oscillator circuit) may be shut down individually prior to entering Stop Mode. Stop mode can only be terminated by an internal or external reset. On reset, the CIP-51 performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to in STOP mode for longer than the MCD timeout period of 100  $\mu$ s.

#### 8.3.3. Suspend Mode

The C8051F52x/F52xA/F53x/F53xA devices feature a low-power Suspend mode, which stops the internal oscillator until a wakening event occurs. See Section Section "14.1.1. Internal Oscillator Suspend Mode" on page 136 for more information.

Note: When entering Suspend mode, firmware must set the ZTCEN bit in REF0CN (SFR Definition 5.1).

## **10. Interrupt Handler**

The C8051F52x/F52xA/F53x/F53xA family includes an extended interrupt system with two selectable priority levels. The allocation of interrupt sources between on-chip peripherals and external input pins varies according to the specific version of the device. Each interrupt source has one or more associated interruptpending flag(s) located in an SFR. When a peripheral or external source meets a valid interrupt condition, the associated interrupt-pending flag is set to logic 1.

If interrupts are enabled for the source, an interrupt request is generated when the interrupt-pending flag is set. As soon as execution of the current instruction is complete, the CPU generates an LCALL to a predetermined address to begin execution of an interrupt service routine (ISR). Each ISR must end with an RETI instruction, which returns program execution to the next instruction that would have been executed if the interrupt request had not occurred. If interrupts are not enabled, the interrupt-pending flag is ignored by the hardware and program execution continues as normal. (The interrupt-pending flag is set to logic 1 regardless of the interrupt's enable/disable state.)

Each interrupt source can be individually enabled or disabled through the use of an associated interrupt enable bit in the Interrupt Enable and Extended Interrupt Enable SFRs. However, interrupts must first be globally enabled by setting the EA bit (IE.7) to logic 1 before the individual interrupt enables are recognized. Setting the EA bit to logic 0 disables all interrupt sources regardless of the individual interrupt-enable settings. Note that interrupts which occur when the EA bit is set to logic 0 will be held in a pending state, and will not be serviced until the EA bit is set back to logic 1.

Some interrupt-pending flags are automatically cleared by the hardware when the CPU vectors to the ISR. However, most are not cleared by the hardware and must be cleared by software before returning from the ISR. If an interrupt-pending flag remains set after the CPU completes the return-from-interrupt (RETI) instruction, a new interrupt request will be generated immediately and the CPU will re-enter the ISR after the completion of the next instruction.

#### **10.1. MCU Interrupt Sources and Vectors**

The C8051F52x/F52xA/F53x/F53xA MCUs support 15 interrupt sources. Software can simulate an interrupt by setting any interrupt-pending flag to logic 1. If interrupts are enabled for the flag, an interrupt request will be generated and the CPU will vector to the ISR address associated with the interrupt-pending flag. MCU interrupt sources, associated vector addresses, priority order, and control bits are summarized in Table 10.1 on page 99. Refer to the data sheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

#### **10.2. Interrupt Priorities**

Each interrupt source can be individually programmed to one of two priority levels: low or high. A low priority interrupt service routine can be preempted by a high priority interrupt. A high priority interrupt cannot be preempted. Each interrupt has an associated interrupt priority bit in an SFR (IP or EIP1) used to configure its priority level. Low priority is the default. If two interrupts are recognized simultaneously, the interrupt with the higher priority is serviced first. If both interrupts have the same priority level, a fixed priority order is used to arbitrate, given in Table 10.1.

#### 10.3. Interrupt Latency

Interrupt response time depends on the state of the CPU when the interrupt occurs. Pending interrupts are sampled and priority decoded each system clock cycle. Therefore, the fastest possible response time is 5 system clock cycles: 1 clock cycle to detect the interrupt and 4 clock cycles to complete the LCALL to the ISR. If an interrupt is pending when a RETI is executed, a single instruction is executed before an LCALL is made to service the pending interrupt. Therefore, the maximum response time for an interrupt (when no other interrupt is currently being serviced or the new interrupt is of greater priority) occurs when the CPU is performing an RETI instruction followed by a DIV as the next instruction. In this case, the response time is

18 system clock cycles: 1 clock cycle to detect the interrupt, 5 clock cycles to execute the RETI, 8 clock cycles to complete the DIV instruction, and 4 clock cycles to execute the LCALL to the ISR. If the CPU is executing an ISR for an interrupt with equal or higher priority, the new interrupt will not be serviced until the current ISR completes, including the RETI and following instruction.

| Table | 10.1. | Interrupt | Summary |

|-------|-------|-----------|---------|

|-------|-------|-----------|---------|

| Top<br>0<br>1<br>2<br>3<br>4<br>5<br>6 | None           IE0 (TCON.1)           TF0 (TCON.5)           IE1 (TCON.3)           TF1 (TCON.7)           RI0 (SCON0.0)           TI0 (SCON0.1)           TF2H (TMR2CN.7)           TF2L (TMR2CN.6)           SPIF (SPI0CN.7)           WCOL (SPI0CN.6)           MODF (SPI0CN.5) | N/A<br>Y<br>Y<br>Y<br>Y<br>Y<br>Y                                                           | N/A<br>Y<br>Y<br>Y<br>Y<br>N<br>N                                                                                           | Always<br>Enabled<br>EX0 (IE.0)<br>ET0 (IE.1)<br>EX1 (IE.2)<br>ET1 (IE.3)<br>ES0 (IE.4)<br>ET2 (IE.5)<br>ESPI0<br>(IE.6)                                     | Always<br>Highest<br>PX0 (IP.0)<br>PT0 (IP.1)<br>PX1 (IP.2)<br>PT1 (IP.3)<br>PS0 (IP.4)<br>PT2 (IP.5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5                  | TF0 (TCON.5)           IE1 (TCON.3)           TF1 (TCON.7)           RI0 (SCON0.0)           TI0 (SCON0.1)           TF2H (TMR2CN.7)           TF2L (TMR2CN.6)           SPIF (SPI0CN.7)           WCOL (SPI0CN.6)                                                                 | Y<br>Y<br>Y<br>Y<br>Y                                                                       | Y<br>Y<br>Y<br>N                                                                                                            | ET0 (IE.1)<br>EX1 (IE.2)<br>ET1 (IE.3)<br>ES0 (IE.4)<br>ET2 (IE.5)<br>ESPI0                                                                                  | PT0 (IP.1)<br>PX1 (IP.2)<br>PT1 (IP.3)<br>PS0 (IP.4)<br>PT2 (IP.5)<br>PSPI0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2<br>3<br>4<br>5                       | IE1 (TCON.3)<br>TF1 (TCON.7)<br>RI0 (SCON0.0)<br>TI0 (SCON0.1)<br>TF2H (TMR2CN.7)<br>TF2L (TMR2CN.6)<br>SPIF (SPI0CN.7)<br>WCOL (SPI0CN.6)                                                                                                                                         | Y<br>Y<br>Y<br>Y                                                                            | Y<br>Y<br>N<br>N                                                                                                            | EX1 (IE.2)<br>ET1 (IE.3)<br>ES0 (IE.4)<br>ET2 (IE.5)<br>ESPI0                                                                                                | PX1 (IP.2)<br>PT1 (IP.3)<br>PS0 (IP.4)<br>PT2 (IP.5)<br>PSPI0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3<br>4<br>5                            | TF1 (TCON.7)           RI0 (SCON0.0)           TI0 (SCON0.1)           TF2H (TMR2CN.7)           TF2L (TMR2CN.6)           SPIF (SPI0CN.7)           WCOL (SPI0CN.6)                                                                                                               | Y<br>Y<br>Y                                                                                 | Y<br>N<br>N                                                                                                                 | ET1 (IE.3)<br>ES0 (IE.4)<br>ET2 (IE.5)<br>ESPI0                                                                                                              | PT1 (IP.3)<br>PS0 (IP.4)<br>PT2 (IP.5)<br>PSPI0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4<br>5                                 | RI0 (SCON0.0)<br>TI0 (SCON0.1)<br>TF2H (TMR2CN.7)<br>TF2L (TMR2CN.6)<br>SPIF (SPI0CN.7)<br>WCOL (SPI0CN.6)                                                                                                                                                                         | Y<br>Y                                                                                      | N<br>N                                                                                                                      | ES0 (IE.4)<br>ET2 (IE.5)<br>ESPI0                                                                                                                            | PS0 (IP.4)<br>PT2 (IP.5)<br>PSPI0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5                                      | TI0 (SCON0.1)<br>TF2H (TMR2CN.7)<br>TF2L (TMR2CN.6)<br>SPIF (SPI0CN.7)<br>WCOL (SPI0CN.6)                                                                                                                                                                                          | Y                                                                                           | N                                                                                                                           | ET2 (IE.5)<br>ESPI0                                                                                                                                          | PT2 (IP.5)<br>PSPI0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                        | TF2L (TMR2CN.6)<br>SPIF (SPI0CN.7)<br>WCOL (SPI0CN.6)                                                                                                                                                                                                                              |                                                                                             |                                                                                                                             | ESPI0                                                                                                                                                        | PSPI0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6                                      | WCOL (SPI0CN.6)                                                                                                                                                                                                                                                                    | Y                                                                                           | Ν                                                                                                                           |                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                        | RXOVRN (SPI0CN.4)                                                                                                                                                                                                                                                                  |                                                                                             |                                                                                                                             | (IE.6)                                                                                                                                                       | (IP.6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 7                                      | ADOWINT<br>(ADC0CN.3)                                                                                                                                                                                                                                                              | Y                                                                                           | N                                                                                                                           | EWADC0<br>(EIE1.0)                                                                                                                                           | PWADC0<br>(EIP1.0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 8                                      | AD0INT (ADC0CN.5)                                                                                                                                                                                                                                                                  | Y                                                                                           | N                                                                                                                           | EADC0<br>(EIE1.1)                                                                                                                                            | PADC0<br>(EIP1.1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9                                      | CF (PCA0CN.7)<br>CCFn (PCA0CN.n)                                                                                                                                                                                                                                                   | Y                                                                                           | Ν                                                                                                                           | EPCA0<br>(EIE1.2)                                                                                                                                            | PPCA0<br>(EIP1.2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10                                     | CP0FIF (CPT0CN.4)                                                                                                                                                                                                                                                                  | N                                                                                           | Ν                                                                                                                           | ECPF<br>(EIE1.3)                                                                                                                                             | PCPF<br>(EIP1.3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 11                                     | CP0RIF (CPT0CN.5)                                                                                                                                                                                                                                                                  | Ν                                                                                           | Ν                                                                                                                           | ECPR<br>(EIE1.4)                                                                                                                                             | PCPR<br>(EIP1.4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 12                                     | LININT (LINST.3)                                                                                                                                                                                                                                                                   | N                                                                                           | N*                                                                                                                          | ELIN<br>(EIE1.5)                                                                                                                                             | PLIN<br>(EIP1.5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 13                                     | N/A                                                                                                                                                                                                                                                                                | N/A                                                                                         | N/A                                                                                                                         | EREG0<br>(EIE1.6)                                                                                                                                            | PREG0<br>(EIP1.6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 14                                     | N/A                                                                                                                                                                                                                                                                                | N/A                                                                                         | N/A                                                                                                                         | EMAT<br>(EIE1.7)                                                                                                                                             | PMAT<br>(EIP1.7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |