Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | -                                                                       |

| Core Size                  | -                                                                       |

| Speed                      | -                                                                       |

| Connectivity               | -                                                                       |

| Peripherals                | -                                                                       |

| Number of I/O              | -                                                                       |

| Program Memory Size        | -                                                                       |

| Program Memory Type        | -                                                                       |

| EEPROM Size                | -                                                                       |

| RAM Size                   | •                                                                       |

| Voltage - Supply (Vcc/Vdd) | -                                                                       |

| Data Converters            | -                                                                       |

| Oscillator Type            | -                                                                       |

| Operating Temperature      | -                                                                       |

| Mounting Type              | -                                                                       |

| Package / Case             | -                                                                       |

| Supplier Device Package    | •                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6g3dvk05ab |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### i.MX 6UltraLite introduction

| Peripheral Name | Instance | G0 | G1 | G2 | G3 |

|-----------------|----------|----|----|----|----|

| Timer/PWM       | EPIT1    | Y  | Y  | Y  | Y  |

|                 | EPIT2    | NA | Y  | Y  | Y  |

|                 | GPT1     | Y  | Y  | Y  | Y  |

|                 | GPT2     | NA | Y  | Y  | Y  |

|                 | PWM1     | Y  | Y  | Y  | Y  |

|                 | PWM2     | Y  | Y  | Y  | Y  |

|                 | PWM3     | Y  | Y  | Y  | Y  |

|                 | PWM4     | Y  | Y  | Y  | Y  |

|                 | PWM5     | NA | Y  | Y  | Y  |

|                 | PWM6     | NA | Y  | Y  | Y  |

|                 | PWM7     | NA | Y  | Y  | Y  |

|                 | PWM8     | NA | Y  | Y  | Y  |

| ADC             | ADC1     | Y  | Y  | Y  | Y  |

|                 | ADC2     | NA | NA | Y  | Y  |

Table 2. Detailed Peripherals Information (continued)<sup>1,2,3</sup>

<sup>1</sup>For detailed pin mux information, please refer to "Chapter 4 External Signals and Pin Multiplexing" of *i.MX* 6UltraLite Refer*ence Manual* (IMX6ULRM). <sup>2</sup> Y stands for yes, NA stands for not available.

<sup>3</sup> G0 and G3 are not offered in automotive grade.

#### 1.2 **Features**

The i.MX 6UltraLite processors are based on ARM Cortex-A7 MPCore<sup>TM</sup> Platform, which has the following features:

- Supports single ARM Cortex-A7 MPCore (with TrustZone) with:

- 32 KBytes L1 Instruction Cache

- 32 KBytes L1 Data Cache

- Private Timer

- Cortex-A7 NEON Media Processing Engine (MPE) Co-processor

- General Interrupt Controller (GIC) with 128 interrupts support ٠

- Global Timer ٠

- Snoop Control Unit (SCU) ٠

- 128 KB unified I/D L2 cache (on G2 and G3 devices only) ٠

- Single Master AXI bus interface output of L2 cache (for G2 and G3 devices only) ٠

- Frequency of the core (including Neon and L1 cache), as per Table 11, "Operating Ranges," on ٠ page 23.

#### i.MX 6UltraLite introduction

- Four  $I^2C$

- Two 10/100 Ethernet Controller (IEEE1588 compliant)

- Eight Pulse Width Modulators (PWM)

- System JTAG Controller (SJC)

- GPIO with interrupt capabilities

- 8x8 Key Pad Port (KPP)

- One Quad SPI

- Two Flexible Controller Area Network (FlexCAN)

- Three Watchdog timers (WDOG)

- Two 12-bit Analog to Digital Converters (ADC) with up to 10 input channels in total

- Touch Screen Controller (TSC)

The i.MX 6UltraLite processors integrate advanced power management unit and controllers:

- Provide PMU, including LDO supplies, for on-chip resources

- Use Temperature Sensor for monitoring the die temperature

- Use Voltage Sensor for monitoring the die voltage

- Support DVFS techniques for low power modes

- Use SW State Retention and Power Gating for ARM and NEON

- Support various levels of system power modes

- Use flexible clock gating control scheme

- Two smart card interfaces compatible with EVM Standard 4.3

The i.MX 6UltraLite processors use dedicated hardware accelerators to meet the targeted multimedia performance. The use of hardware accelerators is a key factor in obtaining high performance at low power consumption, while having the CPU core relatively free for performing other tasks.

The i.MX 6UltraLite processors incorporate the following hardware accelerators:

- PXP—Pixel Processing Pipeline for imagine resize, rotation, overlay, and CSC<sup>1</sup>. Off loading key pixel processing operations are required to support the LCD display applications.

- ASRC—Asynchronous Sample Rate Converter

Security functions are enabled and accelerated by the following hardware:

- ARM TrustZone including the TZ architecture (separation of interrupts, memory mapping, etc.)

- SJC—System JTAG Controller. Protecting JTAG from debug port attacks by regulating or blocking the access to the system debug features.

- CAAM—Cryptographic Acceleration and Assurance Module, containing cryptographic and hash engines, 32 KB secure RAM, and True and Pseudo Random Number Generator (NIST certified).

- SNVS—Secure Non-Volatile Storage, including Secure Real Time Clock.

- CSU—Central Security Unit. CSU is configured during boot and by eFUSEs and determine the security level operation mode as well as the TZ policy.

1. G2 and G3 only

| Block Mnemonic                                               | Block Name                          | Subsystem                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------|-------------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPMI                                                         | General Purpose<br>Memory Interface | Connectivity<br>Peripherals | The GPMI module supports up to 8x NAND devices and 40-bit ECC for NAND Flash Controller (GPMI2). GPMI supports separate DMA channels for each NAND device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| GPT1<br>GPT2                                                 | General Purpose Timer               | Timer peripherals           | Each GPT is a 32-bit "free-running" or "set and forget"<br>mode timer with programmable prescaler and compare<br>and capture register. A timer counter value can be<br>captured using an external event and can be configured<br>to trigger a capture event on either the leading or trailing<br>edges of an input pulse. When the timer is configured to<br>operate in "set and forget" mode, it is capable of<br>providing precise interrupts at regular intervals with<br>minimal processor intervention. The counter has output<br>compare logic to provide the status and interrupt at<br>comparison. This timer can be configured to run either<br>on an external clock or on an internal clock. |

| LCDIF                                                        | LCD interface                       | Connectivity<br>peripherals | The LCDIF is a general purpose display controller used<br>to drive a wide range of display devices varying in size<br>and capability. The LCDIF is designed to support dumb<br>(synchronous 24-bit Parallel RGB interface) and smart<br>(asynchronous parallel MPU interface) LCD devices.                                                                                                                                                                                                                                                                                                                                                                                                             |

| MQS                                                          | Medium Quality Sound                | Multimedia<br>Peripherals   | MQS is used to generate 2-channel medium quality PWM-like audio via two standard digital GPIO pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PWM1<br>PWM2<br>PWM3<br>PWM4<br>PWM5<br>PWM6<br>PWM7<br>PWM8 | Pulse Width Modulation              | Connectivity<br>peripherals | The pulse-width modulator (PWM) has a 16-bit counter<br>and is optimized to generate sound from stored sample<br>audio images and it can also generate tones. It uses<br>16-bit resolution and a 4x16 data FIFO to generate<br>sound.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| РХР                                                          | Pixel Processing Pipeline           | Display peripherals         | A high-performance pixel processor capable of 1<br>pixel/clock performance for combined operations, such<br>as color-space conversion, alpha blending,<br>gamma-mapping, and rotation. The PXP is enhanced<br>with features specifically for gray scale applications. In<br>addition, the PXP supports traditional pixel/frame<br>processing paths for still-image and video processing<br>applications, allowing it to interface with the integrated<br>EPD.                                                                                                                                                                                                                                          |

| Table 3. i.MX 6UltraLite | Modules | List (co | ntinued) |

|--------------------------|---------|----------|----------|

|--------------------------|---------|----------|----------|

**Modules List**

# 3.1 Special signal considerations

Table 4 lists special signal considerations for the i.MX 6UltraLite processors. The signal names are listed in alphabetical order.

The package contact assignments can be found in Section 6, "Package information and contact assignments"." Signal descriptions are provided in the *i.MX 6UltraLite Reference Manual* (IMX6ULRM).

| Signal Name               | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CCM_CLK1_P/<br>CCM_CLK1_N | <ul> <li>One general purpose differential high speed clock Input/output is provided.</li> <li>It can be used: <ul> <li>To feed external reference clock to the PLLs and further to the modules inside SoC.</li> <li>To output internal SoC clock to be used outside the SoC as either reference clock or as a functional clock for peripherals.</li> </ul> </li> <li>See the <i>i.MX</i> 6UltraLite Reference Manual (IMX6ULRM) for details on the respective clock trees. Alternatively one may use single ended signal to drive CLK1_P input. In this case corresponding CLK1_N input should be tied to the constant voltage level equal 1/2 of the input signal swing. Termination should be provided in case of high frequency signals. After initialization, the CLK1 input/output can be disabled (if not used). If unused either or both of the CLK1_N/P pairs may be remain unconnected.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                          |

| RTC_XTALI/RTC_XTALO       | If the user wishes to configure RTC_XTALI and RTC_XTALO as an RTC oscillator, a 32.768 kHz crystal, ( $\leq$ 100 k $\Omega$ ESR, 10 pF load) should be connected between RTC_XTALI and RTC_XTALO. Keep in mind the capacitors implemented on either side of the crystal are about twice the crystal load capacitor. To hit the exact oscillation frequency, the board capacitors need to be reduced to account for board and chip parasitics. The integrated oscillation amplifier is self biasing, but relatively weak. Care must be taken to limit parasitic leakage from RTC_XTALI and RTC_XTALO to either power or ground (>100 M $\Omega$ ). This will debias the amplifier and cause a reduction of startup margin. Typically RTC_XTALI and RTC_XTALO should bias to approximately 0.5 V. If it is desired to feed an external low frequency clock into RTC_XTALI, the RTC_XTALO pin must remain unconnected or driven with a complimentary signal. The logic level of this forcing clock should not exceed VDD_SNVS_CAP level and the frequency should be <100 kHz under typical conditions. In case when high accuracy real time clock are not required system may use internal low frequency ring oscillator. It is recommended to connect RTC_XTALI to GND and keep RTC_XTALO unconnected. |

| XTALI/XTALO               | A 24.0 MHz crystal should be connected between XTALI and XTALO.<br>The crystal must be rated for a maximum drive level of 250 $\mu$ W. An ESR (equivalent series resistance) of typical 80 $\Omega$ is recommended. NXP BSP (board support package) software requires 24 MHz on XTALI/XTALO.<br>The crystal can be eliminated if an external 24 MHz oscillator is available in the system. In this case, XTALO must be directly driven by the external oscillator and XTALI mounted with 18 pF capacitor. Please refer to the EVK board reference design for details. The logic level of this forcing clock cannot exceed NVCC_PLL level.<br>If this clock is used as a reference for USB, then there are strict frequency tolerance and jitter requirements. See OSC24M chapter and relevant interface specifications chapters for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### Table 4. Special Signal Considerations

The RTC\_XTALI is used for low-frequency functions. It supplies the clock for wake-up circuit, power-down real time clock operation, and slow system and watch-dog counters. The clock input can be connected to either external oscillator or a crystal using internal oscillator amplifier. Additionally, there is an internal ring oscillator, which can be used instead of the RTC\_XTALI if accuracy is not important.

The system clock input XTALI is used to generate the main system clock. It supplies the PLLs and other peripherals. The system clock input can be connected to either external oscillator or a crystal using internal oscillator amplifier.

Table 13 shows the interface frequency requirements.

Table 13. External Input Clock Frequency

| Parameter Description               | Symbol            | Min | Тур                       | Мах | Unit |

|-------------------------------------|-------------------|-----|---------------------------|-----|------|

| RTC_XTALI Oscillator <sup>1,2</sup> | f <sub>ckil</sub> | _   | 32.768 <sup>3</sup> /32.0 |     | kHz  |

| XTALI Oscillator <sup>2,4</sup>     | f <sub>xtal</sub> | _   | 24                        |     | MHz  |

<sup>1</sup> External oscillator or a crystal with internal oscillator amplifier.

<sup>2</sup> The required frequency stability of this clock source is application dependent. For recommendations, see the Hardware Development Guide for *i.MX 6UltraLite Applications Processors* (IMX6ULHDG).

<sup>3</sup> Recommended nominal frequency 32.768 kHz.

<sup>4</sup> External oscillator or a fundamental frequency crystal with internal oscillator amplifier.

The typical values shown in Table 13 are required for use with NXP BSPs to ensure precise time keeping and USB operation. For RTC\_XTALI operation, two clock sources are available.

- On-chip 40 kHz ring oscillator—this clock source has the following characteristics:

- Approximately 25 µA more Idd than crystal oscillator

- Approximately  $\pm 50\%$  tolerance

- No external component required

- Starts up quicker than 32 kHz crystal oscillator

- External crystal oscillator with on-chip support circuit:

- At power up, ring oscillator is utilized. After crystal oscillator is stable, the clock circuit switches over to the crystal oscillator automatically.

- Higher accuracy than ring oscillator

- If no external crystal is present, then the ring oscillator is utilized

The decision of choosing a clock source should be taken based on real-time clock use and precision time-out.

# 4.1.5 Maximum supply currents

The data shown in Table 14 represent a use case designed specifically to show the maximum current consumption possible. All cores are running at the defined maximum frequency and are limited to L1 cache accesses only to ensure no pipeline stalls. Although a valid condition, it would have a very limited practical use case, if at all, and be limited to an extremely low duty cycle unless the intention was to specifically show the worst case power consumption.

| Parameters                               | Symbol   | Test Conditions   | Min               | Max               | Unit |

|------------------------------------------|----------|-------------------|-------------------|-------------------|------|

| DC High-Level input voltage              | Vih_DC   | —                 | Vref+0.13         | OVDD              | V    |

| DC Low-Level input voltage               | Vil_DC   | —                 | OVSS              | Vref-0.13         | V    |

| Differential Input Logic High            | Vih_diff | —                 | 0.26              | Note <sup>2</sup> | _    |

| Differential Input Logic Low             | Vil_diff | —                 | Note <sup>2</sup> | -0.26             |      |

| Pull-up/Pull-down Impedance Mismatch     | Mmpupd   | —                 | -15               | 15                | %    |

| 240 $\Omega$ unit calibration resolution | Rres     | —                 | _                 | 10                | Ω    |

| Keeper Circuit Resistance                | Rkeep    | —                 | 110               | 175               | kΩ   |

| Input current (no pull-up/down)          | lin      | VI = 0, VI = OVDD | -2.5              | 2.5               | μA   |

# Table 25. LPDDR2 I/O DC Electrical Parameters<sup>1</sup> (continued)

<sup>1</sup> Note that the JEDEC LPDDR2 specification (JESD209\_2B) supersedes any specification in this document.

<sup>2</sup> The single-ended signals need to be within the respective limits (Vih(dc) max, Vil(dc) min) for single-ended signals as well as the limitations for overshoot and undershoot.

# 4.6.3.2 DDR3/DDR3L mode I/O DC parameters

The parameters in Table 27 are guaranteed per the operating ranges in Table 11, unless otherwise noted.

| Parameters                               | Symbol   | Test Conditions                               | Min                    | Мах       | Unit |

|------------------------------------------|----------|-----------------------------------------------|------------------------|-----------|------|

| High-level output voltage                | VOH      | loh= -0.1mA<br>Voh (for ipp_dse=001)          | 0.8*OVDD <sup>1</sup>  | _         | V    |

| Low-level output voltage                 | VOL      | lol= 0.1mA<br>Vol (for ipp_dse=001)           | 0.2*OVDD               | —         | V    |

| High-level output voltage                | VOH      | loh= -1mA<br>Voh (for all except ipp_dse=001) | 0.8*OVDD               | —         | V    |

| Low-level output voltage                 | VOL      | Iol= 1mA<br>Vol (for all except ipp_dse=001)  | 0.2*OVDD               | —         | V    |

| Input Reference Voltage                  | Vref     | —                                             | 0.49*ovdd              | 0.51*ovdd | V    |

| DC High-Level input voltage              | Vih_DC   | —                                             | Vref <sup>2</sup> +0.1 | OVDD      | V    |

| DC Low-Level input voltage               | Vil_DC   | —                                             | OVSS                   | Vref-0.1  | V    |

| Differential Input Logic High            | Vih_diff | —                                             | 0.2                    | _         | V    |

| Differential Input Logic Low             | Vil_diff | —                                             | _                      | -0.2      | V    |

| Termination Voltage                      | Vtt      | Vtt tracking OVDD/2                           | 0.49*OVDD              | 0.51*OVDD | V    |

| Pull-up/Pull-down Impedance Mismatch     | Mmpupd   | —                                             | -10                    | 10        | %    |

| 240 $\Omega$ unit calibration resolution | Rres     | —                                             | —                      | 10        | Ω    |

| Keeper Circuit Resistance                | Rkeep    | —                                             | 105                    | 165       | kΩ   |

| Input current (no pull-up/down)          | lin      | VI = 0,VI = OVDD                              | -2.9                   | 2.9       | μA   |

Table 27. DDR3/DDR3L I/O DC Electrical Characteristics

<sup>1</sup> OVDD – I/O power supply (1.425 V–1.575 V for DDR3 and 1.283 V–1.45 V for DDR3L)

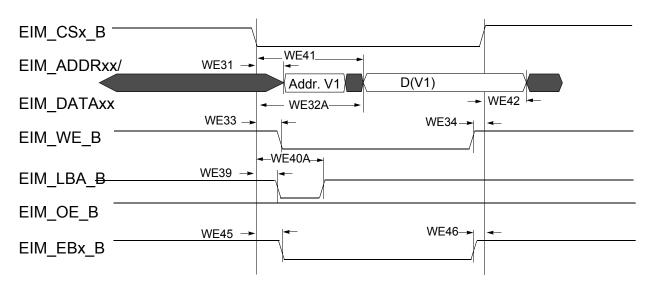

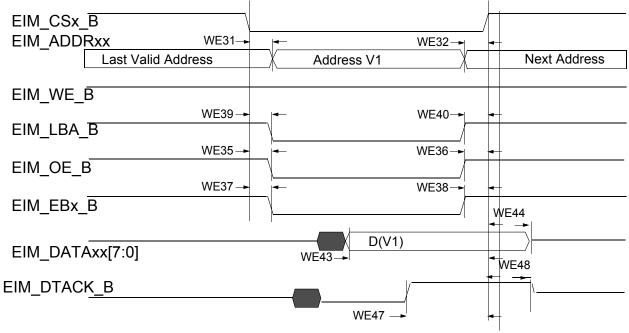

# 4.9.3 External Interface Module (EIM)

The following subsections provide information on the EIM. Maximum operating frequency for EIM data transfer is 104 MHz. Timing parameters in this section that are given as a function of register settings or clock periods are valid for the entire range of allowed frequencies (0–104 MHz).

# 4.9.3.1 EIM interface pads allocation

EIM supports 16-bit and 8-bit devices operating in address/data separate or multiplexed modes. Table 38 provides EIM interface pads allocation in different modes.

| _                                 | Non Multiplexed Address/Data Mode |                       |                       |                       |                       |                       |                       |

|-----------------------------------|-----------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| Setup                             |                                   | 8                     | Bit                   |                       | 16                    | Bit                   | 16 Bit                |

|                                   | MUM = 0,<br>DSZ = 100             | MUM = 0,<br>DSZ = 101 | MUM = 0,<br>DSZ = 110 | MUM = 0,<br>DSZ = 111 | MUM = 0,<br>DSZ = 001 | MUM = 0,<br>DSZ = 010 | MUM = 1,<br>DSZ = 001 |

| EIM_ADDR<br>[15:00]               | EIM_AD<br>[15:00]                 | EIM_AD<br>[15:00]     | EIM_AD<br>[15:00]     | EIM_AD<br>[15:00]     | EIM_AD<br>[15:00]     | EIM_AD<br>[15:00]     | EIM_AD<br>[15:00]     |

| EIM_ADDR<br>[26:16]               | EIM_ADDR<br>[26:16]               | EIM_ADDR<br>[26:16]   | EIM_ADDR<br>[26:16]   | EIM_ADDR<br>[26:16]   | EIM_ADDR<br>[26:16]   | EIM_ADDR<br>[26:16]   | EIM_ADDR<br>[26:16]   |

| EIM_DATA<br>[07:00],<br>EIM_EB0_B | EIM_DATA<br>[07:00]               | _                     | Reserved              | Reserved              | EIM_DATA<br>[07:00]   | Reserved              | EIM_AD<br>[07:00]     |

| EIM_DATA<br>[15:08],<br>EIM_EB1_B | —                                 | EIM_DATA<br>[15:08]   | Reserved              | Reserved              | EIM_DATA<br>[15:08]   | Reserved              | EIM_AD<br>[15:08]     |

<sup>1</sup> For more information on configuration ports mentioned in this table, see the *i.MX* 6UltraLite Reference Manual (IMX6ULRM).

Figure 19. DTACK Mode Read Access (DAP=0)

|                         |                                        |                                     |                                        | r                                      | 1      |

|-------------------------|----------------------------------------|-------------------------------------|----------------------------------------|----------------------------------------|--------|

| LCD_D12 /<br>ENABLE**   | _                                      | R[1]                                | R[0]                                   | G[4]                                   | —      |

| LCD_D11                 | —                                      | R[0]                                | G[5]                                   | G[3]                                   | —      |

| LCD_D10                 | —                                      | G[5]                                | G[4]                                   | G[2]                                   | —      |

| LCD_D9                  | _                                      | G[4]                                | G[3]                                   | G[1]                                   | —      |

| LCD_D8                  | _                                      | G[3]                                | G[2]                                   | G[0]                                   | —      |

| LCD_D8                  | _                                      | G[3]                                | G[2]                                   | G[0]                                   | —      |

| LCD_D7                  | R[2]                                   | G[2]                                | G[1]                                   | B[7]                                   | Y/C[7] |

| LCD_D6                  | R[1]                                   | G[1]                                | G[0]                                   | B[6]                                   | Y/C[6] |

| LCD_D5                  | R[0]                                   | G[0]                                | B[5]                                   | B[5]                                   | Y/C[5] |

| LCD_D4                  | G[2]                                   | B[4]                                | B[4]                                   | B[4]                                   | Y/C[4] |

| LCD_D3                  | G[1]                                   | B[3]                                | B[3]                                   | B[3]                                   | Y/C[3] |

| LCD_D2                  | G[0]                                   | B[2]                                | B[2]                                   | B[2]                                   | Y/C[2] |

| LCD_D1                  | B[1]                                   | B[1]                                | B[1]                                   | B[1]                                   | Y/C[1] |

| LCD_D0                  | B[0]                                   | B[0]                                | B[0]                                   | B[0]                                   | Y/C[0] |

| LCD_RESET               | LCD_RESET                              | LCD_RESET                           | LCD_RESET                              | LCD_RESET                              | —      |

| LCD_BUSY /<br>LCD_VSYNC | LCD_BUSY (or<br>optional<br>LCD_VSYNC) | LCD_BUSY (or<br>optional LCD_VSYNC) | LCD_BUSY (or<br>optional<br>LCD_VSYNC) | LCD_BUSY (or<br>optional<br>LCD_VSYNC) | —      |

Table 61. LCD Signal Parameters (continued)

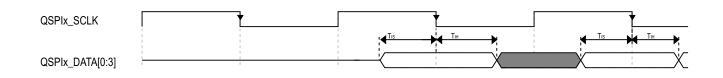

# 4.12.9 QUAD SPI (QSPI) timing parameters

Measurement conditions are with 35 pF load on SCK and SIO pins and input slew rate of 1 V/ns.

# 4.12.9.1 SDR mode

Figure 49. QuadSPI Input/Read Timing (SDR mode with internal sampling)

| Symbol           | Parameter                     | Val | Unit |              |

|------------------|-------------------------------|-----|------|--------------|

| Symbol           | Farameter                     | Min | Мах  | Onit         |

| T <sub>DVO</sub> | Output data valid time        | —   | 2    | ns           |

| T <sub>DHO</sub> | Output data hold time         | 0   | _    | ns           |

| Т <sub>СК</sub>  | SCK clock period              | 10  | —    | ns           |

| T <sub>CSS</sub> | Chip select output setup time | 3   | —    | SCK cycle(s) |

| T <sub>CSH</sub> | Chip select output hold time  | 3   | —    | SCK cycle(s) |

#### Table 64. QuadSPI Output/Write Timing (SDR mode)

## NOTE

T<sub>css</sub> and T<sub>csh</sub> are configured by the QuadSPIx\_FLSHCR register, the default value of 3 are shown on the timing. Please refer to the *i.MX 6UltraLite Reference Manual (IMX6ULRM)* for more details.

## 4.12.9.2 DDR mode

Figure 52. QuadSPI Input/Read Timing (DDR mode with internal sampling)

## Table 65. QuadSPI Input/Read Timing (DDR mode with internal sampling)

| Symbol          | Parameter                               | Val  | Value |      |

|-----------------|-----------------------------------------|------|-------|------|

| Gymbol          | i arameter                              | Min  | Мах   | Unit |

| T <sub>IS</sub> | Setup time for incoming data            | 8.67 | _     | ns   |

| T <sub>IH</sub> | Hold time requirement for incoming data | 0    | _     | ns   |

# <sup>2</sup> DC potential differences

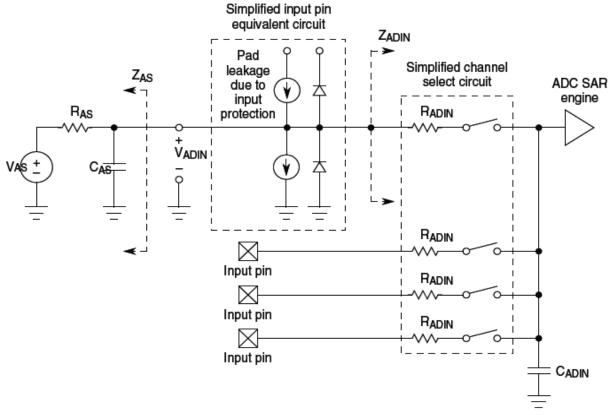

Figure 67. 12-bit ADC Input Impedance Equivalency Diagram

## 4.13.1.1.1 12-bit ADC characteristics

Table 77. 12-bit ADC Characteristics ( $V_{REFH} = V_{DDAD}$ ,  $V_{REFL} = V_{SSAD}$ )

| Characteristic      | Conditions <sup>1</sup>    | Symb               | Min | Typ <sup>2</sup> | Max | Unit | Comment                     |

|---------------------|----------------------------|--------------------|-----|------------------|-----|------|-----------------------------|

| [L:] Supply Current | ADLPC=1,<br>ADHSC=0        | I <sub>DDAD</sub>  | —   | 250              | —   | μA   | ADLSMP=0<br>ADSTS=10 ADCO=1 |

|                     | ADLPC=0,<br>ADHSC=0        |                    |     | 350              |     |      |                             |

|                     | ADLPC=0,<br>ADHSC=1        |                    |     | 400              |     |      |                             |

| [L:] Supply Current | Stop, Reset, Module<br>Off | I <sub>DDAD</sub>  | —   | 0.01             | 0.8 | μA   | —                           |

| ADC Asynchronous    | ADHSC=0                    | f <sub>ADACK</sub> | _   | 10               | _   | MHz  | $t_{ADACK} = 1/f_{ADACK}$   |

| Clock Source        | ADHSC=1                    |                    | _   | 20               | _   |      |                             |

Boot mode configuration

| Ball Name   | Signal Name    | Mux Mode | Common | BOOT_CFG1[3:2]=<br>01b | BOOT_CFG1[3:2]=<br>10b |

|-------------|----------------|----------|--------|------------------------|------------------------|

| NAND_DATA00 | rawnand.DATA00 | Alt 0    | Yes    |                        |                        |

| NAND_DATA01 | rawnand.DATA01 | Alt 0    | Yes    |                        |                        |

| NAND_DATA02 | rawnand.DATA02 | Alt 0    | Yes    |                        |                        |

| NAND_DATA03 | rawnand.DATA03 | Alt 0    | Yes    |                        |                        |

| NAND_DATA04 | rawnand.DATA04 | Alt 0    | Yes    |                        |                        |

| NAND_DATA05 | rawnand.DATA05 | Alt 0    | Yes    |                        |                        |

| NAND_DATA06 | rawnand.DATA06 | Alt 0    | Yes    |                        |                        |

| NAND_DATA07 | rawnand.DATA07 | Alt 0    | Yes    |                        |                        |

| NAND_DQS    | rawnand.DQS    | Alt 0    | Yes    |                        |                        |

| CSI_MCLK    | rawnand.CE2_B  | Alt 2    |        |                        | Yes                    |

| CSI_PIXCLK  | rawnand.CE3_B  | Alt 2    |        |                        | Yes                    |

Table 84. NAND Boot through GPMI (continued)

## Table 85. SD/MMC Boot through USDHC1

| Ball Name    | Signal Name    | Mux<br>Mode | Common | 4-bit | 8-bit | BOOT_CFG1[1]=1<br>(SD Power Cycle) | SDMMC<br>MFG<br>mode |

|--------------|----------------|-------------|--------|-------|-------|------------------------------------|----------------------|

| UART1_RTS_B  | usdhc1.CD_B    | Alt 2       |        |       |       |                                    | Yes                  |

| SD1_CLK      | usdhc1.CLK     | Alt 0       | Yes    |       |       |                                    |                      |

| SD1_CMD      | usdhc1.CMD     | Alt 0       | Yes    |       |       |                                    |                      |

| SD1_DATA0    | usdhc1.DATA0   | Alt 0       | Yes    |       |       |                                    |                      |

| SD1_DATA1    | usdhc1.DATA1   | Alt 0       |        | Yes   | Yes   |                                    |                      |

| SD1_DATA2    | usdhc1.DATA2   | Alt 0       |        | Yes   | Yes   |                                    |                      |

| SD1_DATA3    | usdhc1.DATA3   | Alt 0       | Yes    |       |       |                                    |                      |

| NAND_READY_B | usdhc1.DATA4   | Alt 1       |        |       | Yes   |                                    |                      |

| NAND_CE0_B   | usdhc1.DATA5   | Alt 1       |        |       | Yes   |                                    |                      |

| NAND_CE1_B   | usdhc1.DATA6   | Alt 1       |        |       | Yes   |                                    |                      |

| NAND_CLE     | usdhc1.DATA7   | Alt 1       |        |       | Yes   |                                    |                      |

| GPIO1_IO09   | usdhc1.RESET_B | Alt 5       |        |       |       | Yes                                |                      |

| GPIO1_IO05   | usdhc1.VSELECT | Alt 4       |        |       |       | Yes                                |                      |

This section includes the contact assignment information and mechanical package drawing.

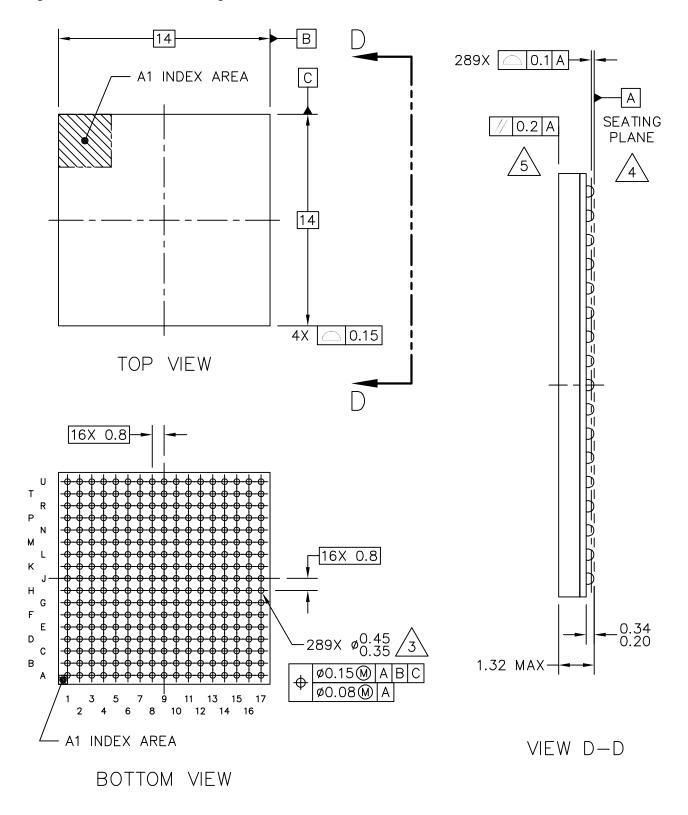

# 6.1 14x14 mm package information

# 6.1.1 14x14 mm, 0.8 mm pitch, ball matrix

Figure 68 shows the top, bottom, and side views of the 14x14 mm BGA package.

|             | Table 91. | 14X14 mm Funcuc | onal Cont | act Assig | gnments (continued) |        |                   |

|-------------|-----------|-----------------|-----------|-----------|---------------------|--------|-------------------|

| DRAM_ADDR07 | H4        | NVCC_DRAM       | DDR       | ALT0      | DRAM_ADDR07         | Output | 100 kΩ<br>pull-up |

| DRAM_ADDR08 | J4        | NVCC_DRAM       | DDR       | ALT0      | DRAM_ADDR08         | Output | 100 kΩ<br>pull-up |

| DRAM_ADDR09 | L2        | NVCC_DRAM       | DDR       | ALT0      | DRAM_ADDR09         | Output | 100 kΩ<br>pull-up |

| DRAM_ADDR10 | M4        | NVCC_DRAM       | DDR       | ALT0      | DRAM_ADDR10         | Output | 100 kΩ<br>pull-up |

| DRAM_ADDR11 | K3        | NVCC_DRAM       | DDR       | ALT0      | DRAM_ADDR11         | Output | 100 kΩ<br>pull-up |

| DRAM_ADDR12 | L4        | NVCC_DRAM       | DDR       | ALT0      | DRAM_ADDR12         | Output | 100 kΩ<br>pull-up |

| DRAM_ADDR13 | H3        | NVCC_DRAM       | DDR       | ALT0      | DRAM_ADDR13         | Output | 100 kΩ<br>pull-up |

| DRAM_ADDR14 | G1        | NVCC_DRAM       | DDR       | ALT0      | DRAM_ADDR14         | Output | 100 kΩ<br>pull-up |

| DRAM_ADDR15 | K5        | NVCC_DRAM       | DDR       | ALT0      | DRAM_ADDR15         | Output | 100 kΩ<br>pull-up |

| DRAM_CAS_B  | J2        | NVCC_DRAM       | DDR       | ALT0      | DRAM_CAS_B          | Output | 100 kΩ<br>pull-up |

| DRAM_CS0_B  | N2        | NVCC_DRAM       | DDR       | ALT0      | DRAM_CS0_B          | Output | 100 kΩ<br>pull-up |

| DRAM_CS1_B  | H5        | NVCC_DRAM       | DDR       | ALT0      | DRAM_CS1_B          | Output | 100 kΩ<br>pull-up |

| DRAM_DATA00 | T4        | NVCC_DRAM       | DDR       | ALT0      | DRAM_DATA00         | Input  | 100 kΩ<br>pull-up |

| DRAM_DATA01 | U6        | NVCC_DRAM       | DDR       | ALT0      | DRAM_DATA01         | Input  | 100 kΩ<br>pull-up |

| DRAM_DATA02 | Т6        | NVCC_DRAM       | DDR       | ALT0      | DRAM_DATA02         | Input  | 100 kΩ<br>pull-up |

| DRAM_DATA03 | U7        | NVCC_DRAM       | DDR       | ALT0      | DRAM_DATA03         | Input  | 100 kΩ<br>pull-up |

| DRAM_DATA04 | U8        | NVCC_DRAM       | DDR       | ALT0      | DRAM_DATA04         | Input  | 100 kΩ<br>pull-up |

| DRAM_DATA05 | T8        | NVCC_DRAM       | DDR       | ALT0      | DRAM_DATA05         | Input  | 100 kΩ<br>pull-up |

| DRAM_DATA06 | T5        | NVCC_DRAM       | DDR       | ALT0      | DRAM_DATA06         | Input  | 100 kΩ<br>pull-up |

| DRAM_DATA07 | U4        | NVCC_DRAM       | DDR       | ALT0      | DRAM_DATA07         | Input  | 100 kΩ<br>pull-up |

| DRAM_DATA08 | U2        | NVCC_DRAM       | DDR       | ALT0      | DRAM_DATA08         | Input  | 100 kΩ<br>pull-up |

Table 91. 14x14 mm Functional Contact Assignments (continued)

| USB_OTG1_CHD_B | U16 | OPEN DRAIN  | GPIO          | _ | USB_OTG1_CHD_B | _ | — |

|----------------|-----|-------------|---------------|---|----------------|---|---|

| USB_OTG1_DN    | T15 | VDD_USB_CAP | ANALOG        |   | USB_OTG1_DN    | — | — |

| USB_OTG1_DP    | U15 | VDD_USB_CAP | ANALOG        | _ | USB_OTG1_DP    | — | — |

| USB_OTG1_VBUS  | T12 | USB_VBUS    | VBUS<br>POWER | Ι | USB_OTG1_VBUS  | _ | — |

| USB_OTG2_DN    | T13 | VDD_USB_CAP | ANALOG        | - | USB_OTG2_DN    | — | — |

| USB_OTG2_DP    | U13 | VDD_USB_CAP | ANALOG        | - | USB_OTG2_DP    | — | — |

| USB_OTG2_VBUS  | U12 | USB_VBUS    | VBUS<br>POWER | Ι | USB_OTG2_VBUS  | — | — |

| XTALI          | T16 | NVCC_PLL    | ANALOG        | _ | XTALI          | _ | _ |

| XTALO          | T17 | NVCC_PLL    | ANALOG        | _ | XTALO          | _ | — |

| Table 91. 14x14 mm Functional Contact Assignments (c | continued) |

|------------------------------------------------------|------------|

|------------------------------------------------------|------------|

<sup>1</sup> SNVS\_TAMPER0 to SNVS\_TAMPER9 can be configured as GPIO or tamper detection pin, it is depending on the fuse setting TAMPER\_PIN\_DISABLE[1:0].

| z             | Σ           |              | ¥             | 7                                                       | т             | υ             |

|---------------|-------------|--------------|---------------|---------------------------------------------------------|---------------|---------------|

| DRAM_ODT0     | DRAM_SDBA0  | DRAM_ADDR05  | DRAM_ADDR02   | DRAM_SDWE_B                                             | DRAM_SDBA1    | DRAM_ADDR14   |

| DRAM_CS0_B    | DRAM_ADDR03 | DRAM_ADDR09  | DRAM_SDBA2    | DRAM_CAS_B                                              | DRAM_ADDR01   | DRAM_ADDR06   |

| VSS           | DRAM_SDCKE0 | VSS          | DRAM_ADDR11   | DRAM_SDCKE1                                             | DRAM_ADDR13   | VSS           |

| DRAM_ZQPAD    | DRAM_ADDR10 | DRAM_ADDR12  | DRAM_ADDR04   | DRAM_ADDR08                                             | DRAM_ADDR07   | DRAM_RESET    |

| VSS           | DRAM_RAS_B  | DRAM_ADDR00  | DRAM_ADDR15   | NSS                                                     | DRAM_CS1_B    | NSS           |

| NVCC_DRAM_2P5 | NVCC_DRAM   | NVCC_DRAM    | NVCC_DRAM     | NVCC_DRAM                                               | NVCC_DRAM     | NVCC_DRAM     |

| TEST_MODE     | VSS         | VSS          | VSS           | NSS                                                     | VSS           | NSS           |

| SNVS_TAMPER5  | VSS         | VDD_SOC_CAP  | VDD_SOC_CAP   | VDD_SOC_CAP                                             | VDD_SOC_CAP   | VDD_SOC_CAP   |

| SNVS_TAMPER8  | VSS         | VDD_SOC_CAP  | VDD_SOC_IN    | VDD_SOC_IN                                              | VDD_SOC_IN    | VDD_ARM_CAP   |

| SNVS_TAMPER7  | VSS         | VDD_SOC_CAP  | VDD_SOC_IN    | VDD_SOC_IN                                              | VDD_SOC_IN    | VDD_ARM_CAP   |

| SNVS_TAMPER6  | VSS         | VDD_SOC_CAP  | VDD_SOC_CAP   | VDD_SOC_CAP                                             | VDD_ARM_CAP   | VDD_ARM_CAP   |

| VDD_SNVS_CAP  | NGND_KEL0   | VSS          | VSS           | NSS                                                     | VSS           | NSS           |

| VDD_HIGH_IN   | ADC_VREFH   | VDDA_ADC_3P3 | GPI01_1000    | NVCC_GPIO                                               | NVCC_UART     | UART5_RX_DATA |

| JTAG_TRST_B   | JTAG_TCK    | GPI01_I002   | UART1_TX_DATA | UART1_RTS_B                                             | UART2_RTS_B   | UART3_RTS_B   |

| JTAG_TDO      | GPI01_1009  | GPI01_1001   | UART1_CTS_B   | UART2_CTS_B                                             | UART3_CTS_B   | NSS           |

| JTAG_TDI      | GPI01_I004  | GPI01_1007   | UART1_RX_DATA | UART1_RX_DATA UART2_RX_DATA UART3_RX_DATA UART4_RX_DATA | UART3_RX_DATA | UART4_RX_DATA |

| GPI01_1008    | GPI01_I005  | GPI01_1003   | GPI01_1006    | UART2_TX_DATA                                           | UART3_TX_DATA | UART4_TX_DATA |

| z             | Σ           | -            | ¥             | 7                                                       | т             | U             |

Table 92. 14x14 mm, 0.8 mm Pitch, Ball Map (continued)

## Package information and contact assignments

## Table 95. 9x9 mm, 0.5 mm Pitch, Ball Map (continued)

|    | Þ                 | F                | ĸ            |

|----|-------------------|------------------|--------------|

| ٢  | VSS               | DRAM_VREF        | DRAM_DM1     |

| 2  | DRAM_DATA09       | DRAM_ZQPAD       | DRAM_DATA11  |

| 3  | DRAM_DATA07       | DRAM_DATA00      | VSS          |

| 4  | DRAM_DQM0         | DRAM_DATA02      | DRAM_DATA06  |

| 5  | DRAM_DATA04       | DRAM_DATA03      | DRAM_SDQS0_N |

| 9  | NSS               | DRAM_DATA05      | ONOFF        |

| 7  | CCM_PMIC_STBY_REQ | SNVS_PMIC_ON_REQ | SNVS_TAMPER6 |

| 8  | BOOT_MODE1        | BOOT_MODE0       | SNVS_TAMPER0 |

| 6  | USB_OTG2_VBUS     | USB_OTG1_VBUS    | VSS          |

| 10 | USB_OTG2_DP       | USB_OTG2_DN      | POR_B        |

| 11 | VDD_HIGH_CAP      | GPANAIO          | USB_OTG1_DN  |

| 12 | RTC_XTALO         | RTC_XTALI        | VSS          |

| 13 | VSS               | NVCC_PLL         | JTAG_MOD     |

| 14 | XTALO             | XTALI            | JTAG_TMS     |

| 15 | VDD_HIGH_IN       | USB_OTG1_CHD_B   | VSS          |

| 16 | CCM_CLK1_N        | CCM_CLK1_P       | JTAG_TDO     |

| 17 | VSS               | VDDA_ADC_3P3     | JTAG_TCK     |

|    | n                 | Т                | R            |

# 6.3 GPIO reset behaviors during reset

Table 96 shows the GPIO behaviors during reset.

# Table 96. GPIO Behaviors during Reset <sup>1</sup>

| Ball Name     | Mux Mode | Function      | Input/Output | Value            |

|---------------|----------|---------------|--------------|------------------|

| GPIO01_IO03   | ALT7     | Reserved      | Input        | 100 kΩ pull-down |

| UART3_TX_DATA | ALT7     | SJC_JTAG_ACT  | Output       | 0                |

| LCD_DATA00    | ALT6     | SRC_BT_CFG[0] | Input        | 100 kΩ pull-down |

| LCD_DATA01    | ALT6     | SRC_BT_CFG[1] | Input        | 100 kΩ pull-down |

| LCD_DATA02    | ALT6     | SRC_BT_CFG[2] | Input        | 100 kΩ pull-down |

| LCD_DATA03    | ALT6     | SRC_BT_CFG[3] | Input        | 100 kΩ pull-down |

| LCD_DATA04    | ALT6     | SRC_BT_CFG[4] | Input        | 100 kΩ pull-down |

| LCD_DATA05    | ALT6     | SRC_BT_CFG[5] | Input        | 100 kΩ pull-down |

| LCD_DATA06    | ALT6     | SRC_BT_CFG[6] | Input        | 100 kΩ pull-down |

| LCD_DATA07    | ALT6     | SRC_BT_CFG[7] | Input        | 100 kΩ pull-down |

| LCD_DATA08    | ALT6     | SRC_BT_CFG[8] | Input        | 100 kΩ pull-down |

| LCD_DATA09    | ALT6     | SRC_BT_CFG[9] | Input        | 100 kΩ pull-down |

## How to Reach Us:

Home Page: nxp.com

Web Support: nxp.com/support Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals" must be validated for each customer application by customer, customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

NXP, the NXP logo, Freescale, the Freescale logo, and the Energy Efficient Solutions logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. ARM, the ARM Powered logo, and Cortex are trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. The USB-IF Logo is a registered trademark of USB Implementers Forum, Inc. All rights reserved. © 2015-2017 NXP B.V.