#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | SPI, UART/USART                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 20                                                                       |

| Program Memory Size        | 2KB (1K x 16)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 6V                                                                |

| Data Converters            | A/D 6x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | 0°C ~ 70°C                                                               |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 28-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at90ls2333-4pc |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

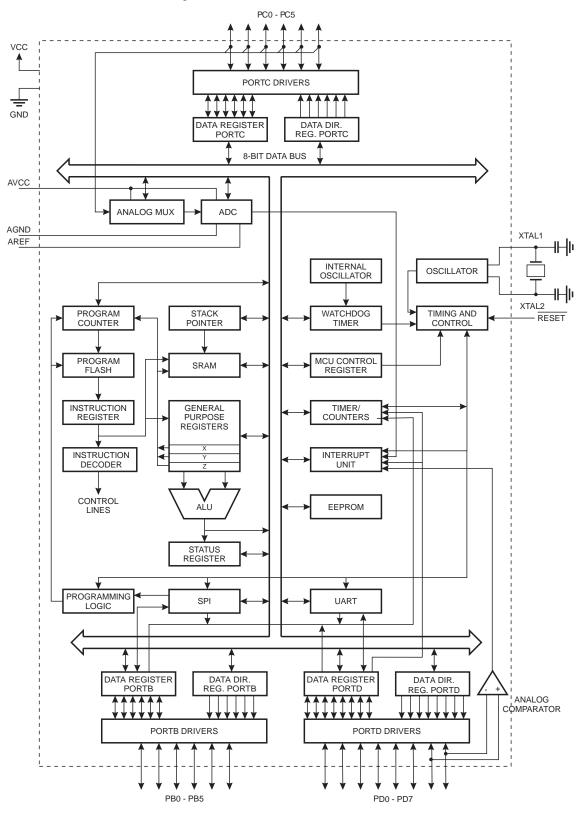

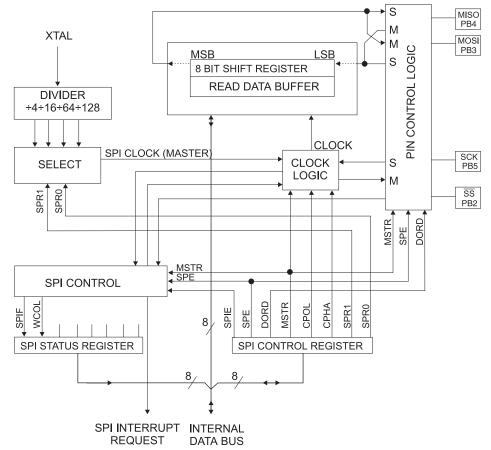

# **Block Diagram**

Figure 1. The AT90S2333/4433 Block Diagram

# **Pin Descriptions**

# vcc

Supply voltage

# GND

Ground

# Port B (PB5..PB0)

Port B is a 6-bit bi-directional I/O port with internal pullup resistors. The Port B output buffers can sink 20 mA. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated.

Port B also serves the functions of various special features of the AT90S2333/4433 as listed on page 60.

The port B pins are tristated when a reset condition becomes active, even if the clock is not running.

# Port C (PC5..PC0)

Port C is a 6-bit bi-directional I/O port with internal pullup resistors. The Port C output buffers can sink 20 mA. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. Port C also serves as the analog inputs to the A/D Converter.

The port C pins are tristated when a reset condition becomes active, even if the clock is not running.

# Port D (PD7..PD0)

Port D is an 8-bit bi-directional I/O port with internal pull-up resistors. The Port D output buffers can sink 20 mA. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated.

Port D also serves the functions of various special features of the AT90S2333/4433 as listed on page 67.

The port D pins are tristated when a reset condition becomes active, even if the clock is not running.

# RESET

Reset input. An external reset is generated by a low level on the RESET pin. Reset pulses longer than 50 ns will generate a reset, even if the clock is not running. Shorter pulses are not guaranteed to generate a reset.

# XTAL1

Input to the inverting oscillator amplifier and input to the internal clock operating circuit.

# XTAL2

Output from the inverting oscillator amplifier

# AVCC

This is the supply voltage pin for the A/D Converter. It should be externally connected to  $V_{CC}$  via a low-pass filter. See page 52 for details on operation of the ADC.

# AREF

This is the analog reference input for the A/D Converter. For ADC operations, a voltage in the range 2.7V to AVCC must be applied to this pin.

# AGND

If the board has a separate analog ground plane, this pin should be connected to this ground plane. Otherwise, connect to GND.

# **Clock Options**

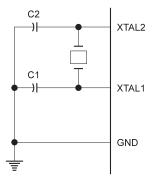

# **Crystal Oscillator**

XTAL1 and XTAL2 are input and output, respectively, of an inverting amplifier which can be configured for use as an onchip oscillator, as shown in Figure 2 and Figure 3. Either a quartz crystal or a ceramic resonator may be used.

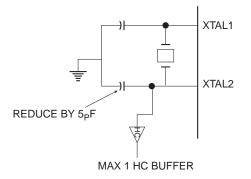

# **External Clock**

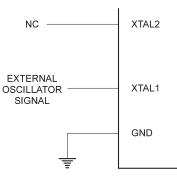

If the oscillator is to be used as a clock for an external device, the clock signal from XTAL2 may be routed to one HC buffer, while reducing the load capacitor by 5 pF, as shown in Figure 3. To drive the device from an external clock source, XTAL2 should be left unconnected while XTAL1 is driven as shown in Figure 4.

# Figure 2. Oscillator Connections

Figure 3. Using MCU Oscillator as a Clock for an External Device

Figure 4. External Clock Drive Configuration

#### Table 5. Reset Delay Selections

| CKSEL [2:0] | Start-Up Time, t <sub>TOUT</sub> at V <sub>CC</sub> = 2.7V | Start-Up Time, t <sub>TOUT</sub> at V <sub>CC</sub> = 5.0V | Recommended Usage                              |  |  |

|-------------|------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------|--|--|

| 000         | 16 ms + 6 CK                                               | External Clock, slowly rising power                        |                                                |  |  |

| 001         | 6 CK                                                       | 6 CK                                                       | External Clock, BOD enabled <sup>(1)</sup>     |  |  |

| 010         | 256 ms + 16K CK                                            | 64 ms + 16K CK                                             | Crystal Oscillator                             |  |  |

| 011         | 16 ms + 16K CK                                             | 4 ms + 16K CK                                              | Crystal Oscillator, fast rising power          |  |  |

| 100         | 16K CK                                                     | 16K CK                                                     | Crystal Oscillator, BOD enabled <sup>(1)</sup> |  |  |

| 101         | 256 ms + 1K CK                                             | 64 ms + 1K CK                                              | Ceramic Resonator                              |  |  |

| 110         | 16 ms + 1K CK                                              | 4 ms + 1K CK                                               | Ceramic Resonator, fast rising power           |  |  |

| 111         | 1K CK                                                      | 1K CK                                                      | Ceramic Resonator, BOD enabled <sup>(1)</sup>  |  |  |

#### Notes: 1. Or external power-on reset.

This table shows the start-up times from reset. From sleep, only the clock counting part of the start-up time is used. The watchdog oscillator is used for timing the real-time part of the start-up time. The number WDT oscillator cycles used for each time-out is shown in Table 6.

#### Table 6. Number of Watchdog Oscillator Cycles

| Time-out                         | Number of cycles |

|----------------------------------|------------------|

| 4.0 ms (at $V_{cc}$ =5.0V)       | 4К               |

| 64 ms (at V <sub>cc</sub> =5.0V) | 64К              |

The frequency of the watchdog oscillator is voltage dependent as shown in the Electrical Characteristics section.

#### **Power-On Reset**

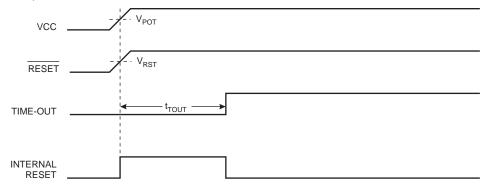

A Power-On Reset (POR) pulse is generated by an on-chip detection circuit. The detection level is nominally 2.2V. The POR is activated whenever  $V_{CC}$  is below the detection level. The POR circuit can be used to trigger the start-up reset, as well as detect a failure in supply voltage.

The Power-On Reset (POR) circuit ensures that the device is reset from power-on. Reaching the power-on reset threshold voltage invokes a delay counter, which determines the delay, for which the device is kept in RESET after  $V_{CC}$  rise. The time-out period of the delay counter is a combination of internal RC oscillator cycles and external oscillator cycles, and it can be defined by the user through the CKSEL fuses. The eight different selections for the delay period are presented in Table 5. The RESET signal is activated again, without any delay, when the  $V_{CC}$  decreases below detection level.

Figure 25. MCU Start-Up, RESET Tied to VCC.

# AT90S/LS2333 and AT90S/LS4433

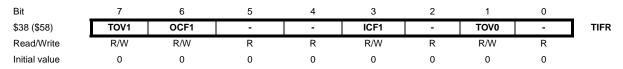

# Timer/Counter Interrupt Flag Register - TIFR

# • Bit 7 - TOV1: Timer/Counter1 Overflow Flag

The TOV1 is set (one) when an overflow occurs in Timer/Counter1. TOV1 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, TOV1 is cleared by writing a logic one to the flag. When the I-bit in SREG, and TOIE1 (Timer/Counter1 Overflow Interrupt Enable), and TOV1 are set (one), the Timer/Counter1 Overflow Interrupt is executed. In PWM mode, this bit is set when Timer/Counter1 advances from \$0000.

#### Bit 6 - OCF1: Output Compare Flag 1

The OCF1 bit is set (one) when compare match occurs between the Timer/Counter1 and the data in OCR1 - Output Compare Register 1. OCF1 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF1 is cleared by writing a logic one to the flag. When the I-bit in SREG, and OCIE1 (Timer/Counter1 Compare match InterruptA Enable), and the OCF1 are set (one), the Timer/Counter1 Compare match Interrupt is executed.

#### • Bit 5, 4 - Res: Reserved Bits

These bits are reserved bits in the AT90S2333/4433 and always read as 0.

#### • Bit 3 - ICF1: Input Capture Flag 1

The ICF1 bit is set (one) to flag an input capture event, indicating that the Timer/Counter1 value has been transferred to the input capture register - ICR1. ICF1 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, ICF1 is cleared by writing a logic one to the flag. When the SREG I-bit, and TICIE1 (Timer/Counter1 Input Capture Interrupt Enable), and ICF1 are set (one), the Timer/Counter1 Capture Interrupt is executed.

#### • Bit 2 - Res: Reserved Bit

This bit is a reserved bit in the AT90S2333/4433 and always reads as 0.

#### • Bit 1 - TOV0: Timer/Counter0 Overflow Flag

The bit TOV0 is set (one) when an overflow occurs in Timer/Counter0. TOV0 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, TOV0 is cleared by writing a logic one to the flag. When the SREG Ibit, and TOIE0 (Timer/Counter0 Overflow Interrupt Enable), and TOV0 are set (one), the Timer/Counter0 Overflow interrupt is executed.

#### • Bit 0 - Res: Reserved bit

This bit is a reserved bit in the AT90S2333/4433 and always reads as zero.

# **External Interrupts**

The external interrupts are triggered by the INT1 and INT0 pins. Observe that, if enabled, the interrupts will trigger even if the INT0/INT1 pins are configured as outputs. This feature provides a way of generating a software interrupt. The external interrupts can be triggered by a falling or rising edge or a low level. This is set up as indicated in the specification for the MCU Control Register - MCUCR. When the external interrupt is enabled and is configured as level triggered, the interrupt will trigger as long as the pin is held low.

The external interrupts are set up as described in the specification for the MCU Control Register - MCUCR.

# Interrupt Response Time

The interrupt execution response for all the enabled AVR interrupts is 4 clock cycles minimum. 4 clock cycles after the interrupt flag has been set, the program vector address for the actual interrupt handling routine is executed. During this 4 clock cycle period, the Program Counter (2 bytes) is pushed onto the Stack, and the Stack Pointer is decremented by 2. The vector is normally a relative jump to the interrupt routine, and this jump takes 2 clock cycles. If an interrupt occurs during execution of a multi-cycle instruction, this instruction is completed before the interrupt is served.

A return from an interrupt handling routine (same as for a subroutine call routine) takes 4 clock cycles. During these 4 clock cycles, the Program Counter (2 bytes) is popped back from the Stack, the Stack Pointer is incremented by 2, and the I flag in SREG is set. When the AVR exits from an interrupt, it will always return to the main program and execute one more instruction before any pending interrupt is served.

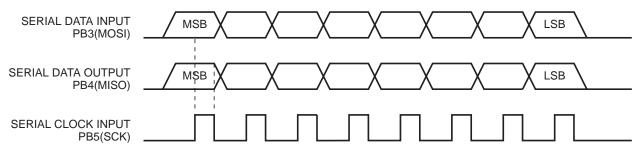

# Serial Peripheral Interface - SPI

The Serial Peripheral Interface (SPI) allows high-speed synchronous data transfer between the AT90S2333/4433 and peripheral devices or between several AVR devices. The AT90S2333/4433 SPI features include the following:

- Full-Duplex, 3-Wire Synchronous Data Transfer

- Master or Slave Operation

- LSB First or MSB First Data Transfer

- Four Programmable Bit Rates

- End of Transmission Interrupt Flag

- Write Collision Flag Protection

- Wake-up from Idle Mode

# Figure 36. SPI Block Diagram

The interconnection between master and slave CPUs with SPI is shown in Figure 37. The PB5(SCK) pin is the clock output in the master mode and is the clock input in the slave mode. Writing to the SPI data register of the master CPU starts the SPI clock generator, and the data written shifts out of the PB3(MOSI) pin and into the PB3(MOSI) pin of the slave CPU. After shifting one byte, the SPI clock generator stops, setting the end of transmission flag (SPIF). If the SPI interrupt enable bit (SPIE) in the SPCR register is set, an interrupt is requested. The Slave Select input, PB2( $\overline{SS}$ ), is set low to select an individual slave SPI device. The two shift registers in the Master and the Slave can be considered as one distributed 16-bit circular shift register. This is shown in Figure 37. When data is shifted from the master to the slave, data is also shifted in the opposite direction, simultaneously. This means that during one shift cycle, data in the master and the slave are interchanged.

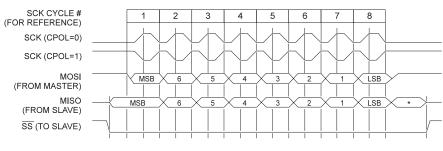

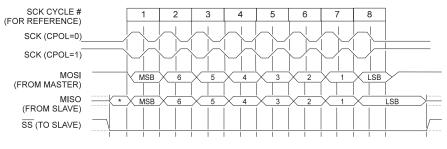

# **Data Modes**

There are four combinations of SCK phase and polarity with respect to serial data, which are determined by control bits CPHA and CPOL. The SPI data transfer formats are shown in Figure 38 and Figure 39.

Figure 38. SPI Transfer Format with CPHA = 0 and DORD = 0

\* Not defined but normally MSB of character just received

# Figure 39. SPI Transfer Format with CPHA = 1 and DORD = 0

\* Not defined but normally LSB of previously transmitted character

# **SPI Control Register - SPCR**

| Bit           | 7    | 6   | 5    | 4    | 3    | 2    | 1    | 0    |      |

|---------------|------|-----|------|------|------|------|------|------|------|

| \$0D (\$2D)   | SPIE | SPE | DORD | MSTR | CPOL | CPHA | SPR1 | SPR0 | SPCR |

| Read/Write    | R/W  | R/W | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | -    |

| Initial value | 0    | 0   | 0    | 0    | 0    | 0    | 0    | 0    |      |

# • Bit 7 - SPIE: SPI Interrupt Enable

This bit causes the SPI interrupt to be executed if SPIF bit in the SPSR register is set and the global interrupts are enabled. • Bit 6 - SPE: SPI Enable

When the SPE bit is set (one), the SPI is enabled. This bit must be set to enable any SPI operations.

# Bit 5 - DORD: Data ORDer

When the DORD bit is set (one), the LSB of the data word is transmitted first.

When the DORD bit is cleared (zero), the MSB of the data word is transmitted first.

# • Bit 4 - MSTR: Master/Slave Select

This bit selects Master SPI mode when set (one), and Slave SPI mode when cleared (zero). If  $\overline{SS}$  is configured as an input and is driven low while MSTR is set, MSTR will be cleared, and SPIF in SPSR will become set. The user will then have to set MSTR to re-enable SPI master mode.

# • Bit 3 - CPOL: Clock POLarity

When this bit is set (one), SCK is high when idle. When CPOL is cleared (zero), SCK is low when idle. Refer to Figure 38 and Figure 39 for additional information.

# • Bit 2 - CPHA: Clock PHAse

Refer to Figure 38 or Figure 39 for the functionality of this bit.

#### • Bits 1,0 - SPR1, SPR0: SPI Clock Rate Select 1 and 0

These two bits control the SCK rate of the device configured as a master. SPR1 and SPR0 have no effect on the slave. The relationship between SCK and the Oscillator Clock frequency  $f_{cl}$  is shown in the following table:

| SPR1 | SPR0 | SCK Frequency         |

|------|------|-----------------------|

| 0    | 0    | f <sub>cl</sub> /4    |

| 0    | 1    | f <sub>cl</sub> / 16  |

| 1    | 0    | f <sub>cl</sub> / 64  |

| 1    | 1    | f <sub>cl</sub> / 128 |

#### Table 18. Relationship Between SCK and the Oscillator Frequency

#### **SPI Status Register - SPSR**

| Bit           | 7    | 6    | 5 | 4 | 3 | 2 | 1 | 0 |      |

|---------------|------|------|---|---|---|---|---|---|------|

| \$0E (\$2E)   | SPIF | WCOL | - | - | - | - | - | - | SPSR |

| Read/Write    | R    | R    | R | R | R | R | R | R | -    |

| Initial value | 0    | 0    | 0 | 0 | 0 | 0 | 0 | 0 |      |

#### • Bit 7 - SPIF: SPI Interrupt Flag

When a serial transfer is complete, the SPIF bit is set (one) and an interrupt is generated if SPIE in SPCR is set (one) and global interrupts are enabled. If <del>SS</del> is an input and is driven low when the SPI is in master mode, this will also set the SPIF flag. SPIF is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, the SPIF bit is cleared by first reading the SPI status register with SPIF set (one), then accessing the SPI Data Register (SPDR).

# Bit 6 - WCOL: Write COLlision flag

The WCOL bit is set if the SPI data register (SPDR) is written during a data transfer. The WCOL bit (and the SPIF bit) are cleared (zero) by first reading the SPI Status Register with WCOL set (one), and then accessing the SPI Data Register. • Bit 5..0 - Res: Reserved bits

These bits are reserved bits in the AT90S2333/4433 and will always read as zero.

The SPI interface on the AT90S2333/4433 is also used for program memory and EEPROM downloading or uploading. See page 78 for serial programming and verification.

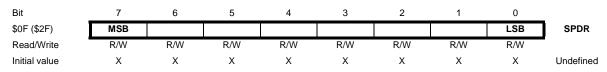

# **SPI Data Register - SPDR**

The SPI Data Register is a read/write register used for data transfer between the register file and the SPI Shift register. Writing to the register initiates data transmission. Reading the register causes the Shift Register Receive buffer to be read.

# **UART Baud Rate Register - UBRR**

| Bit           | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | _      |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|--------|

| \$03 (\$23)   | -   | -   | -   | -   | MSB |     |     | LSB | UBRRHI |

| \$09 (\$29)   | MSB |     |     |     |     |     |     | LSB | UBRR   |

|               | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | -      |

| Read/Write    | R   | R   | R   | R   | R/W | R/W | R/W | R/W |        |

|               | R/W |        |

| Initial value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |        |

|               | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |        |

This is a 12-bit register which contains the UART Baud Rate according to the equation on the previous page. The UBRRHI contains the 4 most significant bits, and the UBRR contains the 8 least significant bits of the UART Baud Rate.

# **Analog Comparator**

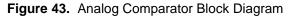

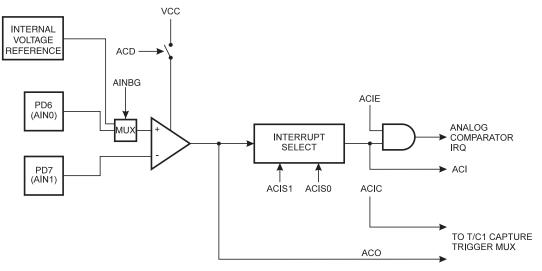

The analog comparator compares the input values on the positive input PD6 (AIN0) and negative input PD7 (AIN1). When the voltage on the positive input PD6 (AIN0) is higher than the voltage on the negative input PD7 (AIN1), the Analog Comparator Output, ACO is set (one). The comparator's output can be set to trigger the Timer/Counter1 Input Capture function. In addition, the comparator can trigger a separate interrupt, exclusive to the Analog Comparator. The user can select Interrupt triggering on comparator output rise, fall or toggle. A block diagram of the comparator and its surrounding logic is shown in Figure 43.

#### Analog Comparator Control And Status Register - ACSR

#### • Bit 7 - ACD: Analog Comparator Disable

50

When this bit is set(one), the power to the analog comparator is switched off. This bit can be set at any time to turn off the analog comparator. When changing the ACD bit, the Analog Comparator Interrupt must be disabled by clearing the ACIE bit in ACSR. Otherwise an interrupt can occur when the bit is changed.

The ADC is enabled by writing a logical one to the ADC Enable bit, ADEN in ADCSR. The first conversion that is started after enabling the ADC, will be preceded by a dummy conversion to initialize the ADC. To the user, the only difference will be that this conversion takes 12 more clock cycles than a normal conversion.

A conversion is started by writing a logical one to the ADC Start Conversion bit, ADSC. This bit will stay high as long as the conversion is in progress and be set to zero by hardware when the conversion is completed. If a different data channel is selected while a conversion is in progress, the ADC will finish the current conversion before performing the channel change.

As the ADC generates a 10-bit result, two data registers, ADCH and ADCL, must be read to get the result when the conversion is complete. Special data protection logic is used to ensure that the contents of the data registers belong to the same result when they are read. This mechanism works as follows:

When reading data, ADCL must be read first. Once ADCL is read, ADC access to data registers is blocked. This means that if ADCL has been read, and a conversion completes before ADCH is read, none of the registers are updated and the result from the conversion is lost. When ADCH is read, ADC access to the ADCH and ADCL registers is re-enabled.

The ADC has its own interrupt, ADIF, which can be triggered when a conversion completes. When ADC access to the data registers is prohibited between reading of ADCH and ADCL, the interrupt will trigger even if the result gets lost.

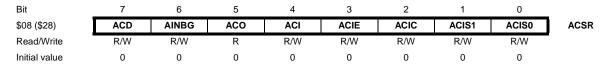

# Prescaling

Figure 45. ADC Prescaler

The ADC contains a prescaler, which divides the system clock to an acceptable ADC clock frequency. The ADC accepts input clock frequencies in the range 50 - 200 kHz. Applying a higher input frequency will result in a poorer accuracy, see "ADC Characteristics" on page 58.

The ADPS0 - ADPS2 bits in ADCSR are used to generate a proper ADC clock input frequency from any XTAL frequency above 100 kHz. The prescaler starts counting from the moment the ADC is switched on by setting the ADEN bit in ADCSR. The prescaler keeps running for as long as the ADEN bit is set, and is continuously reset when ADEN is low.

When initiating a conversion by setting the ADSC bit in ADCSR, the conversion starts at the following rising edge of the ADC clock cycle. The actual sample-and-hold takes place 1.5 ADC clock cycles after the start of the conversion. The result is ready and written to the ADC Result Register after 13 cycles. In single conversion mode, the ADC needs one more clock cycle before a new conversion can be started, see Figure 47. If ADSC is set high in this period, the ADC will start the new conversion immediately. In Free Run Mode, a new conversion will be started immediately after the result is written to the ADC Result Register. Using Free Run Mode and an ADC clock frequency of 200 kHz gives the lowest conversion time, 65 µs, equivalent to 15.4 kSPS. For a summary of conversion times, see Table 21.

# AT90S/LS2333 and AT90S/LS4433

# ADC Data Register - ADCL AND ADCH

| Bit           | 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    | _    |

|---------------|------|------|------|------|------|------|------|------|------|

| \$05 (\$25)   | -    | -    | -    | -    | -    | -    | ADC9 | ADC8 | ADCH |

| \$04 (\$26)   | ADC7 | ADC6 | ADC5 | ADC4 | ADC3 | ADC2 | ADC1 | ADC0 | ADCL |

|               | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    | -    |

| Read/Write    | R    | R    | R    | R    | R    | R    | R    | R    |      |

|               | R    | R    | R    | R    | R    | R    | R    | R    |      |

| Initial value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

|               | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

When an ADC conversion is complete, the result is found in these two registers. In free-run mode, it is essential that both registers are read, and that ADCL is read before ADCH.

# **Scanning Multiple Channels**

Since change of analog channel always is delayed until a conversion is finished, the Free Run Mode can be used to scan multiple channels without interrupting the converter. Typically, the ADC Conversion Complete interrupt will be used to perform the channel shift. However, the user should take the following fact into consideration:

The interrupt triggers once the result is ready to be read. In Free Run Mode, the next conversion will start immediately when the interrupt triggers. If ADMUX is changed after the interrupt triggers, the next conversion has already started, and the old setting is used.

# **ADC Noise Canceling Techniques**

Digital circuitry inside and outside the AT90S2333/4433 generates EMI which might affect the accuracy of analog measurements. If conversion accuracy is critical, the noise level can be reduced by applying the following techniques:

1. The analog part of the AT90S2333/4433 and all analog components in the application should have a separate analog ground plane on the PCB. This ground plane is connected to the digital ground plane via a single point on the PCB.

2. Keep analog signal paths as short as possible. Make sure analog tracks run over the analog ground plane, and keep them well away from high-speed switching digital tracks.

3. The AV<sub>CC</sub> pin on the AT90S2333/4433 should be connected to the digital V<sub>CC</sub> supply voltage via an RC network as shown in Figure 47.

4. Use the ADC noise canceler function to reduce induced noise from the CPU.

5. If some Port C pins are used as digital outputs, it is essential that these do not switch while a conversion is in progress.

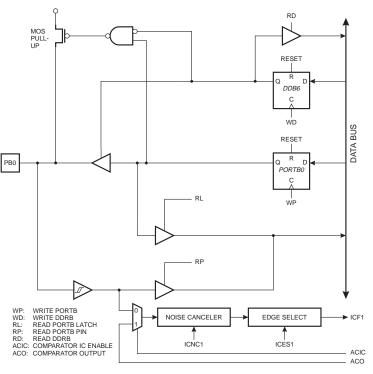

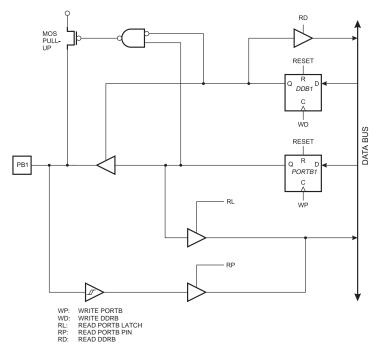

Figure 50. Port B Schematic Diagram (Pin PB0)

Figure 51. Port B Schematic Diagram (Pin PB1)

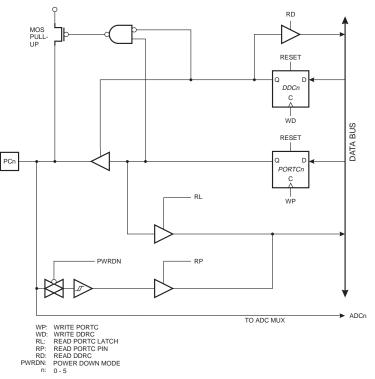

# Port C

Port C is a 6-bit bi-directional I/O port.

Three I/O memory address locations are allocated for the Port C, one each for the Data Register - PORTC, \$15(\$35), Data Direction Register - DDRC, \$14(\$34) and the Port C Input Pins - PINC, \$13(\$33). The Port C Input Pins address is read only, while the Data Register and the Data Direction Register are read/write.

All port pins have individually selectable pull-up resistors. The Port C output buffers can sink 20mA and thus drive LED displays directly. When pins PC0 to PC5 are used as inputs and are externally pulled low, they will source current if the internal pull-up resistors are activated.

Port C has an alternate function as analog inputs for the ADC. If some Port C pins are configured as outputs, it is essential that these do not switch when a conversion is in progress. This might corrupt the result of the conversion.

During Power Down Mode, the schmitt triggers of the digital inputs are disconnected. This allows an analog voltage close to  $V_{CC}/2$  to be present during power down without causing excessive power consumption.

# Port C Data Register - PORTC

| Bit           | 7 | 6 | 5      | 4      | 3      | 2      | 1      | 0      | _     |

|---------------|---|---|--------|--------|--------|--------|--------|--------|-------|

| \$15 (\$35)   | - | - | PORTC5 | PORTC4 | PORTC3 | PORTC2 | PORTC1 | PORTC0 | PORTC |

| Read/Write    | R | R | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |       |

| Initial value | 0 | 0 | 0      | 0      | 0      | 0      | 0      | 0      |       |

# Port C Data Direction Register - DDRC

| Bit           | 7 | 6 | 5    | 4    | 3    | 2    | 1    | 0    |      |

|---------------|---|---|------|------|------|------|------|------|------|

| \$14 (\$34)   | - | - | DDC5 | DDC4 | DDC3 | DDC2 | DDC1 | DDC0 | DDRC |

| Read/Write    | R | R | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | -    |

| Initial value | 0 | 0 | 0    | 0    | 0    | 0    | 0    | 0    |      |

# Port C Input Pins Address - PINC

| Bit           | 7 | 6 | 5     | 4     | 3     | 2     | 1     | 0     |      |

|---------------|---|---|-------|-------|-------|-------|-------|-------|------|

| \$13 (\$33)   | - | - | PINC5 | PINC4 | PINC3 | PINC2 | PINC1 | PINC0 | PINC |

| Read/Write    | R | R | R     | R     | R     | R     | R     | R     | -    |

| Initial value | Q | Q | Hi-Z  | Hi-Z  | Hi-Z  | Hi-Z  | Hi-Z  | Hi-Z  |      |

The Port C Input Pins address - PINC - is not a register, and this address enables access to the physical value on each Port C pin. When reading PORTC, the Port C Data Latch is read, and when reading PINC, the logical values present on the pins are read.

# Port C As General Digital I/O

All 6 pins in Port C have equal functionality when used as digital I/O pins.

PCn, General I/O pin: The DDCn bit in the DDRC register selects the direction of this pin, if DDCn is set (one), PCn is configured as an output pin. If DDCn is cleared (zero), PCn is configured as an input pin. If PORTCn is set (one) when the pin configured as an input pin, the MOS pull up resistor is activated. To switch the pull up resistor off, PORTCn has to be cleared (zero) or the pin has to be configured as an output pin. The port pins are tristated when a reset condition becomes active, even if the clock is not running

| DDCn | PORTCn | I/O    | Pull Up | Comment                                     |  |  |  |  |  |  |  |  |

|------|--------|--------|---------|---------------------------------------------|--|--|--|--|--|--|--|--|

| 0    | 0      | Input  | No      | Tri-state (Hi-Z)                            |  |  |  |  |  |  |  |  |

| 0    | 1      | Input  | Yes     | PCn will source current if ext. pulled low. |  |  |  |  |  |  |  |  |

| 1    | 0      | Output | No      | Push-Pull Zero Output                       |  |  |  |  |  |  |  |  |

| 1    | 1      | Output | No      | Push-Pull One Output                        |  |  |  |  |  |  |  |  |

#### Table 25. DDCn Effects on Port C Pins

Note: n: 5...0, pin number

#### **Port C Schematics**

Note that all port pins are synchronized. The synchronization latch is however, not shown in the figure.

Figure 56. Port C Schematic Diagrams (Pins PC0 - PC5)

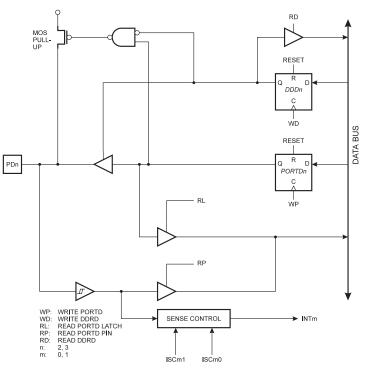

# Port D

Port D is an 8 bit bi-directional I/O port with internal pull-up resistors.

Three I/O memory address locations are allocated for Port D, one each for the Data Register - PORTD, \$12(\$32), Data Direction Register - DDRD, \$11(\$31) and the Port D Input Pins - PIND, \$10(\$30). The Port D Input Pins address is read only, while the Data Register and the Data Direction Register are read/write.

The Port D output buffers can sink 20 mA. As inputs, Port D pins that are externally pulled low will source current if the pullup resistors are activated.

Some Port D pins have alternate functions as shown in the following table:

#### Table 26. Port D Pins Alternate Functions

| Port Pin | Alternate Function                          |

|----------|---------------------------------------------|

| PD0      | RXD (UART Input line)                       |

| PD1      | TXD (UART Output line)                      |

| PD2      | INT0 (External interrupt 0 input)           |

| PD3      | INT1 (External interrupt 1 input)           |

| PD4      | T0 (Timer/Counter 0 external counter input) |

| PD5      | T1 (Timer/Counter 1 external counter input) |

| PD6      | AIN0 (Analog comparator positive input)     |

| PD7      | AIN1 (Analog comparator negative input)     |

# Port D Data Register - PORTD

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      | _     |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|

| \$12 (\$32)   | PORTD7 | PORTD6 | PORTD5 | PORTD4 | PORTD3 | PORTD2 | PORTD1 | PORTD0 | PORTD |

| Read/Write    | R/W    | •     |

| Initial value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

# Port D Data Direction Register - DDRD

| Bit           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |      |

|---------------|------|------|------|------|------|------|------|------|------|

| \$11 (\$31)   | DDD7 | DDD6 | DDD5 | DDD4 | DDD3 | DDD2 | DDD1 | DDD0 | DDRD |

| Read/Write    | R/W  | -    |

| Initial value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

# Port D Input Pins Address - PIND

| Bit           | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |      |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| \$10 (\$30)   | PIND7 | PIND6 | PIND5 | PIND4 | PIND3 | PIND2 | PIND1 | PIND0 | PIND |

| Read/Write    | R     | R     | R     | R     | R     | R     | R     | R     | -    |

| Initial value | Hi-Z  |      |

The Port D Input Pins address - PIND - is not a register, and this address enables access to the physical value on each Port D pin. When reading PORTD, the Port D Data Latch is read, and when reading PIND, the logical values present on the pins are read.

# Port D As General Digital I/O

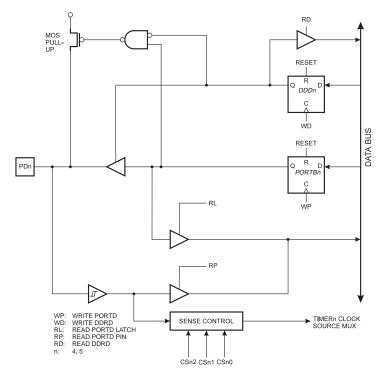

PDn, General I/O pin: The DDDn bit in the DDRD register selects the direction of this pin. If DDDn is set (one), PDn is configured as an output pin. If DDDn is cleared (zero), PDn is configured as an input pin. If PDn is set (one) when configured as an input pin the MOS pull up resistor is activated. To switch the pull up resistor off the PDn has to be cleared (zero) or the pin has to be configured as an output pin. The port pins are tristated when a reset condition becomes active, even if the clock is not running. Figure 59. Port D Schematic Diagram (Pins PD2 and PD3)

Figure 60. Port D Schematic Diagram (Pins PD4 and PD5)

# **Data Polling EEPROM**

When a byte is being programmed into the EEPROM, reading the address location being programmed will give the value P1 until the auto-erase is finished, and then the value P2. See Table 34 for P1 and P2 values.

At the time the device is ready for a new EEPROM byte, the programmed value will read correctly. This is used to determine when the next byte can be written. This will not work for the values P1 and P2, so when programming these values, the user will have to wait for at least the prescribed time  $t_{WD\_PROG}$  before programming the next byte. See Table 38 for  $t_{WD\_PROG}$  value. As a chip-erased device contains \$FF in all locations, programming of addresses that are meant to contain \$FF, can be skipped. This does not apply if the EEPROM is reprogrammed without first chip-erasing the device.

| Table 34. Read Back Value during EEPROM po | olling |

|--------------------------------------------|--------|

|--------------------------------------------|--------|

| Part         | P1   | P2   |

|--------------|------|------|

| AT90S/LS2333 | \$00 | \$FF |

| AT90S/LS4433 | \$00 | \$FF |

#### **Data Polling Flash**

When a byte is being programmed into the Flash, reading the address location being programmed will give the value FF. At the time the device is ready for a new byte, the programmed value will read correctly. This is used to determine when the next byte can be written. This will not work for the value FF, so when programming this value, the user will have to wait for at least  $t_{WD_{PROG}}$  before programming the next byte. As a chip-erased device contains FF in all locations, programming of addresses that are meant to contain FF, can be skipped.

Figure 67. Serial Programming Waveforms

# **DC Characteristics**

| $T_A = -40^{\circ}C$ to $85^{\circ}C$ , $V_{CC} = 2.7V$ to $6.0V$ | (unless otherwise noted) | (Continued) |

|-------------------------------------------------------------------|--------------------------|-------------|

| $T_A = -40$ C to 65 C, $v_{CC} = 2.7$ v to 0.0 v                  | (unless otherwise noted) | (Continueu) |

| Symbol            | Parameter                                 | Condition                            | Min | Тур        | Мах | Units |

|-------------------|-------------------------------------------|--------------------------------------|-----|------------|-----|-------|

| V <sub>ACIO</sub> | Analog Comparator Input<br>Offset Voltage | $V_{CC} = 5V$                        |     |            | 40  | mV    |

| I <sub>ACLK</sub> | Analog Comparator Input<br>Leakage A      | $V_{CC} = 5V$<br>$V_{in} = V_{CC}/2$ | -50 |            | 50  | nA    |

| t <sub>ACPD</sub> | Analog Comparator<br>Propagation Delay    | $V_{CC} = 2.7V$<br>$V_{CC} = 4.0V$   |     | 750<br>500 |     | ns    |

Notes: 1. "Max" means the highest value where the pin is guaranteed to be read as low (logical zero).

2. "Min" means the lowest value where the pin is guaranteed to be read as high (logical one).

3. Although each I/O port can sink more than the test conditions (20mA at Vcc = 5V, 10mA at Vcc = 3V) under steady state conditions (non-transient), the following must be observed:

1] The sum of all IOL, for all ports, should not exceed 300 mA.

2] The sum of all IOL, for port C0-C5, should not exceed 100 mA.

3] The sum of all IOL, for ports B0-B5, D0-D7 and XTAL2, should not exceed 200 mA.

If IOL exceeds the test condition, VOL may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test condition.

4. Although each I/O port can source more than the test conditions (3mA at Vcc = 5V, 1.5mA at Vcc = 3V) under steady state conditions (non-transient), the following must be observed:

1] The sum of all IOL, for all ports, should not exceed 300 mA.

2] The sum of all IOL, for port C0-C5 , should not exceed 100 mA.

3] The sum of all IOL, for ports B0-B5, D0-D7 and XTAL2, should not exceed 200 mA.

If IOH exceeds the test condition, VOH may exceed the related specification. Pins are not guaranteed to source current greater than the listed test condition.

5. Minimum  $V_{CC}$  for Power Down is 2V.

# AT90S/LS2333 and AT90S/LS4433

# **Register Summary**

| Address                    | Name     | Bit 7           | Bit 6           | Bit 5           | Bit 4       | Bit 3  | Bit 2        | Bit 1     | Bit 0  | Page               |

|----------------------------|----------|-----------------|-----------------|-----------------|-------------|--------|--------------|-----------|--------|--------------------|

| \$3F (\$5F)                | SREG     | Ι               | Т               | Н               | S           | V      | N            | Z         | С      | page 17            |

| \$3E (\$5E)                | Reserved | -               | -               | -               | -           | -      | -            | -         | -      | page 17            |

| \$3D (\$5D)                | SP       | SP7             | SP6             | SP5             | SP4         | SP3    | SP2          | SP1       | SP0    | page 17            |

| \$3C (\$5C)                | Reserved |                 | ł               | 4               | •           | 4      | +            |           |        |                    |

| \$3B (\$5B)                | GIMSK    | INT1            | INT0            | -               | -           | -      | -            | -         | -      | page 23            |

| \$3A (\$5A)                | GIFR     | INTF1           | INTF0           |                 |             |        |              |           |        | page 24            |

| \$39 (\$59)                | TIMSK    | TOIE1           | OCIE1           | -               | -           | TICIE1 | -            | TOIE0     | -      | page 24            |

| \$38 (\$58)                | TIFR     | TOV1            | OCF1            | -               | -           | ICF1   | -            | TOV0      | -      | page 25            |

| \$37 (\$57)                | Reserved |                 | 0011            |                 |             | 1011   |              | 1010      |        | page 20            |

| \$36 (\$56)                | Reserved |                 |                 |                 |             |        |              |           |        |                    |

| \$35 (\$55)                | MCUCR    | -               |                 | SE              | SM          | ISC11  | ISC10        | ISC01     | ISC00  | page 26            |

| \$34 (\$54)                | MCUSR    | -               | -               | -               | -           | WDRF   | BORF         | EXTRF     | PORF   | page 20<br>page 22 |

| \$33 (\$53)                | TCCR0    |                 | _               | -               | -           | -      | CS02         | CS01      | CS00   | page 29            |

| \$32 (\$52)                | TCNT0    | -<br>Timor/Cour | nter0 (8 Bits)  | _               | -           | _      | 0002         | 0001      | 0000   | page 23<br>page 30 |

| \$32 (\$52)                |          | Timer/Cour      | itero (o bits)  |                 |             |        |              |           |        | page 30            |

|                            | Reserved |                 |                 |                 |             |        |              |           |        |                    |

| \$30 (\$50)                | Reserved | 00144           | 001440          | 1               | 1           | 1      |              |           | DIMANA |                    |

| \$2F (\$4F)                | TCCR1A   | COM11           | COM10           | -               | -           | -      | -            | PWM11     | PWM10  | page 31            |

| \$2E (\$4E)                | TCCR1B   | ICNC1           | ICES1           | -               | -           | CTC1   | CS12         | CS11      | CS10   | page 32            |

| \$2D (\$4D)                | TCNT1H   |                 |                 | Register High I |             |        |              |           |        | page 33            |

| \$2C (\$4C)                | TCNT1L   |                 |                 | Register Low E  |             |        |              |           |        | page 33            |

| \$2B (\$4B)                | OCR1H    |                 |                 | compare Regist  |             |        |              |           |        | page 34            |

| \$2A (\$4A)                | OCR1L    | Timer/Coun      | ter1 - Output C | compare Regist  | er Low Byte |        |              |           |        | page 34            |

| \$29 (\$49)                | Reserved |                 |                 |                 |             |        |              |           |        |                    |

| \$28 (\$48)                | Reserved |                 |                 |                 |             |        |              |           |        |                    |

| \$27 (\$47)                | ICR1H    | Timer/Coun      | ter1 - Input Ca | pture Register  | High Byte   |        |              |           |        | page 34            |

| \$26 (\$46)                | ICR1L    | Timer/Coun      | ter1 - Input Ca | pture Register  | Low Byte    |        |              |           |        | page 34            |

| \$25 (\$45)                | Reserved |                 |                 |                 |             |        |              |           |        |                    |

| \$24 (\$44)                | Reserved |                 |                 |                 |             |        |              |           |        |                    |

| \$23 (\$43)                | Reserved |                 |                 |                 |             |        |              |           |        |                    |

| \$22 (\$42)                | Reserved |                 |                 |                 |             |        |              |           |        |                    |

| \$21 (\$41)                | WDTCR    | -               | -               | -               | WDTOE       | WDE    | WDP2         | WDP1      | WDP0   | page 36            |

| \$20 (\$40)                | Reserved |                 |                 |                 | MBIOL       | WDL    | TIDI 2       | WBI 1     | WBI 0  | page ee            |

| \$1F (\$3F)                | Reserved |                 |                 |                 |             |        |              |           |        |                    |

| \$1E (\$3E)                | EEAR     | EEDDOM          | Address Regist  | or              |             |        |              |           |        | page 38            |

| \$1D (\$3D)                | EEDR     |                 | Data Register   | ei              |             |        |              |           |        | page 38            |

| \$1C (\$3C)                | EECR     | EEFROMI         |                 |                 |             |        |              |           |        |                    |

|                            |          | -               | -               | -               | -           | EERIE  | EEMWE        | EEWE      | EERE   | page 38            |

| \$1B (\$3B)                | Reserved |                 |                 |                 |             |        |              |           |        |                    |

| \$1A (\$3A)                | Reserved |                 |                 |                 |             |        |              |           |        |                    |

| \$19 (\$39)                | Reserved |                 | 1               |                 |             |        |              |           |        |                    |

| \$18 (\$38)                | PORTB    | -               | -               | PORTB5          | PORTB4      | PORTB3 | PORTB2       | PORTB1    | PORTB0 | page 59            |

| \$17 (\$37)                | DDRB     | -               | -               | DDB5            | DDB4        | DDB3   | DDB2         | DDB1      | DDB0   | page 59            |

| \$16 (\$36)                | PINB     | -               | -               | PINB5           | PINB4       | PINB3  | PINB2        | PINB1     | PINB0  | page 59            |

| \$15 (\$35)                | PORTC    | -               | -               | PORTC5          | PORTC4      | PORTC3 | PORTC2       | PORTC1    | PORTC0 | page 64            |

| \$14 (\$34)                | DDRC     | -               | -               | DDC5            | DDC4        | DDC3   | DDC2         | DDC1      | DDC0   | page 64            |

| \$13 (\$33)                | PINC     | -               | -               | PINC5           | PINC4       | PINC3  | PINC2        | PINC1     | PINC0  | page 64            |

| \$12 (\$32)                | PORTD    | PORTD7          | PORTD6          | PORTD5          | PORTD4      | PORTD3 | PORTD2       | PORTD1    | PORTD0 | page 66            |

| \$11 (\$31)                | DDRD     | DDD7            | DDD6            | DDD5            | DDD4        | DDD3   | DDD2         | DDD1      | DDD0   | page 66            |

| \$10 (\$30)                | PIND     | PIND7           | PIND6           | PIND5           | PIND4       | PIND3  | PIND2        | PIND1     | PIND0  | page 66            |

| \$0F (\$2F)                | SPDR     | SPI Data R      |                 | 1               | u           | 1      |              |           |        | page 43            |

| \$0E (\$2E)                | SPSR     | SPIF            | WCOL            | -               | -           | -      | -            | -         | -      | page 43            |

| \$0D (\$2D)                | SPCR     | SPIE            | SPE             | DORD            | MSTR        | CPOL   | СРНА         | SPR1      | SPR0   | page 42            |

| \$0C (\$2C)                | UDR      |                 | Data Register   | 2010            |             | 0.02   | 0.100        | 0.101     | 00     | page 42<br>page 47 |

| \$0B (\$2B)                | UCSRA    | RXC             | TXC             | UDRE            | FE          | OR     | -            | -         | -      | page 47<br>page 47 |

| \$0B (\$2B)<br>\$0A (\$2A) | UCSRA    | RXCIE           | TXCIE           | UDRIE           | RXEN        | TXEN   | CHR9         | -<br>RXB8 | TXB8   | page 47<br>page 48 |

|                            | UBRR     |                 |                 |                 | INAEIN      | IAEN   | CITKS        | NAD0      | 1700   |                    |

| \$09 (\$29)                |          |                 | d Rate Registe  |                 |             |        |              | 40104     | 40100  | page 50            |

| \$08 (\$28)                | ACSR     | ACD             | AINBG           | ACO             | ACI         | ACIE   | ACIC         | ACIS1     | ACIS0  | page 50            |

| \$07 (\$27)                | ADMUX    | -               | ADCBG           | -               | -           | -      | MUX2         | MUX1      | MUX0   | page 55            |

| \$06 (\$26)                | ADCSR    | ADEN            | ADSC            | ADFR            | ADIF        | ADIE   | ADPS2        | ADPS1     | ADPS0  | page 56            |

| \$05 (\$25)                | ADCH     | -               | -               | -               | -           | -      | -            | ADC9      | ADC8   | page 57            |

| \$04 (\$24)                | ADCL     | ADC7            | ADC6            | ADC5            | ADC4        | ADC3   | ADC2         | ADC1      | ADC0   | page 57            |

| \$03 (\$23)                | UBRRHI   |                 |                 |                 |             |        | UART Baud Ra |           |        | page 50            |

# Instruction Set Summary (Continued)

| Mnemonics      | Operands        | Description                      | Operation                                                                       | Flags        | #Clocks  |

|----------------|-----------------|----------------------------------|---------------------------------------------------------------------------------|--------------|----------|

|                | R INSTRUCTIONS  |                                  |                                                                                 |              |          |

| MOV            | Rd, Rr          | Move Between Registers           | $Rd \leftarrow Rr$                                                              | None         | 1        |

| LDI            | Rd, K           | Load Immediate                   | $Rd \leftarrow K$                                                               | None         | 1        |

| LD             | Rd, X           | Load Indirect                    | $Rd \leftarrow (X)$                                                             | None         | 2        |

| LD             | Rd, X+          | Load Indirect and Post-Inc.      | $Rd \leftarrow (X), X \leftarrow X + 1$                                         | None         | 2        |

| LD             | Rd, - X         | Load Indirect and Pre-Dec.       | $X \leftarrow X - 1, Rd \leftarrow (X)$                                         | None         | 2        |

| LD             | Rd, Y           | Load Indirect                    | $Rd \leftarrow (Y)$                                                             | None         | 2        |

| LD             | Rd, Y+          | Load Indirect and Post-Inc.      | $Rd \leftarrow (Y), Y \leftarrow Y + 1$                                         | None         | 2        |

| LD             | Rd, - Y         | Load Indirect and Pre-Dec.       | $Y \leftarrow Y - 1, Rd \leftarrow (Y)$                                         | None         | 2        |

| LDD            | Rd,Y+q          | Load Indirect with Displacement  | $Rd \leftarrow (Y + q)$                                                         | None         | 2        |

| LD             | Rd, Z           | Load Indirect                    | $Rd \leftarrow (Z)$                                                             | None         | 2        |

| LD             | Rd, Z+          | Load Indirect and Post-Inc.      | $Rd \leftarrow (Z), Z \leftarrow Z+1$                                           | None         | 2        |

| LD             | Rd, -Z          | Load Indirect and Pre-Dec.       | $Z \leftarrow Z - 1, Rd \leftarrow (Z)$                                         | None         | 2        |

| LDD            | Rd, Z+q         | Load Indirect with Displacement  | $Rd \leftarrow (Z + q)$                                                         | None         | 2        |

| LDS            | Rd, k           | Load Direct from SRAM            | $Rd \leftarrow (k)$                                                             | None         | 2        |

| ST             | X, Rr           | Store Indirect                   | $(X) \leftarrow Rr$                                                             | None         | 2        |

| ST             | X+, Rr          | Store Indirect and Post-Inc.     | $(X) \leftarrow \operatorname{Rr}, X \leftarrow X + 1$                          | None         | 2        |

| ST             | - X, Rr         | Store Indirect and Pre-Dec.      | $X \leftarrow X - 1, (X) \leftarrow Rr$                                         | None         | 2        |

| ST             | Y, Rr           | Store Indirect                   | $(Y) \leftarrow Rr$                                                             | None         | 2        |

| ST             | Y+, Rr          | Store Indirect and Post-Inc.     | $(Y) \leftarrow Rr, Y \leftarrow Y + 1$                                         | None         | 2        |

| ST             | - Y, Rr         | Store Indirect and Pre-Dec.      | $Y \leftarrow Y - 1, (Y) \leftarrow Rr$                                         | None         | 2        |

| STD            | Y+q,Rr          | Store Indirect with Displacement | $(Y + q) \leftarrow Rr$                                                         | None         | 2        |

| ST             | Z, Rr           | Store Indirect                   | $(Z) \leftarrow Rr$                                                             | None         | 2        |

| ST             | Z+, Rr          | Store Indirect and Post-Inc.     | $(Z) \leftarrow Rr, Z \leftarrow Z + 1$                                         | None         | 2        |

| ST             | -Z, Rr          | Store Indirect and Pre-Dec.      | $Z \leftarrow Z - 1, (Z) \leftarrow Rr$                                         | None         | 2        |

|                | ,               |                                  |                                                                                 |              |          |

| STD            | Z+q,Rr          | Store Indirect with Displacement | $(Z + q) \leftarrow Rr$                                                         | None         | 2        |

| STS            | k, Rr           | Store Direct to SRAM             | $(k) \leftarrow Rr$                                                             | None         | 2        |

| LPM            |                 | Load Program Memory              | $R0 \leftarrow (Z)$                                                             | None         | 3        |

| IN             | Rd, P           | In Port                          | $Rd \leftarrow P$                                                               | None         | 1        |

| OUT            | P, Rr           | Out Port                         | $P \leftarrow Rr$                                                               | None         | 1        |

| PUSH           | Rr              | Push Register on Stack           | $STACK \leftarrow Rr$                                                           | None         | 2        |

| POP            | Rd              | Pop Register from Stack          | $Rd \gets STACK$                                                                | None         | 2        |

| BIT AND BIT-TE | ST INSTRUCTIONS |                                  |                                                                                 |              |          |

| SBI            | P,b             | Set Bit in I/O Register          | I/O(P,b) ← 1                                                                    | None         | 2        |

| CBI            | P,b             | Clear Bit in I/O Register        | $I/O(P,b) \leftarrow 0$                                                         | None         | 2        |

| LSL            | Rd              | Logical Shift Left               | $Rd(n+1) \leftarrow Rd(n), Rd(0) \leftarrow 0$                                  | Z,C,N,V      | 1        |

| LSR            | Rd              | Logical Shift Right              | $Rd(n) \leftarrow Rd(n+1), Rd(7) \leftarrow 0$                                  | Z,C,N,V      | 1        |

| ROL            | Rd              | Rotate Left Through Carry        | $Rd(0) \leftarrow C, Rd(n+1) \leftarrow Rd(n), C \leftarrow Rd(7)$              | Z,C,N,V      | 1        |

| ROR            | Rd              | Rotate Right Through Carry       | $Rd(7) \leftarrow C, Rd(n) \leftarrow Rd(n+1), C \leftarrow Rd(0)$              | Z,C,N,V      | 1        |

| ASR            | Rd              | Arithmetic Shift Right           | Rd(n) ← Rd(n+1), n=06                                                           | Z,C,N,V      | 1        |

| SWAP           | Rd              | Swap Nibbles                     | Rd(30)←Rd(74),Rd(74)←Rd(30)                                                     | None         | 1        |

| BSET           | s               | Flag Set                         | $\frac{1}{\text{SREG(s)} \leftarrow 1}$                                         | SREG(s)      | 1        |

| BCLR           | S               | Flag Clear                       | $\frac{SREG(S) \leftarrow I}{SREG(S) \leftarrow O}$                             | SREG(s)      | 1        |

| BST            | Rr, b           | Bit Store from Register to T     |                                                                                 | T            | 1        |

| BLD            |                 | Bit load from T to Register      | $T \leftarrow Rr(b)$                                                            |              | 1        |

|                | Rd, b           |                                  | $Rd(b) \leftarrow T$                                                            | None         |          |

| SEC            |                 | Set Carry                        | C ← 1                                                                           | C            | 1        |

| CLC            |                 | Clear Carry                      | C ← 0                                                                           | С            | 1        |

| SEN            |                 | Set Negative Flag                | N ← 1                                                                           | N            | 1        |

| CLN            |                 | Clear Negative Flag              | N ← 0                                                                           | N            | 1        |

| SEZ            |                 | Set Zero Flag                    | Z ← 1                                                                           | Z            | 1        |

| CLZ            |                 | Clear Zero Flag                  | $Z \leftarrow 0$                                                                | Z            | 1        |

| SEI            |                 | Global Interrupt Enable          | l ← 1                                                                           | I            | 1        |

| CLI            |                 | Global Interrupt Disable         | l ← 0                                                                           | 1            | 1        |

| SES            |                 | Set Signed Test Flag             | S ← 1                                                                           | S            | 1        |

| CLS            |                 | Clear Signed Test Flag           | S ← 0                                                                           | S            | 1        |

| SEV            |                 | Set Twos Complement Overflow.    | $V \leftarrow 1$                                                                | V            | 1        |

| CLV            |                 | Clear Twos Complement Overflow   | $V \leftarrow 0$                                                                | V            | 1        |

| SET            |                 | Set T in SREG                    | T ← 1                                                                           | T            | 1        |

| CLT            |                 | Clear T in SREG                  | T ← 0                                                                           | T            | 1        |

| SEH            |                 | Set Half Carry Flag in SREG      | H ← 1                                                                           | H            | 1        |

| CLH            |                 | Clear Half Carry Flag in SREG    | $H \leftarrow 0$                                                                | H            | 1        |

| NOP            |                 | , ,                              |                                                                                 |              |          |

|                | 1               | No Operation                     |                                                                                 | None         | 1        |

|                |                 | Clean                            | (and appealing descention Observation 11)                                       | Manc         | <u>^</u> |

| SLEEP<br>WDR   |                 | Sleep<br>Watchdog Reset          | (see specific descr. for Sleep function)<br>(see specific descr. for WDR/timer) | None<br>None | 3        |