# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | SPI, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 20                                                                      |

| Program Memory Size        | 2KB (1K x 16)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 128 x 8                                                                 |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                 |

| Data Converters            | A/D 6x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | 0°C ~ 70°C                                                              |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 32-TQFP                                                                 |

| Supplier Device Package    | 32-TQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at90s2333-8ac |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

See the next section for a detailed description of the different addressing modes.

#### **Program and Data Addressing Modes**

The AT90S2333/4433 AVR RISC microcontroller supports powerful and efficient addressing modes for access to the Flash program memory, SRAM, Register File, and I/O data memory. This section describes the different addressing modes supported by the AVR architecture. In the figures, OP means the operation code part of the instruction word. To simplify, not all figures show the exact location of the addressing bits.

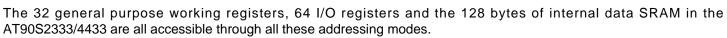

#### **Register Direct, Single Register Rd**

Figure 10. Direct Single Register Addressing

The operand is contained in register d (Rd).

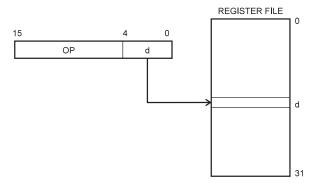

#### Register Direct, Two Registers Rd and Rr

Figure 11. Direct Register Addressing, Two Registers

Operands are contained in register r (Rr) and d (Rd). The result is stored in register d (Rd).

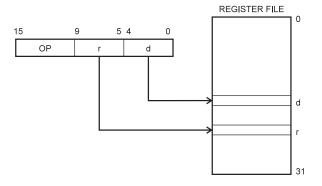

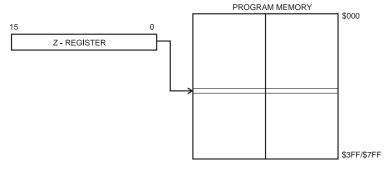

#### **Constant Addressing Using the LPM Instruction**

Figure 18. Code Memory Constant Addressing

Constant byte address is specified by the Z-register contents. The 15 MSBs select word address (0 - 1K/2K), the LSB selects low byte if cleared (LSB = 0) or high byte if set (LSB = 1).

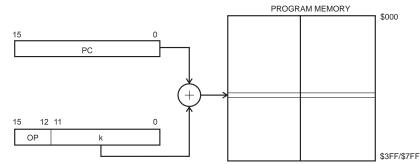

#### Indirect Program Addressing, IJMP and ICALL

Figure 19. Indirect Program Memory Addressing

Program execution continues at address contained by the Z-register (i.e. the PC is loaded with the contents of the Z-register).

#### Relative Program Addressing, RJMP and RCALL

Figure 20. Relative Program Memory Addressing

Program execution continues at address PC + k + 1. The relative address k is from -2048 to 2047.

| Table 2. | AT90S2333/4433 | I/O Space | (Continued) | ) |

|----------|----------------|-----------|-------------|---|

|----------|----------------|-----------|-------------|---|

| I/O Address (SRAM Address) | Name   | Function                                      |

|----------------------------|--------|-----------------------------------------------|

| \$15 (\$35)                | PORTC  | Data Register, Port C                         |

| \$14 (\$34)                | DDRC   | Data Direction Register, Port C               |

| \$13 (\$33)                | PINC   | Input Pins, Port C                            |

| \$12 (\$32)                | PORTD  | Data Register, Port D                         |

| \$11 (\$31)                | DDRD   | Data Direction Register, Port D               |

| \$10 (\$30)                | PIND   | Input Pins, Port D                            |

| \$0F (\$2F)                | SPDR   | SPI I/O Data Register                         |

| \$0E (\$2E)                | SPSR   | SPI Status Register                           |

| \$0D (\$2D)                | SPCR   | SPI Control Register                          |

| \$0C (\$2C)                | UDR    | UART I/O Data Register                        |

| \$0B (\$2B)                | USR    | UART Status Register                          |

| \$0A (\$2A)                | UCR    | UART Control Register                         |

| \$09 (\$29)                | UBRR   | UART Baud Rate Register                       |

| \$08 (\$28)                | ACSR   | Analog Comparator Control and Status Register |

| \$07 (\$27)                | ADMUX  | ADC Multiplexer Select Register               |

| \$06 (\$26)                | ADCSR  | ADC Control and Status Register               |

| \$05 (\$25)                | ADCH   | ADC Data Register High                        |

| \$04 (\$24)                | ADCL   | ADC Data Register Low                         |

| \$03 (\$23)                | UBRRHI | UART Baud Rate Register High                  |

Note: Reserved and unused locations are not shown in the table.

All AT90S2333/4433 I/Os and peripherals are placed in the I/O space. The I/O locations are accessed by the IN and OUT instructions transferring data between the 32 general purpose working registers and the I/O space. I/O registers within the address range \$00 - \$1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the value of single bits can be checked by using the SBIS and SBIC instructions. Refer to the instruction set chapter for more details. When using the I/O specific commands IN, OUT the I/O addresses \$00 - \$3F must be used. When addressing I/O registers as SRAM, \$20 must be added to this address. All I/O register addresses throughout this document are shown with the SRAM address in parentheses.

For compatibility with future devices, reserved bits should be written to zero when accessed. Reserved I/O memory addresses should never be written.

Some of the status flags are cleared by writing a logical one to them. Note that the CBI and SBI instructions will operate on all bits in the I/O register, writing a one back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers \$00 to \$1F only.

The I/O and peripherals control registers are explained in the following sections.

| \$00e | MAIN: | ldi             | r16,low(RAM | END); | Main | program | start |

|-------|-------|-----------------|-------------|-------|------|---------|-------|

| \$00f |       | out             | SP,r16;     |       |      |         |       |

| \$010 |       | <instr></instr> | xxx         | ;     |      |         |       |

|       |       |                 |             |       |      |         |       |

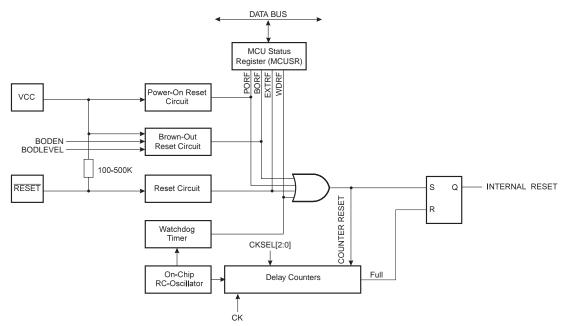

#### **Reset Sources**

The AT90S2333/4433 has four sources of reset:

- Power-On Reset. The MCU is reset when the supply voltage is below the power-on reset threshold (V<sub>POT</sub>).

- External Reset. The MCU is reset when a low level is present on the RESET pin for more than 50 ns.

- Watchdog Reset. The MCU is reset when the Watchdog timer period expires and the Watchdog is enabled.

- Brown-Out Reset. The MCU is reset when the supply voltage V<sub>CC</sub> falls below a certain voltage.

During reset, all I/O registers are then set to their initial values, and the program starts execution from address \$000. The instruction placed in address \$000 must be an RJMP - relative jump - instruction to the reset handling routine. If the program never enables an interrupt source, the interrupt vectors are not used, and regular program code can be placed at these locations. The circuit diagram in Figure 24 shows the reset logic. Table 4 and Table 5 define the timing and electrical parameters of the reset circuitry.

Figure 24. Reset Logic

#### **Table 4.** Reset Characteristics ( $V_{CC} = 5.0V$ )

| Symbol           | Parameter                                 | Min                | Тур                | Мах                | Units |

|------------------|-------------------------------------------|--------------------|--------------------|--------------------|-------|

|                  | Power-On Reset Threshold Voltage, rising  | 1.0                | 1.4                | 1.8                | V     |

| V <sub>POT</sub> | Power-On Reset Threshold Voltage, falling | 0.4                | 0.6                | 0.8                | V     |

| V <sub>RST</sub> | RESET Pin Threshold Voltage               |                    | 0.6V <sub>CC</sub> |                    | V     |

| M                | Brown Out Deast Threshold Valtage         | 2.6 (BODLEVEL = 1) | 2.7 (BODLEVEL = 1) | 2.8 (BODLEVEL = 1) | V     |

| V <sub>BOT</sub> | Brown-Out Reset Threshold Voltage         | 3.8 (BODLEVEL = 0) | 4.0 (BODLEVEL = 0) | 4.2 (BODLEVEL = 0) | V     |

Note: The Power-On Reset will not work unless the supply voltage has been below Vpot (falling).

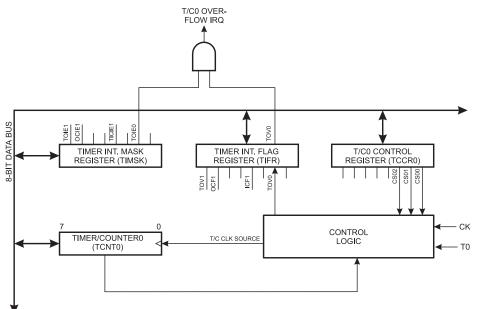

#### Figure 31. Timer/Counter0 Block Diagram

#### Timer/Counter0 Control Register - TCCR0

| Bit           | 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0    |       |

|---------------|---|---|---|---|---|------|------|------|-------|

| \$33 (\$53)   | - | - | - | - | - | CS02 | CS01 | CS00 | TCCR0 |

| Read/Write    | R | R | R | R | R | R/W  | R/W  | R/W  | -     |

| Initial value | 0 | 0 | 0 | 0 | 0 | 0    | 0    | 0    |       |

• Bits 7-3 - Res: Reserved bits

These bits are reserved bits in the AT90S2333/4433 and always read as zero.

#### - Bits 2,1,0 - CS02, CS01, CS00: Clock Select0, bit 2,1 and 0

The Clock Select0 bits 2,1, and 0 define the prescaling source of Timer0.

| CS02 | CS01 | CS00 | Description                      |

|------|------|------|----------------------------------|

| 0    | 0    | 0    | Stop, Timer/Counter0 is stopped. |

| 0    | 0    | 1    | СК                               |

| 0    | 1    | 0    | CK / 8                           |

| 0    | 1    | 1    | СК / 64                          |

| 1    | 0    | 0    | СК / 256                         |

| 1    | 0    | 1    | СК / 1024                        |

| 1    | 1    | 0    | External Pin T0, falling edge    |

| 1    | 1    | 1    | External Pin T0, rising edge     |

#### Table 9. Clock 0 Prescale Select

The Stop condition provides a Timer Enable/Disable function. The prescaled CK modes are scaled directly from the CK oscillator clock. If the external pin modes are used, for Timer/Counter0, transitions on PD4/(T0) will clock the counter even if the pin is configured as an output. This feature can give the user SW control of the counting.

#### • Bits 5..2 - Res: Reserved bits

These bits are reserved bits in the AT90S2333/4433 and always read zero.

#### • Bits 1,0 - PWM11, PWM10: Pulse Width Modulator Select Bits

These bits select PWM operation of Timer/Counter1 as specified in Table 11. This mode is described on page 34.

#### Table 11. PWM Mode Select

| PWM11 | PWM10 | Description                                 |

|-------|-------|---------------------------------------------|

| 0     | 0     | PWM operation of Timer/Counter1 is disabled |

| 0     | 1     | Timer/Counter1 is an 8-bit PWM              |

| 1     | 0     | Timer/Counter1 is a 9-bit PWM               |

| 1     | 1     | Timer/Counter1 is a 10-bit PWM              |

#### Timer/Counter1 Control Register B - TCCR1B

| Bit           | 7     | 6     | 5 | 4 | 3    | 2    | 1    | 0    |        |

|---------------|-------|-------|---|---|------|------|------|------|--------|

| \$2E (\$4E)   | ICNC1 | ICES1 | - | - | CTC1 | CS12 | CS11 | CS10 | TCCR1B |

| Read/Write    | R/W   | R/W   | R | R | R/W  | R/W  | R/W  | R/W  |        |

| Initial value | 0     | 0     | 0 | 0 | 0    | 0    | 0    | 0    |        |

#### • Bit 7 - ICNC1: Input Capture1 Noise Canceler (4 CKs)

When the ICNC1 bit is cleared (zero), the input capture trigger noise canceler function is disabled. The input capture is triggered at the first rising/falling edge sampled on the ICP - input capture pin - as specified. When the ICNC1 bit is set (one), four successive samples are measured on the ICP - input capture pin, and all samples must be high/low according to the input capture trigger specification in the ICES1 bit. The actual sampling frequency is the XTAL clock frequency.

#### Bit 6 - ICES1: Input Capture1 Edge Select

While the ICES1 bit is cleared (zero), the Timer/Counter1 contents are transferred to the Input Capture Register - ICR1 - on the falling edge of the input capture pin - ICP. While the ICES1 bit is set (one), the Timer/Counter1 contents are transferred to the Input Capture Register - ICR1 - on the rising edge of the input capture pin - ICP.

#### • Bits 5, 4 - Res: Reserved bits

These bits are reserved bits in the AT90S2333/4433 and always read zero.

#### • Bit 3 - CTC1: Clear Timer/Counter1 on Compare match

When the CTC1 control bit is set (one), the Timer/Counter1 is reset to \$0000 in the clock cycle after a compare match. If the CTC1 control bit is cleared, Timer/Counter1 continues counting and is unaffected by a compare match. Since the compare match is detected in the CPU clock cycle following the match, this function will behave differently when a prescaling higher than 1 is used for the timer. When a prescaling of 1 is used, and the compare register is set to C, the timer will count as follows if CTC1 is set:

#### ... | C-2 | C-1 | C | 0 | 1 | ...

When the prescaler is set to divide by 8, the timer will count like this:

... | C-2, C-2, C-2, C-2, C-2, C-2, C-2, C-2 | C-1, C-1, C-1, C-1, C-1, C-1, C-1, C-1 | C, 0, 0, 0, 0, 0, 0, 0, 0 | ...

In PWM mode, this bit has no effect.

#### • Bits 2,1,0 - CS12, CS11, CS10: Clock Select1, bit 2,1 and 0

The Clock Select1 bits 2,1 and 0 define the prescaling source of Timer/Counter1.

#### Table 15. PWM Outputs OCR = \$0000 or TOP

| COM11 | COM10 | OCR1   | Output OC1 |

|-------|-------|--------|------------|

| 1     | 0     | \$0000 | L          |

| 1     | 0     | TOP    | н          |

| 1     | 1     | \$0000 | Н          |

| 1     | 1     | TOP    | L          |

In PWM mode, the Timer Overflow Flag1, TOV1, is set when the counter changes direction at \$0000. Timer Overflow Interrupt1 operates exactly as in normal Timer/Counter mode, i.e. it is executed when TOV1 is set provided that Timer Overflow Interrupt1 and global interrupts are enabled. This also applies to the Timer Output Compare1 flag and interrupt.

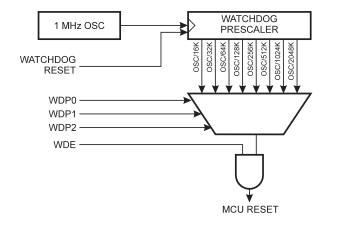

### Watchdog Timer

The Watchdog Timer is clocked from a separate on-chip oscillator. By controlling the Watchdog Timer prescaler, the Watchdog reset interval can be adjusted as shown in Table 6. See characterization data for typical values at other  $V_{CC}$  levels. The WDR - Watchdog Reset - instruction resets the Watchdog Timer. Eight different clock cycle periods can be selected to determine the reset period. If the reset period expires without another Watchdog reset, the AT90S2333/4433 resets and executes from the reset vector. For timing details on the Watchdog reset, refer to page 22.

To prevent unintentional disabling of the watchdog, a special turn-off sequence must be followed when the watchdog is disabled. Refer to the description of the Watchdog Timer Control Register for details.

#### Figure 35. Watchdog Timer

#### Watchdog Timer Control Register - WDTCR

| Bit           | 7 | 6 | 5 | 4     | 3   | 2    | 1    | 0    | _     |

|---------------|---|---|---|-------|-----|------|------|------|-------|

| \$21 (\$41)   | - | - | - | WDTOE | WDE | WDP2 | WDP1 | WDP0 | WDTCR |

| Read/Write    | R | R | R | R/W   | R/W | R/W  | R/W  | R/W  | -     |

| Initial value | 0 | 0 | 0 | 0     | 0   | 0    | 0    | 0    |       |

#### • Bits 7..5 - Res: Reserved bits

36

These bits are reserved bits in the AT90S2333/4433 and will always read as zero.

#### Bit 4 - WDTOE: Watch Dog Turn-Off Enable

This bit must be set (one) when the WDE bit is cleared. Otherwise, the watchdog will not be disabled. Once set, hardware will clear this bit to zero after four clock cycles. Refer to the description of the WDE bit for a watchdog disable procedure.

# AIMEL

## **EEPROM Read/Write Access**

The EEPROM access registers are accessible in the I/O space.

The write access time is in the range of 2.5 - 4ms, depending on the  $V_{CC}$  voltages. A self-timing function lets the user software detect when the next byte can be written. A special EEPROM Ready interrupt can be set to trigger when the EEPROM is ready to accept new data.

An ongoing EEPROM write operation will complete even if a reset condition occurs.

In order to prevent unintentional EEPROM writes, a two state write procedure must be followed. Refer to the description of the EEPROM Control Register for details on this.

When the EEPROM is written, the CPU is halted for two clock cycles before the next instruction is executed.

When the EEPROM is read, the CPU is halted for four clock cycles before the next instruction is executed.

#### **EEPROM Address Register - EEAR**

| Bit           | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |      |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| \$1E (\$3E)   | EEAR7 | EEAR6 | EEAR5 | EEAR4 | EEAR3 | EEAR2 | EEAR1 | EEAR0 | EEAR |

|               |       |       |       |       |       |       |       |       |      |

| Read/Write    | R/W   |      |

| Initial value | х     | Х     | Х     | Х     | Х     | Х     | Х     | Х     |      |

The EEPROM Address Register - EEAR specifies the EEPROM address in the 128/256 bytes EEPROM space. The EEPROM data bytes are addressed linearly between 0 and 127/255. The initial value of EEAR is undefined. A proper value must be written before the EEPROM may be accessed.

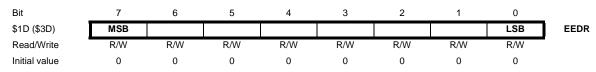

#### **EEPROM Data Register - EEDR**

#### • Bits 7..0 - EEDR7.0: EEPROM Data

For the EEPROM write operation, the EEDR register contains the data to be written to the EEPROM in the address given by the EEAR register. For the EEPROM read operation, the EEDR contains the data read out from the EEPROM at the address given by EEAR.

#### **EEPROM Control Register - EECR**

| Bit           | 7 | 6 | 5 | 4 | 3     | 2     | 1    | 0    |      |

|---------------|---|---|---|---|-------|-------|------|------|------|

| \$1C (\$3C)   | - | - | - | - | EERIE | EEMWE | EEWE | EERE | EECR |

| Read/Write    | R | R | R | R | R/W   | R/W   | R/W  | R/W  | -    |

| Initial value | 0 | 0 | 0 | 0 | 0     | 0     | 0    | 0    |      |

#### • Bit 7..4 - Res: Reserved bits

These bits are reserved bits in the AT90S2333/4433 and will always read as zero.

#### • Bit 3 - EERIE: EEPROM Ready Interrupt Enable

When the I bit in SREG and EERIE are set (one), the EEPROM Ready Interrupt is enabled. When cleared (zero), the interrupt is disabled. The EEPROM Ready interrupt generates a constant interrupt when EEWE is cleared (zero).

#### • Bit 2 - EEMWE: EEPROM Master Write Enable

The EEMWE bit determines whether setting EEWE to one causes the EEPROM to be written. When EEMWE is set(one) setting EEWE will write data to the EEPROM at the selected address If EEMWE is zero, setting EEWE will have no effect. When EEMWE has been set (one) by software, hardware clears the bit to zero after four clock cycles. See the description of the EEWE bit for a EEPROM write procedure.

#### • Bit 6 - AINBG: Analog Comparator Bandgap Select

When this bit is set BOD is enabled and the BODEN is programmed, a fixed bandgap voltage of  $1.22 \pm 0.05$ V replaces the normal input to the positive input (AIN0) of the comparator. When this bit is cleared, the normal input pin PD6 is applied to the positive input of the comparator.

#### • Bit 5 - ACO: Analog Comparator Output

ACO is directly connected to the comparator output.

#### Bit 4 - ACI: Analog Comparator Interrupt Flag

This bit is set (one) when a comparator output event triggers the interrupt mode defined by ACI1 and ACI0. The Analog Comparator Interrupt routine is executed if the ACIE bit is set (one) and the I-bit in SREG is set (one). ACI is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, ACI is cleared by writing a logic one to the flag.

#### • Bit 3 - ACIE: Analog Comparator Interrupt Enable

When the ACIE bit is set (one) and the I-bit in the Status Register is set (one), the analog comparator interrupt is activated. When cleared (zero), the interrupt is disabled.

#### Bit 2 - ACIC: Analog Comparator Input Capture Enable

When set (one), this bit enables the Input Capture function in Timer/Counter1 to be triggered by the analog comparator. The comparator output is in this case directly connected to the Input Capture front-end logic, making the comparator utilize the noise canceler and edge select features of the Timer/Counter1 Input Capture interrupt. When cleared (zero), no connection between the analog comparator and the Input Capture function is given. To make the comparator trigger the Timer/Counter1 Input Capture interrupt, the TICIE1 bit in the Timer Interrupt Mask Register (TIMSK) must be set (one).

#### • Bits 1,0 - ACIS1, ACIS0: Analog Comparator Interrupt Mode Select

These bits determine which comparator events that trigger the Analog Comparator interrupt. The different settings are shown in Table 20.

| ACIS1 | ACIS0 | errupt Mode                                 |  |

|-------|-------|---------------------------------------------|--|

| 0     | 0     | comparator Interrupt on Output Toggle       |  |

| 0     | 1     | eserved                                     |  |

| 1     | 0     | Comparator Interrupt on Falling Output Edge |  |

| 1     | 1     | Comparator Interrupt on Rising Output Edge  |  |

#### Table 20. ACIS1/ACIS0 Settings

Note: When changing the ACIS1/ACIS0 bits, The Analog Comparator Interrupt must be disabled by clearing its Interrupt Enable bit in the ACSR register. Otherwise an interrupt can occur when the bits are changed.

Caution: Using the SBI or CBI intruction on other bits than ACI in this register, will write a one back into ACI if it is read as set, thus clearing the flag.

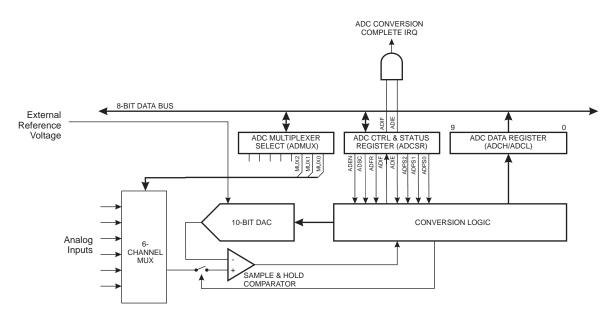

## Analog to Digital Converter

Feature list:

- 10-bit Resolution

- ± 2 LSB Absolute Accuracy

- 0.5 LSB Integral Non-Linearity

- 65 260 µs Conversion Time

- Up to 15 kSPS

- 6 Multiplexed Input Channels

- Rail-to-Rail Input Range

- Free Run or Single Conversion Mode

- Interrupt on ADC conversion complete.

- Sleep Mode Noise Canceler

The AT90S2333/4433 features a 10-bit successive approximation ADC. The ADC is connected to a 6-channel Analog Multiplexer which allows each pin of Port C to be used as an input for the ADC. The ADC contains a Sample and Hold Amplifier which ensures that the input voltage to the ADC is held at a constant level during conversion. A block diagram of the ADC is shown in Figure 44.

The ADC has two separate analog supply voltage pins, AVCC and AGND. AGND must be connected to GND, and the voltage on AVCC must not differ more than  $\pm$  0.3 V from V<sub>CC</sub>. See the paragraph ADC Noise Canceling Techniques on how to connect these pins.

An external reference voltage must be applied to the AREF pin. This voltage must be in the range AGND - AVCC.

#### Figure 44. Analog to Digital Converter Block Schematic

### Operation

The ADC can operate in two modes - Single Conversion and Free Run Mode. In Single Conversion Mode, each conversion will have to be initiated by the user. In Free Run Mode the ADC is constantly sampling and updating the ADC Data Register. The ADFR bit in ADCSR selects between the two available modes.

The ADMUX register selects which one of the six analog input channels to be used as input to the ADC.

# 52 AT90S/LS2333 and AT90S/LS4433

The ADC is enabled by writing a logical one to the ADC Enable bit, ADEN in ADCSR. The first conversion that is started after enabling the ADC, will be preceded by a dummy conversion to initialize the ADC. To the user, the only difference will be that this conversion takes 12 more clock cycles than a normal conversion.

A conversion is started by writing a logical one to the ADC Start Conversion bit, ADSC. This bit will stay high as long as the conversion is in progress and be set to zero by hardware when the conversion is completed. If a different data channel is selected while a conversion is in progress, the ADC will finish the current conversion before performing the channel change.

As the ADC generates a 10-bit result, two data registers, ADCH and ADCL, must be read to get the result when the conversion is complete. Special data protection logic is used to ensure that the contents of the data registers belong to the same result when they are read. This mechanism works as follows:

When reading data, ADCL must be read first. Once ADCL is read, ADC access to data registers is blocked. This means that if ADCL has been read, and a conversion completes before ADCH is read, none of the registers are updated and the result from the conversion is lost. When ADCH is read, ADC access to the ADCH and ADCL registers is re-enabled.

The ADC has its own interrupt, ADIF, which can be triggered when a conversion completes. When ADC access to the data registers is prohibited between reading of ADCH and ADCL, the interrupt will trigger even if the result gets lost.

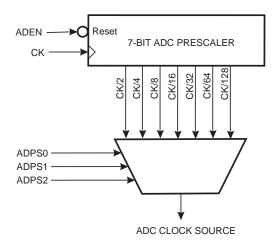

### Prescaling

Figure 45. ADC Prescaler

The ADC contains a prescaler, which divides the system clock to an acceptable ADC clock frequency. The ADC accepts input clock frequencies in the range 50 - 200 kHz. Applying a higher input frequency will result in a poorer accuracy, see "ADC Characteristics" on page 58.

The ADPS0 - ADPS2 bits in ADCSR are used to generate a proper ADC clock input frequency from any XTAL frequency above 100 kHz. The prescaler starts counting from the moment the ADC is switched on by setting the ADEN bit in ADCSR. The prescaler keeps running for as long as the ADEN bit is set, and is continuously reset when ADEN is low.

When initiating a conversion by setting the ADSC bit in ADCSR, the conversion starts at the following rising edge of the ADC clock cycle. The actual sample-and-hold takes place 1.5 ADC clock cycles after the start of the conversion. The result is ready and written to the ADC Result Register after 13 cycles. In single conversion mode, the ADC needs one more clock cycle before a new conversion can be started, see Figure 47. If ADSC is set high in this period, the ADC will start the new conversion immediately. In Free Run Mode, a new conversion will be started immediately after the result is written to the ADC Result Register. Using Free Run Mode and an ADC clock frequency of 200 kHz gives the lowest conversion time, 65 µs, equivalent to 15.4 kSPS. For a summary of conversion times, see Table 21.

#### **ADC Control and Status Register - ADCSR**

| Bit           | 7    | 6    | 5    | 4    | 3    | 2     | 1     | 0     |       |

|---------------|------|------|------|------|------|-------|-------|-------|-------|

| \$06 (\$26)   | ADEN | ADSC | ADFR | ADIF | ADIE | ADPS2 | ADPS1 | ADPS0 | ADCSR |

| Read/Write    | R/W  | R/W  | R/W  | R/W  | R/W  | R/W   | R/W   | R/W   |       |

| Initial value | 0    | 0    | 0    | 0    | 0    | 0     | 0     | 0     |       |

#### • Bit 7 - ADEN: ADC Enable

Writing a logical '1' to this bit enables the ADC. By clearing this bit to zero, the ADC is turned off. Turning the ADC off while a conversion is in progress, will terminate this conversion.

#### • Bit 6 - ADSC: ADC Start Conversion

In Single Conversion Mode, a logical '1' must be written to this bit to start each conversion. In Free Run Mode, a logical '1' must be written to this bit to start the first conversion. The first time ADSC has been written after the ADC has been enabled, or if ADSC is written at the same time as the ADC is enabled, a dummy conversion will precede the initiated conversion. This dummy conversion performs initialization of the ADC.

ADSC remains high during the conversion. ADSC goes low after the conversion is complete, but before the result is written to the ADC Data Registers. This allows a new conversion to be initiated before the current conversion is complete. The new conversion will then start immediately after the current conversion completes. When a dummy conversion precedes a real conversion, ADSC will stay high until the real conversion completes.

Writing a 0 to this bit has no effect.

#### • Bit 5 - ADFR: ADC Free Run Select

When this bit is set (one) the ADC operates in Free Run Mode. In this mode, the ADC samples and updates the data registers continuously. Clearing this bit (zero) will terminate Free Run Mode.

#### • Bit 4 - ADIF: ADC Interrupt Flag

This bit is set (one) when an ADC conversion completes and the data registers are updated. The ADC Conversion Complete Interrupt is executed if the ADIE bit and the I-bit in SREG are set (one). ADIF is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, ADIF is cleared by writing a logical one to the flag. Beware that if doing a read-modify-write on ADCSR, a pending interrupt can be disabled. This also applies if the SBI and CBI instructions are used.

#### • Bit 3 - ADIE: ADC Interrupt Enable

When this bit is set (one) and the I-bit in SREG is set (one), the ADC Conversion Complete Interrupt is activated.

#### • Bits 2..0 - ADPS2..ADPS0: ADC Prescaler Select Bits

These bits determine the division factor between the XTAL frequency and the input clock to the ADC.

| ADPS2 | ADPS1 | ADPS0 | Division Factor |

|-------|-------|-------|-----------------|

| 0     | 0     | 0     | 2               |

| 0     | 0     | 1     | 2               |

| 0     | 1     | 0     | 4               |

| 0     | 1     | 1     | 8               |

| 1     | 0     | 0     | 16              |

| 1     | 0     | 1     | 32              |

| 1     | 1     | 0     | 64              |

| 1     | 1     | 1     | 128             |

#### Table 22. ADC Prescaler Selections

56

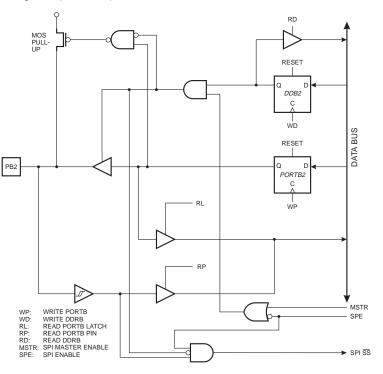

Figure 52. Port B Schematic Diagram (Pin PB2)

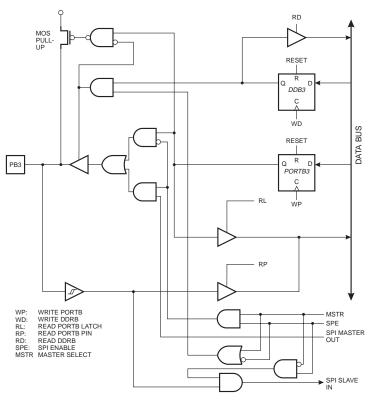

Figure 53. Port B Schematic Diagram (Pin PB3)

### Port C

Port C is a 6-bit bi-directional I/O port.

Three I/O memory address locations are allocated for the Port C, one each for the Data Register - PORTC, \$15(\$35), Data Direction Register - DDRC, \$14(\$34) and the Port C Input Pins - PINC, \$13(\$33). The Port C Input Pins address is read only, while the Data Register and the Data Direction Register are read/write.

All port pins have individually selectable pull-up resistors. The Port C output buffers can sink 20mA and thus drive LED displays directly. When pins PC0 to PC5 are used as inputs and are externally pulled low, they will source current if the internal pull-up resistors are activated.

Port C has an alternate function as analog inputs for the ADC. If some Port C pins are configured as outputs, it is essential that these do not switch when a conversion is in progress. This might corrupt the result of the conversion.

During Power Down Mode, the schmitt triggers of the digital inputs are disconnected. This allows an analog voltage close to  $V_{CC}/2$  to be present during power down without causing excessive power consumption.

#### Port C Data Register - PORTC

| Bit           | 7 | 6 | 5      | 4      | 3      | 2      | 1      | 0      | _     |

|---------------|---|---|--------|--------|--------|--------|--------|--------|-------|

| \$15 (\$35)   | - | - | PORTC5 | PORTC4 | PORTC3 | PORTC2 | PORTC1 | PORTC0 | PORTC |

| Read/Write    | R | R | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |       |

| Initial value | 0 | 0 | 0      | 0      | 0      | 0      | 0      | 0      |       |

#### Port C Data Direction Register - DDRC

| Bit           | 7 | 6 | 5    | 4    | 3    | 2    | 1    | 0    |      |

|---------------|---|---|------|------|------|------|------|------|------|

| \$14 (\$34)   | - | - | DDC5 | DDC4 | DDC3 | DDC2 | DDC1 | DDC0 | DDRC |

| Read/Write    | R | R | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | -    |

| Initial value | 0 | 0 | 0    | 0    | 0    | 0    | 0    | 0    |      |

#### Port C Input Pins Address - PINC

| Bit           | 7 | 6 | 5     | 4     | 3     | 2     | 1     | 0     |      |

|---------------|---|---|-------|-------|-------|-------|-------|-------|------|

| \$13 (\$33)   | - | - | PINC5 | PINC4 | PINC3 | PINC2 | PINC1 | PINC0 | PINC |

| Read/Write    | R | R | R     | R     | R     | R     | R     | R     | -    |

| Initial value | Q | Q | Hi-Z  | Hi-Z  | Hi-Z  | Hi-Z  | Hi-Z  | Hi-Z  |      |

The Port C Input Pins address - PINC - is not a register, and this address enables access to the physical value on each Port C pin. When reading PORTC, the Port C Data Latch is read, and when reading PINC, the logical values present on the pins are read.

#### Port C As General Digital I/O

All 6 pins in Port C have equal functionality when used as digital I/O pins.

PCn, General I/O pin: The DDCn bit in the DDRC register selects the direction of this pin, if DDCn is set (one), PCn is configured as an output pin. If DDCn is cleared (zero), PCn is configured as an input pin. If PORTCn is set (one) when the pin configured as an input pin, the MOS pull up resistor is activated. To switch the pull up resistor off, PORTCn has to be cleared (zero) or the pin has to be configured as an output pin. The port pins are tristated when a reset condition becomes active, even if the clock is not running

# AT90S/LS2333 and AT90S/LS4433

#### Table 30. Pin Name Mapping

| Signal Name in Programming Mode | Pin Name     | I/O | Function                                                          |

|---------------------------------|--------------|-----|-------------------------------------------------------------------|

| RDY/BSY                         | PD1          | 0   | 0: Device is busy programming, 1: Device is ready for new command |

| ŌĒ                              | PD2          | I   | Output Enable (Active low)                                        |

| WR                              | PD3          | I   | Write Pulse (Active low)                                          |

| BS                              | PD4          | Ι   | Byte Select ('0' selects low byte, '1' selects high byte)         |

| XA0                             | PD5          | I   | XTAL Action Bit 0                                                 |

| XA1                             | PD6          | I   | XTAL Action Bit 1                                                 |

| DATA                            | PC1-0, PB5-0 | I/O | Bidirectional Databus (Output when OE is low)                     |

#### Table 31. XA1 and XA0 Coding

| XA1 | XA0 | Action when XTAL1 is Pulsed                                              |

|-----|-----|--------------------------------------------------------------------------|

| 0   | 0   | Load Flash or EEPROM Address (High or low address byte determined by BS) |

| 0   | 1   | Load Data (High or Low data byte for Flash determined by BS)             |

| 1   | 0   | Load Command                                                             |

| 1   | 1   | No Action, Idle                                                          |

#### Table 32. Command Byte Bit Coding

| Command Byte | Command Executed        |

|--------------|-------------------------|

| 1000 0000    | Chip Erase              |

| 0100 0000    | Write Fuse Bits         |

| 0010 0000    | Write Lock Bits         |

| 0001 0000    | Write Flash             |

| 0001 0001    | Write EEPROM            |

| 0000 1000    | Read Signature Bytes    |

| 0000 0100    | Read Fuse and Lock Bits |

| 0000 0010    | Read Flash              |

| 0000 0011    | Read EEPROM             |

#### **Enter Programming Mode**

The following algorithm puts the device in parallel programming mode:

- 1. Apply supply voltage according to Table 29, between  $V_{CC}$  and GND.

- 2. Set the RESET and BS pin to '0' and wait at least 100 ns.

- 3. Apply 11.5 12.5V to RESET. Any activity on BS within 100 ns after +12V has been applied to RESET, will cause the device to fail entering programming mode.

#### **Chip Erase**

The Chip Erase command will erase the Flash and EEPROM memories, and the Lock bits. The Lock bits are not reset until the Flash and EEPROM have been completely erased. The Fuse bits are not changed. Chip Erase must be performed before the Flash or EEPROM is reprogrammed.

Load Command "Chip Erase"

- 1. Set XA1, XA0 to '10'. This enables command loading.

- 2. Set BS to '0'.

- 3. Set DATA to '1000 0000'. This is the command for Chip erase.

- 4. Give XTAL1 a positive pulse. This loads the command.

- 5. Give WR a t<sub>WLWH\_CE</sub> wide negative pulse to execute Chip Erase. See Table 33 for t<sub>WLWH\_CE</sub> value. Chip Erase does not generate any activity on the RDY/BSY pin.

#### **Programming the Flash**

A: Load Command "Write Flash"

- 1. Set XA1, XA0 to '10'. This enables command loading.

- 2. Set BS to '0'

- 3. Set DATA to '0001 0000'. This is the command for Write Flash.

- 4. Give XTAL1 a positive pulse. This loads the command.

- B: Load Address High Byte

- 1. Set XA1, XA0 to '00'. This enables address loading.

- 2. Set BS to '1'. This selects high byte.

- 3. Set DATA = Address high byte (\$00 \$03/\$07)

- 4. Give XTAL1 a positive pulse. This loads the address high byte.

- C: Load Address Low Byte

- 1. Set XA1, XA0 to '00'. This enables address loading.

- 2. Set BS to '0'. This selects low byte.

- 3. Set DATA = Address low byte (\$00 \$FF)

- 4. Give XTAL1 a positive pulse. This loads the address low byte.

- D: Load Data Low Byte

- 1. Set XA1, XA0 to '01'. This enables data loading.

- 2. Set DATA = Data low byte (\$00 \$FF)

- 3. Give XTAL1 a positive pulse. This loads the data low byte.

- E: Write Data Low Byte

- 1. Set BS to '0'. This selects low data.

- 2. Give WR a negative pulse. This starts programming of the data byte. RDY/BSY goes low.

- 3. Wait until RDY/BSY goes high to program the next byte.

- (See Figure 63 for signal waveforms.)

- F: Load Data High Byte

- 1. Set XA1, XA0 to '01'. This enables data loading.

- 2. Set DATA = Data high byte (\$00 \$FF)

- 3. Give XTAL1 a positive pulse. This loads the data high byte.

- G: Write Data High Byte

- 1. Set BS to '1'. This selects high data.

- 2. Give  $\overline{WR}$  a negative pulse. This starts programming of the data byte. RDY/BSY goes low.

- 3. Wait until RDY/BSY goes high to program the next byte.

- (See Figure 64 for signal waveforms.)

The loaded command and address are retained in the device during programming. For efficient programming, the following should be considered.

• The command needs only be loaded once when writing or reading multiple memory locations.

# 74 AT90S/LS2333 and AT90S/LS4433

#### **Data Polling EEPROM**

When a byte is being programmed into the EEPROM, reading the address location being programmed will give the value P1 until the auto-erase is finished, and then the value P2. See Table 34 for P1 and P2 values.

At the time the device is ready for a new EEPROM byte, the programmed value will read correctly. This is used to determine when the next byte can be written. This will not work for the values P1 and P2, so when programming these values, the user will have to wait for at least the prescribed time  $t_{WD\_PROG}$  before programming the next byte. See Table 38 for  $t_{WD\_PROG}$  value. As a chip-erased device contains \$FF in all locations, programming of addresses that are meant to contain \$FF, can be skipped. This does not apply if the EEPROM is reprogrammed without first chip-erasing the device.

| Table 34. Read Back Value during EEPROM po | olling |

|--------------------------------------------|--------|

|--------------------------------------------|--------|

| Part         | P1   | P2   |

|--------------|------|------|

| AT90S/LS2333 | \$00 | \$FF |

| AT90S/LS4433 | \$00 | \$FF |

#### **Data Polling Flash**

When a byte is being programmed into the Flash, reading the address location being programmed will give the value FF. At the time the device is ready for a new byte, the programmed value will read correctly. This is used to determine when the next byte can be written. This will not work for the value FF, so when programming this value, the user will have to wait for at least  $t_{WD_{PROG}}$  before programming the next byte. As a chip-erased device contains FF in all locations, programming of addresses that are meant to contain FF, can be skipped.

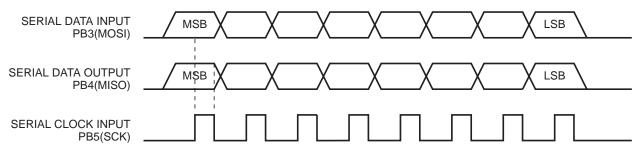

Figure 67. Serial Programming Waveforms

# **Electrical Characteristics**

### Absolute Maximum Ratings\*

| Operating Temperature55°C to +125°C                                                                                  |

|----------------------------------------------------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                                                                    |

| Voltage on any Pin except $\overline{\text{RESET}}$ with respect to Ground1.0V to $V_{\text{CC}}\text{+}0.5\text{V}$ |

| Voltage on $\overline{\text{RESET}}$ with respect to Ground1.0V to +13.0V                                            |

| Maximum Operating Voltage 6.6V                                                                                       |

| DC Current per I/O Pin 40.0 mA                                                                                       |

| DC Current $V_{CC}$ and GND Pins                                                                                     |

\*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **DC Characteristics**

$T_A = -40^{\circ}C$  to  $85^{\circ}C$ ,  $V_{CC} = 2.7V$  to 6.0V (unless otherwise noted)

| Symbol           | Parameter                                             | Condition                                                                                        | Min                                 | Тур | Max                               | Units  |

|------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------|-----|-----------------------------------|--------|

| V <sub>IL</sub>  | Input Low Voltage                                     | Except (XTAL, RESET)                                                                             | -0.5                                |     | 0.3V <sub>CC</sub> <sup>(1)</sup> | V      |

| V <sub>IL1</sub> | Input Low Voltage                                     | XTAL                                                                                             | -0.5                                |     | 0.1 <sup>(1)</sup>                | V      |

| V <sub>IL1</sub> | Input Low Voltage                                     | RESET                                                                                            | -0.5                                |     | 0.2V <sub>CC</sub> <sup>(1)</sup> | V      |

| V <sub>IH</sub>  | Input High Voltage                                    | Except (XTAL, RESET)                                                                             | 0.7 V <sub>CC</sub> <sup>(2)</sup>  |     | V <sub>CC</sub> + 0.5             | V      |

| V <sub>IH1</sub> | Input High Voltage                                    | XTAL                                                                                             | 0.7 V <sub>CC</sub> <sup>(2)</sup>  |     | V <sub>CC</sub> + 0.5             | V      |

| V <sub>IH2</sub> | Input High Voltage                                    | RESET                                                                                            | 0.85 V <sub>CC</sub> <sup>(2)</sup> |     | V <sub>CC</sub> +0.5              | V      |

| V <sub>OL</sub>  | Output Low Voltage <sup>(3)</sup><br>(Ports B, C, D)  | $I_{OL} = 20 \text{ mA}, V_{CC} = 5V$<br>$I_{OL} = 10 \text{ mA}, V_{CC} = 3V$                   |                                     |     | 0.6<br>0.5                        | V<br>V |

| V <sub>OH</sub>  | Output High Voltage <sup>(4)</sup><br>(Ports B, C, D) | I <sub>OH</sub> = -3 mA, V <sub>CC</sub> = 5V<br>I <sub>OH</sub> = -1.5 mA, V <sub>CC</sub> = 3V | 4.3<br>2.2                          |     |                                   | V<br>V |

| IIL              | Input Leakage<br>Current I/O pin                      | V <sub>CC</sub> = 6V, pin = low<br>(Absolute value)                                              |                                     |     | 8.0                               | ua     |

| I <sub>IH</sub>  | Input Leakage<br>Current I/O pin                      | V <sub>CC</sub> = 6V, pin = high<br>(Absolute value)                                             |                                     |     | 8.0                               | ua     |

| RRST             | Reset Pull-Up                                         |                                                                                                  | 100                                 |     | 500                               | kΩ     |

| R <sub>I/O</sub> | I/O Pin Pull-Up Resistor                              |                                                                                                  | 35                                  |     | 120                               | kΩ     |

| I <sub>CC</sub>  | Power Supply Current                                  | Active 4MHz, V <sub>CC</sub> = 3V                                                                |                                     |     | 5.0                               | mA     |

|                  |                                                       | Idle 4MHz, V <sub>CC</sub> = 3V                                                                  |                                     |     | 2.0                               | mA     |

|                  |                                                       | Power Down, $V_{CC} = 3V$<br>WDT enabled <sup>(5)</sup>                                          |                                     |     | 20.0                              | μΑ     |

|                  |                                                       | Power Down, $V_{CC} = 3V$<br>WDT disbled <sup>(5)</sup>                                          |                                     |     | 10                                | μΑ     |

# Instruction Set Summary (Continued)

| Mnemonics           | Operands        | Description                      | Operation                                                                       | Flags        | #Clocks |

|---------------------|-----------------|----------------------------------|---------------------------------------------------------------------------------|--------------|---------|

|                     | R INSTRUCTIONS  |                                  |                                                                                 |              |         |

| MOV                 | Rd, Rr          | Move Between Registers           | $Rd \leftarrow Rr$                                                              | None         | 1       |

| LDI                 | Rd, K           | Load Immediate                   | $Rd \leftarrow K$                                                               | None         | 1       |

| LD                  | Rd, X           | Load Indirect                    | $Rd \leftarrow (X)$                                                             | None         | 2       |

| LD                  | Rd, X+          | Load Indirect and Post-Inc.      | $Rd \leftarrow (X), X \leftarrow X + 1$                                         | None         | 2       |

| LD                  | Rd, - X         | Load Indirect and Pre-Dec.       | $X \leftarrow X - 1, Rd \leftarrow (X)$                                         | None         | 2       |

| LD                  | Rd, Y           | Load Indirect                    | $Rd \leftarrow (Y)$                                                             | None         | 2       |

| LD                  | Rd, Y+          | Load Indirect and Post-Inc.      | $Rd \leftarrow (Y), Y \leftarrow Y + 1$                                         | None         | 2       |

| LD                  | Rd, - Y         | Load Indirect and Pre-Dec.       | $Y \leftarrow Y - 1, Rd \leftarrow (Y)$                                         | None         | 2       |

| LDD                 | Rd,Y+q          | Load Indirect with Displacement  | $Rd \leftarrow (Y + q)$                                                         | None         | 2       |

| LD                  | Rd, Z           | Load Indirect                    | $Rd \leftarrow (Z)$                                                             | None         | 2       |

| LD                  | Rd, Z+          | Load Indirect and Post-Inc.      | $Rd \leftarrow (Z), Z \leftarrow Z+1$                                           | None         | 2       |

| LD                  | Rd, -Z          | Load Indirect and Pre-Dec.       | $Z \leftarrow Z - 1, Rd \leftarrow (Z)$                                         | None         | 2       |

| LDD                 | Rd, Z+q         | Load Indirect with Displacement  | $Rd \leftarrow (Z + q)$                                                         | None         | 2       |

| LDS                 | Rd, k           | Load Direct from SRAM            | $Rd \leftarrow (k)$                                                             | None         | 2       |

| ST                  | X, Rr           | Store Indirect                   | $(X) \leftarrow Rr$                                                             | None         | 2       |

| ST                  | X+, Rr          | Store Indirect and Post-Inc.     | $(X) \leftarrow Rr, X \leftarrow X + 1$                                         | None         | 2       |

| ST                  | - X, Rr         | Store Indirect and Pre-Dec.      | $X \leftarrow X - 1, (X) \leftarrow Rr$                                         | None         | 2       |

| ST                  | Y, Rr           | Store Indirect                   | $(Y) \leftarrow Rr$                                                             | None         | 2       |

| ST                  | Y+, Rr          | Store Indirect and Post-Inc.     | $(Y) \leftarrow Rr, Y \leftarrow Y + 1$                                         | None         | 2       |

| ST                  | - Y, Rr         | Store Indirect and Pre-Dec.      | $Y \leftarrow Y - 1, (Y) \leftarrow Rr$                                         | None         | 2       |

| STD                 | Y+q,Rr          | Store Indirect with Displacement | $(Y + q) \leftarrow Rr$                                                         | None         | 2       |

| ST                  | Z, Rr           | Store Indirect                   | $(Z) \leftarrow Rr$                                                             | None         | 2       |

| ST                  | Z+, Rr          | Store Indirect and Post-Inc.     | $(Z) \leftarrow Rr, Z \leftarrow Z + 1$                                         | None         | 2       |

| ST                  | -Z, Rr          | Store Indirect and Pre-Dec.      | $Z \leftarrow Z - 1, (Z) \leftarrow Rr$                                         | None         | 2       |

|                     | ,               |                                  |                                                                                 |              |         |

| STD                 | Z+q,Rr          | Store Indirect with Displacement | $(Z + q) \leftarrow Rr$                                                         | None         | 2       |

| STS                 | k, Rr           | Store Direct to SRAM             | $(k) \leftarrow Rr$                                                             | None         | 2       |

| LPM                 |                 | Load Program Memory              | $R0 \leftarrow (Z)$                                                             | None         | 3       |

| IN                  | Rd, P           | In Port                          | $Rd \leftarrow P$                                                               | None         | 1       |

| OUT                 | P, Rr           | Out Port                         | $P \leftarrow Rr$                                                               | None         | 1       |

| PUSH                | Rr              | Push Register on Stack           | $STACK \leftarrow Rr$                                                           | None         | 2       |

| POP                 | Rd              | Pop Register from Stack          | $Rd \gets STACK$                                                                | None         | 2       |

| BIT AND BIT-TE      | ST INSTRUCTIONS |                                  |                                                                                 |              |         |

| SBI                 | P,b             | Set Bit in I/O Register          | I/O(P,b) ← 1                                                                    | None         | 2       |

| CBI                 | P,b             | Clear Bit in I/O Register        | $I/O(P,b) \leftarrow 0$                                                         | None         | 2       |

| LSL                 | Rd              | Logical Shift Left               | $Rd(n+1) \leftarrow Rd(n), Rd(0) \leftarrow 0$                                  | Z,C,N,V      | 1       |

| LSR                 | Rd              | Logical Shift Right              | $Rd(n) \leftarrow Rd(n+1), Rd(7) \leftarrow 0$                                  | Z,C,N,V      | 1       |

| ROL                 | Rd              | Rotate Left Through Carry        | $Rd(0) \leftarrow C, Rd(n+1) \leftarrow Rd(n), C \leftarrow Rd(7)$              | Z,C,N,V      | 1       |

| ROR                 | Rd              | Rotate Right Through Carry       | $Rd(7)\leftarrow C,Rd(n)\leftarrow Rd(n+1),C\leftarrow Rd(0)$                   | Z,C,N,V      | 1       |

| ASR                 | Rd              | Arithmetic Shift Right           | Rd(n) ← Rd(n+1), n=06                                                           | Z,C,N,V      | 1       |

| SWAP                | Rd              | Swap Nibbles                     | Rd(30)←Rd(74),Rd(74)←Rd(30)                                                     | None         | 1       |

| BSET                | s               | Flag Set                         | $\frac{1}{\text{SREG(s)} \leftarrow 1}$                                         | SREG(s)      | 1       |

| BCLR                | s               | Flag Clear                       | $\frac{SREG(s)}{SREG(s)} \leftarrow 0$                                          | SREG(s)      | 1       |

| BST                 | Rr, b           | Bit Store from Register to T     | $T \leftarrow Rr(b)$                                                            | T            | 1       |

| BLD                 | Rd, b           | Bit load from T to Register      | $Rd(b) \leftarrow T$                                                            | None         | 1       |

|                     | KU, D           |                                  |                                                                                 |              |         |

| SEC                 |                 | Set Carry                        | C ← 1                                                                           | C            | 1       |

| CLC                 |                 | Clear Carry                      | $C \leftarrow 0$                                                                | С            | 1       |

| SEN                 |                 | Set Negative Flag                | N ← 1                                                                           | N            | 1       |

| CLN                 |                 | Clear Negative Flag              | N ← 0                                                                           | N            | 1       |

| SEZ                 |                 | Set Zero Flag                    | Z ← 1                                                                           | Z            | 1       |

| CLZ                 |                 | Clear Zero Flag                  | Z ← 0                                                                           | Z            | 1       |

| SEI                 |                 | Global Interrupt Enable          | l ← 1                                                                           | I            | 1       |

| CLI                 |                 | Global Interrupt Disable         | l ← 0                                                                           | 1            | 1       |

| SES                 |                 | Set Signed Test Flag             | S ← 1                                                                           | S            | 1       |

| CLS                 |                 | Clear Signed Test Flag           | S ← 0                                                                           | S            | 1       |

| SEV                 |                 | Set Twos Complement Overflow.    | V ← 1                                                                           | V            | 1       |

| CLV                 |                 | Clear Twos Complement Overflow   | $V \leftarrow 0$                                                                | V            | 1       |

| SET                 |                 | Set T in SREG                    | T ← 1                                                                           | T            | 1       |

| CLT                 |                 | Clear T in SREG                  | T ← 0                                                                           | T            | 1       |

| SEH                 |                 | Set Half Carry Flag in SREG      | H ← 1                                                                           | H            | 1       |

| CLH                 |                 | Clear Half Carry Flag in SREG    | $H \leftarrow 0$                                                                | H            | 1       |

|                     |                 |                                  |                                                                                 |              |         |

|                     | 1               | No Operation                     |                                                                                 | None         | 1       |

|                     |                 | Class                            |                                                                                 | Nanc         | 0       |

| NOP<br>SLEEP<br>WDR |                 | Sleep<br>Watchdog Reset          | (see specific descr. for Sleep function)<br>(see specific descr. for WDR/timer) | None<br>None | 3       |

# AT90S/LS2333 and AT90S/LS4433

# **Ordering Information**

| Power Supply | Speed (MHz) | Ordering Code                    | Package     | Operation Range               |

|--------------|-------------|----------------------------------|-------------|-------------------------------|

| 2.7 - 6.0V   | 4           | AT90LS2333-4AC<br>AT90LS2333-4PC | 32A<br>28P3 | Commercial<br>(0°C to 70°C)   |

|              |             | AT90LS2333-4AI<br>AT90LS2333-4PI | 32A<br>28P3 | Industrial<br>(-40°C to 85°C) |

| 4.0 - 6.0V   | 8           | AT90S2333-8AC<br>AT90S2333-8PC   | 32A<br>28P3 | Commercial<br>(0°C to 70°C)   |

|              |             | AT90S2333-8AI<br>AT90S2333-8PI   | 32A<br>28P3 | Industrial<br>(-40°C to 85°C) |

| 2.7 - 6.0V   | 4           | AT90LS4433-4AC<br>AT90LS4433-4PC | 32A<br>28P3 | Commercial<br>(0°C to 70°C)   |

|              |             | AT90LS4433-4AI<br>AT90LS4433-4PI | 32A<br>28P3 | Industrial<br>(-40°C to 85°C) |

| 4.0 - 6.0V   | 8           | AT90S4433-8AC<br>AT90S4433-8PC   | 32A<br>28P3 | Commercial<br>(0°C to 70°C)   |

|              |             | AT90S4433-8AI<br>AT90S4433-8PI   | 32A<br>28P3 | Industrial<br>(-40°C to 85°C) |

| Package Type |                                                                   |  |

|--------------|-------------------------------------------------------------------|--|

| 28P3         | 28-lead, 0.300" Wide, Plastic Dual in Line Package (PDIP)         |  |

| 32A          | 32-lead, Thin (1.0 mm) Plastic Gull Wing Quad Flat Package (TQFP) |  |