Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | SPI, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 20                                                                      |

| Program Memory Size        | 2KB (1K x 16)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 128 x 8                                                                 |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                 |

| Data Converters            | A/D 6x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C                                                            |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 28-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at90s2333-8pi |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

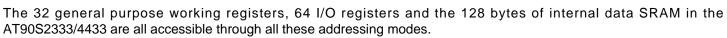

See the next section for a detailed description of the different addressing modes.

### **Program and Data Addressing Modes**

The AT90S2333/4433 AVR RISC microcontroller supports powerful and efficient addressing modes for access to the Flash program memory, SRAM, Register File, and I/O data memory. This section describes the different addressing modes supported by the AVR architecture. In the figures, OP means the operation code part of the instruction word. To simplify, not all figures show the exact location of the addressing bits.

### **Register Direct, Single Register Rd**

Figure 10. Direct Single Register Addressing

The operand is contained in register d (Rd).

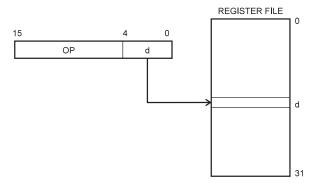

### Register Direct, Two Registers Rd and Rr

Figure 11. Direct Register Addressing, Two Registers

Operands are contained in register r (Rr) and d (Rd). The result is stored in register d (Rd).

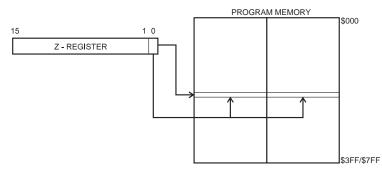

### **Constant Addressing Using the LPM Instruction**

Figure 18. Code Memory Constant Addressing

Constant byte address is specified by the Z-register contents. The 15 MSBs select word address (0 - 1K/2K), the LSB selects low byte if cleared (LSB = 0) or high byte if set (LSB = 1).

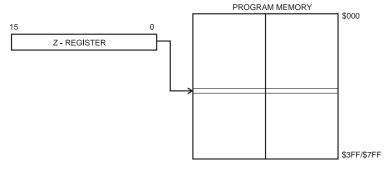

### Indirect Program Addressing, IJMP and ICALL

Figure 19. Indirect Program Memory Addressing

Program execution continues at address contained by the Z-register (i.e. the PC is loaded with the contents of the Z-register).

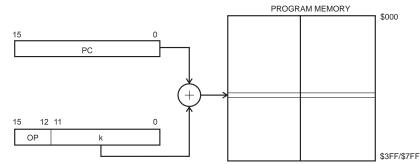

### Relative Program Addressing, RJMP and RCALL

Figure 20. Relative Program Memory Addressing

Program execution continues at address PC + k + 1. The relative address k is from -2048 to 2047.

| Table 2. | AT90S2333/4433 | I/O Space | (Continued) | ) |

|----------|----------------|-----------|-------------|---|

|----------|----------------|-----------|-------------|---|

| I/O Address (SRAM Address) | Name   | Function                                      |

|----------------------------|--------|-----------------------------------------------|

| \$15 (\$35)                | PORTC  | Data Register, Port C                         |

| \$14 (\$34)                | DDRC   | Data Direction Register, Port C               |

| \$13 (\$33)                | PINC   | Input Pins, Port C                            |

| \$12 (\$32)                | PORTD  | Data Register, Port D                         |

| \$11 (\$31)                | DDRD   | Data Direction Register, Port D               |

| \$10 (\$30)                | PIND   | Input Pins, Port D                            |

| \$0F (\$2F)                | SPDR   | SPI I/O Data Register                         |

| \$0E (\$2E)                | SPSR   | SPI Status Register                           |

| \$0D (\$2D)                | SPCR   | SPI Control Register                          |

| \$0C (\$2C)                | UDR    | UART I/O Data Register                        |

| \$0B (\$2B)                | USR    | UART Status Register                          |

| \$0A (\$2A)                | UCR    | UART Control Register                         |

| \$09 (\$29)                | UBRR   | UART Baud Rate Register                       |

| \$08 (\$28)                | ACSR   | Analog Comparator Control and Status Register |

| \$07 (\$27)                | ADMUX  | ADC Multiplexer Select Register               |

| \$06 (\$26)                | ADCSR  | ADC Control and Status Register               |

| \$05 (\$25)                | ADCH   | ADC Data Register High                        |

| \$04 (\$24)                | ADCL   | ADC Data Register Low                         |

| \$03 (\$23)                | UBRRHI | UART Baud Rate Register High                  |

Note: Reserved and unused locations are not shown in the table.

All AT90S2333/4433 I/Os and peripherals are placed in the I/O space. The I/O locations are accessed by the IN and OUT instructions transferring data between the 32 general purpose working registers and the I/O space. I/O registers within the address range \$00 - \$1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the value of single bits can be checked by using the SBIS and SBIC instructions. Refer to the instruction set chapter for more details. When using the I/O specific commands IN, OUT the I/O addresses \$00 - \$3F must be used. When addressing I/O registers as SRAM, \$20 must be added to this address. All I/O register addresses throughout this document are shown with the SRAM address in parentheses.

For compatibility with future devices, reserved bits should be written to zero when accessed. Reserved I/O memory addresses should never be written.

Some of the status flags are cleared by writing a logical one to them. Note that the CBI and SBI instructions will operate on all bits in the I/O register, writing a one back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers \$00 to \$1F only.

The I/O and peripherals control registers are explained in the following sections.

instruction, and it is incremented by two when an address is popped from the Stack with return from subroutine RET or return from interrupt RETI.

### **Reset and Interrupt Handling**

The AT90S2333/4433 provides 13 different interrupt sources. These interrupts and the separate reset vector, each have a separate program vector in the program memory space. All interrupts are assigned individual enable bits which must be set (one) together with the I-bit in the status register in order to enable the interrupt.

The lowest addresses in the program memory space are automatically defined as the Reset and Interrupt vectors. The complete list of vectors is shown in Table 3. The list also determines the priority levels of the different interrupts. The lower the address the higher is the priority level. RESET has the highest priority, and next is INT0 - the External Interrupt Request 0, etc.

| Vector No. | Program Address | Source      | Interrupt Definition                                              |

|------------|-----------------|-------------|-------------------------------------------------------------------|

| 1          | \$000           | RESET       | External Pin, Power-On Reset, Brown-Out Reset and Watchdog Reset. |

| 2          | \$001           | INT0        | External Interrupt Request 0                                      |

| 3          | \$002           | INT1        | External Interrupt Request 1                                      |

| 4          | \$003           | TIMER1 CAPT | Timer/Counter1 Capture Event                                      |

| 5          | \$004           | TIMER1 COMP | Timer/Counter1 Compare Match                                      |

| 6          | \$005           | TIMER1 OVF  | Timer/Counter1 Overflow                                           |

| 7          | \$006           | TIMER0 OVF  | Timer/Counter0 Overflow                                           |

| 8          | \$007           | SPI, STC    | Serial Transfer Complete                                          |

| 9          | \$008           | UART, RX    | UART, Rx Complete                                                 |

| 10         | \$009           | UART, UDRE  | UART Data Register Empty                                          |

| 11         | \$00A           | UART, TX    | UART, Tx Complete                                                 |

| 12         | \$00B           | ADC         | ADC Conversion Complete                                           |

| 13         | \$00C           | EE_RDY      | EEPROM Ready                                                      |

| 14         | \$00D           | ANA_COMP    | Analog Comparator                                                 |

### Table 3. Reset and Interrupt Vectors

### The most typical program setup for the Reset and Interrupt Vector Addresses are:

| <i>J</i> 1 0 |        |      |           |                                             |

|--------------|--------|------|-----------|---------------------------------------------|

| Address      | Labels | Code |           | Comments                                    |

| \$000        |        | rjmp | RESET     | ; Reset Handler                             |

| \$001        |        | rjmp | EXT_INT0  | ; IRQ0 Handler                              |

| \$002        |        | rjmp | EXT_INT1  | ; IRQ1 Handler                              |

| \$003        |        | rjmp | TIM1_CAPT | ; Timerl Capture Handler                    |

| \$004        |        | rjmp | TIM1_COMP | ; Timerl compare Handler                    |

| \$005        |        | rjmp | TIM1_OVF  | ; Timerl Overflow Handler                   |

| \$006        |        | rjmp | TIM0_OVF  | ; Timer0 Overflow Handler                   |

| \$007        |        | rjmp | SPI_STC;  | ; SPI Transfer Complete Handler             |

| \$008        |        | rjmp | UART_RXC  | ; UART RX Complete Handler                  |

| \$009        |        | rjmp | UART_DRE  | ; UDR Empty Handler                         |

| \$00a        |        | rjmp | UART_TXC  | ; UART TX Complete Handler                  |

| \$00b        |        | rjmp | ADC       | ; ADC Conversion Complete Interrupt Handler |

| \$00c        |        | rjmp | EE_RDY    | ; EEPROM Ready Handler                      |

| \$00d        |        | rjmp | ANA_COMP  | ; Analog Comparator Handler                 |

|              |        |      |           |                                             |

;

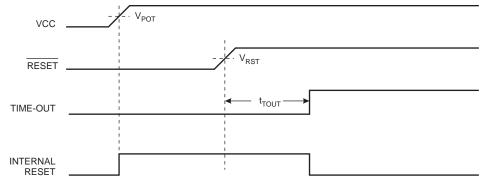

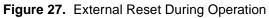

### **External Reset**

An external reset is generated by a low level on the  $\overline{\text{RESET}}$  pin. Reset pulses longer than 50 ns will generate a reset, even if the clock is not running. Shorter pulses are not guaranteed to generate a reset. When the applied signal reaches the Reset Threshold Voltage V<sub>RST</sub> on its positive edge, the delay timer starts the MCU after the Time-out period t<sub>TOUT</sub> has expired.

### **Brown-Out Detection**

AT90S2333/4433 has an on-chip brown-out detection (BOD) circuit for monitoring the V<sub>CC</sub> level during the operation. The power supply must be decoupled with a 47 nF to 100 nF capacitor if the BOD function is used. The BOD circuit can be enabled/disabled by the fuse BODEN. When BODEN is enabled (BODEN programmed), and V<sub>CC</sub> decreases to a value below the trigger level, the brown-out reset is immediately activated. When V<sub>CC</sub> increases above the trigger level, the brown-out reset is deactivated after a delay. The delay is defined by the user in the same way as the delay of POR signal, in Table 5. The trigger level for the BOD can be selected by the fuse BODLEVEL to be 2.7V (BODLEVEL unprogrammed), or 4.0V (BODLEVEL programmed). The trigger level has a hysteresis of 50 mV to ensure spike free brown-out detection.

The BOD circuit will only detect a drop in  $V_{CC}$  if the voltage stays below the trigger level for longer than 3 µs for trigger level 4.0V, 7 µs for trigger level 2.7V (typical values).

### Table 15. PWM Outputs OCR = \$0000 or TOP

| COM11 | COM10 | OCR1   | Output OC1 |

|-------|-------|--------|------------|

| 1     | 0     | \$0000 | L          |

| 1     | 0     | TOP    | н          |

| 1     | 1     | \$0000 | Н          |

| 1     | 1     | TOP    | L          |

In PWM mode, the Timer Overflow Flag1, TOV1, is set when the counter changes direction at \$0000. Timer Overflow Interrupt1 operates exactly as in normal Timer/Counter mode, i.e. it is executed when TOV1 is set provided that Timer Overflow Interrupt1 and global interrupts are enabled. This also applies to the Timer Output Compare1 flag and interrupt.

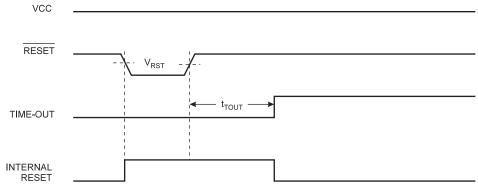

## Watchdog Timer

The Watchdog Timer is clocked from a separate on-chip oscillator. By controlling the Watchdog Timer prescaler, the Watchdog reset interval can be adjusted as shown in Table 6. See characterization data for typical values at other  $V_{CC}$  levels. The WDR - Watchdog Reset - instruction resets the Watchdog Timer. Eight different clock cycle periods can be selected to determine the reset period. If the reset period expires without another Watchdog reset, the AT90S2333/4433 resets and executes from the reset vector. For timing details on the Watchdog reset, refer to page 22.

To prevent unintentional disabling of the watchdog, a special turn-off sequence must be followed when the watchdog is disabled. Refer to the description of the Watchdog Timer Control Register for details.

### Figure 35. Watchdog Timer

### Watchdog Timer Control Register - WDTCR

| Bit           | 7 | 6 | 5 | 4     | 3   | 2    | 1    | 0    | _     |

|---------------|---|---|---|-------|-----|------|------|------|-------|

| \$21 (\$41)   | - | - | - | WDTOE | WDE | WDP2 | WDP1 | WDP0 | WDTCR |

| Read/Write    | R | R | R | R/W   | R/W | R/W  | R/W  | R/W  | -     |

| Initial value | 0 | 0 | 0 | 0     | 0   | 0    | 0    | 0    |       |

### • Bits 7..5 - Res: Reserved bits

36

These bits are reserved bits in the AT90S2333/4433 and will always read as zero.

### Bit 4 - WDTOE: Watch Dog Turn-Off Enable

This bit must be set (one) when the WDE bit is cleared. Otherwise, the watchdog will not be disabled. Once set, hardware will clear this bit to zero after four clock cycles. Refer to the description of the WDE bit for a watchdog disable procedure.

### • Bit 3 - WDE: Watch Dog Enable

When the WDE is set (one) the Watchdog Timer is enabled, and if the WDE is cleared (zero) the Watchdog Timer function is disabled. WDE can only be cleared if the WDTOE bit is set(one). To disable an enabled watchdog timer, the following procedure must be followed:

- 1. In the same operation, write a logical one to WDTOE and WDE. A logical one must be written to WDE even though it is set to one before the disable operation starts.

- 2. Within the next four clock cycles, write a logical 0 to WDE. This disables the watchdog.

### • Bits 2..0 - WDP2, WDP1, WDP0: Watch Dog Timer Prescaler 2, 1 and 0

The WDP2, WDP1 and WDP0 bits determine the Watchdog Timer prescaling when the Watchdog Timer is enabled. The different prescaling values and their corresponding time-out Periods are shown inTable 16.

| WDP2 | WDP1 | WDP0 | Number of WDT Oscillator cycles | Typical time-out at $V_{CC} = 3.0V$ | Typical time-out<br>at V <sub>CC</sub> = 5.0V |

|------|------|------|---------------------------------|-------------------------------------|-----------------------------------------------|

| 0    | 0    | 0    | 16K cycles                      | 47 ms                               | 15 ms                                         |

| 0    | 0    | 1    | 32K cycles                      | 94 ms                               | 30 ms                                         |

| 0    | 1    | 0    | 64K cycles                      | 0.19 s                              | 60 ms                                         |

| 0    | 1    | 1    | 128K cycles                     | 0.38 s                              | 0.12 s                                        |

| 1    | 0    | 0    | 256K cycles                     | 0.75 s                              | 0,24 s                                        |

| 1    | 0    | 1    | 512K cycles                     | 1.5 s                               | 0.49 s                                        |

| 1    | 1    | 0    | 1,024K cycles                   | 3.0 s                               | 0.97 s                                        |

| 1    | 1    | 1    | 2,048K cycles                   | 6.0 s                               | 1.9 s                                         |

### Table 16. Watch Dog Timer Prescale Select

Note: The frequency of the watchdog oscillator is voltage dependent as shown in the Electrical Characteristics section. The WDR - Watchdog Reset - instruction should always be executed before the Watchdog Timer is enabled. This ensures that the reset period will be in accordance with the Watchdog Timer prescale settings. If the Watchdog Timer is enabled without reset, the watchdog timer may not start counting from zero.

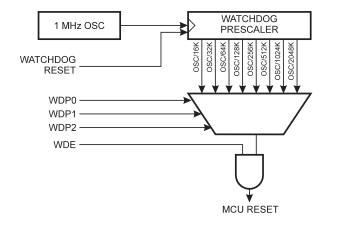

## UART

The AT90S2333/4433 features a full duplex (separate receive and transmit registers) Universal Asynchronous Receiver and Transmitter (UART). The main features are:

- Baud rate generator generates any baud rate

- High baud rates at low XTAL frequencies

- 8 or 9 bits data

- Noise filtering

- Overrun detection

- Framing Error detection

- False Start Bit detection

- Three separate interrupts on TX Complete, TX Data Register Empty and RX Complete

- Multi-Processor Communication Mode

### **Data Transmission**

A block schematic of the UART transmitter is shown in Figure 40.

Figure 40. UART Transmitter

Data transmission is initiated by writing the data to be transmitted to the UART I/O Data Register, UDR. Data is transferred from UDR to the Transmit shift register when:

• A new character has been written to UDR after the stop bit from the previous character has been shifted out. The shift register is loaded immediately.

### Bit 3 - OR: OverRun

This bit is set if an Overrun condition is detected, i.e. when a character already present in the UDR register is not read before the next character has been shifted into the Receiver Shift register. The OR bit is buffered, which means that it will be set once the valid data still in UDRE is read.

The OR bit is cleared (zero) when data is received and transferred to UDR.

### • Bits 2..1 - Res: Reserved bits

These bits are reserved bits in the AT90S2333/4433 and will always read as zero.

### • Bit 0 - MPCM: Multi-Processor Communication Mode

This bit is used to enter Multi-Processor Communication Mode. The bit is set when the slave MCU waits for an address byte to be received. When the MCU has been addressed, the MCU switches off the MPCM bit, and starts data reception.

For a detailed description, see "Multi-Processor Communication Mode".

### **UART Control and Status Registers - UCSRB**

| Bit           | 7     | 6     | 5     | 4    | 3    | 2    | 1    | 0    | _     |

|---------------|-------|-------|-------|------|------|------|------|------|-------|

| \$0A (\$2A)   | RXCIE | TXCIE | UDRIE | RXEN | TXEN | CHR9 | RXB8 | TXB8 | UCSRB |

| Read/Write    | R/W   | R/W   | R/W   | R/W  | R/W  | R/W  | R    | W    | -     |

| Initial value | 0     | 0     | 0     | 0    | 0    | 0    | 1    | 0    |       |

### • Bit 7 - RXCIE: RX Complete Interrupt Enable

When this bit is set (one), a setting of the RXC bit in USR will cause the Receive Complete interrupt routine to be executed provided that global interrupts are enabled.

### Bit 6 - TXCIE: TX Complete Interrupt Enable

When this bit is set (one), a setting of the TXC bit in USR will cause the Transmit Complete interrupt routine to be executed provided that global interrupts are enabled.

### • Bit 5 - UDRIE: UART Data Register Empty Interrupt Enable

When this bit is set (one), a setting of the UDRE bit in USR will cause the UART Data Register Empty interrupt routine to be executed provided that global interrupts are enabled.

### • Bit 4 - RXEN: Receiver Enable

This bit enables the UART receiver when set (one). When the receiver is disabled, the TXC, OR and FE status flags cannot become set. If these flags are set, turning off RXEN does not cause them to be cleared.

### • Bit 3 - TXEN: Transmitter Enable

This bit enables the UART transmitter when set (one). When disabling the transmitter while transmitting a character, the transmitter is not disabled before the character in the shift register plus any following character in UDR has been completely transmitted.

### Bit 2 - CHR9: 9 Bit Characters

When this bit is set (one) transmitted and received characters are 9 bit long plus start and stop bits. The 9th bit is read and written by using the RXB8 and TXB8 bits in UCR, respectively. The 9th data bit can be used as an extra stop bit or a parity bit.

### Bit 1 - RXB8: Receive Data Bit 8

When CHR9 is set (one), RXB8 is the 9th data bit of the received character.

### • Bit 0 - TXB8: Transmit Data Bit 8

When CHR9 is set (one), TXB8 is the 9th data bit in the character to be transmitted.

### **Baud Rate Generator**

The baud rate generator is a frequency divider which generates baud-rates according to the following equation:

$$\mathsf{BAUD} = \frac{f_{\mathsf{CK}}}{\mathsf{16}(\mathsf{UBR}+1)}$$

- BAUD = Baud-Rate

- f<sub>CK</sub>= Crystal Clock frequency

- UBR = Contents of the UBRRH and UBRR registers, (0-4095)

# Analog to Digital Converter

Feature list:

- 10-bit Resolution

- ± 2 LSB Absolute Accuracy

- 0.5 LSB Integral Non-Linearity

- 65 260 µs Conversion Time

- Up to 15 kSPS

- 6 Multiplexed Input Channels

- Rail-to-Rail Input Range

- Free Run or Single Conversion Mode

- Interrupt on ADC conversion complete.

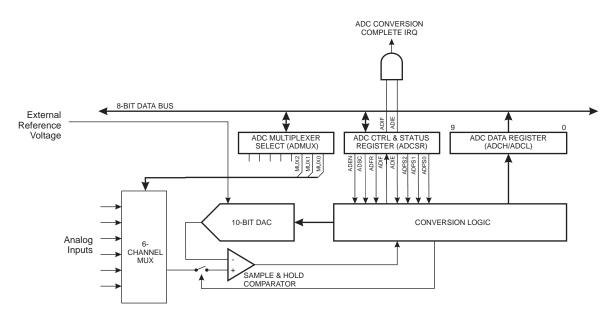

- Sleep Mode Noise Canceler

The AT90S2333/4433 features a 10-bit successive approximation ADC. The ADC is connected to a 6-channel Analog Multiplexer which allows each pin of Port C to be used as an input for the ADC. The ADC contains a Sample and Hold Amplifier which ensures that the input voltage to the ADC is held at a constant level during conversion. A block diagram of the ADC is shown in Figure 44.

The ADC has two separate analog supply voltage pins, AVCC and AGND. AGND must be connected to GND, and the voltage on AVCC must not differ more than  $\pm$  0.3 V from V<sub>CC</sub>. See the paragraph ADC Noise Canceling Techniques on how to connect these pins.

An external reference voltage must be applied to the AREF pin. This voltage must be in the range AGND - AVCC.

### Figure 44. Analog to Digital Converter Block Schematic

### Operation

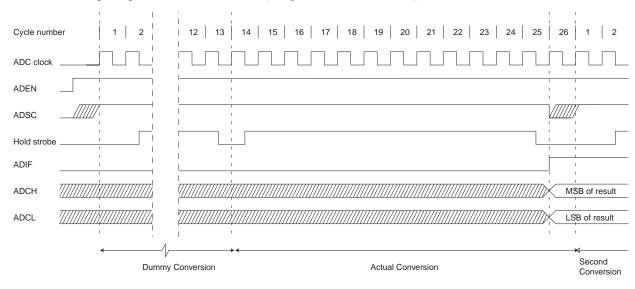

The ADC can operate in two modes - Single Conversion and Free Run Mode. In Single Conversion Mode, each conversion will have to be initiated by the user. In Free Run Mode the ADC is constantly sampling and updating the ADC Data Register. The ADFR bit in ADCSR selects between the two available modes.

The ADMUX register selects which one of the six analog input channels to be used as input to the ADC.

### Figure 46. ADC Timing Diagram, First Conversion (Single Conversion Mode)

### Table 21. ADC Conversion Time

| Condition                | Sample Cycle Number | Result Ready (cycle<br>number) | Total Conversion Time<br>(cycles) | Total Conversion Time<br>(μs) |

|--------------------------|---------------------|--------------------------------|-----------------------------------|-------------------------------|

| 1st Conversion, Free Run | 14                  | 25                             | 25                                | 125 - 500                     |

| 1st Conversion, Single   | 14                  | 25                             | 26                                | 130 - 520                     |

| Free Run Conversion      | 2                   | 13                             | 13                                | 65 - 260                      |

| Single Conversion        | 2                   | 13                             | 14                                | 70 - 280                      |

### Figure 47. ADC Timing Diagram, Single Conversion

| Cycle num   | ber   1   2   3   4   5   6   7   8   9   10   11   12   13   14 | 1   2                |

|-------------|------------------------------------------------------------------|----------------------|

| ADC clock   |                                                                  |                      |

| ADSC        |                                                                  | 1                    |

| Hold strobe |                                                                  | 1<br>1               |

| ADIF        |                                                                  | <br> <br>            |

| ADCH        |                                                                  | MSB of result        |

| ADCL        |                                                                  | LSB of result        |

|             | ← One Conversion                                                 | ×<br>Next Conversion |

## I/O Ports

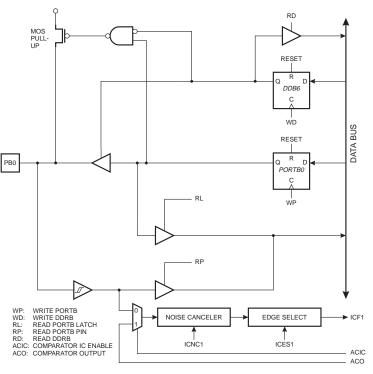

All AVR ports have true Read-Modify-Write functionality when used as general digital I/O ports. This means that the direction of one port pin can be changed without unintentionally changing the direction of any other pin with the SBI and CBI instructions. The same applies for changing drive value (if configured as output) or enabling/disabling of pull-up resistors (if configured as input).

## Port B

Port B is a 6-bit bi-directional I/O port.

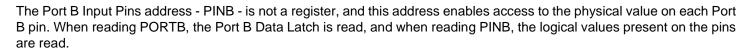

Three I/O memory address locations are allocated for the Port B, one each for the Data Register - PORTB, \$18(\$38), Data Direction Register - DDRB, \$17(\$37) and the Port B Input Pins - PINB, \$16(\$36). The Port B Input Pins address is read only, while the Data Register and the Data Direction Register are read/write.

All port pins have individually selectable pull-up resistors. The Port B output buffers can sink 20mA and thus drive LED displays directly. When pins PB0 to PB7 are used as inputs and are externally pulled low, they will source current if the internal pull-up resistors are activated.

The Port B pins with alternate functions are shown in the following table:

| Port Pin | Alternate Functions                               |  |  |  |  |  |

|----------|---------------------------------------------------|--|--|--|--|--|

| PB0      | ICP (Timer/Counter 1 input capture pin)           |  |  |  |  |  |

| PB1      | OC1 (Timer/Counter 1 output compare match output) |  |  |  |  |  |

| PB2      | SS (SPI Slave Select input)                       |  |  |  |  |  |

| PB3      | MOSI (SPI Bus Master Output/Slave Input)          |  |  |  |  |  |

| PB4      | MISO (SPI Bus Master Input/Slave Output)          |  |  |  |  |  |

| PB5      | SCK (SPI Bus Serial Clock)                        |  |  |  |  |  |

### Table 23. Port B Pins Alternate Functions

When the pins are used for the alternate function, the DDRB and PORTB register has to be set according to the alternate function description.

### Port B Data Register - PORTB

| Bit           | 7 | 6 | 5      | 4      | 3      | 2      | 1      | 0      |       |

|---------------|---|---|--------|--------|--------|--------|--------|--------|-------|

| \$18 (\$38)   | - | - | PORTB5 | PORTB4 | PORTB3 | PORTB2 | PORTB1 | PORTB0 | PORTB |

| Read/Write    | R | R | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | •     |

| Initial value | 0 | 0 | 0      | 0      | 0      | 0      | 0      | 0      |       |

### Port B Data Direction Register - DDRB

| Bit           | 7 | 6 | 5    | 4    | 3    | 2    | 1    | 0    |      |

|---------------|---|---|------|------|------|------|------|------|------|

| \$17 (\$37)   | - | - | DDB5 | DDB4 | DDB3 | DDB2 | DDB1 | DDB0 | DDRB |

| Read/Write    | R | R | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | -    |

| Initial value | 0 | 0 | 0    | 0    | 0    | 0    | 0    | 0    |      |

### Port B Input Pins Address - PINB

| Bit           | 7 | 6 | 5     | 4     | 3     | 2     | 1     | 0     |      |

|---------------|---|---|-------|-------|-------|-------|-------|-------|------|

| \$16 (\$36)   | - | - | PINB5 | PINB4 | PINB3 | PINB2 | PINB1 | PINB0 | PINB |

| Read/Write    | R | R | R     | R     | R     | R     | R     | R     | •    |

| Initial value | 0 | 0 | Hi-Z  | Hi-Z  | Hi-Z  | Hi-Z  | Hi-Z  | Hi-Z  |      |

### Port B As General Digital I/O

All 6 pins in Port B have equal functionality when used as digital I/O pins.

PBn, General I/O pin: The DDBn bit in the DDRB register selects the direction of this pin, if DDBn is set (one), PBn is configured as an output pin. If DDBn is cleared (zero), PBn is configured as an input pin. If PORTBn is set (one) when the pin configured as an input pin, the MOS pull up resistor is activated. To switch the pull up resistor off, the PORTBn has to be cleared (zero) or the pin has to be configured as an output pin. The port pins are tristated when a reset condition becomes active, even if the clock is not running.

| Table 24. | DDBn | Effects | on | Port | B Pins |

|-----------|------|---------|----|------|--------|

|-----------|------|---------|----|------|--------|

| DDBn | PORTBn | I/O    | Pull Up | Comment                                     |

|------|--------|--------|---------|---------------------------------------------|

| 0    | 0      | Input  | No      | Tri-state (Hi-Z)                            |

| 0    | 1      | Input  | Yes     | PBn will source current if ext. pulled low. |

| 1    | 0      | Output | No      | Push-Pull Zero Output                       |

| 1    | 1      | Output | No      | Push-Pull One Output                        |

Note: n: 5...0, pin number.

### **Alternate Functions Of Port B**

The alternate pin configuration is as follows:

### • SCK - Port B, Bit 5

SCK: Master clock output, slave clock input pin for SPI channel. When the SPI is enabled as a slave, this pin is configured as an input regardless of the setting of DDB5. When the SPI is enabled as a master, the data direction of this pin is controlled by DDB5. When the pin is forced to be an input, the pull-up can still be controlled by the PORTB5 bit. See the description of the SPI port for further details.

### • MISO - Port B, Bit 4

MISO: Master data input, slave data output pin for SPI channel. When the SPI is enabled as a master, this pin is configured as an input regardless of the setting of DDB4. When the SPI is enabled as a slave, the data direction of this pin is controlled by DDB4. When the pin is forced to be an input, the pull-up can still be controlled by the PORTB4 bit. See the description of the SPI port for further details.

### • MOSI - Port B, Bit 3

MOSI: SPI Master data output, slave data input for SPI channel. When the SPI is enabled as a slave, this pin is configured as an input regardless of the setting of DDB3. When the SPI is enabled as a master, the data direction of this pin is controlled by DDB3. When the pin is forced to be an input, the pull-up can still be controlled by the PORTB3 bit. See the description of the SPI port for further details.

### • SS - Port B, Bit 2

S: Slave port select input. When the SPI is enabled as a slave, this pin is configured as an input regardless of the setting of DDB2. As a slave, the SPI is activated when this pin is driven low. When the SPI is enabled as a master, the data direction of this pin is controlled by DDB2. When the pin is forced to be an input, the pull-up can still be controlled by the PORTB2 bit. See the description of the SPI port for further details.

### • OC1 - Port B, Bit1

OC1, Output compare match output: PB1 pin can serve as an external output for the Timer/Counter1 output compare. The pin has to be configured as an output (DDB1 set (one)) to serve this function. See the timer description on how to enable this function. The OC1 pin is also the output pin for the PWM mode timer function.

### • ICP- Port B, Bit0

ICP, Input Capture Pin: PB0 pin can serve as an external input for the Timer/Counter1 input capture. The pin has to be configured as an input (DDB0 cleared (zero)) to serve this function. See the timer description on how to enable this function.

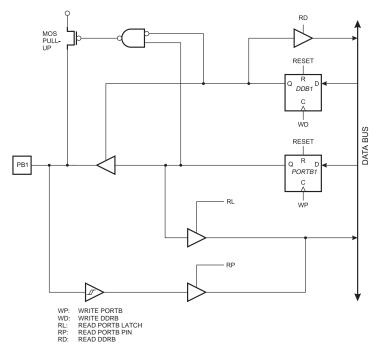

Figure 50. Port B Schematic Diagram (Pin PB0)

Figure 51. Port B Schematic Diagram (Pin PB1)

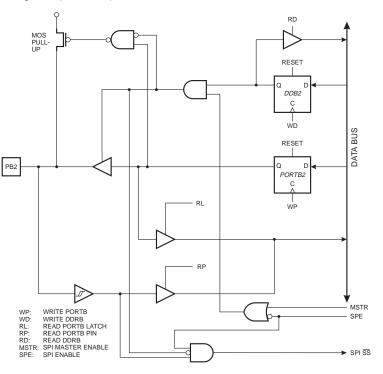

Figure 52. Port B Schematic Diagram (Pin PB2)

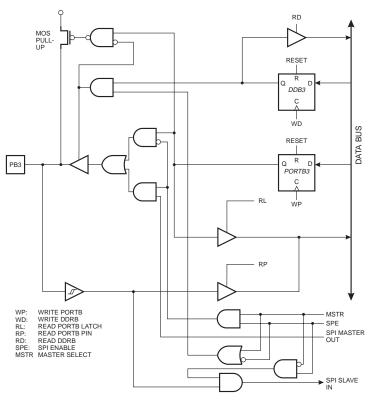

Figure 53. Port B Schematic Diagram (Pin PB3)

| DDCn | PORTCn | I/O    | Pull Up                                         | Comment               |  |  |  |  |  |

|------|--------|--------|-------------------------------------------------|-----------------------|--|--|--|--|--|

| 0    | 0      | Input  | No                                              | Tri-state (Hi-Z)      |  |  |  |  |  |

| 0    | 1      | Input  | Yes PCn will source current if ext. pulled low. |                       |  |  |  |  |  |

| 1    | 0      | Output | No                                              | Push-Pull Zero Output |  |  |  |  |  |

| 1    | 1      | Output | No                                              | Push-Pull One Output  |  |  |  |  |  |

### Table 25. DDCn Effects on Port C Pins

Note: n: 5...0, pin number

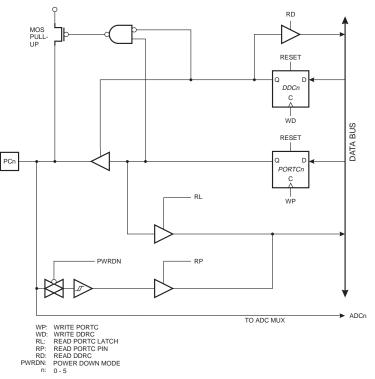

### **Port C Schematics**

Note that all port pins are synchronized. The synchronization latch is however, not shown in the figure.

Figure 56. Port C Schematic Diagrams (Pins PC0 - PC5)

### Port D

Port D is an 8 bit bi-directional I/O port with internal pull-up resistors.

Three I/O memory address locations are allocated for Port D, one each for the Data Register - PORTD, \$12(\$32), Data Direction Register - DDRD, \$11(\$31) and the Port D Input Pins - PIND, \$10(\$30). The Port D Input Pins address is read only, while the Data Register and the Data Direction Register are read/write.

The Port D output buffers can sink 20 mA. As inputs, Port D pins that are externally pulled low will source current if the pullup resistors are activated.

Some Port D pins have alternate functions as shown in the following table:

### Programming the EEPROM

The programming algorithm for the EEPROM data memory is as follows (refer to Programming the Flash for details on Command, Address and Data loading):

- 1. A: Load Command '0001 0001'.

- 2. C: Load Address Low Byte (\$00 \$7F/\$FF).

- 3. D: Load Data Low Byte (\$00 \$FF).

- 4. E: Write Data Low Byte.

### **Reading the EEPROM**

The algorithm for reading the EEPROM memory is as follows (refer to Programming the Flash for details on Command and Address loading):

- 1. A: Load Command '0000 0011'.

- 2. C: Load Address Low Byte (\$00 \$7F/\$FF).

- 3. Set OE to '0', and BS to '0'. The EEPROM data byte can now be read at DATA.

- 4. Set OE to '1'.

### **Programming the Fuse Bits**

The algorithm for programming the Fuse bits is as follows (refer to Programming the Flash for details on Command and Data loading):

- 1. A: Load Command '0100 0000'.

- 2. D: Load Data Low Byte. Bit  $n = 0^{\circ}$  programs and bit  $n = 1^{\circ}$  erases the Fuse bit.

- Bit 5 = SPIEN Fuse bit

- Bit 4 = BODLEVEL Fuse bit

- Bit 3 = BODEN Fuse bit

- Bit 2 = CKSEL2 Fuse bit

- Bit 1 = CKSEL1 Fuse bit

- Bit 0 = CKSEL0 Fuse bit

Bit  $7-6 = 1^{\circ}$ . These bits are reserved and should be left unprogrammed (1).

Give WR a t<sub>WLWH\_PFB</sub> wide negative pulse to execute the programming, t<sub>WLWH\_PFB</sub> is found in Table 33. Programming the Fuse bits does not generate any activity on the RDY/BSY pin.

### **Programming the Lock Bits**

The algorithm for programming the Lock bits is as follows (refer to Programming the Flash for details on Command and Data loading):

- 1. A: Load Command '0010 0000'.

- 2. D: Load Data Low Byte. Bit n = '0' programs the Lock bit.

- Bit 2 = Lock Bit2

- Bit 1 = Lock Bit1

- Bit 7-3,0 = 1'. These bits are reserved and should be left unprogrammed (1').

- 3. E: Write Data Low Byte.

The Lock bits can only be cleared by executing Chip Erase.

### **Reading the Fuse and Lock Bits**

The algorithm for reading the Fuse and Lock bits is as follows (refer to Programming the Flash for details on Command loading):

- 1. A: Load Command '0000 0100'.

- 2. Set  $\overline{\text{OE}}$  to '0', and BS to '0'. The status of the Fuse bits can now be read at DATA ('0' means programmed).

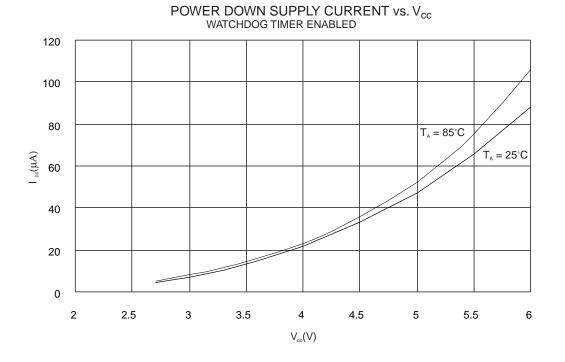

Figure 75. Power Down Supply Current vs. V<sub>CC</sub>

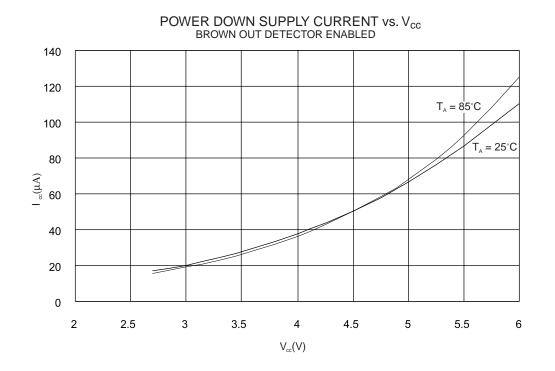

Figure 76. Power Down Supply Current vs. V<sub>CC</sub>

## **Register Summary (Continued)**

| Address                                                                                                                             | Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Page |

|-------------------------------------------------------------------------------------------------------------------------------------|----------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| \$02 (\$22)                                                                                                                         | Reserved |       |       |       |       |       |       |       |       |      |

| \$01 (\$21)                                                                                                                         | Reserved |       |       |       |       |       |       |       |       |      |

| \$00 (\$20)                                                                                                                         | Reserved |       |       |       |       |       |       |       |       |      |

| lates: 1. For compatibility with future devices, received bits should be written to zero if accessed. Received I/O memory addresses |          |       |       |       |       |       |       |       |       |      |

Notes: 1. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

Some of the status flags are cleared by writing a logical one to them. Note that the CBI and SBI instructions will operate on all bits in the I/O register, writing a one back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers \$00 to \$1F only.

# AT90S/LS2333 and AT90S/LS4433

# **Ordering Information**

| Power Supply | Speed (MHz) | Ordering Code                    | Package     | Operation Range               |

|--------------|-------------|----------------------------------|-------------|-------------------------------|

| 2.7 - 6.0V   | 4           | AT90LS2333-4AC<br>AT90LS2333-4PC | 32A<br>28P3 | Commercial<br>(0°C to 70°C)   |

|              |             | AT90LS2333-4AI<br>AT90LS2333-4PI | 32A<br>28P3 | Industrial<br>(-40°C to 85°C) |

| 4.0 - 6.0V   | 8           | AT90S2333-8AC<br>AT90S2333-8PC   | 32A<br>28P3 | Commercial<br>(0°C to 70°C)   |

|              |             | AT90S2333-8AI<br>AT90S2333-8PI   | 32A<br>28P3 | Industrial<br>(-40°C to 85°C) |

| 2.7 - 6.0V   | 4           | AT90LS4433-4AC<br>AT90LS4433-4PC | 32A<br>28P3 | Commercial<br>(0°C to 70°C)   |

|              |             | AT90LS4433-4AI<br>AT90LS4433-4PI | 32A<br>28P3 | Industrial<br>(-40°C to 85°C) |

| 4.0 - 6.0V   | 8           | AT90S4433-8AC<br>AT90S4433-8PC   | 32A<br>28P3 | Commercial<br>(0°C to 70°C)   |

|              |             | AT90S4433-8AI<br>AT90S4433-8PI   | 32A<br>28P3 | Industrial<br>(-40°C to 85°C) |

| Package Type                                                   |                                                                   |  |  |  |  |

|----------------------------------------------------------------|-------------------------------------------------------------------|--|--|--|--|

| 28P3 28-lead, 0.300" Wide, Plastic Dual in Line Package (PDIP) |                                                                   |  |  |  |  |

| 32A                                                            | 32-lead, Thin (1.0 mm) Plastic Gull Wing Quad Flat Package (TQFP) |  |  |  |  |