Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                            |

|----------------------------|------------------------------------------------------------|

| Product Status             | Obsolete                                                   |

| Core Processor             | 80C51                                                      |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 30/20MHz                                                   |

| Connectivity               | UART/USART                                                 |

| Peripherals                | POR, WDT                                                   |

| Number of I/O              | 32                                                         |

| Program Memory Size        | 16KB (16K x 8)                                             |

| Program Memory Type        | OTP                                                        |

| EEPROM Size                | -                                                          |

| RAM Size                   | 256 x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                |

| Data Converters            | -                                                          |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                          |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 44-LCC (J-Lead)                                            |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/at87c54x2-slsul |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Table 5-1. Pin Description for 40/44 pin packages

|                 | PIN NUMBER |              | TYPE         |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|-----------------|------------|--------------|--------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MNEMONIC        | DIL        | LCC          | VQFP 1.4     | TYPE | Name And Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| V <sub>SS</sub> | 20         | 22           | 16           | I    | Ground: 0V reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| Vss1            |            | 1            | 39           | I    | Optional Ground: Contact the Sales Office for ground connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| V <sub>CC</sub> | 40         | 44           | 38           | I    | Power Supply: This is the power supply voltage for normal, idle and power-down operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| P0.0-P0.7       | 39-32      | 43-36        | 37-30        | I/O  | Port 0: Port 0 is an open-drain, bidirectional I/O port. Port 0 pins that have 1s writte<br>them float and can be used as high impedance inputs. Port 0 pins must be polarize<br>Vcc or Vss in order to prevent any parasitic current consumption. Port 0 is also the<br>multiplexed low-order address and data bus during access to external program ar<br>data memory. In this application, it uses strong internal pull-up when emitting 1s. P<br>also inputs the code bytes during EPROM programming. External pull-ups are requ<br>during program verification during which P0 outputs the code bytes.                                                                                                               |  |  |  |

| P1.0-P1.7       | 1-8        | 2-9          | 40-44<br>1-3 | I/O  | Port 1: Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. Port 1 pins that<br>have 1s written to them are pulled high by the internal pull-ups and can be used as<br>inputs. As inputs, Port 1 pins that are externally pulled low will source current becau<br>of the internal pull-ups. Port 1 also receives the low-order address byte during mem<br>programming and verification.<br>Alternate functions for Port 1 include:                                                                                                                                                                                                                                                                          |  |  |  |

|                 | 1          | 2            | 40           | I/O  | T2 (P1.0): Timer/Counter 2 external count input/Clockout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                 | 2          | 3            | 41           | I    | T2EX (P1.1): Timer/Counter 2 Reload/Capture/Direction Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                 |            |              |              |      | have 1s written to them are pulled high by the internal pull-ups and can be used as<br>inputs. As inputs, Port 2 pins that are externally pulled low will source current becaus<br>of the internal pull-ups. Port 2 emits the high-order address byte during fetches from<br>external program memory and during accesses to external data memory that use 16<br>bit addresses (MOVX @DPTR).In this application, it uses strong internal pull-ups<br>emitting 1s. During accesses to external data memory that use 8-bit addresses (MOV<br>@Ri), port 2 emits the contents of the P2 SFR. Some Port 2 pins receive the high order<br>address bits during EPROM programming and verification:<br>P2.0 to P2.5 for A8 to A13 |  |  |  |

| P3.0-P3.7       | 10-17      | 11,<br>13-19 | 5,<br>7-13   | I/O  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                 | 10         | 11           | 5            | I    | RXD (P3.0): Serial input port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                 | 11         | 13           | 7            | 0    | TXD (P3.1): Serial output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                 | 12         | 14           | 8            | 1    | INT0 (P3.2): External interrupt 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                 | 13         | 15           | 9            | 1    | INT1 (P3.3): External interrupt 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                 | 14         | 16           | 10           | I    | T0 (P3.4): Timer 0 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                 | 15         | 17           | 11           | I    | T1 (P3.5): Timer 1 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                 | 16         | 18           | 12           | 0    | WR (P3.6): External data memory write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                 | 17         | 19           | 13           | 0    | <b>RD (P3.7):</b> External data memory read strobe<br>P3.4 also receives A14 during TS87C58X2 EPROM Programming.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| Reset           | 9          | 10           | 4            | I    | <b>Reset:</b> A high on this pin for two machine cycles while the oscillator is running, reset the device. An internal diffused resistor to $V_{SS}$ permits a power-on reset using only ar external capacitor to $V_{CC}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

# Table 6-1. CKCON Register CKCON - Clock Control Register (8Fh)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0  |

|---|---|---|---|---|---|---|----|

| - | - | - | - | - | - | - | X2 |

| Bit    | Bit      |                                                                                                                                                                                                                 |

|--------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number | Mnemonic | Description                                                                                                                                                                                                     |

| 7      | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 6      | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 5      | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 4      | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 3      | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 2      | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 1      | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 0      | X2       | <b>CPU and peripheral clock bit</b><br>Clear to select 12 clock periods per machine cycle (STD mode, $F_{OSC}=F_{XTAL}/2$ ).<br>Set to select 6 clock periods per machine cycle (X2 mode, $F_{OSC}=F_{XTAL}$ ). |

Reset Value = XXXX XXX0b Not bit addressable

For further details on the X2 feature, please refer to ANM072 available on the web (http://www.atmel.com)

# 7.1 Application

Software can take advantage of the additional data pointers to both increase speed and reduce code size, for example, block operations (copy, compare, search ...) are well served by using one data pointer as a 'source' pointer and the other one as a "destination" pointer.

#### ASSEMBLY LANGUAGE

| ; Block move using dual data pointers<br>; Destroys DPTR0, DPTR1, A and PSW<br>; note: DPS exits opposite of entry state<br>; unless an extra INC AUXR1 is added |       |              |                            |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------|----------------------------|--|--|--|--|--|

| ,<br>00A2                                                                                                                                                        | AUXR  | 1 EQU 0A2H   |                            |  |  |  |  |  |

| ;                                                                                                                                                                |       |              |                            |  |  |  |  |  |

| 0000 909000                                                                                                                                                      | MOV   | DPTR,#SOURCE | ; address of SOURCE        |  |  |  |  |  |

| 0003 05A2                                                                                                                                                        | INC   | AUXR1        | ; switch data pointers     |  |  |  |  |  |

| 0005 90A000                                                                                                                                                      | MOV   | DPTR,#DEST   | ; address of DEST          |  |  |  |  |  |

| 0008                                                                                                                                                             | LOOP: |              |                            |  |  |  |  |  |

| 0008 05A2                                                                                                                                                        | INC   | AUXR1        | ; switch data pointers     |  |  |  |  |  |

| 000A E0                                                                                                                                                          | MOVX  | A, @DPTR     | ; get a byte from SOURCE   |  |  |  |  |  |

| 000B A3                                                                                                                                                          | INC   | DPTR         | ; increment SOURCE address |  |  |  |  |  |

| 000C 05A2                                                                                                                                                        | INC   | AUXR1        | ; switch data pointers     |  |  |  |  |  |

| 000E F0                                                                                                                                                          | MOVX  | @DPTR,A      | ; write the byte to DEST   |  |  |  |  |  |

| 000F A3                                                                                                                                                          | INC   | DPTR         | ; increment DEST address   |  |  |  |  |  |

| 0010 70F6                                                                                                                                                        | JNZ   | LOOP         | ; check for 0 terminator   |  |  |  |  |  |

| 0012 05A2                                                                                                                                                        | INC   | AUXR1        | ; (optional) restore DPS   |  |  |  |  |  |

INC is a short (2 bytes) and fast (12 clocks) way to manipulate the DPS bit in the AUXR1 SFR. However, note that the INC instruction does not directly force the DPS bit to a particular state, but simply toggles it. In simple routines, such as the block move example, only the fact that DPS is toggled in the proper sequence matters, not its actual value. In other words, the block move routine works the same whether DPS is '0' or '1' on entry. Observe that without the last instruction (INC AUXR1), the routine will exit with DPS in the opposite state.

- AMEL

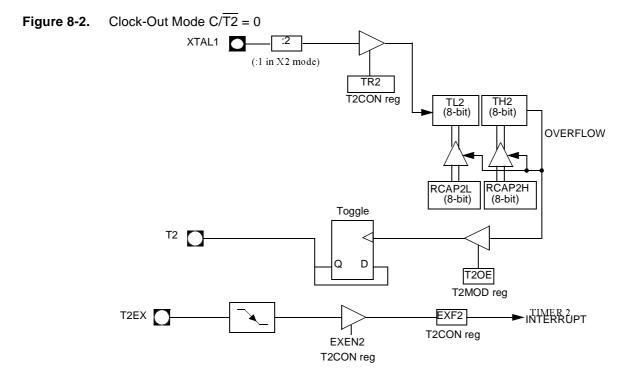

- Enter a 16-bit initial value in timer registers TH2/TL2. It can be the same as the reload value or a different one depending on the application.

- To start the timer, set TR2 run control bit in T2CON register.

It is possible to use timer 2 as a baud rate generator and a clock generator simultaneously. For this configuration, the baud rates and clock frequencies are not independent since both functions use the values in the RCAP2H and RCAP2L registers.

# <sup>16</sup> **AT/TS8xC54/8X2**

# AT/TS8xC54/8X2

| Table 8-1. | T2CON Register |

|------------|----------------|

|------------|----------------|

T2CON - Timer 2 Control Register (C8h)

| 7             | 6               | 6 5 4 3 2 1                                                                                                                                                                                                                          |                                                                                                                                                                                        |                  |                  |               | 0       |  |  |  |

|---------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|---------------|---------|--|--|--|

| TF2           | EXF2            | RCLK                                                                                                                                                                                                                                 | TCLK                                                                                                                                                                                   | EXEN2            | TR2              | C/T2#         | CP/RL2# |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic |                                                                                                                                                                                                                                      | Description                                                                                                                                                                            |                  |                  |               |         |  |  |  |

| 7             | TF2             | Timer 2 overflow<br>Must be cleared b<br>Set by hardware c                                                                                                                                                                           | y software.                                                                                                                                                                            | flow, if RCLK =  | 0 and TCLK =     | 0.            |         |  |  |  |

| 6             | EXF2            | Set when a captur<br>When set, causes<br>enabled.                                                                                                                                                                                    | Must be cleared by software. EXF2 doesn't cause an interrupt in Up/down counter mode                                                                                                   |                  |                  |               |         |  |  |  |

| 5             | RCLK            |                                                                                                                                                                                                                                      | Receive Clock bit<br>Clear to use timer 1 overflow as receive clock for serial port in mode 1 or 3.<br>Set to use timer 2 overflow as receive clock for serial port in mode 1 or 3.    |                  |                  |               |         |  |  |  |

| 4             | TCLK            | Clear to use timer                                                                                                                                                                                                                   | Transmit Clock bit<br>Clear to use timer 1 overflow as transmit clock for serial port in mode 1 or 3.<br>Set to use timer 2 overflow as transmit clock for serial port in mode 1 or 3. |                  |                  |               |         |  |  |  |

| 3             | EXEN2           | Timer 2 External Enable bit<br>Clear to ignore events on T2EX pin for timer 2 operation.<br>Set to cause a capture or reload when a negative transition on T2EX pin is detected, if timer<br>2 is not used to clock the serial port. |                                                                                                                                                                                        |                  |                  |               |         |  |  |  |

| 2             | TR2             | Timer 2 Run control bit<br>Clear to turn off timer 2.<br>Set to turn on timer 2.                                                                                                                                                     |                                                                                                                                                                                        |                  |                  |               |         |  |  |  |

| 1             | C/T2#           | <b>Timer/Counter 2 select bit</b><br>Clear for timer operation (input from internal clock system: F <sub>OSC</sub> ).<br>Set for counter operation (input from T2 input pin, falling edge trigger). Must be 0 for clock<br>out mode. |                                                                                                                                                                                        |                  |                  |               |         |  |  |  |

| 0             | CP/RL2#         | Timer 2 Capture/F<br>If RCLK=1 or TCL<br>overflow.<br>Clear to auto-reloa<br>Set to capture on                                                                                                                                       | K=1, CP/RL2#<br>ad on timer 2 c                                                                                                                                                        | overflows or neg | ative transition | s on T2EX pin |         |  |  |  |

Reset Value = 0000 0000b Bit addressable

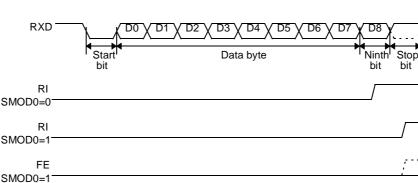

#### Figure 9-3. UART Timings in Modes 2 and 3

## 9.1.1 Automatic Address Recognition

The automatic address recognition feature is enabled when the multiprocessor communication feature is enabled (SM2 bit in SCON register is set).

Implemented in hardware, automatic address recognition enhances the multiprocessor communication feature by allowing the serial port to examine the address of each incoming command frame. Only when the serial port recognizes its own address, the receiver sets RI bit in SCON register to generate an interrupt. This ensures that the CPU is not interrupted by command frames addressed to other devices.

If desired, you may enable the automatic address recognition feature in mode 1. In this configuration, the stop bit takes the place of the ninth data bit. Bit RI is set only when the received command frame address matches the device's address and is terminated by a valid stop bit. To support automatic address recognition, a device is identified by a given address and a broadcast address.

NOTE: The multiprocessor communication and automatic address recognition features cannot be enabled in mode 0 (i.e. setting SM2 bit in SCON register in mode 0 has no effect).

#### 9.1.2 Given Address

Each device has an individual address that is specified in SADDR register; the SADEN register is a mask byte that contains don't-care bits (defined by zeros) to form the device's given address. The don't-care bits provide the flexibility to address one or more slaves at a time. The following example illustrates how a given address is formed.

To address a device by its individual address, the SADEN mask byte must be 1111 1111b. For example:

| SADDR | 0101 0110b        |

|-------|-------------------|

| SADEN | <u>1111 1100b</u> |

| Given | 0101 01XXb        |

| Table 10-4. | IPH Register |

|-------------|--------------|

|             |              |

| IPH - Ir | nterrupt Priority | High Re | gister (B7h) |

|----------|-------------------|---------|--------------|

|          |                   |         |              |

| 7             | 6               | 5                                                                                                                                   | 4                                                                  | 3               | 2                 | 1    | 0    |  |  |  |

|---------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------|-------------------|------|------|--|--|--|

| -             | -               | PT2H                                                                                                                                | PSH                                                                | PT1H            | PX1H              | РТ0Н | PX0H |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic |                                                                                                                                     | Description                                                        |                 |                   |      |      |  |  |  |

| 7             | -               | Reserved<br>The value rea                                                                                                           | d from this bit is ir                                              | ndeterminate. D | o not set this bi | t.   |      |  |  |  |

| 6             | -               | Reserved<br>The value rea                                                                                                           | d from this bit is ir                                              | ndeterminate. D | o not set this bi | t.   |      |  |  |  |

| 5             | PT2H            | Timer 2 overflue           PT2H         PT2           0         0           0         1           1         0           1         1 | ow interrupt Priorit<br><u>Priority Level</u><br>Lowest<br>Highest | y High bit      |                   |      |      |  |  |  |

| 4             | PSH             | Serial port Prid           PSH         PS           0         0           0         1           1         0           1         1   | ority High bit<br><u>Priority Level</u><br>Lowest<br>Highest       |                 |                   |      |      |  |  |  |

| 3             | PT1H            | Timer 1 overflue           PT1H         PT1           0         0           0         1           1         0           1         1 | ow interrupt Priorit<br><u>Priority Level</u><br>Lowest<br>Highest | y High bit      |                   |      |      |  |  |  |

| 2             | PX1H            | External interr<br><u>PX1H</u> <u>PX1</u><br>0 0<br>0 1<br>1 0<br>1 1                                                               | upt 1 Priority High<br><u>Priority Level</u><br>Lowest<br>Highest  | bit             |                   |      |      |  |  |  |

| 1             | РТОН            | Timer 0 overflu           PT0H         PT0           0         0           1         0           1         1                        | ow interrupt Priorit<br><u>Priority Level</u><br>Lowest<br>Highest | y High bit      |                   |      |      |  |  |  |

| 0             | РХОН            | External interr           PX0H         PX0           0         0           1         0           1         1                        | upt 0 Priority High<br><u>Priority Level</u><br>Lowest<br>Highest  | bit             |                   |      |      |  |  |  |

Reset Value = XX00 0000b Not bit addressable

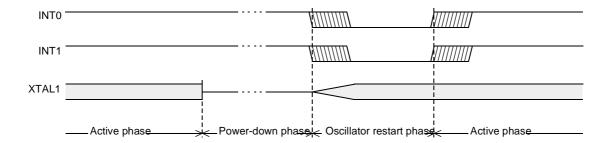

## Figure 11-1. Power-Down Exit Waveform

Exit from power-down by reset redefines all the SFRs, exit from power-down by external interrupt does no affect the SFRs.

Exit from power-down by either reset or external interrupt does not affect the internal RAM content.

NOTE: If idle mode is activated with power-down mode (IDL and PD bits set), the exit sequence is unchanged, when execution is vectored to interrupt, PD and IDL bits are cleared and idle mode is not entered.

| Mode       | Program<br>Memory | ALE | PSEN | PORT0      | PORT1     | PORT2     | PORT3     |

|------------|-------------------|-----|------|------------|-----------|-----------|-----------|

| Idle       | Internal          | 1   | 1    | Port Data* | Port Data | Port Data | Port Data |

| Idle       | External          | 1   | 1    | Floating   | Port Data | Address   | Port Data |

| Power Down | Internal          | 0   | 0    | Port Data* | Port Data | Port Data | Port Data |

| Power Down | External          | 0   | 0    | Floating   | Port Data | Port Data | Port Data |

Table 11-1.

The state of ports during idle and power-down modes

\* Port 0 can force a "zero" level A "one" Level will leave port floating.

| 7             | 6               |                                                | 5                                       | 4                                                       | 3                                                                                                                                                                                                                                                                                                                                            | 2                                                                                                                       | 1                                                                                     | 0 |

|---------------|-----------------|------------------------------------------------|-----------------------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---|

| T4            | Т3              | T3 T2 T1                                       |                                         | ТО                                                      | \$2                                                                                                                                                                                                                                                                                                                                          | S1                                                                                                                      | S0                                                                                    |   |

| Bit<br>Number | Bit<br>Mnemonic |                                                |                                         |                                                         | Descri                                                                                                                                                                                                                                                                                                                                       | ption                                                                                                                   |                                                                                       |   |

| 7             | T4              |                                                |                                         |                                                         |                                                                                                                                                                                                                                                                                                                                              |                                                                                                                         |                                                                                       |   |

| 6             | Т3              |                                                |                                         |                                                         |                                                                                                                                                                                                                                                                                                                                              |                                                                                                                         |                                                                                       |   |

| 5             | T2              | Reserv                                         |                                         | or clear this b                                         | it                                                                                                                                                                                                                                                                                                                                           |                                                                                                                         |                                                                                       |   |

| 4             | T1              | Donot                                          |                                         |                                                         |                                                                                                                                                                                                                                                                                                                                              |                                                                                                                         |                                                                                       |   |

| 3             | T0              |                                                |                                         |                                                         |                                                                                                                                                                                                                                                                                                                                              |                                                                                                                         |                                                                                       |   |

| 2             | S2              | WDT Ti                                         | me-out se                               | elect bit 2                                             |                                                                                                                                                                                                                                                                                                                                              |                                                                                                                         |                                                                                       |   |

| 1             | S1              | WDT Ti                                         | ime-out se                              | elect bit 1                                             |                                                                                                                                                                                                                                                                                                                                              |                                                                                                                         |                                                                                       |   |

| 0             | S0              | WDT Ti                                         | me-out s                                | elect bit 0                                             |                                                                                                                                                                                                                                                                                                                                              |                                                                                                                         |                                                                                       |   |

|               |                 | <u>S2S1</u><br>0<br>0<br>0<br>1<br>1<br>1<br>1 | <u>S0</u><br>0<br>1<br>1<br>0<br>0<br>1 | <u>Selected</u><br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | $\begin{array}{l} \hline \text{Iime-out} \\ (2^{14} - 1) \text{ machir} \\ (2^{15} - 1) \text{ machir} \\ (2^{16} - 1) \text{ machir} \\ (2^{17} - 1) \text{ machir} \\ (2^{18} - 1) \text{ machir} \\ (2^{19} - 1) \text{ machir} \\ (2^{20} - 1) \text{ machir} \\ (2^{21} - 1) \text{ machir} \\ (2^{21} - 1) \text{ machir} \end{array}$ | ne cycles, 32.7 m<br>ne cycles, 65.5 m<br>ne cycles, 131 m<br>ne cycles, 262 m<br>ne cycles, 542 m<br>ne cycles, 1.05 s | ms @ 12 MHz<br>ms @ 12 MHz<br>ns @ 12 MHz<br>ns @ 12 MHz<br>ns @ 12 MHz<br>s @ 12 MHz |   |

#### Table 12-2. WDTPRG Register WDTPRG Address (0A7h)

Reset value XXXX X000

#### 12.1.1 WDT during Power Down and Idle

In Power Down mode the oscillator stops, which means the WDT also stops. While in Power Down mode the user does not need to service the WDT. There are 2 methods of exiting Power Down mode: by a hardware reset or via a level activated external interrupt which is enabled prior to entering Power Down mode. When Power Down is exited with hardware reset, servicing the WDT should occur as it normally should whenever the TS80C54/58X2 is reset. Exiting Power Down with an interrupt is significantly different. The interrupt is held low long enough for the oscillator to stabilize. When the interrupt is brought high, the interrupt is serviced. To prevent the WDT from resetting the device while the interrupt pin is held low, the WDT is not started until the interrupt is pulled high. It is suggested that the WDT be reset during the interrupt service routine.

To ensure that the WDT does not overflow within a few states of exiting of powerdown, it is best to reset the WDT just before entering powerdown.

In the Idle mode, the oscillator continues to run. To prevent the WDT from resetting the TS80C54/58X2 while in Idle mode, the user should always set up a timer that will periodically exit Idle, service the WDT, and re-enter Idle mode.

.

^

# 15. Reduced EMI Mode

Г

The ALE signal is used to demultiplex address and data buses on port 0 when used with external program or data memory. Nevertheless, during internal code execution, ALE signal is still generated. In order to reduce EMI, ALE signal can be disabled by setting AO bit.

The AO bit is located in AUXR register at bit location 0. As soon as AO is set, ALE is no longer output but remains active during MOVX and MOVC instructions and external fetches. During ALE disabling, ALE pin is weakly pulled high.

2 2

| 7             | 6               | 5                                                                               | 4                                                                               | 3                                   | 2                 | 1        | 0  |  |  |  |

|---------------|-----------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------|-------------------|----------|----|--|--|--|

| -             | -               | -                                                                               | -                                                                               | -                                   | -                 | RESERVED | AO |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic |                                                                                 | Description                                                                     |                                     |                   |          |    |  |  |  |

| 7             | -               | <b>Reserved</b><br>The value read                                               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                                     |                   |          |    |  |  |  |

| 6             | -               | Reserved<br>The value read                                                      | eserved<br>ne value read from this bit is indeterminate. Do not set this bit.   |                                     |                   |          |    |  |  |  |

| 5             | -               | Reserved<br>The value read                                                      | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                                     |                   |          |    |  |  |  |

| 4             | -               | Reserved<br>The value read                                                      | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                                     |                   |          |    |  |  |  |

| 3             | -               | Reserved<br>The value read                                                      | d from this bit is                                                              | s indeterminate                     | . Do not set this | s bit.   |    |  |  |  |

| 2             | -               | Reserved<br>The value read                                                      | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                                     |                   |          |    |  |  |  |

| 1             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                                                                                 |                                     |                   |          |    |  |  |  |

| 0             | AO              |                                                                                 | e ALE operatio                                                                  | n during interna<br>during internal |                   |          |    |  |  |  |

Table 15-1.AUXR Register

AUXR - Auxiliary Register (8Eh)

Reset Value = XXXX XXX0b Not bit addressable

# 17. TS87C54/58X2 EPROM

# 17.1 EPROM Structure

The TS87C54/58X2 EPROM is divided in two different arrays:

- the code array:16/32 Kbytes.

- the encryption array:64 bytes.

- In addition a third non programmable array is implemented:

- the signature array: 4 bytes.

# 17.2 EPROM Lock System

The program Lock system, when programmed, protects the on-chip program against software piracy.

### 17.2.1 Encryption Array

Within the EPROM array are 64 bytes of encryption array that are initially unprogrammed (all FF's). Every time a byte is addressed during program verify, 6 address lines are used to select a byte of the encryption array. This byte is then exclusive-NOR'ed (XNOR) with the code byte, creating an encrypted verify byte. The algorithm, with the encryption array in the unprogrammed state, will return the code in its original, unmodified form.

When using the encryption array, one important factor needs to be considered. If a byte has the value FFh, verifying the byte will produce the encryption byte value. If a large block (>64 bytes) of code is left unprogrammed, a verification routine will display the content of the encryption array. For this reason all the unused code bytes should be programmed with random values. This will ensure program protection.

# 17.2.2 Program Lock Bits

The three lock bits, when programmed according to Table 17-1., will provide different level of protection for the on-chip code and data.

| F                 | Program Lo | ock Bits |     |                                                                                                                                                                                                                       |

|-------------------|------------|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Security<br>level |            |          | LB3 | Protection Description                                                                                                                                                                                                |

| 1                 | U          | U        | U   | No program lock features enabled. Code verify will still be encrypted by the encryption array if programmed. MOVC instruction executed from external program memory returns non encrypted data.                       |

| 2                 | Р          | U        | U   | MOVC instruction executed from external program memory are disabled from fetching code bytes from internal memory, $\overline{EA}$ is sampled and latched on reset, and further programming of the EPROM is disabled. |

| 3                 | U          | Р        | U   | Same as 2, also verify is disabled.                                                                                                                                                                                   |

| 4                 | U          | U        | Р   | Same as 3, also external execution is disabled.                                                                                                                                                                       |

Table 17-1.Program Lock bits

U: unprogrammed,

P: programmed

WARNING: Security level 2 and 3 should only be programmed after EPROM and Core verification.

- 5. Typicals are based on a limited number of samples and are not guaranteed. The values listed are at room temperature and 5V.

- Under steady state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows: Maximum I<sub>OL</sub> per port pin: 10 mA Maximum I<sub>OL</sub> per 8-bit port: Port 0: 26 mA Ports 1, 2 and 3: 15 mA Maximum total I<sub>OL</sub> for all output pins: 71 mA If I<sub>OL</sub> exceeds the test condition, V<sub>OL</sub> may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

- 7. For other values, please contact your sales office.

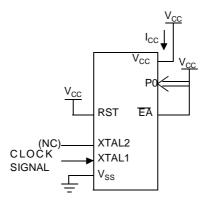

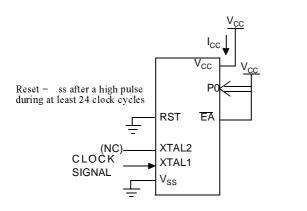

- Operating I<sub>CC</sub> is measured with all output pins disconnected; XTAL1 driven with T<sub>CLCH</sub>, T<sub>CHCL</sub> = 5 ns (see Figure 19-5.), V<sub>IL</sub> = V<sub>SS</sub> + 0.5 V,

$V_{IH} = V_{CC} - 0.5V$ ; XTAL2 N.C.;  $\overline{EA} = Port 0 = V_{CC}$ ; RST =  $V_{SS}$ . The internal ROM runs the code 80 FE (label: SJMP label).  $I_{CC}$  would be slightly higher if a crystal oscillator is used. Measurements are made with OTP products when possible, which is the worst case.

All other pins are disconnected.

All other pins are disconnected.

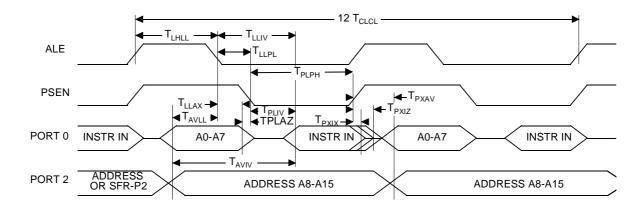

# 19.5.2 External Program Memory Characteristics

# Table 19-5. Symbol Description

| Symbol            | Parameter                         |

|-------------------|-----------------------------------|

| Т                 | Oscillator clock period           |

| T <sub>LHLL</sub> | ALE pulse width                   |

| T <sub>AVLL</sub> | Address Valid to ALE              |

| T <sub>LLAX</sub> | Address Hold After ALE            |

| T <sub>LLIV</sub> | ALE to Valid Instruction In       |

| T <sub>LLPL</sub> | ALE to PSEN                       |

| T <sub>PLPH</sub> | PSEN Pulse Width                  |

| T <sub>PLIV</sub> | PSEN to Valid Instruction In      |

| T <sub>PXIX</sub> | Input Instruction Hold After PSEN |

| T <sub>PXIZ</sub> | Input Instruction FloatAfter PSEN |

| T <sub>PXAV</sub> | PSEN to Address Valid             |

| T <sub>AVIV</sub> | Address to Valid Instruction In   |

| T <sub>PLAZ</sub> | PSEN Low to Address Float         |

Table 19-6.

AC Parameters for Fix Clock

| Speed             |     | M<br>MHz | X2 r<br>30 | V<br>node<br>MHz<br>z equiv. | standard | V<br>I mode 40<br>Hz | X2 n<br>20 | L<br>node<br>MHz<br>z equiv. | standa | L<br>′d mode<br>MHz | Units |

|-------------------|-----|----------|------------|------------------------------|----------|----------------------|------------|------------------------------|--------|---------------------|-------|

| Symbol            | Min | Max      | Min        | Max                          | Min      | Max                  | Min        | Max                          | Min    | Max                 |       |

| Т                 | 25  |          | 33         |                              | 25       |                      | 50         |                              | 33     |                     | ns    |

| T <sub>LHLL</sub> | 40  |          | 25         |                              | 42       |                      | 35         |                              | 52     |                     | ns    |

| T <sub>AVLL</sub> | 10  |          | 4          |                              | 12       |                      | 5          |                              | 13     |                     | ns    |

| T <sub>LLAX</sub> | 10  |          | 4          |                              | 12       |                      | 5          |                              | 13     |                     | ns    |

| T <sub>LLIV</sub> |     | 70       |            | 45                           | l l      | 78                   |            | 65                           |        | 98                  | ns    |

| T <sub>LLPL</sub> | 15  |          | 9          |                              | 17       |                      | 10         |                              | 18     |                     | ns    |

| T <sub>PLPH</sub> | 55  |          | 35         |                              | 60       |                      | 50         |                              | 75     |                     | ns    |

| T <sub>PLIV</sub> |     | 35       |            | 25                           | l l      | 50                   |            | 30                           |        | 55                  | ns    |

| T <sub>PXIX</sub> | 0   |          | 0          |                              | 0        |                      | 0          |                              | 0      |                     | ns    |

| T <sub>PXIZ</sub> |     | 18       |            | 12                           | l l      | 20                   |            | 10                           |        | 18                  | ns    |

| T <sub>AVIV</sub> |     | 85       |            | 53                           |          | 95                   |            | 80                           |        | 122                 | ns    |

| T <sub>PLAZ</sub> |     | 10       |            | 10                           |          | 10                   |            | 10                           |        | 10                  | ns    |

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | -М | -V | -L | Units |

|-------------------|------|-------------------|-----------|----|----|----|-------|

| T <sub>LHLL</sub> | Min  | 2 T - x           | T - x     | 10 | 8  | 15 | ns    |

| T <sub>AVLL</sub> | Min  | T - x             | 0.5 T - x | 15 | 13 | 20 | ns    |

| T <sub>LLAX</sub> | Min  | T - x             | 0.5 T - x | 15 | 13 | 20 | ns    |

| T <sub>LLIV</sub> | Max  | 4 T - x           | 2 T - x   | 30 | 22 | 35 | ns    |

| T <sub>LLPL</sub> | Min  | T - x             | 0.5 T - x | 10 | 8  | 15 | ns    |

| T <sub>PLPH</sub> | Min  | 3 T - x           | 1.5 T - x | 20 | 15 | 25 | ns    |

| T <sub>PLIV</sub> | Max  | 3 T - x           | 1.5 T - x | 40 | 25 | 45 | ns    |

| T <sub>PXIX</sub> | Min  | х                 | х         | 0  | 0  | 0  | ns    |

| T <sub>PXIZ</sub> | Max  | T - x             | 0.5 T - x | 7  | 5  | 15 | ns    |

| T <sub>AVIV</sub> | Max  | 5 T - x           | 2.5 T - x | 40 | 30 | 45 | ns    |

| T <sub>PLAZ</sub> | Max  | х                 | х         | 10 | 10 | 10 | ns    |

Table 19-7. AC Parameters for a Variable Clock: derating formula

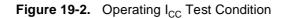

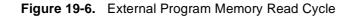

# 19.5.3 External Program Memory Read Cycle

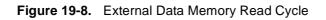

# 19.5.4 External Data Memory Characteristics

Table 19-8.

Symbol Description

| Symbol            | Parameter                   |

|-------------------|-----------------------------|

| T <sub>RLRH</sub> | RD Pulse Width              |

| T <sub>WLWH</sub> | WR Pulse Width              |

| T <sub>RLDV</sub> | RD to Valid Data In         |

| T <sub>RHDX</sub> | Data Hold After RD          |

| T <sub>RHDZ</sub> | Data Float After RD         |

| T <sub>LLDV</sub> | ALE to Valid Data In        |

| T <sub>AVDV</sub> | Address to Valid Data In    |

| T <sub>LLWL</sub> | ALE to WR or RD             |

| T <sub>AVWL</sub> | Address to WR or RD         |

| T <sub>QVWX</sub> | Data Valid to WR Transition |

| T <sub>QVWH</sub> | Data set-up to WR High      |

| T <sub>WHQX</sub> | Data Hold After WR          |

| T <sub>RLAZ</sub> | RD Low to Address Float     |

| T <sub>WHLH</sub> | RD or WR High to ALE high   |

## Table 19-9. AC Parameters for a Fix Clock

| Speed             |     | M<br>MHz | X2 r<br>30 | V<br>node<br>MHz<br>z equiv. | standard | V<br>I mode 40<br>Hz | X2 r<br>20 | ·L<br>node<br>MHz<br>z equiv. | standa | ·L<br>rd mode<br>MHz | Units |

|-------------------|-----|----------|------------|------------------------------|----------|----------------------|------------|-------------------------------|--------|----------------------|-------|

| Symbol            | Min | Max      | Min        | Max                          | Min      | Max                  | Min        | Max                           | Min    | Max                  |       |

| T <sub>RLRH</sub> | 130 |          | 85         |                              | 135      |                      | 125        |                               | 175    |                      | ns    |

| T <sub>WLWH</sub> | 130 |          | 85         |                              | 135      |                      | 125        |                               | 175    |                      | ns    |

| T <sub>RLDV</sub> |     | 100      | 1          | 60                           |          | 102                  |            | 95                            |        | 137                  | ns    |

| T <sub>RHDX</sub> | 0   | 1        | 0          | 1                            | 0        |                      | 0          | l l                           | 0      |                      | ns    |

| T <sub>RHDZ</sub> |     | 30       |            | 18                           |          | 35                   |            | 25                            |        | 42                   | ns    |

| T <sub>LLDV</sub> |     | 160      |            | 98                           |          | 165                  |            | 155                           |        | 222                  | ns    |

| T <sub>AVDV</sub> |     | 165      | 1          | 100                          |          | 175                  |            | 160                           |        | 235                  | ns    |

| T <sub>LLWL</sub> | 50  | 100      | 30         | 70                           | 55       | 95                   | 45         | 105                           | 70     | 130                  | ns    |

| T <sub>AVWL</sub> | 75  | 1        | 47         | 1                            | 80       |                      | 70         | l l                           | 103    |                      | ns    |

| T <sub>QVWX</sub> | 10  | 1        | 7          | 1                            | 15       |                      | 5          | l l                           | 13     |                      | ns    |

| T <sub>QVWH</sub> | 160 |          | 107        |                              | 165      |                      | 155        |                               | 213    |                      | ns    |

| T <sub>WHQX</sub> | 15  |          | 9          |                              | 17       |                      | 10         |                               | 18     |                      | ns    |

| T <sub>RLAZ</sub> |     | 0        | 1          | 0                            |          | 0                    |            | 0                             |        | 0                    | ns    |

| T <sub>WHLH</sub> | 10  | 40       | 7          | 27                           | 15       | 35                   | 5          | 45                            | 13     | 53                   | ns    |

# 19.5.6 External Data Memory Read Cycle

# 19.5.7 Serial Port Timing - Shift Register Mode Table 19-11. Symbol Description

| Symbol            | Parameter                                |

|-------------------|------------------------------------------|

| T <sub>XLXL</sub> | Serial port clock cycle time             |

| T <sub>QVHX</sub> | Output data set-up to clock rising edge  |

| T <sub>XHQX</sub> | Output data hold after clock rising edge |

| T <sub>XHDX</sub> | Input data hold after clock rising edge  |

| T <sub>XHDV</sub> | Clock rising edge to input data valid    |

Table 19-12. AC Parameters for a Fix Clock

| Speed             |     | M<br>MHz | X2 n<br>30 l | V<br>node<br>MHz<br>z equiv. | standard | V<br>mode 40<br>Hz | 20 1 | L<br>node<br>MHz<br>z equiv. | standar | L<br>d mode<br>MHz | Units |

|-------------------|-----|----------|--------------|------------------------------|----------|--------------------|------|------------------------------|---------|--------------------|-------|

| Symbol            | Min | Max      | Min          | Max                          | Min      | Max                | Min  | Max                          | Min     | Max                |       |

| T <sub>XLXL</sub> | 300 |          | 200          |                              | 300      |                    | 300  |                              | 400     |                    | ns    |

| T <sub>QVHX</sub> | 200 |          | 117          |                              | 200      |                    | 200  |                              | 283     |                    | ns    |

| T <sub>XHQX</sub> | 30  |          | 13           |                              | 30       |                    | 30   |                              | 47      |                    | ns    |

| T <sub>XHDX</sub> | 0   |          | 0            |                              | 0        |                    | 0    |                              | 0       |                    | ns    |

| $T_{XHDV}$        |     | 117      |              | 34                           |          | 117                |      | 117                          |         | 200                | ns    |

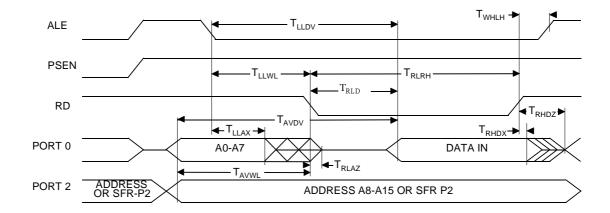

# **19.5.11** External Clock Drive Characteristics (XTAL1)

# Table 19-15.AC Parameters

| Symbol                               | Parameter               | Min | Мах | Units |

|--------------------------------------|-------------------------|-----|-----|-------|

| T <sub>CLCL</sub>                    | Oscillator Period       | 25  |     | ns    |

| T <sub>CHCX</sub>                    | High Time               | 5   |     | ns    |

| T <sub>CLCX</sub>                    | Low Time                | 5   |     | ns    |

| T <sub>CLCH</sub>                    | Rise Time               |     | 5   | ns    |

| T <sub>CHCL</sub>                    | Fall Time               |     | 5   | ns    |

| T <sub>CHCX</sub> /T <sub>CLCX</sub> | Cyclic ratio in X2 mode | 40  | 60  | %     |

#### 19.5.12 External Clock Drive Waveforms

Figure 19-11. External Clock Drive Waveforms

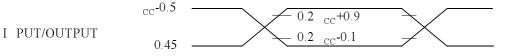

### 19.5.13 AC Testing Input/Output Waveforms

#### Figure 19-12. AC Testing Input/Output Waveforms

AC inputs during testing are driven at V<sub>CC</sub> - 0.5 for a logic "1" and 0.45V for a logic "0". Timing measurement are made at V<sub>IH</sub> min for a logic "1" and V<sub>IL</sub> max for a logic "0".

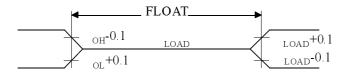

# 19.5.14 Float Waveforms

#### Figure 19-13. Float Waveforms

For timing purposes a port pin is no longer floating when a 100 mV change from load voltage occurs and begins to float when a 100 mV change from the loaded  $V_{OH}/V_{OL}$  level occurs.  $I_{OL}/I_{OH} \ge \pm 20$ mA.

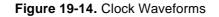

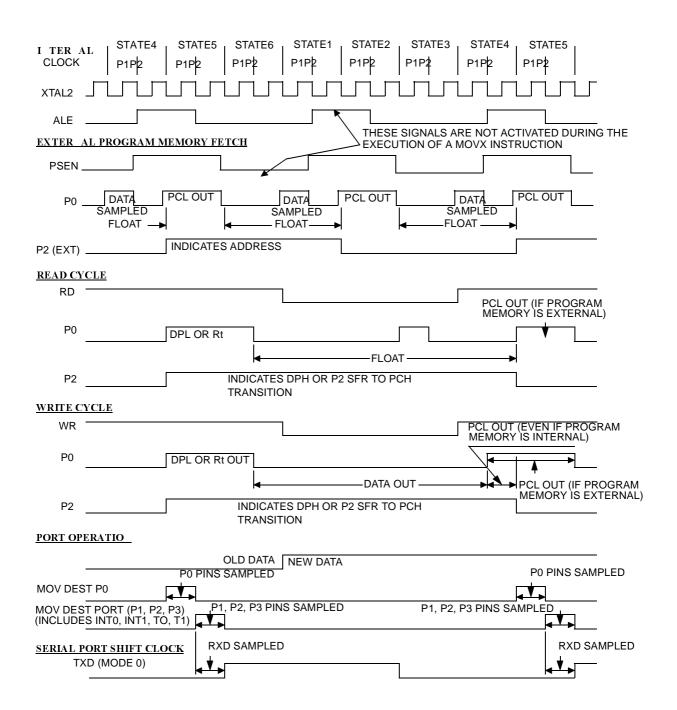

#### 19.5.15 Clock Waveforms

Valid in normal clock mode. In X2 mode XTAL2 signal must be changed to XTAL2 divided by two.

This diagram indicates when signals are clocked internally. The time it takes the signals to propagate to the pins, however, ranges from 25 to 125 ns. This propagation delay is dependent on variables such as temperature and pin loading. Propagation also varies from output to output and component. Typically though ( $T_A=25^{\circ}C$  fully loaded) RD and WR propagation delays are approximately 50ns. The other signals are typically 85 ns. Propagation delays are incorporated in the AC specifications.

# AT/TS8xC54/8X2

| Part Number     | Supply Voltage | Temperature Range  | Package | Packing |

|-----------------|----------------|--------------------|---------|---------|

| TS87C54X2-MCC   | 5V ±10%        | Commercial         | PQFP44  | Tray    |

| TS87C54X2-MCE   | 5V ±10%        | Commercial         | VQFP44  | Tray    |

| TS87C54X2-VCA   | 5V ±10%        | Commercial         | PDIL40  | Stick   |

| TS87C54X2-VCB   | 5V ±10%        | Commercial         | PLCC44  | Stick   |

| TS87C54X2-VCC   | 5V ±10%        | Commercial         | PQFP44  | Tray    |

| TS87C54X2-VCE   | 5V ±10%        | Commercial         | VQFP44  | Tray    |

| TS87C54X2-LCA   | 2.7 to 5.5V    | Commercial         | PDIL40  | Stick   |

| TS87C54X2-LCB   | 2.7 to 5.5V    | Commercial         | PLCC44  | Stick   |

| TS87C54X2-LCC   | 2.7 to 5.5V    | Commercial         | PQFP44  | Tray    |

| TS87C54X2-LCE   | 2.7 to 5.5V    | Commercial         | VQFP44  | Tray    |

| TS87C54X2-MIA   | 5V ±10%        | Industrial         | PDIL40  | Stick   |

| TS87C54X2-MIB   | 5V ±10%        | Industrial         | PLCC44  | Stick   |

| TS87C54X2-MIC   | 5V ±10%        | Industrial         | PQFP44  | Tray    |

| TS87C54X2-MIE   | 5V ±10%        | Industrial         | VQFP44  | Tray    |

| TS87C54X2-VIA   | 5V ±10%        | Industrial         | PDIL40  | Stick   |

| TS87C54X2-VIB   | 5V ±10%        | Industrial         | PLCC44  | Stick   |

| TS87C54X2-VIC   | 5V ±10%        | Industrial         | PQFP44  | Tray    |

| TS87C54X2-VIE   | 5V ±10%        | Industrial         | VQFP44  | Tray    |

| TS87C54X2-LIA   | 2.7 to 5.5V    | Industrial         | PDIL40  | Stick   |

| TS87C54X2-LIB   | 2.7 to 5.5V    | Industrial         | PLCC44  | Stick   |

| TS87C54X2-LIC   | 2.7 to 5.5V    | Industrial         | PQFP44  | Tray    |

| TS87C54X2-LIE   | 2.7 to 5.5V    | Industrial         | VQFP44  | Tray    |

|                 |                |                    |         |         |

| AT87C54X2-3CSUM | 5V ±10%        | Industrial & Green | PDIL40  | Stick   |

| AT87C54X2-SLSUM | 5V ±10%        | Industrial & Green | PLCC44  | Stick   |

| AT87C54X2-RLTUM | 5V ±10%        | Industrial & Green | VQFP44  | Tray    |

| AT87C54X2-3CSUL | 2.7 to 5.5V    | Industrial & Green | PDIL40  | Stick   |

| AT87C54X2-SLSUL | 2.7 to 5.5V    | Industrial & Green | PLCC44  | Stick   |

| AT87C54X2-RLTUL | 2.7 to 5.5V    | Industrial & Green | VQFP44  | Tray    |

| AT87C54X2-3CSUV | 5V ±10%        | Industrial & Green | PDIL40  | Stick   |

| AT87C54X2-SLSUV | 5V ±10%        | Industrial & Green | PLCC44  | Stick   |

| AT87C54X2-RLTUV | 5V ±10%        | Industrial & Green | VQFP44  | Tray    |