Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                            |

|----------------------------|------------------------------------------------------------|

| Product Status             | Obsolete                                                   |

| Core Processor             | 80C51                                                      |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 30/20MHz                                                   |

| Connectivity               | UART/USART                                                 |

| Peripherals                | POR, WDT                                                   |

| Number of I/O              | 32                                                         |

| Program Memory Size        | 32KB (32K x 8)                                             |

| Program Memory Type        | ОТР                                                        |

| EEPROM Size                | -                                                          |

| RAM Size                   | 256 x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                |

| Data Converters            | -                                                          |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                          |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 44-LQFP                                                    |

| Supplier Device Package    | 44-VQFP (10x10)                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/at87c58x2-rltul |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

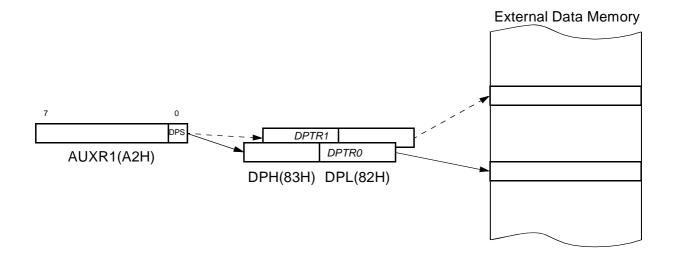

# 7. Dual Data Pointer Register Ddptr

The additional data pointer can be used to speed up code execution and reduce code size in a number of ways.

The dual DPTR structure is a way by which the chip will specify the address of an external data memory location. There are two 16-bit DPTR registers that address the external memory, and a single bit called

DPS = AUXR1/bit0 (See Table 7-1.) that allows the program code to switch between them (Refer to Figure 7-1).

Figure 7-1. Use of Dual Pointer

Table 7-1. AUXR1: Auxiliary Register 1

| 7 | 6 | 5 | 4 | 3   | 2 | 1 | 0   |

|---|---|---|---|-----|---|---|-----|

| - | - | - | - | GF3 | 0 | - | DPS |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                  |

|---------------|-----------------|------------------------------------------------------------------------------|

| 7             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit. |

| 6             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit. |

| 5             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit. |

| 4             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit. |

| 3             | GF3             | This bit is a general purpose user flag                                      |

| 2             | 0               | Reserved Always stuck at 0.                                                  |

| 1             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit. |

| 0             | DPS             | Data Pointer Selection Clear to select DPTR0. Set to select DPTR1.           |

Reset Value = XXXX 00X0 Not bit addressable

User software should not write 1s to reserved bits. These bits may be used in future 8051 family products to invoke new feature. In that case, the reset value of the new bit will be 0, and its active value will be 1. The value read from a reserved bit is indeterminate.

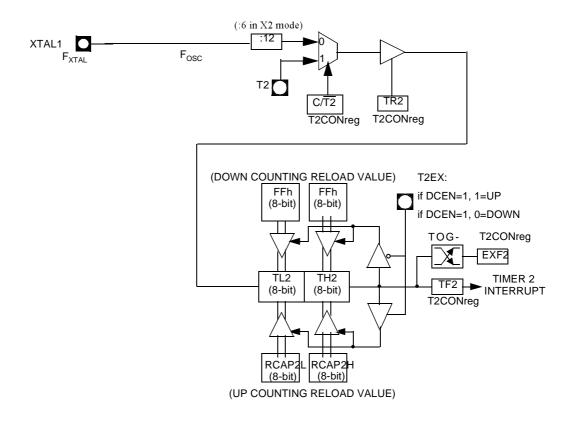

Figure 8-1. Auto-Reload Mode Up/Down Counter (DCEN = 1)

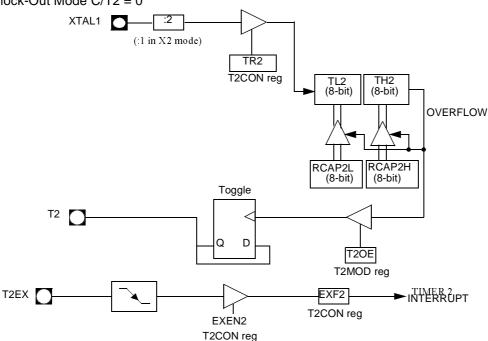

## 8.1.1 Programmable Clock-Output

In the clock-out mode, timer 2 operates as a 50%-duty-cycle, programmable clock generator (See Figure 8-2) . The input clock increments TL2 at frequency  $F_{\rm OSC}/2$ . The timer repeatedly counts to overflow from a loaded value. At overflow, the contents of RCAP2H and RCAP2L registers are loaded into TH2 and TL2. In this mode, timer 2 overflows do not generate interrupts. The formula gives the clock-out frequency as a function of the system oscillator frequency and the value in the RCAP2H and RCAP2L registers :

$$Clock - OutFrequency = \frac{F_{osc}}{4 \times (65536 - RCAP2H/RCAP2L)}$$

For a 16 MHz system clock, timer 2 has a programmable frequency range of 61 Hz  $(F_{OSC}/2^{16})$  to 4 MHz  $(F_{OSC}/4)$ . The generated clock signal is brought out to T2 pin (P1.0).

Timer 2 is programmed for the clock-out mode as follows:

- Set T2OE bit in T2MOD register.

- Clear C/T2 bit in T2CON register.

- Determine the 16-bit reload value from the formula and enter it in RCAP2H/RCAP2L registers.

- Enter a 16-bit initial value in timer registers TH2/TL2. It can be the same as the reload value or a different one depending on the application.

- To start the timer, set TR2 run control bit in T2CON register.

It is possible to use timer 2 as a baud rate generator and a clock generator simultaneously. For this configuration, the baud rates and clock frequencies are not independent since both functions use the values in the RCAP2H and RCAP2L registers.

Figure 8-2. Clock-Out Mode  $C/\overline{T2} = 0$

Table 8-1.T2CON Register

T2CON - Timer 2 Control Register (C8h)

| 7   | 6    | 5    | 4    | 3     | 2   | 1     | 0       |

|-----|------|------|------|-------|-----|-------|---------|

| TF2 | EXF2 | RCLK | TCLK | EXEN2 | TR2 | C/T2# | CP/RL2# |

| Bit    | Bit      |                                                                                                                                                                                                                                                                                                                    |

|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number | Mnemonic | Description                                                                                                                                                                                                                                                                                                        |

| 7      | TF2      | Timer 2 overflow Flag  Must be cleared by software.  Set by hardware on timer 2 overflow, if RCLK = 0 and TCLK = 0.                                                                                                                                                                                                |

| 6      | EXF2     | Timer 2 External Flag Set when a capture or a reload is caused by a negative transition on T2EX pin if EXEN2=1. When set, causes the CPU to vector to timer 2 interrupt routine when timer 2 interrupt is enabled. Must be cleared by software. EXF2 doesn't cause an interrupt in Up/down counter mode (DCEN = 1) |

| 5      | RCLK     | Receive Clock bit Clear to use timer 1 overflow as receive clock for serial port in mode 1 or 3. Set to use timer 2 overflow as receive clock for serial port in mode 1 or 3.                                                                                                                                      |

| 4      | TCLK     | Transmit Clock bit Clear to use timer 1 overflow as transmit clock for serial port in mode 1 or 3. Set to use timer 2 overflow as transmit clock for serial port in mode 1 or 3.                                                                                                                                   |

| 3      | EXEN2    | Timer 2 External Enable bit Clear to ignore events on T2EX pin for timer 2 operation. Set to cause a capture or reload when a negative transition on T2EX pin is detected, if timer 2 is not used to clock the serial port.                                                                                        |

| 2      | TR2      | Timer 2 Run control bit Clear to turn off timer 2. Set to turn on timer 2.                                                                                                                                                                                                                                         |

| 1      | C/T2#    | Timer/Counter 2 select bit Clear for timer operation (input from internal clock system: F <sub>OSC</sub> ). Set for counter operation (input from T2 input pin, falling edge trigger). Must be 0 for clock out mode.                                                                                               |

| 0      | CP/RL2#  | Timer 2 Capture/Reload bit  If RCLK=1 or TCLK=1, CP/RL2# is ignored and timer is forced to auto-reload on timer 2 overflow.  Clear to auto-reload on timer 2 overflows or negative transitions on T2EX pin if EXEN2=1.  Set to capture on negative transitions on T2EX pin if EXEN2=1.                             |

Reset Value = 0000 0000b

Bit addressable

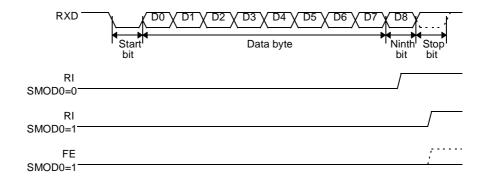

Figure 9-3. UART Timings in Modes 2 and 3

### 9.1.1 Automatic Address Recognition

The automatic address recognition feature is enabled when the multiprocessor communication feature is enabled (SM2 bit in SCON register is set).

Implemented in hardware, automatic address recognition enhances the multiprocessor communication feature by allowing the serial port to examine the address of each incoming command frame. Only when the serial port recognizes its own address, the receiver sets RI bit in SCON register to generate an interrupt. This ensures that the CPU is not interrupted by command frames addressed to other devices.

If desired, you may enable the automatic address recognition feature in mode 1. In this configuration, the stop bit takes the place of the ninth data bit. Bit RI is set only when the received command frame address matches the device's address and is terminated by a valid stop bit.

To support automatic address recognition, a device is identified by a given address and a broadcast address.

NOTE: The multiprocessor communication and automatic address recognition features cannot be enabled in mode 0 (i.e. setting SM2 bit in SCON register in mode 0 has no effect).

#### 9.1.2 Given Address

Each device has an individual address that is specified in SADDR register; the SADEN register is a mask byte that contains don't-care bits (defined by zeros) to form the device's given address. The don't-care bits provide the flexibility to address one or more slaves at a time. The following example illustrates how a given address is formed.

To address a device by its individual address, the SADEN mask byte must be 1111 1111b. For example:

| SADDR | 0101 | 0110b |

|-------|------|-------|

| SADEN | 1111 | 1100b |

| Given | 0101 | 01XXb |

The following is an example of how to use given addresses to address different slaves:

| Slave A: | SADDR<br><u>SADEN</u><br>Given | 1111 0001b<br>1111 1010b<br>1111 0X0Xb |

|----------|--------------------------------|----------------------------------------|

| Slave B: | SADDR<br><u>SADEN</u><br>Given | 1111 0011b<br>1111 1001b<br>1111 0XX1b |

| Slave C: | SADDR<br><u>SADEN</u><br>Given | 1111 0010b<br>1111 1101b<br>1111 00X1b |

The SADEN byte is selected so that each slave may be addressed separately.

For slave A, bit 0 (the LSB) is a don't-care bit; for slaves B and C, bit 0 is a 1. To communicate with slave A only, the master must send an address where bit 0 is clear (e.g. 1111 0000b). For slave A, bit 1 is a 1; for slaves B and C, bit 1 is a don't care bit. To communicate with slaves B and C, but not slave A, the master must send an address with bits 0 and 1 both set (e.g. 1111 0011b).

To communicate with slaves A, B and C, the master must send an address with bit 0 set, bit 1 clear, and bit 2 clear (e.g. 1111 0001b).

#### 9.1.3 Broadcast Address

A broadcast address is formed from the logical OR of the SADDR and SADEN registers with zeros defined as don't-care bits, e.g.:

| SA            | DDR          | 0101 | 0110b |

|---------------|--------------|------|-------|

| SA            | DEN          | 1111 | 1100b |

| Broadcast =SA | DDR OR SADEN | 1111 | 111Xb |

The use of don't-care bits provides flexibility in defining the broadcast address, however in most applications, a broadcast address is FFh. The following is an example of using broadcast addresses:

| Slave A: | SADDR<br><u>SADEN</u><br>Broadcast  | 1111 0001b<br>1111 1010b<br>1111 1X11b, |

|----------|-------------------------------------|-----------------------------------------|

| Slave B: | SADDR<br><u>SADEN</u><br>Broadcast  | 1111 0011b<br>1111 1001b<br>1111 1X11B, |

| Slave C: | SADDR=<br><u>SADEN</u><br>Broadcast | 1111 0010b<br>1111 1101b<br>1111 1111b  |

For slaves A and B, bit 2 is a don't care bit; for slave C, bit 2 is set. To communicate with all of the slaves, the master must send an address FFh. To communicate with slaves A and B, but not slave C, the master can send and address FBh.

#### 9.1.4 Reset Addresses

On reset, the SADDR and SADEN registers are initialized to 00h, i.e. the given and broadcast addresses are xxxx xxxxb (all don't-care bits). This ensures that the serial port will reply to any address, and so, that it is backwards compatible with the 80C51 microcontrollers that do not support automatic address recognition.

Table 9-1.

SADEN - Slave Address Mask Register (B9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

**Table 9-2.** SADDR - Slave Address Register (A9h)

| ĺ | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

## Table 9-4.PCON Register

Table 9-5.

PCON - Power Control Register (87h)

| 7     | 6     | 5 | 4   | 3   | 2   | 1  | 0   |

|-------|-------|---|-----|-----|-----|----|-----|

| SMOD1 | SMOD0 | - | POF | GF1 | GF0 | PD | IDL |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                   |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 7             | SMOD1           | Serial port Mode bit 1 Set to select double baud rate in mode 1, 2 or 3.                                                                      |

| 6             | SMOD0           | Serial port Mode bit 0 Clear to select SM0 bit in SCON register. Set to to select FE bit in SCON register.                                    |

| 5             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                                                                  |

| 4             | POF             | Power-Off Flag Clear to recognize next reset type. Set by hardware when VCC rises from 0 to its nominal voltage. Can also be set by software. |

| 3             | GF1             | General purpose Flag Cleared by user for general purpose usage. Set by user for general purpose usage.                                        |

| 2             | GF0             | General purpose Flag Cleared by user for general purpose usage. Set by user for general purpose usage.                                        |

| 1             | PD              | Power-Down mode bit Cleared by hardware when reset occurs. Set to enter power-down mode.                                                      |

| 0             | IDL             | Idle mode bit Clear by hardware when interrupt or reset occurs. Set to enter idle mode.                                                       |

Reset Value = 00X1 0000b

Not bit addressable

Power-off flag reset value will be 1 only after a power on (cold reset). A warm reset doesn't affect the value of this bit.

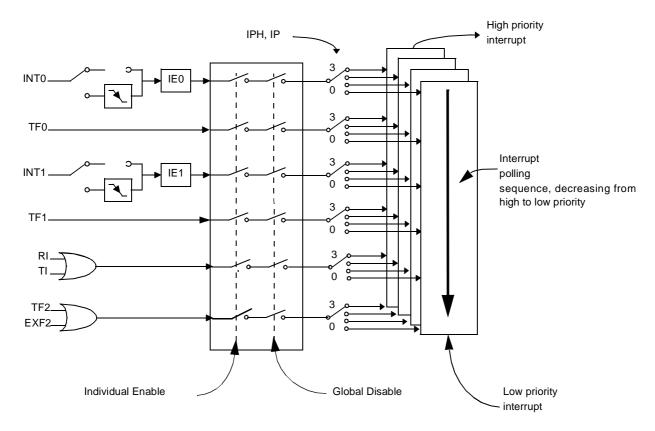

## 10. Interrupt System

The TS80C54/58X2 has a total of 7 interrupt vectors: two external interrupts (INT0 and INT1), three timer interrupts (timers 0, 1 and 2) and the serial port interrupt. These interrupts are shown in Figure 10-1.

Figure 10-1. Interrupt Control System

Each of the interrupt sources can be individually enabled or disabled by setting or clearing a bit in the Interrupt Enable register (See Table 10-2.). This register also contains a global disable bit, which must be cleared to disable all interrupts at once.

Each interrupt source can also be individually programmed to one out of four priority levels by setting or clearing a bit in the Interrupt Priority register (See Table 10-3.) and in the Interrupt Priority High register (See Table 10-4.). shows the bit values and priority levels associated with each combination.

Table 10-1. Priority Level Bit Values

| IPH.x | IP.x | Interrupt Level Priority |

|-------|------|--------------------------|

| 0     | 0    | 0 (Lowest)               |

| 0     | 1    | 1                        |

| 1     | 0    | 2                        |

| 1     | 1    | 3 (Highest)              |

A low-priority interrupt can be interrupted by a high priority interrupt, but not by another low-priority interrupt. A high-priority interrupt can't be interrupted by any other interrupt source.

If two interrupt requests of different priority levels are received simultaneously, the request of higher priority level is serviced. If interrupt requests of the same priority level are received simultaneously, an internal polling sequence determines which request is serviced. Thus within each priority level there is a second priority structure determined by the polling sequence.

Table 10-2. IE Register

IE - Interrupt Enable Register (A8h)

| 7  | 6 | 5   | 4  | 3   | 2   | 1   | 0   |

|----|---|-----|----|-----|-----|-----|-----|

| EA | - | ET2 | ES | ET1 | EX1 | ET0 | EX0 |

| Bit    | Bit      |                                                                                                                                                                                                                 |  |  |  |  |  |

|--------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|        |          | <b>5</b>                                                                                                                                                                                                        |  |  |  |  |  |

| Number | Mnemonic | Description                                                                                                                                                                                                     |  |  |  |  |  |

| 7      | EA       | Enable All interrupt bit Clear to disable all interrupts. Set to enable all interrupts. If EA=1, each interrupt source is individually enabled or disabled by setting or clearing its own interrupt enable bit. |  |  |  |  |  |

| 6      | -        | Reserved The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                    |  |  |  |  |  |

| 5      | ET2      | Timer 2 overflow interrupt Enable bit Clear to disable timer 2 overflow interrupt. Set to enable timer 2 overflow interrupt.                                                                                    |  |  |  |  |  |

| 4      | ES       | Serial port Enable bit Clear to disable serial port interrupt. Set to enable serial port interrupt.                                                                                                             |  |  |  |  |  |

| 3      | ET1      | Timer 1 overflow interrupt Enable bit Clear to disable timer 1 overflow interrupt. Set to enable timer 1 overflow interrupt.                                                                                    |  |  |  |  |  |

| 2      | EX1      | External interrupt 1 Enable bit Clear to disable external interrupt 1. Set to enable external interrupt 1.                                                                                                      |  |  |  |  |  |

| 1      | ET0      | Timer 0 overflow interrupt Enable bit Clear to disable timer 0 overflow interrupt. Set to enable timer 0 overflow interrupt.                                                                                    |  |  |  |  |  |

| 0      | EX0      | External interrupt 0 Enable bit Clear to disable external interrupt 0. Set to enable external interrupt 0.                                                                                                      |  |  |  |  |  |

Reset Value = 0X00 0000b

Bit addressable

### 11. Idle mode

An instruction that sets PCON.0 causes that to be the last instruction executed before going into the Idle mode. In the Idle mode, the internal clock signal is gated off to the CPU, but not to the interrupt, Timer, and Serial Port functions. The CPU status is preserved in its entirely: the Stack Pointer, Program Counter, Program Status Word, Accumulator and all other registers maintain their data during Idle. The port pins hold the logical states they had at the time Idle was activated. ALE and PSEN hold at logic high levels.

There are two ways to terminate the Idle. Activation of any enabled interrupt will cause PCON.0 to be cleared by hardware, terminating the Idle mode. The interrupt will be serviced, and following RETI the next instruction to be executed will be the one following the instruction that put the device into idle.

The flag bits GF0 and GF1 can be used to give an indication if an interrupt occured during normal operation or during an Idle. For example, an instruction that activates Idle can also set one or both flag bits. When Idle is terminated by an interrupt, the interrupt service routine can examine the flag bits.

The other way of terminating the Idle mode is with a hardware reset. Since the clock oscillator is still running, the hardware reset needs to be held active for only two machine cycles (24 oscillator periods) to complete the reset.

#### 11.1 Power-Down Mode

To save maximum power, a power-down mode can be invoked by software (Refer to Table 9-4., PCON register).

In power-down mode, the oscillator is stopped and the instruction that invoked power-down mode is the last instruction executed. The internal RAM and SFRs retain their value until the power-down mode is terminated.  $V_{CC}$  can be lowered to save further power. Either a hardware reset or an external interrupt can cause an exit from power-down. To properly terminate power-down, the reset or external interrupt should not be executed before  $V_{CC}$  is restored to its normal operating level and must be held active long enough for the oscillator to restart and stabilize.

Only external interrupts INTO and INT1 are useful to exit from power-down. For that, interrupt must be enabled and configured as level or edge sensitive interrupt input.

Holding the pin low restarts the oscillator but bringing the pin high completes the exit as detailed in Figure 11-1. When both interrupts are enabled, the oscillator restarts as soon as one of the two inputs is held low and power down exit will be completed when the first input will be released. In this case the higher priority interrupt service routine is executed.

Once the interrupt is serviced, the next instruction to be executed after RETI will be the one following the instruction that put TS80C54/58X2 into power-down mode.

# 12. Hardware Watchdog Timer

The WDT is intended as a recovery method in situations where the CPU may be subjected to software upset. The WDT consists of a 14-bit counter and the WatchDog Timer ReSeT (WDTRST) SFR. The WDT is by default disabled from exiting reset. To enable the WDT, user must write 01EH and 0E1H in sequence to the WDTRST, SFR location 0A6H. When WDT is enabled, it will increment every machine cycle while the oscillator is running and there is no way to disable the WDT except through reset (either hardware reset or WDT overflow reset). When WDT overflows, it will drive an output RESET HIGH pulse at the RST-pin.

## 12.1 Using the WDT

To enable the WDT, user must write 01EH and 0E1H in sequence to the WDTRST, SFR location 0A6H. When WDT is enabled, the user needs to service it by writing to 01EH and 0E1H to WDTRST to avoid WDT overflow. The 14-bit counter overflows when it reaches 16383 (3FFFH) and this will reset the device. When WDT is enabled, it will increment every machine cycle while the oscillator is running. This means the user must reset the WDT at least every 16383 machine cycle. To reset the WDT the user must write 01EH and 0E1H to WDTRST. WDTRST is a write only register. The WDT counter cannot be read or written. When WDT overflows, it will generate an output RESET pulse at the RST-pin. The RESET pulse duration is 96 x  $T_{\rm OSC}$ , where  $T_{\rm OSC}$  =  $1/F_{\rm OSC}$ . To make the best use of the WDT, it should be serviced in those sections of code that will periodically be executed within the time required to prevent a WDT reset.

To have a more powerful WDT, a  $2^7$  counter has been added to extend the Time-out capability, ranking from 16ms to 2s @  $F_{OSC}$  = 12MHz. To manage this feature, refer to WDTPRG register description, Table 12-2. (SFR0A7h).

**Table 12-1.** WDTRST Register WDTRST Address (0A6h)

|             | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

|-------------|---|---|---|---|---|---|---|

| Reset value | X | Х | X | Х | Х | X | X |

Write only, this SFR is used to reset/enable the WDT by writing 01EH then 0E1H in sequence.

# 15. Reduced EMI Mode

The ALE signal is used to demultiplex address and data buses on port 0 when used with external program or data memory. Nevertheless, during internal code execution, ALE signal is still generated. In order to reduce EMI, ALE signal can be disabled by setting AO bit.

The AO bit is located in AUXR register at bit location 0. As soon as AO is set, ALE is no longer output but remains active during MOVX and MOVC instructions and external fetches. During ALE disabling, ALE pin is weakly pulled high.

**Table 15-1.** AUXR Register AUXR - Auxiliary Register (8Eh)

| 7 | 6 | 5 | 4 | 3 | 2 | 1        | 0  |

|---|---|---|---|---|---|----------|----|

| - | - | - | - | - | - | RESERVED | AO |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                  |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------|

| 7             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                                                 |

| 6             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                                                 |

| 5             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                                                 |

| 4             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                                                 |

| 3             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                                                 |

| 2             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                                                 |

| 1             | -               | Reserved The value read from this bit is indeterminate. Do not set this bit.                                                 |

| 0             | АО              | ALE Output bit Clear to restore ALE operation during internal fetches. Set to disable ALE operation during internal fetches. |

Reset Value = XXXX XXX0b Not bit addressable

#### 17.2.3 Signature bytes

The TS87C54/58X2 contains 4 factory programmed signatures bytes. To read these bytes, perform the process described in section 8.3.

## 17.3 EPROM Programming

#### 17.3.1 Set-up modes

In order to program and verify the EPROM or to read the signature bytes, the TS87C54/58X2 is placed in specific set-up modes (See Figure 17-1.).

Control and program signals must be held at the levels indicated in Table 17-2.

#### 17.3.2 Definition of terms

**Address Lines:**P1.0-P1.7, P2.0-P2.5, P3.4 respectively for A0-A14 (P2.5 (A13) for TS87C54X2, P3.4 (A14) for TS87C58X2).

Data Lines:P0.0-P0.7 for D0-D7

Control Signals: RST, PSEN, P2.6, P2.7, P3.3, P3.6, P3.7.

Program Signals: ALE/PROG, EA/VPP.

Table 17-2. EPROM Set-Up Modes

| Mode                                      | RST | PSEN | ALE/PR<br>OG | EA/VPP | P2.6 | P2.7 | P3.3 | P3.6 | P3.7 |

|-------------------------------------------|-----|------|--------------|--------|------|------|------|------|------|

| Program Code data                         | 1   | 0    | ır           | 12.75  | 0    | 1    | 1    | 1    | 1    |

| Verify Code data                          | 1   | 0    | 1            | 1      | 0    | 7    | 0    | 1    | 1    |

| Program Encryption<br>Array Address 0-3Fh | 1   | 0    | ır           | 12.75  | 0    | 1    | 1    | 0    | 1    |

| Read Signature Bytes                      | 1   | 0    | 1            | 1      | 0    | 7    | 0    | 0    | 0    |

| Program Lock bit 1                        | 1   | 0    | ır           | 12.75  | 1    | 1    | 1    | 1    | 1    |

| Program Lock bit 2                        | 1   | 0    | ī.           | 12.75  | 1    | 1    | 1    | 0    | 0    |

| Program Lock bit 3                        | 1   | 0    | Ъ            | 12.75  | 1    | 0    | 1    | 1    | 0    |

- Typicals are based on a limited number of samples and are not guaranteed. The values listed are at room temperature and 5V.

- 6. Under steady state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows:

Maximum I<sub>OL</sub> per port pin: 10 mA

Maximum I<sub>OL</sub> per 8-bit port:

Port 0: 26 mA

Ports 1, 2 and 3: 15 mA

Maximum total I<sub>OI</sub> for all output pins: 71 mA

If  $I_{OL}$  exceeds the test condition,  $V_{OL}$  may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

- 7. For other values, please contact your sales office.

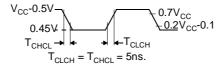

- 8. Operating  $I_{CC}$  is measured with all output pins disconnected; XTAL1 driven with  $T_{CLCH}$ ,  $T_{CHCL}$  = 5 ns (see Figure 19-5.),  $V_{IL} = V_{SS} + 0.5 \text{ V}$ ,

$V_{IH} = V_{CC} - 0.5V$ ; XTAL2 N.C.;  $\overline{EA} = Port \ 0 = V_{CC}$ ; RST =  $V_{SS}$ . The internal ROM runs the code 80 FE (label: SJMP label).  $I_{CC}$  would be slightly higher if a crystal oscillator is used. Measurements are made with OTP products when possible, which is the worst case.

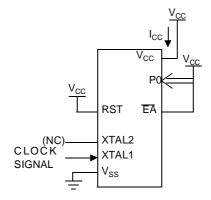

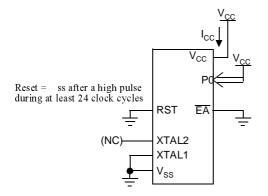

Figure 19-1. I<sub>CC</sub> Test Condition, under reset

All other pins are disconnected.

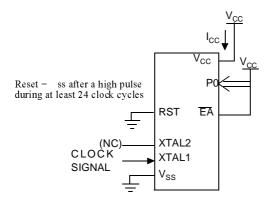

Figure 19-2. Operating I<sub>CC</sub> Test Condition

All other pins are disconnected.

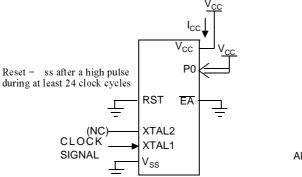

Figure 19-3. I<sub>CC</sub> Test Condition, Idle Mode

All other pins are disconnected.

Figure 19-4.  $I_{CC}$  Test Condition, Power-Down Mode

All other pins are disconnected.

Figure 19-5. Clock Signal Waveform for  $I_{CC}$  Tests in Active and Idle Modes

### 19.5 AC Parameters

#### 19.5.1 Explanation of the AC Symbols

Each timing symbol has 5 characters. The first character is always a "T" (stands for time). The other characters, depending on their positions, stand for the name of a signal or the logical status of that signal. The following is a list of all the characters and what they stand for.

Example: $T_{AVLL}$  = Time for Address <u>Valid</u> to ALE Low.  $T_{ILPL}$  = Time for ALE Low to <u>PSEN</u> Low.

TA = 0 to +70°C (commercial temperature range);  $V_{SS}$  = 0 V;  $V_{CC}$  = 5 V  $\pm$  10%; -M and -V ranges. TA = -40°C to +85°C (industrial temperature range);  $V_{SS}$  = 0 V;  $V_{CC}$  = 5 V  $\pm$  10%; -M and -V ranges.

TA = 0 to +70°C (commercial temperature range);  $V_{SS}$  = 0 V; 2.7 V <  $V_{CC}$  < 5.5 V; -L range. TA = -40°C to +85°C (industrial temperature range);  $V_{SS}$  = 0 V; 2.7 V <  $V_{CC}$  < 5.5 V; -L range.

Table 19-3. gives the maximum applicable load capacitance for Port 0, Port 1, 2 and 3, and ALE and PSEN signals. Timings will be guaranteed if these capacitances are respected. Higher capacitance values can be used, but timings will then be degraded.

Table 19-3. Load Capacitance versus speed range, in pF

|              | -M  | -V | -L  |

|--------------|-----|----|-----|

| Port 0       | 100 | 50 | 100 |

| Port 1, 2, 3 | 80  | 50 | 80  |

| ALE / PSEN   | 100 | 30 | 100 |

Table 19-5., Table 19-8. and Table 19-11. give the description of each AC symbols.

Table 19-6., Table 19-9. and Table 19-12. give for each range the AC parameter.

Table 19-7., Table 19-10. and Table 19-13. give the frequency derating formula of the AC parameter. To calculate each AC symbols, take the x value corresponding to the speed grade you need (-M, -V or -L) and replace this value in the formula. Values of the frequency must be limited to the corresponding speed grade:

Table 19-4. Max frequency for derating formula regarding the speed grade

|            | -M X1 mode | -M X2 mode | -V X1 mode | -V X2 mode | -L X1 mode | -L X2 mode |

|------------|------------|------------|------------|------------|------------|------------|

| Freq (MHz) | 40         | 20         | 40         | 30         | 30         | 20         |

| T (ns)     | 25         | 50         | 25         | 33.3       | 33.3       | 50         |

## Example:

$T_{LLIV}$  in X2 mode for a -V part at 20 MHz (T =  $1/20^{E6}$  = 50 ns):

$$T_{LLIV} = 2T - x = 2 \times 50 - 22 = 78$$

ns

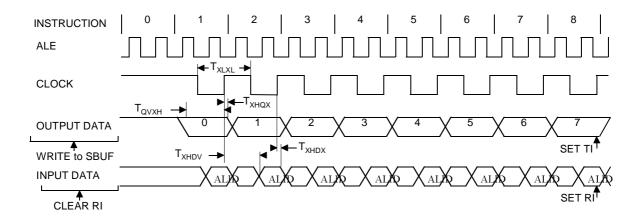

Table 19-13. AC Parameters for a Variable Clock: derating formula

| Symbol            | Туре | Standard<br>Clock | X2 Clock | -М  | -V  | -L  | Units |

|-------------------|------|-------------------|----------|-----|-----|-----|-------|

| $T_{XLXL}$        | Min  | 12 T              | 6 T      |     |     |     | ns    |

| T <sub>QVHX</sub> | Min  | 10 T - x          | 5 T - x  | 50  | 50  | 50  | ns    |

| T <sub>XHQX</sub> | Min  | 2 T - x           | T - x    | 20  | 20  | 20  | ns    |

| T <sub>XHDX</sub> | Min  | х                 | х        | 0   | 0   | 0   | ns    |

| $T_{XHDV}$        | Max  | 10 T - x          | 5 T- x   | 133 | 133 | 133 | ns    |

## 19.5.8 Shift Register Timing Waveforms

Figure 19-9. Shift Register Timing Waveforms

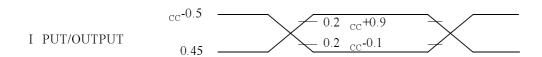

#### 19.5.13 AC Testing Input/Output Waveforms

Figure 19-12. AC Testing Input/Output Waveforms

AC inputs during testing are driven at  $V_{CC}$  - 0.5 for a logic "1" and 0.45V for a logic "0". Timing measurement are made at  $V_{IH}$  min for a logic "1" and  $V_{IL}$  max for a logic "0".

#### 19.5.14 Float Waveforms

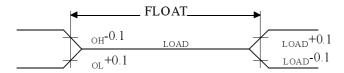

Figure 19-13. Float Waveforms

For timing purposes a port pin is no longer floating when a 100 mV change from load voltage occurs and begins to float when a 100 mV change from the loaded  $V_{OH}/V_{OL}$  level occurs.  $I_{OL}/I_{OH} \ge \pm 20$ mA.

#### 19.5.15 Clock Waveforms

Valid in normal clock mode. In X2 mode XTAL2 signal must be changed to XTAL2 divided by two.