# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                   |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 40/30MHz                                                                |

| Connectivity               | UART/USART                                                              |

| Peripherals                | POR, WDT                                                                |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | 16KB (16K x 8)                                                          |

| Program Memory Type        | ОТР                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 256 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                             |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-QFP                                                                  |

| Supplier Device Package    | 44-PQFP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/ts87c54x2-vcc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The TS80C54/58X2 has 2 software-selectable modes of reduced activity for further reduction in power consumption. In the idle mode the CPU is frozen while the timers, the serial port and the interrupt system are still operating. In the power-down mode the RAM is saved and all other functions are inoperative.

| PDIL40<br>PLCC44<br>PQFP44 F1<br>VQFP44 1.4 | ROM (bytes) | EPROM (bytes) |

|---------------------------------------------|-------------|---------------|

| TS80C54X2                                   | 16k         | 0             |

| TS80C58X2                                   | 32k         | 0             |

| TS87C54X2                                   | 0           | 16k           |

| TS87C58X2                                   | 0           | 32k           |

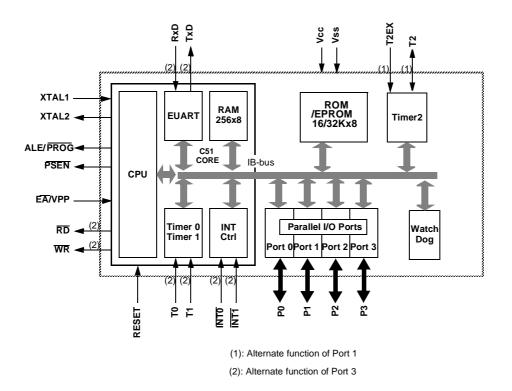

### 2. Block Diagram

| Table 4-1. | All SFRs with their address and their reset value |

|------------|---------------------------------------------------|

|            |                                                   |

|     | Bit<br>address-<br>able |                    |                     | Nor                 | ) Bit address    | able             |                     |                     |     |

|-----|-------------------------|--------------------|---------------------|---------------------|------------------|------------------|---------------------|---------------------|-----|

|     | 0/8                     | 1/9                | 2/A                 | 3/B                 | 4/C              | 5/D              | 6/E                 | 7/F                 |     |

| F8h |                         |                    |                     |                     |                  |                  |                     |                     | FFh |

| F0h | B<br>0000 0000          |                    |                     |                     |                  |                  |                     |                     | F7h |

| E8h |                         |                    |                     |                     |                  |                  |                     |                     | EFh |

| E0h | ACC<br>0000 0000        |                    |                     |                     |                  |                  |                     |                     | E7h |

| D8h |                         |                    |                     |                     |                  |                  |                     |                     | DFh |

| D0h | PSW<br>0000 0000        |                    |                     |                     |                  |                  |                     |                     | D7h |

| C8h | T2CON<br>0000 0000      | T2MOD<br>XXXX XX00 | RCAP2L<br>0000 0000 | RCAP2H<br>0000 0000 | TL2<br>0000 0000 | TH2<br>0000 0000 |                     |                     | CFh |

| C0h |                         |                    |                     |                     |                  |                  |                     |                     | C7h |

| B8h | IP<br>XX00 0000         | SADEN<br>0000 0000 |                     |                     |                  |                  |                     |                     | BFh |

| B0h | P3<br>1111 1111         |                    |                     |                     |                  |                  |                     | IPH<br>XX00 0000    | B7h |

| A8h | IE<br>0X00 0000         | SADDR<br>0000 0000 |                     |                     |                  |                  |                     |                     | AFh |

| A0h | P2<br>1111 1111         |                    | AUXR1<br>XXXX 0XX0  |                     |                  |                  | WDTRST<br>XXXX XXXX | WDTPRG<br>XXXX X000 | A7h |

| 98h | SCON<br>0000 0000       | SBUF<br>XXXX XXXX  |                     |                     |                  |                  |                     |                     | 9Fh |

| 90h | P1<br>1111 1111         |                    |                     |                     |                  |                  |                     |                     | 97h |

| 88h | TCON<br>0000 0000       | TMOD<br>0000 0000  | TL0<br>0000 0000    | TL1<br>0000 0000    | TH0<br>0000 0000 | TH1<br>0000 0000 | AUXR<br>XXXX XXX0   | CKCON<br>XXXX XXX0  | 8Fh |

| 80h | P0<br>1111 1111         | SP<br>0000 0111    | DPL<br>0000 0000    | DPH<br>0000 0000    |                  |                  |                     | PCON<br>00X1 0000   | 87h |

|     | 0/8                     | 1/9                | 2/A                 | 3/B                 | 4/C              | 5/D              | 6/E                 | 7/F                 | 1   |

reserved

## Table 6-1. CKCON Register CKCON - Clock Control Register (8Fh)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0  |

|---|---|---|---|---|---|---|----|

| - | - | - | - | - | - | - | X2 |

| Bit    | Bit      |                                                                                                                                                                                                                 |

|--------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number | Mnemonic | Description                                                                                                                                                                                                     |

| 7      | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 6      | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 5      | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 4      | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 3      | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 2      | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 1      | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 0      | X2       | <b>CPU and peripheral clock bit</b><br>Clear to select 12 clock periods per machine cycle (STD mode, $F_{OSC}=F_{XTAL}/2$ ).<br>Set to select 6 clock periods per machine cycle (X2 mode, $F_{OSC}=F_{XTAL}$ ). |

Reset Value = XXXX XXX0b Not bit addressable

For further details on the X2 feature, please refer to ANM072 available on the web (http://www.atmel.com)

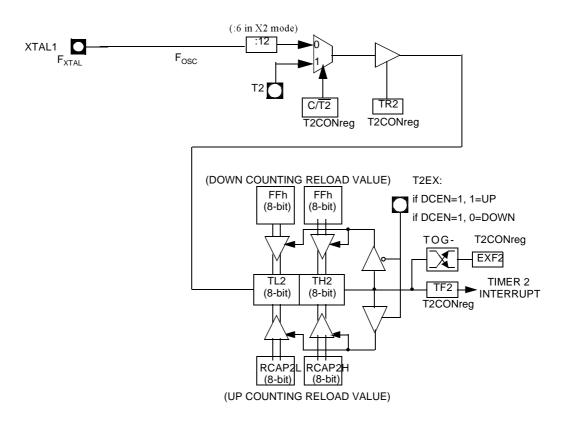

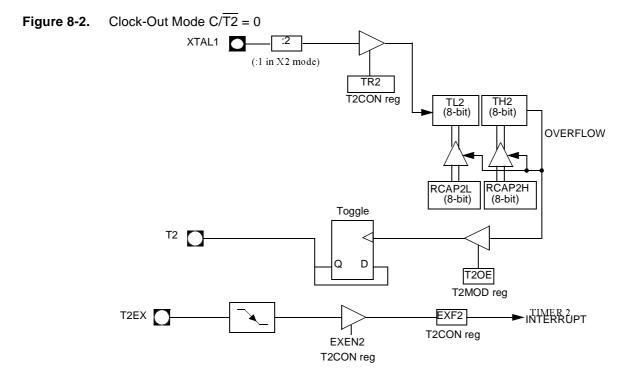

#### 8.1.1 Programmable Clock-Output

In the clock-out mode, timer 2 operates as a 50%-duty-cycle, programmable clock generator (See Figure 8-2) . The input clock increments TL2 at frequency  $F_{OSC}/2$ . The timer repeatedly counts to overflow from a loaded value. At overflow, the contents of RCAP2H and RCAP2L registers are loaded into TH2 and TL2. In this mode, timer 2 overflows do not generate interrupts. The formula gives the clock-out frequency as a function of the system oscillator frequency and the value in the RCAP2H and RCAP2L registers :

$$Clock - OutFrequency = \frac{F_{osc}}{4 \times (65536 - RCAP2H/RCAP2L)}$$

For a 16 MHz system clock, timer 2 has a programmable frequency range of 61 Hz  $(F_{OSC}/2^{16})$  to 4 MHz  $(F_{OSC}/4)$ . The generated clock signal is brought out to T2 pin (P1.0).

Timer 2 is programmed for the clock-out mode as follows:

- Set T2OE bit in T2MOD register.

- Clear C/T2 bit in T2CON register.

- Determine the 16-bit reload value from the formula and enter it in RCAP2H/RCAP2L registers.

- AMEL

- Enter a 16-bit initial value in timer registers TH2/TL2. It can be the same as the reload value or a different one depending on the application.

- To start the timer, set TR2 run control bit in T2CON register.

It is possible to use timer 2 as a baud rate generator and a clock generator simultaneously. For this configuration, the baud rates and clock frequencies are not independent since both functions use the values in the RCAP2H and RCAP2L registers.

## <sup>16</sup> **AT/TS8xC54/8X2**

### 10. Interrupt System

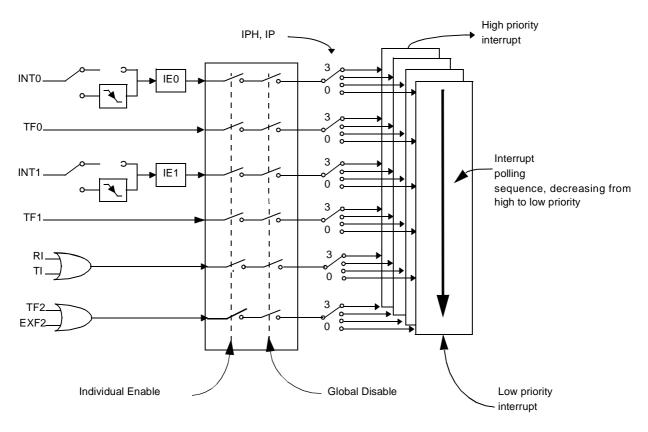

The TS80C54/58X2 has a total of 7 interrupt vectors: two external interrupts (INT0 and INT1), three timer interrupts (timers 0, 1 and 2) and the serial port interrupt. These interrupts are shown in Figure 10-1.

#### Figure 10-1. Interrupt Control System

Each of the interrupt sources can be individually enabled or disabled by setting or clearing a bit in the Interrupt Enable register (See Table 10-2.). This register also contains a global disable bit, which must be cleared to disable all interrupts at once.

Each interrupt source can also be individually programmed to one out of four priority levels by setting or clearing a bit in the Interrupt Priority register (See Table 10-3.) and in the Interrupt Priority High register (See Table 10-4.). shows the bit values and priority levels associated with each combination.

| IPH.x | IP.x | Interrupt Level Priority |

|-------|------|--------------------------|

| 0     | 0    | 0 (Lowest)               |

| 0     | 1    | 1                        |

| 1     | 0    | 2                        |

| 1     | 1    | 3 (Highest)              |

Table 10-1. Priority Level Bit Values

A low-priority interrupt can be interrupted by a high priority interrupt, but not by another low-priority interrupt. A high-priority interrupt can't be interrupted by any other interrupt source.

| 7             | 6               |                                                | 5                                       | 4                                                       | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2                                                                                                                       | 1                                                                                     | 0  |

|---------------|-----------------|------------------------------------------------|-----------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----|

| T4            | Т3              |                                                | T2                                      | T1                                                      | ТО                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | \$2                                                                                                                     | S1                                                                                    | S0 |

| Bit<br>Number | Bit<br>Mnemonic |                                                |                                         |                                                         | Descri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ption                                                                                                                   |                                                                                       |    |

| 7             | T4              |                                                |                                         |                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                         |                                                                                       |    |

| 6             | Т3              |                                                |                                         |                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                         |                                                                                       |    |

| 5             | T2              | Reserv                                         |                                         | or clear this b                                         | it                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                         |                                                                                       |    |

| 4             | T1              | Donot                                          |                                         |                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                         |                                                                                       |    |

| 3             | T0              |                                                |                                         |                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                         |                                                                                       |    |

| 2             | S2              | WDT Ti                                         | me-out se                               | elect bit 2                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                         |                                                                                       |    |

| 1             | S1              | WDT Ti                                         | ime-out se                              | elect bit 1                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                         |                                                                                       |    |

| 0             | S0              | WDT Ti                                         | me-out s                                | elect bit 0                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                         |                                                                                       |    |

|               |                 | <u>S2S1</u><br>0<br>0<br>0<br>1<br>1<br>1<br>1 | <u>S0</u><br>0<br>1<br>1<br>0<br>0<br>1 | <u>Selected</u><br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | $\begin{array}{l} \hline \mbox{Imme-out} \\ (2^{14} - 1) machir \\ (2^{15} - 1) machir \\ (2^{16} - 1) machir \\ (2^{17} - 1) machir \\ (2^{18} - 1) machir \\ (2^{19} - 1) machir \\ (2^{20} - 1) machir \\ (2^{21} - 1) mach$ | ne cycles, 32.7 m<br>ne cycles, 65.5 m<br>ne cycles, 131 m<br>ne cycles, 262 m<br>ne cycles, 542 m<br>ne cycles, 1.05 s | ms @ 12 MHz<br>ms @ 12 MHz<br>ns @ 12 MHz<br>ns @ 12 MHz<br>ns @ 12 MHz<br>s @ 12 MHz |    |

#### Table 12-2. WDTPRG Register WDTPRG Address (0A7h)

Reset value XXXX X000

#### 12.1.1 WDT during Power Down and Idle

In Power Down mode the oscillator stops, which means the WDT also stops. While in Power Down mode the user does not need to service the WDT. There are 2 methods of exiting Power Down mode: by a hardware reset or via a level activated external interrupt which is enabled prior to entering Power Down mode. When Power Down is exited with hardware reset, servicing the WDT should occur as it normally should whenever the TS80C54/58X2 is reset. Exiting Power Down with an interrupt is significantly different. The interrupt is held low long enough for the oscillator to stabilize. When the interrupt is brought high, the interrupt is serviced. To prevent the WDT from resetting the device while the interrupt pin is held low, the WDT is not started until the interrupt is pulled high. It is suggested that the WDT be reset during the interrupt service routine.

To ensure that the WDT does not overflow within a few states of exiting of powerdown, it is best to reset the WDT just before entering powerdown.

In the Idle mode, the oscillator continues to run. To prevent the WDT from resetting the TS80C54/58X2 while in Idle mode, the user should always set up a timer that will periodically exit Idle, service the WDT, and re-enter Idle mode.

### 14. Power-Off Flag

The power-off flag allows the user to distinguish between a "cold start" reset and a "warm start" reset.

A cold start reset is the one induced by  $V_{CC}$  switch-on. A warm start reset occurs while  $V_{CC}$  is still applied to the device and could be generated for example by an exit from power-down.

The power-off flag (POF) is located in PCON register (See Table 14-1.). POF is set by hardware when  $V_{CC}$  rises from 0 to its nominal voltage. The POF can be set or cleared by software allowing the user to determine the type of reset.

The POF value is only relevant with a Vcc range from 4.5V to 5.5V. For lower Vcc value, reading POF bit will return indeterminate value.

| 7             | 6               | 5                                                               | 4                 | 3                | 2                  | 1              | 0              |

|---------------|-----------------|-----------------------------------------------------------------|-------------------|------------------|--------------------|----------------|----------------|

| SMOD1         | SMOD            | ) -                                                             | POF               | GF1              | GF0                | PD             | IDL            |

| Bit<br>Number | Bit<br>Mnemonic |                                                                 |                   | Descrip          | otion              |                |                |

| 7             | SMOD1           | Serial port Mode<br>Set to select dou                           |                   | n mode 1, 2 or 3 | 3.                 |                |                |

| 6             | SMOD0           | Serial port Mode<br>Clear to select SI<br>Set to to select F    | /10 bit in SCON   | •                |                    |                |                |

| 5             | -               | <b>Reserved</b><br>The value read fr                            | om this bit is in | determinate. Do  | o not set this bit |                |                |

| 4             | POF             | Power-Off Flag<br>Clear to recogniz<br>Set by hardware          |                   |                  | ominal voltage.    | Can also be se | t by software. |

| 3             | GF1             | General purpose<br>Cleared by user f<br>Set by user for ge      | or general purp   |                  |                    |                |                |

| 2             | GF0             | General purpose<br>Cleared by user f<br>Set by user for ge      | or general purp   |                  |                    |                |                |

| 1             | PD              | Power-Down mc<br>Cleared by hardw<br>Set to enter powe          | are when reset    | t occurs.        |                    |                |                |

| 0             | IDL             | <b>Idle mode bit</b><br>Clear by hardwar<br>Set to enter idle r |                   | ot or reset occu | ſS.                |                |                |

## Table 14-1.PCON RegisterPCON - Power Control Register (87h)

Reset Value = 00X1 0000b Not bit addressable

## AT/TS8xC54/8X2

| Table 18-1. | Signature By | tes Content |

|-------------|--------------|-------------|

|-------------|--------------|-------------|

| Location | Contents | Comment                                                 |

|----------|----------|---------------------------------------------------------|

| 30h      | 58h      | Manufacturer Code: Atmel Wireless &<br>Microcontrollers |

| 31h      | 57h      | Family Code: C51 X2                                     |

| 60h      | 37h      | Product name: TS80C58X2                                 |

| 60h      | B7h      | Product name: TS87C58X2                                 |

| 60h      | 3Bh      | Product name: TS80C54X2                                 |

| 60h      | BBh      | Product name: TS87C54X2                                 |

| 61h      | FFh      | Product revision number                                 |

### **19. Electrical Characteristics**

#### 19.1 Absolute Maximum Ratings <sup>(1)</sup>

Ambiant Temperature Under Bias: C = commercial0°C to 70°C I = industrial -40°C to 85°C Storage Temperature-65°C to + 150°C Voltage on V<sub>CC</sub> to V<sub>SS</sub>-0.5 V to + 7 V Voltage on V<sub>PP</sub> to V<sub>SS</sub>-0.5 V to + 13 V Voltage on Any Pin to V<sub>SS</sub>-0.5 V to V<sub>CC</sub> + 0.5 V Power Dissipation1 W<sup>(2)</sup>

- 1. Stresses at or above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- 2. This value is based on the maximum allowable die temperature and the thermal resistance of the package.

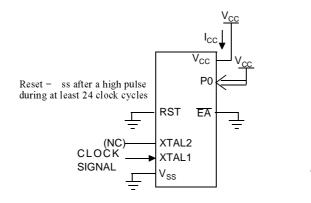

#### **19.2** Power consumption measurement

Since the introduction of the first C51 devices, every manufacturer made operating lcc measurements under reset, which made sense for the designs were the CPU was running under reset. In Atmel new devices, the CPU is no more active during reset, so the power consumption is very low but is not really representative of what will happen in the customer system. That's why, while keeping measurements under Reset, Atmel presents a new way to measure the operating lcc:

Using an internal test ROM, the following code is executed:

Label:

SJMP Label (80 FE)

Ports 1, 2, 3 are disconnected, Port 0 is tied to FFh, EA = Vcc, RST = Vss, XTAL2 is not connected and XTAL1 is driven by the clock.

This is much more representative of the real operating Icc.

#### 19.3 DC Parameters for Standard Voltage

$\begin{array}{l} T_{A}=0^{\circ}C \ to \ +70^{\circ}C; \ V_{SS}=0 \ V; \ V_{CC}=5 \ V \pm 10\%; \ F=0 \ to \ 40 \ MHz. \\ T_{A}=-40^{\circ}C \ to \ +85^{\circ}C; \ V_{SS}=0 \ V; \ V_{CC}=5 \ V \pm 10\%; \ F=0 \ to \ 40 \ MHz. \end{array}$

| Symbol           | Parameter                             | Min                       | Тур | Max                       | Unit | Test Conditions                         |

|------------------|---------------------------------------|---------------------------|-----|---------------------------|------|-----------------------------------------|

| V <sub>IL</sub>  | Input Low Voltage                     | -0.5                      |     | 0.2 V <sub>CC</sub> - 0.1 | V    |                                         |

| V <sub>IH</sub>  | Input High Voltage except XTAL1, RST  | 0.2 V <sub>CC</sub> + 0.9 |     | V <sub>CC</sub> + 0.5     | V    |                                         |

| V <sub>IH1</sub> | Input High Voltage, XTAL1, RST        | 0.7 V <sub>CC</sub>       |     | V <sub>CC</sub> + 0.5     | V    |                                         |

|                  |                                       |                           |     | 0.3                       | V    | $I_{OL} = 100 \ \mu A^{(4)}$            |

| V <sub>OL</sub>  | Output Low Voltage, ports 1, 2, 3 (6) |                           |     | 0.45                      | V    | I <sub>OL</sub> = 1.6 mA <sup>(4)</sup> |

|                  |                                       |                           |     | 1.0                       | V    | I <sub>OL</sub> = 3.5 mA <sup>(4)</sup> |

#### 19.4 DC Parameters for Low Voltage

TA = 0°C to +70°C;  $V_{SS} = 0$  V;  $V_{CC} = 2.7$  V to 5.5 V ± 10%; F = 0 to 30 MHz. TA = -40°C to +85°C;  $V_{SS} = 0$  V;  $V_{CC} = 2.7$  V to 5.5 V ± 10%; F = 0 to 30 MHz.

|  | Table 19-2. | DC Parameters for Low Voltage |

|--|-------------|-------------------------------|

|--|-------------|-------------------------------|

| Symbol                            | Parameter                                                    | Min                       | Тур                                    | Max                                                | Unit | Test Conditions                                                                                      |

|-----------------------------------|--------------------------------------------------------------|---------------------------|----------------------------------------|----------------------------------------------------|------|------------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>                   | Input Low Voltage                                            | -0.5                      |                                        | 0.2 V <sub>CC</sub> - 0.1                          | V    |                                                                                                      |

| V <sub>IH</sub>                   | Input High Voltage except XTAL1, RST                         | 0.2 V <sub>CC</sub> + 0.9 |                                        | V <sub>CC</sub> + 0.5                              | V    |                                                                                                      |

| V <sub>IH1</sub>                  | Input High Voltage, XTAL1, RST                               | 0.7 V <sub>CC</sub>       |                                        | V <sub>CC</sub> + 0.5                              | V    |                                                                                                      |

| V <sub>OL</sub>                   | Output Low Voltage, ports 1, 2, 3 (6)                        |                           |                                        | 0.45                                               | V    | $I_{OL} = 0.8 \text{ mA}^{(4)}$                                                                      |

| V <sub>OL1</sub>                  | Output Low Voltage, port 0, ALE, PSEN (6)                    |                           |                                        | 0.45                                               | V    | I <sub>OL</sub> = 1.6 mA <sup>(4)</sup>                                                              |

| V <sub>OH</sub>                   | Output High Voltage, ports 1, 2, 3                           | 0.9 V <sub>CC</sub>       |                                        |                                                    | V    | I <sub>OH</sub> = -10 μA                                                                             |

| V <sub>OH1</sub>                  | Output High Voltage, port 0, ALE, PSEN                       | 0.9 V <sub>CC</sub>       |                                        |                                                    | V    | I <sub>OH</sub> = -40 μA                                                                             |

| I <sub>IL</sub>                   | Logical 0 Input Current ports 1, 2 and 3                     |                           |                                        | -50                                                | μΑ   | Vin = 0.45 V                                                                                         |

| I <sub>LI</sub>                   | Input Leakage Current                                        |                           |                                        | ±10                                                | μA   | 0.45 V < Vin < V <sub>CC</sub>                                                                       |

| I <sub>TL</sub>                   | Logical 1 to 0 Transition Current, ports 1, 2, 3             |                           |                                        | -650                                               | μA   | Vin = 2.0 V                                                                                          |

| R <sub>RST</sub>                  | RST Pulldown Resistor                                        | 50                        | 90 <sup>(5)</sup>                      | 200                                                | kΩ   |                                                                                                      |

| CIO                               | Capacitance of I/O Buffer                                    |                           |                                        | 10                                                 | pF   | Fc = 1 MHz<br>TA = 25°C                                                                              |

| I <sub>PD</sub>                   | Power Down Current                                           |                           | 20 <sup>(5)</sup><br>10 <sup>(5)</sup> | 50<br>30                                           | μΑ   | $V_{CC} = 2.0 \text{ V to } 5.5 \text{ V}^{(3)}$<br>$V_{CC} = 2.0 \text{ V to } 3.3 \text{ V}^{(3)}$ |

| I <sub>CC</sub><br>under<br>RESET | Power Supply Current Maximum values, X1 mode: <sup>(7)</sup> |                           |                                        | 1 + 0.2 Freq<br>(MHz)<br>@12MHz 3.4<br>@16MHz 4.2  | mA   | $V_{CC} = 3.3 V^{(1)}$                                                                               |

| I <sub>CC</sub><br>operating      | Power Supply Current Maximum values, X1 mode: (7)            |                           |                                        | 1 + 0.3 Freq<br>(MHz)<br>@12MHz 4.6<br>@16MHz 5.8  | mA   | $V_{\rm CC} = 3.3 \ V^{(8)}$                                                                         |

| I <sub>CC</sub><br>idle           | Power Supply Current Maximum values, X1 mode: <sup>(7)</sup> |                           |                                        | 0.15 Freq (MHz)<br>+ 0.2<br>@12MHz 2<br>@16MHz 2.6 | mA   | $V_{CC} = 3.3 V^{(2)}$                                                                               |

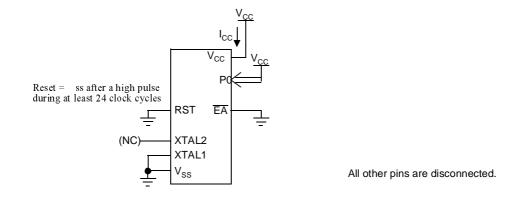

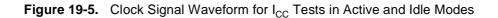

1.  $I_{CC}$  under reset is measured with all output pins disconnected; XTAL1 driven with  $T_{CLCH}$ ,  $T_{CHCL}$  = 5 ns (see Figure 19-5.),  $V_{IL} = V_{SS} + 0.5 V$ ,

$V_{IH} = V_{CC} - 0.5V$ ; XTAL2 N.C.;  $\overline{EA} = RST = Port 0 = V_{CC}$ .  $I_{CC}$  would be slightly higher if a crystal oscillator used...

- 2. Idle I<sub>CC</sub> is measured with all output pins disconnected; XTAL1 driven with T<sub>CLCH</sub>, T<sub>CHCL</sub> = 5 ns, V<sub>IL</sub> = V<sub>SS</sub> + 0.5 V, V<sub>IH</sub> = V<sub>CC</sub> 0.5 V; XTAL2 N.C; Port 0 = V<sub>CC</sub>;  $\overline{EA}$  = RST = V<sub>SS</sub> (see Figure 19-3.).

- Power Down I<sub>CC</sub> is measured with all output pins disconnected; EA = V<sub>SS</sub>, PORT 0 = V<sub>CC</sub>; XTAL2 NC.; RST = V<sub>SS</sub> (see Figure 19-4.).

- 4. Capacitance loading on Ports 0 and 2 may cause spurious noise pulses to be superimposed on the V<sub>OL</sub>s of ALE and Ports 1 and 3. The noise is due to external bus capacitance discharging into the Port 0 and Port 2 pins when these pins make 1 to 0 transitions during bus operation. In the worst cases (capacitive loading 100pF), the noise pulse on the ALE line may exceed 0.45V with maxi V<sub>OL</sub> peak 0.6V. A Schmitt Trigger use is not necessary.

Figure 19-3. I<sub>CC</sub> Test Condition, Idle Mode

All other pins are disconnected.

#### 19.5 AC Parameters

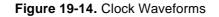

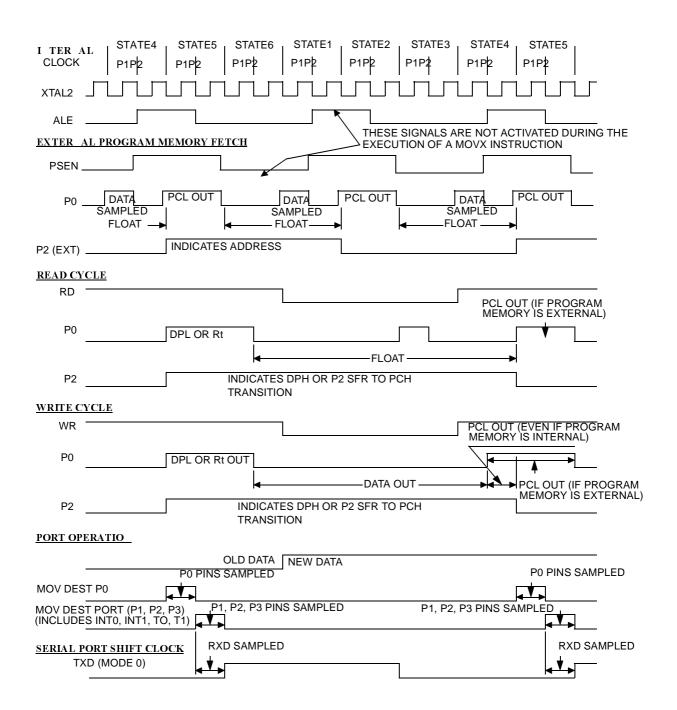

#### 19.5.1 Explanation of the AC Symbols

Each timing symbol has 5 characters. The first character is always a "T" (stands for time). The other characters, depending on their positions, stand for the name of a signal or the logical status of that signal. The following is a list of all the characters and what they stand for.

Example:  $T_{AVLL}$  = Time for Address Valid to ALE Low.  $T_{ILPL}$  = Time for ALE Low to PSEN Low.

TA = 0 to +70°C (commercial temperature range);  $V_{SS} = 0 \text{ V}$ ;  $V_{CC} = 5 \text{ V} \pm 10\%$ ; -M and -V ranges. TA = -40°C to +85°C (industrial temperature range);  $V_{SS} = 0 \text{ V}$ ;  $V_{CC} = 5 \text{ V} \pm 10\%$ ; -M and -V ranges.

TA = 0 to +70°C (commercial temperature range);  $V_{SS} = 0$  V; 2.7 V <  $V_{CC}$  < 5.5 V; -L range. TA = -40°C to +85°C (industrial temperature range);  $V_{SS} = 0$  V; 2.7 V <  $V_{CC}$  < 5.5 V; -L range.

Table 19-3. gives the maximum applicable load capacitance for Port 0, Port 1, 2 and 3, and ALE and  $\overrightarrow{\text{PSEN}}$  signals. Timings will be guaranteed if these capacitances are respected. Higher capacitance values can be used, but timings will then be degraded.

| í. |              |     |    |     |

|----|--------------|-----|----|-----|

|    |              | -М  | -V | ۰L  |

|    | Port 0       | 100 | 50 | 100 |

|    | Port 1, 2, 3 | 80  | 50 | 80  |

|    | ALE / PSEN   | 100 | 30 | 100 |

Table 19-3. Load Capacitance versus speed range, in pF

Table 19-5., Table 19-8. and Table 19-11. give the description of each AC symbols.

Table 19-6., Table 19-9. and Table 19-12. give for each range the AC parameter.

Table 19-7., Table 19-10. and Table 19-13. give the frequency derating formula of the AC parameter. To calculate each AC symbols, take the x value corresponding to the speed grade you need (-M, -V or -L) and replace this value in the formula. Values of the frequency must be limited to the corresponding speed grade:

Table 19-4.

Max frequency for derating formula regarding the speed grade

|            | -M X1 mode | -M X2 mode | -V X1 mode | -V X2 mode | -L X1 mode | -L X2 mode |

|------------|------------|------------|------------|------------|------------|------------|

| Freq (MHz) | 40         | 20         | 40         | 30         | 30         | 20         |

| T (ns)     | 25         | 50         | 25         | 33.3       | 33.3       | 50         |

Example:

$T_{111V}$  in X2 mode for a -V part at 20 MHz (T = 1/20^{E6} = 50 ns):

x= 22 (Table 19-7.)

T= 50ns

$T_{LLIV} = 2T - x = 2 \times 50 - 22 = 78$ ns

#### 19.5.2 External Program Memory Characteristics

#### Table 19-5. Symbol Description

| Symbol            | Parameter                         |

|-------------------|-----------------------------------|

| Т                 | Oscillator clock period           |

| T <sub>LHLL</sub> | ALE pulse width                   |

| T <sub>AVLL</sub> | Address Valid to ALE              |

| T <sub>LLAX</sub> | Address Hold After ALE            |

| T <sub>LLIV</sub> | ALE to Valid Instruction In       |

| T <sub>LLPL</sub> | ALE to PSEN                       |

| T <sub>PLPH</sub> | PSEN Pulse Width                  |

| T <sub>PLIV</sub> | PSEN to Valid Instruction In      |

| T <sub>PXIX</sub> | Input Instruction Hold After PSEN |

| T <sub>PXIZ</sub> | Input Instruction FloatAfter PSEN |

| T <sub>PXAV</sub> | PSEN to Address Valid             |

| T <sub>AVIV</sub> | Address to Valid Instruction In   |

| T <sub>PLAZ</sub> | PSEN Low to Address Float         |

Table 19-6.

AC Parameters for Fix Clock

| Speed             |     | M<br>MHz | X2 r<br>30 | V<br>node<br>MHz<br>z equiv. | standard | V<br>I mode 40<br>Hz | X2 n<br>20 | L<br>node<br>MHz<br>z equiv. | standa | L<br>′d mode<br>MHz | Units |

|-------------------|-----|----------|------------|------------------------------|----------|----------------------|------------|------------------------------|--------|---------------------|-------|

| Symbol            | Min | Max      | Min        | Max                          | Min      | Max                  | Min        | Max                          | Min    | Max                 |       |

| Т                 | 25  |          | 33         |                              | 25       |                      | 50         |                              | 33     |                     | ns    |

| T <sub>LHLL</sub> | 40  |          | 25         |                              | 42       |                      | 35         |                              | 52     |                     | ns    |

| T <sub>AVLL</sub> | 10  |          | 4          |                              | 12       |                      | 5          |                              | 13     |                     | ns    |

| T <sub>LLAX</sub> | 10  |          | 4          |                              | 12       |                      | 5          |                              | 13     |                     | ns    |

| T <sub>LLIV</sub> |     | 70       |            | 45                           | l l      | 78                   |            | 65                           |        | 98                  | ns    |

| T <sub>LLPL</sub> | 15  |          | 9          |                              | 17       |                      | 10         |                              | 18     |                     | ns    |

| T <sub>PLPH</sub> | 55  |          | 35         |                              | 60       |                      | 50         |                              | 75     |                     | ns    |

| T <sub>PLIV</sub> |     | 35       |            | 25                           | Ī        | 50                   |            | 30                           |        | 55                  | ns    |

| T <sub>PXIX</sub> | 0   |          | 0          |                              | 0        |                      | 0          |                              | 0      |                     | ns    |

| T <sub>PXIZ</sub> |     | 18       |            | 12                           | Ī        | 20                   |            | 10                           |        | 18                  | ns    |

| T <sub>AVIV</sub> |     | 85       |            | 53                           |          | 95                   |            | 80                           |        | 122                 | ns    |

| T <sub>PLAZ</sub> |     | 10       |            | 10                           |          | 10                   |            | 10                           |        | 10                  | ns    |

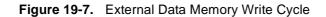

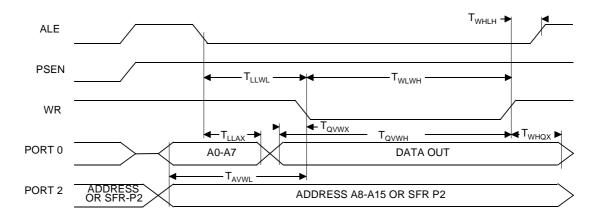

#### 19.5.4 External Data Memory Characteristics

Table 19-8.

Symbol Description

| Symbol            | Parameter                   |

|-------------------|-----------------------------|

| T <sub>RLRH</sub> | RD Pulse Width              |

| T <sub>WLWH</sub> | WR Pulse Width              |

| T <sub>RLDV</sub> | RD to Valid Data In         |

| T <sub>RHDX</sub> | Data Hold After RD          |

| T <sub>RHDZ</sub> | Data Float After RD         |

| T <sub>LLDV</sub> | ALE to Valid Data In        |

| T <sub>AVDV</sub> | Address to Valid Data In    |

| T <sub>LLWL</sub> | ALE to WR or RD             |

| T <sub>AVWL</sub> | Address to WR or RD         |

| T <sub>QVWX</sub> | Data Valid to WR Transition |

| T <sub>QVWH</sub> | Data set-up to WR High      |

| T <sub>WHQX</sub> | Data Hold After WR          |

| T <sub>RLAZ</sub> | RD Low to Address Float     |

| T <sub>WHLH</sub> | RD or WR High to ALE high   |

#### Table 19-9. AC Parameters for a Fix Clock

| Speed             |     | M<br>MHz | X2 r<br>30 | V<br>node<br>MHz<br>z equiv. | standard | V<br>I mode 40<br>Hz | X2 r<br>20 | ·L<br>node<br>MHz<br>z equiv. | standa | ·L<br>rd mode<br>MHz | Units |

|-------------------|-----|----------|------------|------------------------------|----------|----------------------|------------|-------------------------------|--------|----------------------|-------|

| Symbol            | Min | Max      | Min        | Max                          | Min      | Max                  | Min        | Max                           | Min    | Max                  |       |

| T <sub>RLRH</sub> | 130 |          | 85         |                              | 135      |                      | 125        |                               | 175    |                      | ns    |

| T <sub>WLWH</sub> | 130 |          | 85         |                              | 135      |                      | 125        |                               | 175    |                      | ns    |

| T <sub>RLDV</sub> |     | 100      | 1          | 60                           |          | 102                  |            | 95                            |        | 137                  | ns    |

| T <sub>RHDX</sub> | 0   | 1        | 0          | 1                            | 0        |                      | 0          | l l                           | 0      |                      | ns    |

| T <sub>RHDZ</sub> |     | 30       |            | 18                           |          | 35                   |            | 25                            |        | 42                   | ns    |

| T <sub>LLDV</sub> |     | 160      |            | 98                           |          | 165                  |            | 155                           |        | 222                  | ns    |

| T <sub>AVDV</sub> |     | 165      | 1          | 100                          |          | 175                  |            | 160                           |        | 235                  | ns    |

| T <sub>LLWL</sub> | 50  | 100      | 30         | 70                           | 55       | 95                   | 45         | 105                           | 70     | 130                  | ns    |

| T <sub>AVWL</sub> | 75  | 1        | 47         | 1                            | 80       |                      | 70         | Ī                             | 103    |                      | ns    |

| T <sub>QVWX</sub> | 10  | 1        | 7          | 1                            | 15       |                      | 5          | Ī                             | 13     |                      | ns    |

| T <sub>QVWH</sub> | 160 |          | 107        |                              | 165      |                      | 155        |                               | 213    |                      | ns    |

| T <sub>WHQX</sub> | 15  |          | 9          |                              | 17       |                      | 10         |                               | 18     |                      | ns    |

| T <sub>RLAZ</sub> |     | 0        | 1          | 0                            |          | 0                    |            | 0                             |        | 0                    | ns    |

| T <sub>WHLH</sub> | 10  | 40       | 7          | 27                           | 15       | 35                   | 5          | 45                            | 13     | 53                   | ns    |

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | -М | -V | -L | Units |

|-------------------|------|-------------------|-----------|----|----|----|-------|

| T <sub>RLRH</sub> | Min  | 6 T - x           | 3 T - x   | 20 | 15 | 25 | ns    |

| T <sub>WLWH</sub> | Min  | 6 T - x           | 3 T - x   | 20 | 15 | 25 | ns    |

| T <sub>RLDV</sub> | Max  | 5 T - x           | 2.5 T - x | 25 | 23 | 30 | ns    |

| T <sub>RHDX</sub> | Min  | х                 | х         | 0  | 0  | 0  | ns    |

| T <sub>RHDZ</sub> | Max  | 2 T - x           | T - x     | 20 | 15 | 25 | ns    |

| T <sub>LLDV</sub> | Max  | 8 T - x           | 4T -x     | 40 | 35 | 45 | ns    |

| T <sub>AVDV</sub> | Max  | 9 T - x           | 4.5 T - x | 60 | 50 | 65 | ns    |

| T <sub>LLWL</sub> | Min  | 3 T - x           | 1.5 T - x | 25 | 20 | 30 | ns    |

| T <sub>LLWL</sub> | Max  | 3 T + x           | 1.5 T + x | 25 | 20 | 30 | ns    |

| T <sub>AVWL</sub> | Min  | 4 T - x           | 2 T - x   | 25 | 20 | 30 | ns    |

| T <sub>QVWX</sub> | Min  | T - x             | 0.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>QVWH</sub> | Min  | 7 T - x           | 3.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>WHQX</sub> | Min  | T - x             | 0.5 T - x | 10 | 8  | 15 | ns    |

| T <sub>RLAZ</sub> | Max  | х                 | х         | 0  | 0  | 0  | ns    |

| T <sub>WHLH</sub> | Min  | T - x             | 0.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>WHLH</sub> | Max  | T + x             | 0.5 T + x | 15 | 10 | 20 | ns    |

Table 19-10. AC Parameters for a Variable Clock: derating formula

#### 19.5.5 External Data Memory Write Cycle

This diagram indicates when signals are clocked internally. The time it takes the signals to propagate to the pins, however, ranges from 25 to 125 ns. This propagation delay is dependent on variables such as temperature and pin loading. Propagation also varies from output to output and component. Typically though ( $T_A=25^{\circ}C$  fully loaded) RD and WR propagation delays are approximately 50ns. The other signals are typically 85 ns. Propagation delays are incorporated in the AC specifications.

## 20. Ordering Information

Possible Ordering Entries

| Part Number        | Supply Voltage | Temperature Range  | Package | Packing |

|--------------------|----------------|--------------------|---------|---------|

| TS80C54X2xxx-MCA   | -5 to +/-10%   | Commercial         | PDIL40  | Stick   |

| TS80C54X2xxx-MCB   | -5 to +/-10%   | Commercial         | PLCC44  | Stick   |

| TS80C54X2xxx-MCC   | -5 to +/-10%   | Commercial         | PQFP44  | Tray    |

| TS80C54X2xxx-MCE   | -5 to +/-10%   | Commercial         | VQFP44  | Tray    |

| TS80C54X2xxx-VCA   | -5 to +/-10%   | Commercial         | PDIL40  | Stick   |

| TS80C54X2xxx-VCB   | -5 to +/-10%   | Commercial         | PLCC44  | Stick   |

| TS80C54X2xxx-VCC   | -5 to +/-10%   | Commercial         | PQFP44  | Tray    |

| TS80C54X2xxx-VCE   | -5 to +/-10%   | Commercial         | VQFP44  | Tray    |

| TS80C54X2xxx-LCA   | -5 to +/-10%   | Commercial         | PDIL40  | Stick   |

| TS80C54X2xxx-LCB   | -5 to +/-10%   | Commercial         | PLCC44  | Stick   |

| TS80C54X2xxx-LCC   | -5 to +/-10%   | Commercial         | PQFP44  | Tray    |

| TS80C54X2xxx-LCE   | -5 to +/-10%   | Commercial         | VQFP44  | Tray    |

| TS80C54X2xxx-MIA   | -5 to +/-10%   | Industrial         | PDIL40  | Stick   |

| TS80C54X2xxx-MIB   | -5 to +/-10%   | Industrial         | PLCC44  | Stick   |

| TS80C54X2xxx-MIC   | -5 to +/-10%   | Industrial         | PQFP44  | Tray    |

| TS80C54X2xxx-MIE   | -5 to +/-10%   | Industrial         | VQFP44  | Tray    |

| TS80C54X2xxx-VIA   | -5 to +/-10%   | Industrial         | PDIL40  | Stick   |

| TS80C54X2xxx-VIB   | -5 to +/-10%   | Industrial         | PLCC44  | Stick   |

| TS80C54X2xxx-VIC   | -5 to +/-10%   | Industrial         | PQFP44  | Tray    |

| TS80C54X2xxx-VIE   | -5 to +/-10%   | Industrial         | VQFP44  | Tray    |

| TS80C54X2xxx-LIA   | -5 to +/-10%   | Industrial         | PDIL40  | Stick   |

| TS80C54X2xxx-LIB   | -5 to +/-10%   | Industrial         | PLCC44  | Stick   |

| TS80C54X2xxx-LIC   | -5 to +/-10%   | Industrial         | PQFP44  | Tray    |

| TS80C54X2xxx-LIE   | -5 to +/-10%   | Industrial         | VQFP44  | Tray    |

|                    |                |                    |         |         |

| AT80C54X2zzz-3CSUM | -5 to +/-10%   | Industrial & Green | PDIL40  | Stick   |

| AT80C54X2zzz-SLSUM | -5 to +/-10%   | Industrial & Green | PLCC44  | Stick   |

| AT80C54X2zzz-RLTUM | -5 to +/-10%   | Industrial & Green | VQFP44  | Tray    |

| AT80C54X2zzz-3CSUL | -5 to +/-10%   | Industrial & Green | PDIL40  | Stick   |

| AT80C54X2zzz-SLSUL | -5 to +/-10%   | Industrial & Green | PLCC44  | Stick   |

| AT80C54X2zzz-RLTUL | -5 to +/-10%   | Industrial & Green | VQFP44  | Tray    |

| AT80C54X2zzz-3CSUV | -5 to +/-10%   | Industrial & Green | PDIL40  | Stick   |

| AT80C54X2zzz-SLSUV | -5 to +/-10%   | Industrial & Green | PLCC44  | Stick   |

| AT80C54X2zzz-RLTUV | -5 to +/-10%   | Industrial & Green | VQFP44  | Tray    |

| TS87C54X2-MCA      | 5V ±10%        | Commercial         | PDIL40  | Stick   |

| TS87C54X2-MCB      | 5V ±10%        | Commercial         | PLCC44  | Stick   |

## 8 AT/TS8xC54/8X2

58

## AT/TS8xC54/8X2

| Part Number     | Supply Voltage | Temperature Range  | Package | Packing |

|-----------------|----------------|--------------------|---------|---------|

| TS87C54X2-MCC   | 5V ±10%        | Commercial         | PQFP44  | Tray    |

| TS87C54X2-MCE   | 5V ±10%        | Commercial         | VQFP44  | Tray    |