Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                   |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 40/30MHz                                                                |

| Connectivity               | UART/USART                                                              |

| Peripherals                | POR, WDT                                                                |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | 16KB (16K x 8)                                                          |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 256 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                             |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-LCC (J-Lead)                                                         |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/ts87c54x2-vib |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                    | PIN NUMBER |        |          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------|------------|--------|----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MNEMONIC           | DIL        | LCC    | VQFP 1.4 | TYPE  | Name And Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| MNEMONIC           |            | PIN NU | MBER     | TYPE  | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

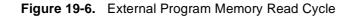

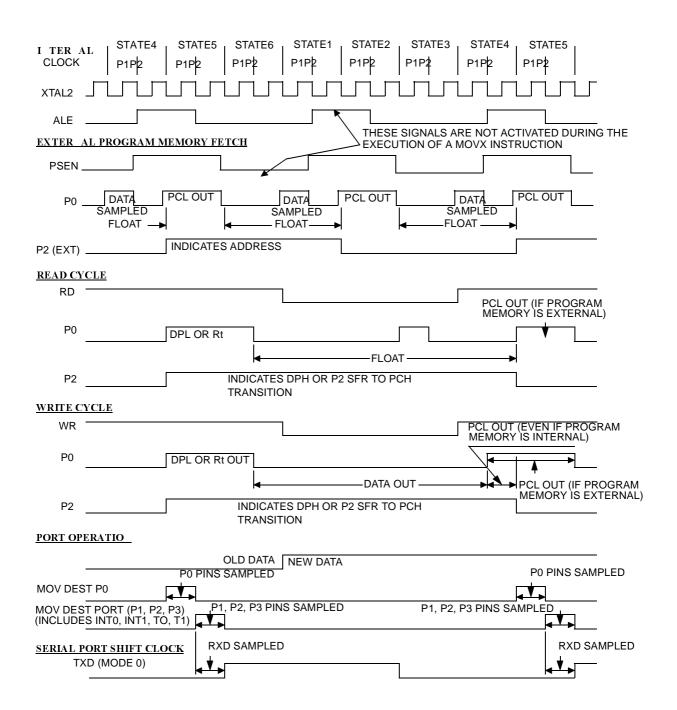

| ALE/PROG           | 30         | 33     | 27       | O (I) | Address Latch Enable/Program Pulse: Output pulse for latching the low byte of the address during an access to external memory. In normal operation, ALE is emitted at a constant rate of 1/6 (1/3 in X2 mode) the oscillator frequency, and can be used for external timing or clocking. Note that one ALE pulse is skipped during each access to external data memory. This pin is also the program pulse input (PROG) during EPROM programming. ALE can be disabled by setting SFR's AUXR.0 bit. With this bit set, ALE will be inactive during internal fetches.                                                                  |

| PSEN               | 29         | 32     | 26       | 0     | <b>Program Store ENable:</b> The read strobe to external program memory. When executing code from the external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory. PSEN is not activated during fetches from internal program memory.                                                                                                                                                                                                                                                                                               |

| ĒĀ/V <sub>PP</sub> | 31         | 35     | 29       | I     | <b>External Access Enable/Programming Supply Voltage:</b> $\overrightarrow{\text{EA}}$ must be externally held<br>low to enable the device to fetch code from external program memory locations 0000H<br>and 3FFFH (54X2) or 7FFFH (58X2). If EA is held high, the device executes from<br>internal program memory unless the program counter contains an address greater<br>than 3FFFH (54X2) or 7FFFH (58X2). This pin also receives the 12.75V programming<br>supply voltage (V <sub>PP</sub> ) during EPROM programming. If security level 1 is programmed,<br>$\overrightarrow{\text{EA}}$ will be internally latched on Reset. |

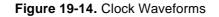

| XTAL1              | 19         | 21     | 15       | I     | <b>Crystal 1:</b> Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| XTAL2              | 18         | 20     | 14       | 0     | Crystal 2: Output from the inverting oscillator amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# **Table 5-1.**Pin Description for 40/44 pin packages

# Table 6-1. CKCON Register CKCON - Clock Control Register (8Fh)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0  |

|---|---|---|---|---|---|---|----|

| - | - | - | - | - | - | - | X2 |

| Bit    | Bit      |                                                                                                                                                                                                                 |

|--------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number | Mnemonic | Description                                                                                                                                                                                                     |

| 7      | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 6      | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 5      | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 4      | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 3      | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 2      | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 1      | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 0      | X2       | <b>CPU and peripheral clock bit</b><br>Clear to select 12 clock periods per machine cycle (STD mode, $F_{OSC}=F_{XTAL}/2$ ).<br>Set to select 6 clock periods per machine cycle (X2 mode, $F_{OSC}=F_{XTAL}$ ). |

Reset Value = XXXX XXX0b Not bit addressable

For further details on the X2 feature, please refer to ANM072 available on the web (http://www.atmel.com)

# 7.1 Application

Software can take advantage of the additional data pointers to both increase speed and reduce code size, for example, block operations (copy, compare, search ...) are well served by using one data pointer as a 'source' pointer and the other one as a "destination" pointer.

### ASSEMBLY LANGUAGE

| ; Block move using dual data pointers<br>; Destroys DPTR0, DPTR1, A and PSW<br>; note: DPS exits opposite of entry state<br>; unless an extra INC AUXR1 is added |       |              |                            |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------|----------------------------|--|--|--|--|--|

| ,<br>00A2                                                                                                                                                        | AUXR  | 1 EQU 0A2H   |                            |  |  |  |  |  |

| ;                                                                                                                                                                |       |              |                            |  |  |  |  |  |

| 0000 909000                                                                                                                                                      | MOV   | DPTR,#SOURCE | ; address of SOURCE        |  |  |  |  |  |

| 0003 05A2                                                                                                                                                        | INC   | AUXR1        | ; switch data pointers     |  |  |  |  |  |

| 0005 90A000                                                                                                                                                      | MOV   | DPTR,#DEST   | ; address of DEST          |  |  |  |  |  |

| 0008                                                                                                                                                             | LOOP: |              |                            |  |  |  |  |  |

| 0008 05A2                                                                                                                                                        | INC   | AUXR1        | ; switch data pointers     |  |  |  |  |  |

| 000A E0                                                                                                                                                          | MOVX  | A, @DPTR     | ; get a byte from SOURCE   |  |  |  |  |  |

| 000B A3                                                                                                                                                          | INC   | DPTR         | ; increment SOURCE address |  |  |  |  |  |

| 000C 05A2                                                                                                                                                        | INC   | AUXR1        | ; switch data pointers     |  |  |  |  |  |

| 000E F0                                                                                                                                                          | MOVX  | @DPTR,A      | ; write the byte to DEST   |  |  |  |  |  |

| 000F A3                                                                                                                                                          | INC   | DPTR         | ; increment DEST address   |  |  |  |  |  |

| 0010 70F6                                                                                                                                                        | JNZ   | LOOP         | ; check for 0 terminator   |  |  |  |  |  |

| 0012 05A2                                                                                                                                                        | INC   | AUXR1        | ; (optional) restore DPS   |  |  |  |  |  |

INC is a short (2 bytes) and fast (12 clocks) way to manipulate the DPS bit in the AUXR1 SFR. However, note that the INC instruction does not directly force the DPS bit to a particular state, but simply toggles it. In simple routines, such as the block move example, only the fact that DPS is toggled in the proper sequence matters, not its actual value. In other words, the block move routine works the same whether DPS is '0' or '1' on entry. Observe that without the last instruction (INC AUXR1), the routine will exit with DPS in the opposite state.

- AMEL

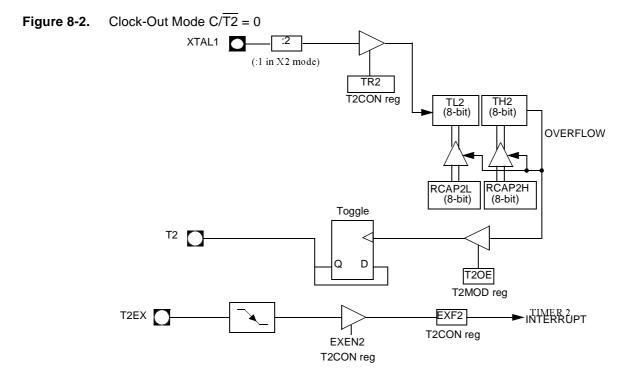

- Enter a 16-bit initial value in timer registers TH2/TL2. It can be the same as the reload value or a different one depending on the application.

- To start the timer, set TR2 run control bit in T2CON register.

It is possible to use timer 2 as a baud rate generator and a clock generator simultaneously. For this configuration, the baud rates and clock frequencies are not independent since both functions use the values in the RCAP2H and RCAP2L registers.

# <sup>16</sup> **AT/TS8xC54/8X2**

| Table 8-2. | T2MOD Register |  |

|------------|----------------|--|

|            |                |  |

| T2MOD - | Timer 2 | Mode | Control | Register (C9h) |

|---------|---------|------|---------|----------------|

|---------|---------|------|---------|----------------|

| 7             | 6               | 5                                 | 4                                                                                                                                   | 3               | 2                   | 1    | 0    |  |  |  |

|---------------|-----------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------|------|------|--|--|--|

| -             | -               | -                                 | -                                                                                                                                   | -               | -                   | T2OE | DCEN |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic |                                   | Description                                                                                                                         |                 |                     |      |      |  |  |  |

| 7             | -               | Reserved<br>The value read        | from this bit is in                                                                                                                 | determinate. Do | o not set this bit. |      |      |  |  |  |

| 6             | -               | Reserved<br>The value read        | eserved<br>ne value read from this bit is indeterminate. Do not set this bit.                                                       |                 |                     |      |      |  |  |  |

| 5             | -               | <b>Reserved</b><br>The value read | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                     |                 |                     |      |      |  |  |  |

| 4             | -               | Reserved<br>The value read        | from this bit is in                                                                                                                 | determinate. Do | o not set this bit. |      |      |  |  |  |

| 3             | -               | Reserved<br>The value read        | from this bit is in                                                                                                                 | determinate. Do | o not set this bit. |      |      |  |  |  |

| 2             | -               | Reserved<br>The value read        | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                     |                 |                     |      |      |  |  |  |

| 1             | T2OE            | Clear to program                  | <b>Timer 2 Output Enable bit</b><br>Clear to program P1.0/T2 as clock input or I/O port.<br>Set to program P1.0/T2 as clock output. |                 |                     |      |      |  |  |  |

| 0             | DCEN            |                                   | Enable bit<br>timer 2 as up/do<br>ner 2 as up/down                                                                                  |                 |                     |      |      |  |  |  |

Reset Value = XXXX XX00b Not bit addressable

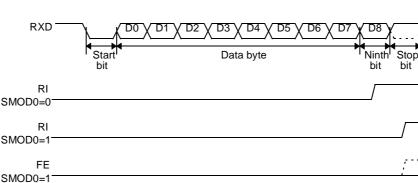

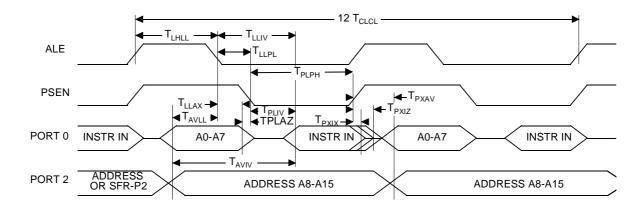

#### Figure 9-3. UART Timings in Modes 2 and 3

## 9.1.1 Automatic Address Recognition

The automatic address recognition feature is enabled when the multiprocessor communication feature is enabled (SM2 bit in SCON register is set).

Implemented in hardware, automatic address recognition enhances the multiprocessor communication feature by allowing the serial port to examine the address of each incoming command frame. Only when the serial port recognizes its own address, the receiver sets RI bit in SCON register to generate an interrupt. This ensures that the CPU is not interrupted by command frames addressed to other devices.

If desired, you may enable the automatic address recognition feature in mode 1. In this configuration, the stop bit takes the place of the ninth data bit. Bit RI is set only when the received command frame address matches the device's address and is terminated by a valid stop bit. To support automatic address recognition, a device is identified by a given address and a broadcast address.

NOTE: The multiprocessor communication and automatic address recognition features cannot be enabled in mode 0 (i.e. setting SM2 bit in SCON register in mode 0 has no effect).

#### 9.1.2 Given Address

Each device has an individual address that is specified in SADDR register; the SADEN register is a mask byte that contains don't-care bits (defined by zeros) to form the device's given address. The don't-care bits provide the flexibility to address one or more slaves at a time. The following example illustrates how a given address is formed.

To address a device by its individual address, the SADEN mask byte must be 1111 1111b. For example:

| SADDR | 0101 0110b        |

|-------|-------------------|

| SADEN | <u>1111 1100b</u> |

| Given | 0101 01XXb        |

### Table 9-1. SADEN - Slave Address Mask Register (B9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b

Not bit addressable

## Table 9-2. SADDR - Slave Address Register (A9h)

|   |   |   |   | ( - ) |   |   |   |

|---|---|---|---|-------|---|---|---|

| 7 | 6 | 5 | 4 | 3     | 2 | 1 | 0 |

|   |   |   |   |       |   |   |   |

Reset Value = 0000 0000b Not bit addressable

# AT/TS8xC54/8X2

# Table 9-3.

SCON Register SCON - Serial Control Register (98h)

| 7             | 6               | 5                                                                                                                                                                                                | 4                                                                                                                                                                                                                                                                   | 3        | 2          | 1 | 0 |  |  |  |

|---------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------|---|---|--|--|--|

| FE/SM0        | SM1             | SM2 REN TB8 RB8 TI F                                                                                                                                                                             |                                                                                                                                                                                                                                                                     |          |            |   |   |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic |                                                                                                                                                                                                  | Description                                                                                                                                                                                                                                                         |          |            |   |   |  |  |  |

| 7             | FE              | Clear to reset th<br>Set by hardware                                                                                                                                                             | Framing Error bit (SMOD0=1)<br>Clear to reset the error state, not cleared by a valid stop bit.<br>Set by hardware when an invalid stop bit is detected.<br>SMOD0 must be set to enable access to the FE bit                                                        |          |            |   |   |  |  |  |

|               | SM0             |                                                                                                                                                                                                  | e bit 0<br>r serial port mode<br>e cleared to enab                                                                                                                                                                                                                  |          | e SM0 bit  |   |   |  |  |  |

| 6             | SM1             |                                                                                                                                                                                                  | 0         0         0         Shift RegisterF <sub>XTAL</sub> /12 (/6 in X2 mode)           0         1         1         8-bit UARTVariable           1         0         2         9-bit UARTF <sub>XTAL</sub> /64 or F <sub>XTAL</sub> /32 (/32, /16 in X2 mode) |          |            |   |   |  |  |  |

| 5             | SM2             | Clear to disable<br>Set to enable m                                                                                                                                                              | Serial port Mode 2 bit / Multiprocessor Communication Enable bit<br>Clear to disable multiprocessor communication feature.<br>Set to enable multiprocessor communication feature in mode 2 and 3, and eventually mode<br>1. This bit should be cleared in mode 0.   |          |            |   |   |  |  |  |

| 4             | REN             | Reception Enal<br>Clear to disable<br>Set to enable set                                                                                                                                          | serial reception.                                                                                                                                                                                                                                                   |          |            |   |   |  |  |  |

| 3             | TB8             | Clear to transmi                                                                                                                                                                                 | / Ninth bit to tra<br>t a logic 0 in the<br>a logic 1 in the 9t                                                                                                                                                                                                     | 9th bit. | s 2 and 3. |   |   |  |  |  |

| 2             | RB8             | Cleared by hard<br>Set by hardware                                                                                                                                                               | Receiver Bit 8 / Ninth bit received in modes 2 and 3<br>Cleared by hardware if 9th bit received is a logic 0.<br>Set by hardware if 9th bit received is a logic 1.<br>In mode 1, if SM2 = 0, RB8 is the received stop bit. In mode 0 RB8 is not used.               |          |            |   |   |  |  |  |

| 1             | ТІ              | Transmit Interrupt flag         Clear to acknowledge interrupt.         Set by hardware at the end of the 8th bit time in mode 0 or at the beginning of the stop bit in the other         modes. |                                                                                                                                                                                                                                                                     |          |            |   |   |  |  |  |

| 0             | RI              | Clear to acknow<br>Set by hardware                                                                                                                                                               | Receive Interrupt flag<br>Clear to acknowledge interrupt.<br>Set by hardware at the end of the 8th bit time in mode 0, see Figure 9-2. and Figure 9-3. in<br>the other modes.                                                                                       |          |            |   |   |  |  |  |

Reset Value = 0000 0000b Bit addressable

If two interrupt requests of different priority levels are received simultaneously, the request of higher priority level is serviced. If interrupt requests of the same priority level are received simultaneously, an internal polling sequence determines which request is serviced. Thus within each priority level there is a second priority structure determined by the polling sequence.

|               | IE - In         | terrupt Enable                                                   | Register (A8                                                                                                                                                                                                      | 3h)             |                   |    |   |  |  |  |

|---------------|-----------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|----|---|--|--|--|

| 7             | 6               | 5                                                                | 4                                                                                                                                                                                                                 | 3               | 2                 | 1  | 0 |  |  |  |

| EA            | -               | ET2                                                              | ET2 ES ET1 EX1 ET0 EX                                                                                                                                                                                             |                 |                   |    |   |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic |                                                                  | Description                                                                                                                                                                                                       |                 |                   |    |   |  |  |  |

| 7             | EA              | Clear to disable a<br>Set to enable all in<br>If EA=1, each inte | able All interrupt bit<br>ear to disable all interrupts.<br>et to enable all interrupts.<br>EA=1, each interrupt source is individually enabled or disabled by setting or clearing its<br>n interrupt enable bit. |                 |                   |    |   |  |  |  |

| 6             | -               | Reserved<br>The value read fro                                   | om this bit is in                                                                                                                                                                                                 | determinate. Do | o not set this bi | t. |   |  |  |  |

| 5             | ET2             | Clear to disable ti                                              | imer 2 overflow interrupt Enable bit<br>Clear to disable timer 2 overflow interrupt.<br>Set to enable timer 2 overflow interrupt.                                                                                 |                 |                   |    |   |  |  |  |

| 4             | ES              | Serial port Enable<br>Clear to disable s<br>Set to enable seri   | erial port interr                                                                                                                                                                                                 |                 |                   |    |   |  |  |  |

| 3             | ET1             | Clear to disable ti                                              | imer 1 overflow interrupt Enable bit<br>Clear to disable timer 1 overflow interrupt.<br>Set to enable timer 1 overflow interrupt.                                                                                 |                 |                   |    |   |  |  |  |

| 2             | EX1             | Clear to disable e                                               | xternal interrupt 1 Enable bit<br>Clear to disable external interrupt 1.<br>Set to enable external interrupt 1.                                                                                                   |                 |                   |    |   |  |  |  |

| 1             | ET0             | Clear to disable ti                                              | imer 0 overflow interrupt Enable bit<br>Clear to disable timer 0 overflow interrupt.<br>Set to enable timer 0 overflow interrupt.                                                                                 |                 |                   |    |   |  |  |  |

| 0             | EX0             | External interrupt<br>Clear to disable e<br>Set to enable exte   | xternal interrup                                                                                                                                                                                                  |                 |                   |    |   |  |  |  |

Table 10-2. IE Register

Reset Value = 0X00 0000b Bit addressable

| 7             | 6               |                                                | 5                                              | 4                                                       | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2                                                                                                                       | 1                                                                                     | 0 |

|---------------|-----------------|------------------------------------------------|------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---|

| T4            | Т3              |                                                | T2         T1         T0         S2         S1 |                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                         |                                                                                       |   |

| Bit<br>Number | Bit<br>Mnemonic |                                                |                                                |                                                         | Descri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ption                                                                                                                   |                                                                                       |   |

| 7             | T4              |                                                |                                                |                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                         |                                                                                       |   |

| 6             | Т3              |                                                |                                                |                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                         |                                                                                       |   |

| 5             | T2              | Reserv                                         |                                                | or clear this b                                         | it                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                         |                                                                                       |   |

| 4             | T1              | Donot                                          |                                                |                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                         |                                                                                       |   |

| 3             | T0              |                                                |                                                |                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                         |                                                                                       |   |

| 2             | S2              | WDT Ti                                         | me-out se                                      | elect bit 2                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                         |                                                                                       |   |

| 1             | S1              | WDT Ti                                         | ime-out se                                     | elect bit 1                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                         |                                                                                       |   |

| 0             | S0              | WDT Ti                                         | me-out s                                       | elect bit 0                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                         |                                                                                       |   |

|               |                 | <u>S2S1</u><br>0<br>0<br>0<br>1<br>1<br>1<br>1 | <u>S0</u><br>0<br>1<br>1<br>0<br>0<br>1        | <u>Selected</u><br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | $\begin{array}{l} \hline \mbox{Imme-out} \\ (2^{14} - 1) machir \\ (2^{15} - 1) machir \\ (2^{16} - 1) machir \\ (2^{17} - 1) machir \\ (2^{18} - 1) machir \\ (2^{19} - 1) machir \\ (2^{20} - 1) machir \\ (2^{21} - 1) mach$ | ne cycles, 32.7 m<br>ne cycles, 65.5 m<br>ne cycles, 131 m<br>ne cycles, 262 m<br>ne cycles, 542 m<br>ne cycles, 1.05 s | ms @ 12 MHz<br>ms @ 12 MHz<br>ns @ 12 MHz<br>ns @ 12 MHz<br>ns @ 12 MHz<br>s @ 12 MHz |   |

#### Table 12-2. WDTPRG Register WDTPRG Address (0A7h)

Reset value XXXX X000

### 12.1.1 WDT during Power Down and Idle

In Power Down mode the oscillator stops, which means the WDT also stops. While in Power Down mode the user does not need to service the WDT. There are 2 methods of exiting Power Down mode: by a hardware reset or via a level activated external interrupt which is enabled prior to entering Power Down mode. When Power Down is exited with hardware reset, servicing the WDT should occur as it normally should whenever the TS80C54/58X2 is reset. Exiting Power Down with an interrupt is significantly different. The interrupt is held low long enough for the oscillator to stabilize. When the interrupt is brought high, the interrupt is serviced. To prevent the WDT from resetting the device while the interrupt pin is held low, the WDT is not started until the interrupt is pulled high. It is suggested that the WDT be reset during the interrupt service routine.

To ensure that the WDT does not overflow within a few states of exiting of powerdown, it is best to reset the WDT just before entering powerdown.

In the Idle mode, the oscillator continues to run. To prevent the WDT from resetting the TS80C54/58X2 while in Idle mode, the user should always set up a timer that will periodically exit Idle, service the WDT, and re-enter Idle mode.

# 13. ONCE<sup>™</sup> Mode (ON Chip Emulation)

The ONCE mode facilitates testing and debugging of systems using TS80C54/58X2 without removing the circuit from the board. The ONCE mode is invoked by driving certain pins of the TS80C54/58X2; the following sequence must be exercised:

- Pull ALE low while the device is in reset (RST high) and PSEN is high.

- Hold ALE low as RST is deactivated.

While the TS80C54/58X2 is in ONCE mode, an emulator or test CPU can be used to drive the circuit Table 13-1 shows the status of the port pins during ONCE mode.

Normal operation is restored when normal reset is applied.

Table 13-1. External Pin Status during ONCE Mode

| ALE          | PSEN         | Port 0 | Port 1       | Port 2       | Port 3       | XTAL1/2 |

|--------------|--------------|--------|--------------|--------------|--------------|---------|

| Weak pull-up | Weak pull-up | Float  | Weak pull-up | Weak pull-up | Weak pull-up | Active  |

.

^

# 15. Reduced EMI Mode

Г

The ALE signal is used to demultiplex address and data buses on port 0 when used with external program or data memory. Nevertheless, during internal code execution, ALE signal is still generated. In order to reduce EMI, ALE signal can be disabled by setting AO bit.

The AO bit is located in AUXR register at bit location 0. As soon as AO is set, ALE is no longer output but remains active during MOVX and MOVC instructions and external fetches. During ALE disabling, ALE pin is weakly pulled high.

2 2

| 7             | 6               | 5                                 | 4                                                                               | 3                                   | 2                 | 1        | 0  |  |  |  |

|---------------|-----------------|-----------------------------------|---------------------------------------------------------------------------------|-------------------------------------|-------------------|----------|----|--|--|--|

| -             | -               | -                                 | -                                                                               | -                                   | -                 | RESERVED | AO |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic |                                   | Description                                                                     |                                     |                   |          |    |  |  |  |

| 7             | -               | <b>Reserved</b><br>The value read | eserved<br>ne value read from this bit is indeterminate. Do not set this bit.   |                                     |                   |          |    |  |  |  |

| 6             | -               | Reserved<br>The value read        | d from this bit is                                                              | s indeterminate                     | . Do not set this | s bit.   |    |  |  |  |

| 5             | -               | Reserved<br>The value read        | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                                     |                   |          |    |  |  |  |

| 4             | -               | Reserved<br>The value read        | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                                     |                   |          |    |  |  |  |

| 3             | -               | Reserved<br>The value read        | d from this bit is                                                              | s indeterminate                     | . Do not set this | s bit.   |    |  |  |  |

| 2             | -               | Reserved<br>The value read        | eserved<br>he value read from this bit is indeterminate. Do not set this bit.   |                                     |                   |          |    |  |  |  |

| 1             | -               | Reserved<br>The value read        | teserved<br>he value read from this bit is indeterminate. Do not set this bit.  |                                     |                   |          |    |  |  |  |

| 0             | AO              |                                   | e ALE operatio                                                                  | n during interna<br>during internal |                   |          |    |  |  |  |

Table 15-1.AUXR Register

AUXR - Auxiliary Register (8Eh)

Reset Value = XXXX XXX0b Not bit addressable

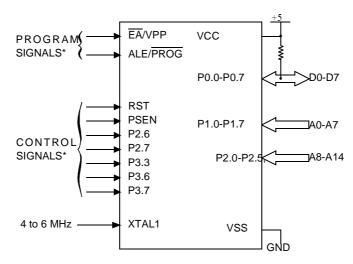

\* See Table 31. for proper value on these inputs

## 17.3.3 Programming Algorithm

The Improved Quick Pulse algorithm is based on the Quick Pulse algorithm and decreases the number of pulses applied during byte programming from 25 to 1.

To program the TS80C54/58X2 the following sequence must be exercised:

- Step 1: Activate the combination of control signals.

- Step 2: Input the valid address on the address lines.

- Step 3: Input the appropriate data on the data lines.

- Step 4: Raise EA/VPP from VCC to VPP (typical 12.75V).

- Step 5: Pulse ALE/PROG once.

- Step 6: Lower EA/VPP from VPP to VCC

Repeat step 2 through 6 changing the address and data for the entire array or until the end of the object file is reached (See Figure 17-2.).

## 17.3.4 Verify algorithm

Code array verify must be done after each byte or block of bytes is programmed. In either case, a complete verify of the programmed array will ensure reliable programming of the TS87C54/58X2.

P 2.7 is used to enable data output.

To verify the TS87C54/58X2 code the following sequence must be exercised:

- Step 1: Activate the combination of program and control signals.

- Step 2: Input the valid address on the address lines.

- Step 3: Read data on the data lines.

Repeat step 2 through 3 changing the address for the entire array verification (See Figure 17-2.)

# AT/TS8xC54/8X2

| Table 18-1. | Signature B | ytes Content |

|-------------|-------------|--------------|

|-------------|-------------|--------------|

| Location | Contents | Comment                                                 |  |  |

|----------|----------|---------------------------------------------------------|--|--|

| 30h      | 58h      | Manufacturer Code: Atmel Wireless &<br>Microcontrollers |  |  |

| 31h      | 57h      | Family Code: C51 X2                                     |  |  |

| 60h      | 37h      | Product name: TS80C58X2                                 |  |  |

| 60h      | B7h      | Product name: TS87C58X2                                 |  |  |

| 60h      | 3Bh      | Product name: TS80C54X2                                 |  |  |

| 60h      | BBh      | Product name: TS87C54X2                                 |  |  |

| 61h      | FFh      | Product revision number                                 |  |  |

# 19.4 DC Parameters for Low Voltage

TA = 0°C to +70°C;  $V_{SS} = 0$  V;  $V_{CC} = 2.7$  V to 5.5 V ± 10%; F = 0 to 30 MHz. TA = -40°C to +85°C;  $V_{SS} = 0$  V;  $V_{CC} = 2.7$  V to 5.5 V ± 10%; F = 0 to 30 MHz.

|  | Table 19-2. | DC Parameters for Low Voltage |

|--|-------------|-------------------------------|

|--|-------------|-------------------------------|

| Symbol                            | Parameter                                                    | Min                       | Тур                                    | Max                                                | Unit | Test Conditions                                                                                      |

|-----------------------------------|--------------------------------------------------------------|---------------------------|----------------------------------------|----------------------------------------------------|------|------------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>                   | Input Low Voltage                                            | -0.5                      |                                        | 0.2 V <sub>CC</sub> - 0.1                          | V    |                                                                                                      |

| V <sub>IH</sub>                   | Input High Voltage except XTAL1, RST                         | 0.2 V <sub>CC</sub> + 0.9 |                                        | V <sub>CC</sub> + 0.5                              | V    |                                                                                                      |

| V <sub>IH1</sub>                  | Input High Voltage, XTAL1, RST                               | 0.7 V <sub>CC</sub>       |                                        | V <sub>CC</sub> + 0.5                              | V    |                                                                                                      |

| V <sub>OL</sub>                   | Output Low Voltage, ports 1, 2, 3 (6)                        |                           |                                        | 0.45                                               | V    | $I_{OL} = 0.8 \text{ mA}^{(4)}$                                                                      |

| V <sub>OL1</sub>                  | Output Low Voltage, port 0, ALE, PSEN (6)                    |                           |                                        | 0.45                                               | V    | I <sub>OL</sub> = 1.6 mA <sup>(4)</sup>                                                              |

| V <sub>OH</sub>                   | Output High Voltage, ports 1, 2, 3                           | 0.9 V <sub>CC</sub>       |                                        |                                                    | V    | I <sub>OH</sub> = -10 μA                                                                             |

| V <sub>OH1</sub>                  | Output High Voltage, port 0, ALE, PSEN                       | 0.9 V <sub>CC</sub>       |                                        |                                                    | V    | I <sub>OH</sub> = -40 μA                                                                             |

| I <sub>IL</sub>                   | Logical 0 Input Current ports 1, 2 and 3                     |                           |                                        | -50                                                | μΑ   | Vin = 0.45 V                                                                                         |