Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                   |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 30/20MHz                                                                |

| Connectivity               | UART/USART                                                              |

| Peripherals                | POR, WDT                                                                |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 256 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | <u>.</u>                                                                |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-QFP                                                                  |

| Supplier Device Package    | 44-PQFP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/ts87c58x2-lcc |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 4-1. | All SFRs with their address and their reset value |

|------------|---------------------------------------------------|

|            |                                                   |

|     | Bit<br>address-<br>able |                    |                     | Nor                 | ) Bit address    | able             |                     |                     |     |

|-----|-------------------------|--------------------|---------------------|---------------------|------------------|------------------|---------------------|---------------------|-----|

|     | 0/8                     | 1/9                | 2/A                 | 3/B                 | 4/C              | 5/D              | 6/E                 | 7/F                 |     |

| F8h |                         |                    |                     |                     |                  |                  |                     |                     | FFh |

| F0h | B<br>0000 0000          |                    |                     |                     |                  |                  |                     |                     | F7h |

| E8h |                         |                    |                     |                     |                  |                  |                     |                     | EFh |

| E0h | ACC<br>0000 0000        |                    |                     |                     |                  |                  |                     |                     | E7h |

| D8h |                         |                    |                     |                     |                  |                  |                     |                     | DFh |

| D0h | PSW<br>0000 0000        |                    |                     |                     |                  |                  |                     |                     | D7h |

| C8h | T2CON<br>0000 0000      | T2MOD<br>XXXX XX00 | RCAP2L<br>0000 0000 | RCAP2H<br>0000 0000 | TL2<br>0000 0000 | TH2<br>0000 0000 |                     |                     | CFh |

| C0h |                         |                    |                     |                     |                  |                  |                     |                     | C7h |

| B8h | IP<br>XX00 0000         | SADEN<br>0000 0000 |                     |                     |                  |                  |                     |                     | BFh |

| B0h | P3<br>1111 1111         |                    |                     |                     |                  |                  |                     | IPH<br>XX00 0000    | B7h |

| A8h | IE<br>0X00 0000         | SADDR<br>0000 0000 |                     |                     |                  |                  |                     |                     | AFh |

| A0h | P2<br>1111 1111         |                    | AUXR1<br>XXXX 0XX0  |                     |                  |                  | WDTRST<br>XXXX XXXX | WDTPRG<br>XXXX X000 | A7h |

| 98h | SCON<br>0000 0000       | SBUF<br>XXXX XXXX  |                     |                     |                  |                  |                     |                     | 9Fh |

| 90h | P1<br>1111 1111         |                    |                     |                     |                  |                  |                     |                     | 97h |

| 88h | TCON<br>0000 0000       | TMOD<br>0000 0000  | TL0<br>0000 0000    | TL1<br>0000 0000    | TH0<br>0000 0000 | TH1<br>0000 0000 | AUXR<br>XXXX XXX0   | CKCON<br>XXXX XXX0  | 8Fh |

| 80h | P0<br>1111 1111         | SP<br>0000 0111    | DPL<br>0000 0000    | DPH<br>0000 0000    |                  |                  |                     | PCON<br>00X1 0000   | 87h |

|     | 0/8                     | 1/9                | 2/A                 | 3/B                 | 4/C              | 5/D              | 6/E                 | 7/F                 | 1   |

reserved

## Table 5-1. Pin Description for 40/44 pin packages

|                 |       | PIN NUMBER   |              | TVDE |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|-----------------|-------|--------------|--------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MNEMONIC        | DIL   | LCC          | VQFP 1.4     | TYPE | Name And Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| V <sub>SS</sub> | 20    | 22           | 16           | I    | Ground: 0V reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| Vss1            |       | 1            | 39           | I    | Optional Ground: Contact the Sales Office for ground connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| V <sub>CC</sub> | 40    | 44           | 38           | I    | <b>Power Supply:</b> This is the power supply voltage for normal, idle and power-down operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| P0.0-P0.7       | 39-32 | 43-36        | 37-30        | I/O  | <b>Port 0</b> : Port 0 is an open-drain, bidirectional I/O port. Port 0 pins that have 1s written t them float and can be used as high impedance inputs. Port 0 pins must be polarized t Vcc or Vss in order to prevent any parasitic current consumption. Port 0 is also the multiplexed low-order address and data bus during access to external program and data memory. In this application, it uses strong internal pull-up when emitting 1s. Port also inputs the code bytes during EPROM programming. External pull-ups are require during program verification during which P0 outputs the code bytes.                                                                                                            |  |  |

| P1.0-P1.7       | 1-8   | 2-9          | 40-44<br>1-3 | I/O  | Port 1: Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. Port 1 pins that<br>have 1s written to them are pulled high by the internal pull-ups and can be used as<br>inputs. As inputs, Port 1 pins that are externally pulled low will source current because<br>of the internal pull-ups. Port 1 also receives the low-order address byte during memory<br>programming and verification.<br>Alternate functions for Port 1 include:                                                                                                                                                                                                                                                                     |  |  |

|                 | 1     | 2            | 40           | I/O  | T2 (P1.0): Timer/Counter 2 external count input/Clockout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|                 | 2     | 3            | 41           | I    | T2EX (P1.1): Timer/Counter 2 Reload/Capture/Direction Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|                 |       |              |              |      | have 1s written to them are pulled high by the internal pull-ups and can be used as<br>inputs. As inputs, Port 2 pins that are externally pulled low will source current becaus<br>of the internal pull-ups. Port 2 emits the high-order address byte during fetches from<br>external program memory and during accesses to external data memory that use 16<br>bit addresses (MOVX @DPTR).In this application, it uses strong internal pull-ups<br>emitting 1s. During accesses to external data memory that use 8-bit addresses (MOV<br>@Ri), port 2 emits the contents of the P2 SFR. Some Port 2 pins receive the high order<br>address bits during EPROM programming and verification:<br>P2.0 to P2.5 for A8 to A13 |  |  |

| P3.0-P3.7       | 10-17 | 11,<br>13-19 | 5,<br>7-13   | I/O  | <b>Port 3:</b> Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally pulled low will source current becaus of the internal pull-ups. Some Port 3 pin P3.4 receive the high order address bits durin EPROM programming and verification for TS8xC58X2 devices.<br>Port 3 also serves the special features of the 80C51 family, as listed below.                                                                                                                                                                                                        |  |  |

|                 | 10    | 11           | 5            | I    | RXD (P3.0): Serial input port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|                 | 11    | 13           | 7            | 0    | TXD (P3.1): Serial output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|                 | 12    | 14           | 8            | 1    | INT0 (P3.2): External interrupt 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                 | 13    | 15           | 9            | 1    | INT1 (P3.3): External interrupt 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                 | 14    | 16           | 10           | I    | T0 (P3.4): Timer 0 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                 | 15    | 17           | 11           | I    | T1 (P3.5): Timer 1 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                 | 16    | 18           | 12           | 0    | WR (P3.6): External data memory write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|                 | 17    | 19           | 13           | 0    | <b>RD (P3.7):</b> External data memory read strobe<br>P3.4 also receives A14 during TS87C58X2 EPROM Programming.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| Reset           | 9     | 10           | 4            | I    | <b>Reset:</b> A high on this pin for two machine cycles while the oscillator is running, reset the device. An internal diffused resistor to $V_{SS}$ permits a power-on reset using only ar external capacitor to $V_{CC}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

## 6. TS80C54/58X2 Enhanced Features

In comparison to the original 80C52, the TS80C54/58X2 implements some new features, which are:

- The X2 option.

- The Dual Data Pointer.

- The Watchdog.

- The 4 level interrupt priority system.

- The power-off flag.

- The ONCE mode.

- The ALE disabling.

- Some enhanced features are also located in the UART and the timer 2.

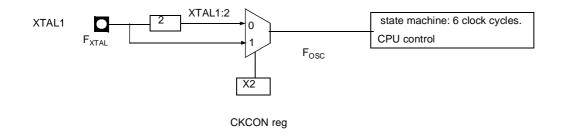

### 6.1 X2 Feature

The TS80C54/58X2 core needs only 6 clock periods per machine cycle. This feature called "X2" provides the following advantages:

- Divide frequency crystals by 2 (cheaper crystals) while keeping same CPU power.

- Save power consumption while keeping same CPU power (oscillator power saving).

- Save power consumption by dividing dynamically operating frequency by 2 in operating and idle modes.

- Increase CPU power by 2 while keeping same crystal frequency.

In order to keep the original C51 compatibility, a divider by 2 is inserted between the XTAL1 signal and the main clock input of the core (phase generator). This divider may be disabled by software.

#### 6.1.1 Description

The clock for the whole circuit and peripheral is first divided by two before being used by the CPU core and peripherals. This allows any cyclic ratio to be accepted on XTAL1 input. In X2 mode, as this divider is bypassed, the signals on XTAL1 must have a cyclic ratio between 40 to 60%. Figure 6-2. shows the clock generation block diagram. X2 bit is validated on XTAL1÷2 rising edge to avoid glitches when switching from X2 to STD mode. Figure 6-2. shows the mode switching waveforms.

#### Figure 6-1. Clock Generation Diagram

# 8 AT/TS8xC54/8X2

# Table 6-1. CKCON Register CKCON - Clock Control Register (8Fh)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0  |

|---|---|---|---|---|---|---|----|

| - | - | - | - | - | - | - | X2 |

| Bit    | Bit      |                                                                                                                                                                                                                 |

|--------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number | Mnemonic | Description                                                                                                                                                                                                     |

| 7      | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 6      | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 5      | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 4      | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 3      | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 2      | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 1      | -        | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                          |

| 0      | X2       | <b>CPU and peripheral clock bit</b><br>Clear to select 12 clock periods per machine cycle (STD mode, $F_{OSC}=F_{XTAL}/2$ ).<br>Set to select 6 clock periods per machine cycle (X2 mode, $F_{OSC}=F_{XTAL}$ ). |

Reset Value = XXXX XXX0b Not bit addressable

For further details on the X2 feature, please refer to ANM072 available on the web (http://www.atmel.com)

## 8. Timer 2

The timer 2 in the TS80C54/58X2 is compatible with the timer 2 in the 80C52.

It is a 16-bit timer/counter: the count is maintained by two eight-bit timer registers, TH2 and TL2, connected in cascade. It is controlled by T2CON register (See Table 8-1) and T2MOD register (See Table 8-2). Timer 2 operation is similar to Timer 0 and Timer 1. C/T2 selects  $F_{OSC}/12$  (timer operation) or external pin T2 (counter operation) as the timer clock input. Setting TR2 allows TL2 to be incremented by the selected input.

Timer 2 has 3 operating modes: capture, autoreload and Baud Rate Generator. These modes are selected by the combination of RCLK, TCLK and CP/RL2 (T2CON), as described in the Atmel Wireless & Microcontrollers 8-bit Microcontroller Hardware description.

Refer to the Atmel Wireless & Microcontrollers 8-bit Microcontroller Hardware description for the description of Capture and Baud Rate Generator Modes.

In TS80C54/58X2 Timer 2 includes the following enhancements:

- Auto-reload mode with up or down counter

- Programmable clock-output

### 8.1 Auto-Reload Mode

The auto-reload mode configures timer 2 as a 16-bit timer or event counter with automatic reload. If DCEN bit in T2MOD is cleared, timer 2 behaves as in 80C52 (refer to the Atmel Wireless & Microcontrollers 8-bit Microcontroller Hardware description). If DCEN bit is set, timer 2 acts as an Up/down timer/counter as shown in Figure 8-1. In this mode the T2EX pin controls the direction of count.

When T2EX is high, timer 2 counts up. Timer overflow occurs at FFFFh which sets the TF2 flag and generates an interrupt request. The overflow also causes the 16-bit value in RCAP2H and RCAP2L registers to be loaded into the timer registers TH2 and TL2.

When T2EX is low, timer 2 counts down. Timer underflow occurs when the count in the timer registers TH2 and TL2 equals the value stored in RCAP2H and RCAP2L registers. The underflow sets TF2 flag and reloads FFFFh into the timer registers.

The EXF2 bit toggles when timer 2 overflows or underflows according to the the direction of the count. EXF2 does not generate any interrupt. This bit can be used to provide 17-bit resolution

# AT/TS8xC54/8X2

| Table 8-1. | T2CON Register |

|------------|----------------|

|------------|----------------|

T2CON - Timer 2 Control Register (C8h)

| 7             | 6               | N - Timer 2 Co<br>5                                                                                        | 4                                  | 3                   | 2                | 1              | 0                |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------|------------------|----------------|------------------|

| TF2           | EXF2            | RCLK                                                                                                       | TCLK                               | EXEN2               | TR2              | C/T2#          | CP/RL2#          |

| Bit<br>Number | Bit<br>Mnemonic |                                                                                                            |                                    | Descrip             | tion             |                |                  |

| 7             | TF2             | Timer 2 overflow<br>Must be cleared b<br>Set by hardware c                                                 | y software.                        | flow, if RCLK =     | 0 and TCLK =     | 0.             |                  |

| 6             | EXF2            | Timer 2 External F<br>Set when a captur<br>When set, causes<br>enabled.<br>Must be cleared b<br>(DCEN = 1) | re or a reload is<br>the CPU to ve | ector to timer 2 ir | nterrupt routine | when timer 2 i | nterrupt is      |

| 5             | RCLK            | Receive Clock bit<br>Clear to use timer<br>Set to use timer 2                                              |                                    |                     |                  |                |                  |

| 4             | TCLK            | Transmit Clock bit<br>Clear to use timer<br>Set to use timer 2                                             | 1 overflow as                      |                     |                  |                |                  |

| 3             | EXEN2           | Timer 2 External E<br>Clear to ignore ev<br>Set to cause a cap<br>2 is not used to clu                     | ents on T2EX<br>oture or reload    | when a negative     |                  | T2EX pin is de | tected, if timer |

| 2             | TR2             | Timer 2 Run contr<br>Clear to turn off tir<br>Set to turn on time                                          | mer 2.                             |                     |                  |                |                  |

| 1             | C/T2#           | Timer/Counter 2<br>Clear for timer ope<br>Set for counter op<br>out mode.                                  | eration (input fi                  |                     |                  |                | e 0 for clock    |

| 0             | CP/RL2#         | Timer 2 Capture/F<br>If RCLK=1 or TCL<br>overflow.<br>Clear to auto-reloa<br>Set to capture on             | K=1, CP/RL2#<br>ad on timer 2 c    | overflows or neg    | ative transition | s on T2EX pin  |                  |

Reset Value = 0000 0000b Bit addressable

#### Table 9-1. SADEN - Slave Address Mask Register (B9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b

Not bit addressable

#### Table 9-2. SADDR - Slave Address Register (A9h)

|   |   |   |   | ( - ) |   |   |   |

|---|---|---|---|-------|---|---|---|

| 7 | 6 | 5 | 4 | 3     | 2 | 1 | 0 |

|   |   |   |   |       |   |   |   |

Reset Value = 0000 0000b Not bit addressable

The encryption array cannot be directly verified. Verification of the encryption array is done by observing that the code array is well encrypted.

### 17.4 EPROM Erasure (Windowed Packages Only)

Erasing the EPROM erases the code array, the encryption array and the lock bits returning the parts to full functionality.

Erasure leaves all the EPROM cells in a 1's state (FF).

#### 17.4.1 Erasure Characteristics

The recommended erasure procedure is exposure to ultraviolet light (at 2537 Å) to an integrated dose at least 15 W-sec/cm<sup>2</sup>. Exposing the EPROM to an ultraviolet lamp of 12,000  $\mu$ W/cm<sup>2</sup> rating for 30 minutes, at a distance of about 25 mm, should be sufficient. An exposure of 1 hour is recommended with most of standard erasers.

Erasure of the EPROM begins to occur when the chip is exposed to light with wavelength shorter than approximately 4,000 Å. Since sunlight and fluorescent lighting have wavelengths in this range, exposure to these light sources over an extended time (about 1 week in sunlight, or 3 years in room-level fluorescent lighting) could cause inadvertent erasure. If an application subjects the device to this type of exposure, it is suggested that an opaque label be placed over the window.

## 18. Signature Bytes

The TS87C54/58X2 has four signature bytes in location 30h, 31h, 60h and 61h. To read these bytes follow the procedure for EPROM verify but activate the control lines provided in Table 31. for Read Signature Bytes. Table 18-1. shows the content of the signature byte for the TS80C54/58X2.

# AT/TS8xC54/8X2

| Table 18-1. | Signature By | tes Content |

|-------------|--------------|-------------|

|-------------|--------------|-------------|

| Location | Contents | Comment                                                 |  |  |

|----------|----------|---------------------------------------------------------|--|--|

| 30h      | 58h      | Manufacturer Code: Atmel Wireless &<br>Microcontrollers |  |  |

| 31h      | 57h      | Family Code: C51 X2                                     |  |  |

| 60h      | 37h      | Product name: TS80C58X2                                 |  |  |

| 60h      | B7h      | Product name: TS87C58X2                                 |  |  |

| 60h      | 3Bh      | Product name: TS80C54X2                                 |  |  |

| 60h      | BBh      | Product name: TS87C54X2                                 |  |  |

| 61h      | FFh      | Product revision number                                 |  |  |

## **19. Electrical Characteristics**

## 19.1 Absolute Maximum Ratings <sup>(1)</sup>

Ambiant Temperature Under Bias: C = commercial0°C to 70°C I = industrial -40°C to 85°C Storage Temperature-65°C to + 150°C Voltage on V<sub>CC</sub> to V<sub>SS</sub>-0.5 V to + 7 V Voltage on V<sub>PP</sub> to V<sub>SS</sub>-0.5 V to + 13 V Voltage on Any Pin to V<sub>SS</sub>-0.5 V to V<sub>CC</sub> + 0.5 V Power Dissipation1 W<sup>(2)</sup>

- 1. Stresses at or above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- 2. This value is based on the maximum allowable die temperature and the thermal resistance of the package.

### **19.2** Power consumption measurement

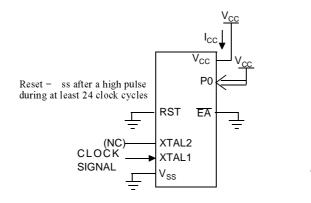

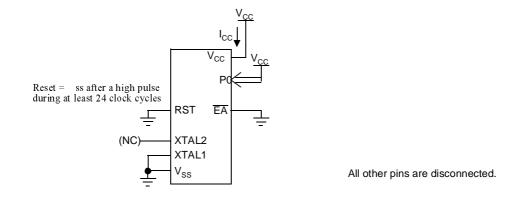

Since the introduction of the first C51 devices, every manufacturer made operating lcc measurements under reset, which made sense for the designs were the CPU was running under reset. In Atmel new devices, the CPU is no more active during reset, so the power consumption is very low but is not really representative of what will happen in the customer system. That's why, while keeping measurements under Reset, Atmel presents a new way to measure the operating lcc:

Using an internal test ROM, the following code is executed:

Label:

SJMP Label (80 FE)

Ports 1, 2, 3 are disconnected, Port 0 is tied to FFh, EA = Vcc, RST = Vss, XTAL2 is not connected and XTAL1 is driven by the clock.

This is much more representative of the real operating Icc.

## 19.3 DC Parameters for Standard Voltage

$\begin{array}{l} T_{A}=0^{\circ}C \ to \ +70^{\circ}C; \ V_{SS}=0 \ V; \ V_{CC}=5 \ V \pm 10\%; \ F=0 \ to \ 40 \ MHz. \\ T_{A}=-40^{\circ}C \ to \ +85^{\circ}C; \ V_{SS}=0 \ V; \ V_{CC}=5 \ V \pm 10\%; \ F=0 \ to \ 40 \ MHz. \end{array}$

| Symbol           | Parameter                                        | Min                       | Тур | Max                       | Unit | Test Conditions                         |

|------------------|--------------------------------------------------|---------------------------|-----|---------------------------|------|-----------------------------------------|

| V <sub>IL</sub>  | Input Low Voltage                                | -0.5                      |     | 0.2 V <sub>CC</sub> - 0.1 | V    |                                         |

| V <sub>IH</sub>  | Input High Voltage except XTAL1, RST             | 0.2 V <sub>CC</sub> + 0.9 |     | V <sub>CC</sub> + 0.5     | V    |                                         |

| V <sub>IH1</sub> | Input High Voltage, XTAL1, RST                   | 0.7 V <sub>CC</sub>       |     | V <sub>CC</sub> + 0.5     | V    |                                         |

|                  |                                                  |                           |     | 0.3                       | V    | $I_{OL} = 100 \ \mu A^{(4)}$            |

| V <sub>OL</sub>  | Output Low Voltage, ports 1, 2, 3 <sup>(6)</sup> |                           |     | 0.45                      | V    | I <sub>OL</sub> = 1.6 mA <sup>(4)</sup> |

|                  |                                                  |                           |     | 1.0                       | V    | $I_{OL} = 3.5 \text{ mA}^{(4)}$         |

Figure 19-3. I<sub>CC</sub> Test Condition, Idle Mode

All other pins are disconnected.

## 19.5 AC Parameters

#### 19.5.1 Explanation of the AC Symbols

Each timing symbol has 5 characters. The first character is always a "T" (stands for time). The other characters, depending on their positions, stand for the name of a signal or the logical status of that signal. The following is a list of all the characters and what they stand for.

Example:  $T_{AVLL}$  = Time for Address Valid to ALE Low.  $T_{ILPL}$  = Time for ALE Low to PSEN Low.

TA = 0 to +70°C (commercial temperature range);  $V_{SS} = 0 \text{ V}$ ;  $V_{CC} = 5 \text{ V} \pm 10\%$ ; -M and -V ranges. TA = -40°C to +85°C (industrial temperature range);  $V_{SS} = 0 \text{ V}$ ;  $V_{CC} = 5 \text{ V} \pm 10\%$ ; -M and -V ranges.

TA = 0 to +70°C (commercial temperature range);  $V_{SS} = 0$  V; 2.7 V <  $V_{CC}$  < 5.5 V; -L range. TA = -40°C to +85°C (industrial temperature range);  $V_{SS} = 0$  V; 2.7 V <  $V_{CC}$  < 5.5 V; -L range.

Table 19-3. gives the maximum applicable load capacitance for Port 0, Port 1, 2 and 3, and ALE and  $\overrightarrow{\text{PSEN}}$  signals. Timings will be guaranteed if these capacitances are respected. Higher capacitance values can be used, but timings will then be degraded.

| í. |              |     |    |     |

|----|--------------|-----|----|-----|

|    |              | -М  | -V | ۰L  |

|    | Port 0       | 100 | 50 | 100 |

|    | Port 1, 2, 3 | 80  | 50 | 80  |

|    | ALE / PSEN   | 100 | 30 | 100 |

Table 19-3. Load Capacitance versus speed range, in pF

Table 19-5., Table 19-8. and Table 19-11. give the description of each AC symbols.

Table 19-6., Table 19-9. and Table 19-12. give for each range the AC parameter.

Table 19-7., Table 19-10. and Table 19-13. give the frequency derating formula of the AC parameter. To calculate each AC symbols, take the x value corresponding to the speed grade you need (-M, -V or -L) and replace this value in the formula. Values of the frequency must be limited to the corresponding speed grade:

Table 19-4.

Max frequency for derating formula regarding the speed grade

|            | -M X1 mode | -M X2 mode | -V X1 mode | -V X2 mode | -L X1 mode | -L X2 mode |

|------------|------------|------------|------------|------------|------------|------------|

| Freq (MHz) | 40         | 20         | 40         | 30         | 30         | 20         |

| T (ns)     | 25         | 50         | 25         | 33.3       | 33.3       | 50         |

Example:

$T_{111V}$  in X2 mode for a -V part at 20 MHz (T = 1/20^{E6} = 50 ns):

x= 22 (Table 19-7.)

T= 50ns

$T_{LLIV} = 2T - x = 2 \times 50 - 22 = 78$ ns

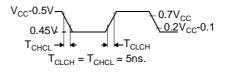

## 19.5.2 External Program Memory Characteristics

## Table 19-5. Symbol Description

| Symbol            | Parameter                         |

|-------------------|-----------------------------------|

| Т                 | Oscillator clock period           |

| T <sub>LHLL</sub> | ALE pulse width                   |

| T <sub>AVLL</sub> | Address Valid to ALE              |

| T <sub>LLAX</sub> | Address Hold After ALE            |

| T <sub>LLIV</sub> | ALE to Valid Instruction In       |

| T <sub>LLPL</sub> | ALE to PSEN                       |

| T <sub>PLPH</sub> | PSEN Pulse Width                  |

| T <sub>PLIV</sub> | PSEN to Valid Instruction In      |

| T <sub>PXIX</sub> | Input Instruction Hold After PSEN |

| T <sub>PXIZ</sub> | Input Instruction FloatAfter PSEN |

| T <sub>PXAV</sub> | PSEN to Address Valid             |

| T <sub>AVIV</sub> | Address to Valid Instruction In   |

| T <sub>PLAZ</sub> | PSEN Low to Address Float         |

Table 19-6.

AC Parameters for Fix Clock

| Speed             |     | M<br>MHz | X2 r<br>30 | V<br>node<br>MHz<br>z equiv. | standard | V<br>I mode 40<br>Hz | X2 n<br>20 | L<br>node<br>MHz<br>z equiv. | standa | L<br>′d mode<br>MHz | Units |

|-------------------|-----|----------|------------|------------------------------|----------|----------------------|------------|------------------------------|--------|---------------------|-------|

| Symbol            | Min | Max      | Min        | Max                          | Min      | Max                  | Min        | Max                          | Min    | Max                 |       |

| Т                 | 25  |          | 33         |                              | 25       |                      | 50         |                              | 33     |                     | ns    |

| T <sub>LHLL</sub> | 40  |          | 25         |                              | 42       |                      | 35         |                              | 52     |                     | ns    |

| T <sub>AVLL</sub> | 10  |          | 4          |                              | 12       |                      | 5          |                              | 13     |                     | ns    |

| T <sub>LLAX</sub> | 10  |          | 4          |                              | 12       |                      | 5          |                              | 13     |                     | ns    |

| T <sub>LLIV</sub> |     | 70       |            | 45                           | l l      | 78                   |            | 65                           |        | 98                  | ns    |

| T <sub>LLPL</sub> | 15  |          | 9          |                              | 17       |                      | 10         |                              | 18     |                     | ns    |

| T <sub>PLPH</sub> | 55  |          | 35         |                              | 60       |                      | 50         |                              | 75     |                     | ns    |

| T <sub>PLIV</sub> |     | 35       |            | 25                           | l l      | 50                   |            | 30                           |        | 55                  | ns    |

| T <sub>PXIX</sub> | 0   |          | 0          |                              | 0        |                      | 0          |                              | 0      |                     | ns    |

| T <sub>PXIZ</sub> |     | 18       |            | 12                           | l l      | 20                   |            | 10                           |        | 18                  | ns    |

| T <sub>AVIV</sub> |     | 85       |            | 53                           |          | 95                   |            | 80                           |        | 122                 | ns    |

| T <sub>PLAZ</sub> |     | 10       |            | 10                           |          | 10                   |            | 10                           |        | 10                  | ns    |

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | -М | -V | -L | Units |

|-------------------|------|-------------------|-----------|----|----|----|-------|

| T <sub>LHLL</sub> | Min  | 2 T - x           | T - x     | 10 | 8  | 15 | ns    |

| T <sub>AVLL</sub> | Min  | T - x             | 0.5 T - x | 15 | 13 | 20 | ns    |

| T <sub>LLAX</sub> | Min  | T - x             | 0.5 T - x | 15 | 13 | 20 | ns    |

| T <sub>LLIV</sub> | Max  | 4 T - x           | 2 T - x   | 30 | 22 | 35 | ns    |

| T <sub>LLPL</sub> | Min  | T - x             | 0.5 T - x | 10 | 8  | 15 | ns    |

| T <sub>PLPH</sub> | Min  | 3 T - x           | 1.5 T - x | 20 | 15 | 25 | ns    |

| T <sub>PLIV</sub> | Max  | 3 T - x           | 1.5 T - x | 40 | 25 | 45 | ns    |

| T <sub>PXIX</sub> | Min  | х                 | х         | 0  | 0  | 0  | ns    |

| T <sub>PXIZ</sub> | Max  | T - x             | 0.5 T - x | 7  | 5  | 15 | ns    |

| T <sub>AVIV</sub> | Max  | 5 T - x           | 2.5 T - x | 40 | 30 | 45 | ns    |

| T <sub>PLAZ</sub> | Max  | х                 | х         | 10 | 10 | 10 | ns    |

Table 19-7. AC Parameters for a Variable Clock: derating formula

#### 19.5.3 External Program Memory Read Cycle

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | -M | -V | -L | Units |

|-------------------|------|-------------------|-----------|----|----|----|-------|

| T <sub>RLRH</sub> | Min  | 6 T - x           | 3 T - x   | 20 | 15 | 25 | ns    |

| T <sub>WLWH</sub> | Min  | 6 T - x           | 3 T - x   | 20 | 15 | 25 | ns    |

| T <sub>RLDV</sub> | Max  | 5 T - x           | 2.5 T - x | 25 | 23 | 30 | ns    |

| T <sub>RHDX</sub> | Min  | х                 | х         | 0  | 0  | 0  | ns    |

| T <sub>RHDZ</sub> | Max  | 2 T - x           | T - x     | 20 | 15 | 25 | ns    |

| T <sub>LLDV</sub> | Max  | 8 T - x           | 4T -x     | 40 | 35 | 45 | ns    |

| T <sub>AVDV</sub> | Max  | 9 T - x           | 4.5 T - x | 60 | 50 | 65 | ns    |

| T <sub>LLWL</sub> | Min  | 3 T - x           | 1.5 T - x | 25 | 20 | 30 | ns    |

| T <sub>LLWL</sub> | Max  | 3 T + x           | 1.5 T + x | 25 | 20 | 30 | ns    |

| T <sub>AVWL</sub> | Min  | 4 T - x           | 2 T - x   | 25 | 20 | 30 | ns    |

| T <sub>QVWX</sub> | Min  | T - x             | 0.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>QVWH</sub> | Min  | 7 T - x           | 3.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>WHQX</sub> | Min  | T - x             | 0.5 T - x | 10 | 8  | 15 | ns    |

| T <sub>RLAZ</sub> | Max  | х                 | х         | 0  | 0  | 0  | ns    |

| T <sub>WHLH</sub> | Min  | T - x             | 0.5 T - x | 15 | 10 | 20 | ns    |

| T <sub>WHLH</sub> | Max  | T + x             | 0.5 T + x | 15 | 10 | 20 | ns    |

Table 19-10. AC Parameters for a Variable Clock: derating formula

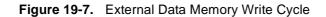

## 19.5.5 External Data Memory Write Cycle

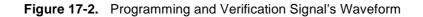

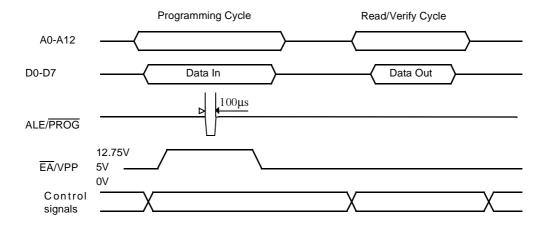

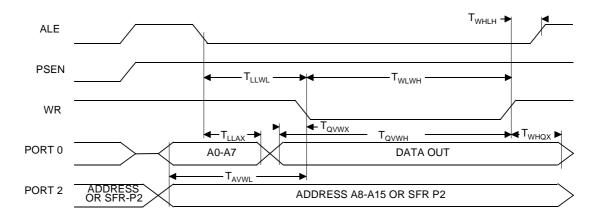

## 19.5.9 EPROM Programming and Verification Characteristics

$T_A$  = 21°C to 27°C;  $V_{SS}$  = 0V;  $V_{CC}$  = 5V  $\pm$  10% while programming.  $V_{CC}$  = operating range while verifying.

| Symbol              | Parameter                         | Min                  | Max                  | Units |

|---------------------|-----------------------------------|----------------------|----------------------|-------|

| V <sub>PP</sub>     | Programming Supply Voltage        | 12.5                 | 13                   | V     |

| I <sub>PP</sub>     | Programming Supply Current        |                      | 75                   | mA    |

| 1/T <sub>CLCL</sub> | Oscillator Frquency               | 4                    | 6                    | MHz   |

| T <sub>AVGL</sub>   | Address Setup to PROG Low         | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>GHAX</sub>   | Adress Hold after PROG            | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>DVGL</sub>   | Data Setup to PROG Low            | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>GHDX</sub>   | Data Hold after PROG              | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>EHSH</sub>   | (Enable) High to V <sub>PP</sub>  | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>SHGL</sub>   | V <sub>PP</sub> Setup to PROG Low | 10                   |                      | μs    |

| T <sub>GHSL</sub>   | V <sub>PP</sub> Hold after PROG   | 10                   |                      | μs    |

| T <sub>GLGH</sub>   | PROG Width                        | 90                   | 110                  | μs    |

| T <sub>AVQV</sub>   | Address to Valid Data             |                      | 48 T <sub>CLCL</sub> |       |

| $T_{ELQV}$          | ENABLE Low to Data Valid          |                      | 48 T <sub>CLCL</sub> |       |

| T <sub>EHQZ</sub>   | Data Float after ENABLE           | 0                    | 48 T <sub>CLCL</sub> |       |

Table 19-14. EPROM Programming Parameters

#### 19.5.10 EPROM Programming and Verification Waveforms

\* 8KB: up to P2.4, 16KB: up to P2.5, 32KB: up to P3.4, 64KB: up to P3.5

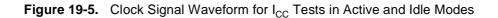

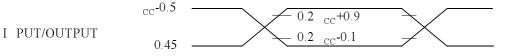

#### 19.5.13 AC Testing Input/Output Waveforms

#### Figure 19-12. AC Testing Input/Output Waveforms

AC inputs during testing are driven at V<sub>CC</sub> - 0.5 for a logic "1" and 0.45V for a logic "0". Timing measurement are made at V<sub>IH</sub> min for a logic "1" and V<sub>IL</sub> max for a logic "0".

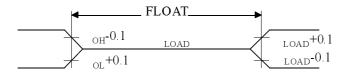

### 19.5.14 Float Waveforms

#### Figure 19-13. Float Waveforms

For timing purposes a port pin is no longer floating when a 100 mV change from load voltage occurs and begins to float when a 100 mV change from the loaded  $V_{OH}/V_{OL}$  level occurs.  $I_{OL}/I_{OH} \ge \pm 20$ mA.

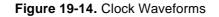

#### 19.5.15 Clock Waveforms

Valid in normal clock mode. In X2 mode XTAL2 signal must be changed to XTAL2 divided by two.

This diagram indicates when signals are clocked internally. The time it takes the signals to propagate to the pins, however, ranges from 25 to 125 ns. This propagation delay is dependent on variables such as temperature and pin loading. Propagation also varies from output to output and component. Typically though ( $T_A=25^{\circ}C$  fully loaded) RD and WR propagation delays are approximately 50ns. The other signals are typically 85 ns. Propagation delays are incorporated in the AC specifications.

# AT/TS8xC54/8X2

| Part Number     | Supply Voltage | Temperature Range  | Package | Packing |

|-----------------|----------------|--------------------|---------|---------|

| TS87C54X2-MCC   | 5V ±10%        | Commercial         | PQFP44  | Tray    |

| TS87C54X2-MCE   | 5V ±10%        | Commercial         | VQFP44  | Tray    |

| TS87C54X2-VCA   | 5V ±10%        | Commercial         | PDIL40  | Stick   |

| TS87C54X2-VCB   | 5V ±10%        | Commercial         | PLCC44  | Stick   |

| TS87C54X2-VCC   | 5V ±10%        | Commercial         | PQFP44  | Tray    |

| TS87C54X2-VCE   | 5V ±10%        | Commercial         | VQFP44  | Tray    |

| TS87C54X2-LCA   | 2.7 to 5.5V    | Commercial         | PDIL40  | Stick   |

| TS87C54X2-LCB   | 2.7 to 5.5V    | Commercial         | PLCC44  | Stick   |

| TS87C54X2-LCC   | 2.7 to 5.5V    | Commercial         | PQFP44  | Tray    |

| TS87C54X2-LCE   | 2.7 to 5.5V    | Commercial         | VQFP44  | Tray    |

| TS87C54X2-MIA   | 5V ±10%        | Industrial         | PDIL40  | Stick   |

| TS87C54X2-MIB   | 5V ±10%        | Industrial         | PLCC44  | Stick   |

| TS87C54X2-MIC   | 5V ±10%        | Industrial         | PQFP44  | Tray    |

| TS87C54X2-MIE   | 5V ±10%        | Industrial         | VQFP44  | Tray    |

| TS87C54X2-VIA   | 5V ±10%        | Industrial         | PDIL40  | Stick   |

| TS87C54X2-VIB   | 5V ±10%        | Industrial         | PLCC44  | Stick   |

| TS87C54X2-VIC   | 5V ±10%        | Industrial         | PQFP44  | Tray    |

| TS87C54X2-VIE   | 5V ±10%        | Industrial         | VQFP44  | Tray    |

| TS87C54X2-LIA   | 2.7 to 5.5V    | Industrial         | PDIL40  | Stick   |

| TS87C54X2-LIB   | 2.7 to 5.5V    | Industrial         | PLCC44  | Stick   |

| TS87C54X2-LIC   | 2.7 to 5.5V    | Industrial         | PQFP44  | Tray    |

| TS87C54X2-LIE   | 2.7 to 5.5V    | Industrial         | VQFP44  | Tray    |

|                 |                |                    |         |         |

| AT87C54X2-3CSUM | 5V ±10%        | Industrial & Green | PDIL40  | Stick   |

| AT87C54X2-SLSUM | 5V ±10%        | Industrial & Green | PLCC44  | Stick   |

| AT87C54X2-RLTUM | 5V ±10%        | Industrial & Green | VQFP44  | Tray    |

| AT87C54X2-3CSUL | 2.7 to 5.5V    | Industrial & Green | PDIL40  | Stick   |

| AT87C54X2-SLSUL | 2.7 to 5.5V    | Industrial & Green | PLCC44  | Stick   |

| AT87C54X2-RLTUL | 2.7 to 5.5V    | Industrial & Green | VQFP44  | Tray    |

| AT87C54X2-3CSUV | 5V ±10%        | Industrial & Green | PDIL40  | Stick   |

| AT87C54X2-SLSUV | 5V ±10%        | Industrial & Green | PLCC44  | Stick   |

| AT87C54X2-RLTUV | 5V ±10%        | Industrial & Green | VQFP44  | Tray    |

# AT/TS8xC54/8X2

| Part Number     | Supply Voltage | Temperature Range  | Package | Packing |

|-----------------|----------------|--------------------|---------|---------|

| TS87C58X2-MCE   | 5V ±10%        | Commercial         | VQFP44  | Tray    |

| TS87C58X2-VCA   | 5V ±10%        | Commercial         | PDIL40  | Stick   |

| TS87C58X2-VCB   | 5V ±10%        | Commercial         | PLCC44  | Stick   |

| TS87C58X2-VCC   | 5V ±10%        | Commercial         | PQFP44  | Tray    |

| TS87C58X2-VCE   | 5V ±10%        | Commercial         | VQFP44  | Tray    |

| TS87C58X2-LCA   | 2.7 to 5.5V    | Commercial         | PDIL40  | Stick   |

| TS87C58X2-LCB   | 2.7 to 5.5V    | Commercial         | PLCC44  | Stick   |

| TS87C58X2-LCC   | 2.7 to 5.5V    | Commercial         | PQFP44  | Tray    |

| TS87C58X2-LCE   | 2.7 to 5.5V    | Commercial         | VQFP44  | Tray    |

| TS87C58X2-MIA   | 5V ±10%        | Industrial         | PDIL40  | Stick   |

| TS87C58X2-MIB   | 5V ±10%        | Industrial         | PLCC44  | Stick   |

| TS87C58X2-MIC   | 5V ±10%        | Industrial         | PQFP44  | Tray    |

| TS87C58X2-MIE   | 5V ±10%        | Industrial         | VQFP44  | Tray    |

| TS87C58X2-VIA   | 5V ±10%        | Industrial         | PDIL40  | Stick   |

| TS87C58X2-VIB   | 5V ±10%        | Industrial         | PLCC44  | Stick   |

| TS87C58X2-VIC   | 5V ±10%        | Industrial         | PQFP44  | Tray    |

| TS87C58X2-VIE   | 5V ±10%        | Industrial         | VQFP44  | Tray    |

| TS87C58X2-LIA   | 2.7 to 5.5V    | Industrial         | PDIL40  | Stick   |

| TS87C58X2-LIB   | 2.7 to 5.5V    | Industrial         | PLCC44  | Stick   |

| TS87C58X2-LIC   | 2.7 to 5.5V    | Industrial         | PQFP44  | Tray    |

| TS87C58X2-LIE   | 2.7 to 5.5V    | Industrial         | VQFP44  | Tray    |

|                 |                |                    |         |         |

| AT87C58X2-3CSUM | 5V ±10%        | Industrial & Green | PDIL40  | Stick   |

| AT87C58X2-SLSUM | 5V ±10%        | Industrial & Green | PLCC44  | Stick   |

| AT87C58X2-RLTUM | 5V ±10%        | Industrial & Green | VQFP44  | Tray    |

| AT87C58X2-3CSUL | 2.7 to 5.5V    | Industrial & Green | PDIL40  | Stick   |

| AT87C58X2-SLSUL | 2.7 to 5.5V    | Industrial & Green | PLCC44  | Stick   |

| AT87C58X2-RLTUL | 2.7 to 5.5V    | Industrial & Green | VQFP44  | Tray    |

| AT87C58X2-3CSUV | 5V ±10%        | Industrial & Green | PDIL40  | Stick   |

| AT87C58X2-SLSUV | 5V ±10%        | Industrial & Green | PLCC44  | Stick   |

| AT87C58X2-RLTUV | 5V ±10%        | Industrial & Green | VQFP44  | Tray    |

## 21. Datasheet Revision History

## 21.1 Changes from Rev. C 01/01 to Rev. D 11/05

1. Added green product Ordering Information.

## 21.2 Changes from Rev. D 11/05 to Rev. E 04/06

1. Changed value of AUXR register.