#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                     | Not For New Designs                                                                                                 |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 1 Core, 32-Bit                                                                                                      |

| Speed                              | 1.0GHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON™ SIMD                                                                                              |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | -                                                                                                                   |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | 0°C ~ 95°C (TJ)                                                                                                     |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-LFBGA                                                                                                           |

| Supplier Device Package            | 624-MAPBGA (21x21)                                                                                                  |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6s5dvm10ab                                             |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Block Mnemonic   | Block Name                            | Subsystem                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------|---------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ENET             | Ethernet Controller                   | Connectivity<br>Peripherals | The Ethernet Media Access Controller (MAC) is<br>designed to support 10/100/1000 Mbps Ethernet/IEEE<br>802.3 networks. An external transceiver interface and<br>transceiver function are required to complete the<br>interface to the media. The module has dedicated<br>hardware to support the IEEE 1588 standard. See the<br>ENET chapter of the reference manual for details.<br><b>Note:</b> The theoretical maximum performance of 1 Gbps<br>ENET is limited to 470 Mbps (total for Tx and Rx) due to<br>internal bus throughput limitations. The actual<br>measured performance in optimized environment is up<br>to 400 Mbps. For details, see the ERR004512 erratum<br>in the i.MX 6Solo/6DualLite errata document<br>(IMX6SDLCE).                                                                                                                                                                                                                                                             |

| EPDC             | Electrophoretic Display<br>Controller | Peripherals                 | The EPDC is a feature-rich, low power, and<br>high-performance direct-drive, active matrix EPD<br>controller. It is specifically designed to drive E-INK <sup>TM</sup><br>EPD panels, supporting a wide variety of TFT<br>backplanes. It is available in both i.MX 6DualLite and<br>i.MX 6Solo.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| EPIT-1<br>EPIT-2 | Enhanced Periodic<br>Interrupt Timer  | Timer Peripherals           | Each EPIT is a 32-bit "set and forget" timer that starts<br>counting after the EPIT is enabled by software. It is<br>capable of providing precise interrupts at regular<br>intervals with minimal processor intervention. It has a<br>12-bit prescaler for division of input clock frequency to<br>get the required time setting for the interrupts to occur,<br>and counter value can be programmed on the fly.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ESAI             | Enhanced Serial Audio<br>Interface    | Connectivity<br>Peripherals | The Enhanced Serial Audio Interface (ESAI) provides a full-duplex serial port for serial communication with a variety of serial devices, including industry-standard codecs, SPDIF transceivers, and other processors. The ESAI consists of independent transmitter and receiver sections, each section with its own clock generator. All serial transfers are synchronized to a clock. Additional synchronization signals are used to delineate the word frames. The normal mode of operation is used to transfer data at a periodic rate, one word per period. The network mode is also intended for periodic transfers; however, it supports up to 32 words (time slots) per period. This mode can be used to build time division multiplexed (TDM) networks. In contrast, the on-demand mode is intended for non-periodic transfers of data and to transfer data serially at high speed when the data becomes available. The ESAI has 12 pins for data and clocking connection to external devices. |

## Table 2. i.MX 6Solo/6DualLite Modules List (continued)

| Block Mnemonic                                 | Block Name                                | Subsystem                     | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------|-------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSI-1<br>SSI-2<br>SSI-3                        | I2S/SSI/AC97 Interface                    | Connectivity<br>Peripherals   | The SSI is a full-duplex synchronous interface, which is<br>used on the AP to provide connectivity with off-chip<br>audio peripherals. The SSI supports a wide variety of<br>protocols (SSI normal, SSI network, I2S, and AC-97), bit<br>depths (up to 24 bits per word), and clock / frame sync<br>options.<br>The SSI has two pairs of 8x24 FIFOs and hardware<br>support for an external DMA controller in order to<br>minimize its impact on system performance. The<br>second pair of FIFOs provides hardware interleaving of<br>a second audio stream that reduces CPU overhead in<br>use cases where two time slots are being used<br>simultaneously. |

| TEMPMON                                        | Temperature Monitor                       | System Control<br>Peripherals | The Temperature sensor IP is used for detecting die<br>temperature. The temperature read out does not reflect<br>case or ambient temperature. It reflects the temperature<br>in proximity of the sensor location on the die.<br>Temperature distribution may not be uniformly<br>distributed, therefore the read out value may not be the<br>reflection of the temperature value of the entire die.                                                                                                                                                                                                                                                          |

| TZASC                                          | Trust-Zone Address<br>Space Controller    | Security                      | The TZASC (TZC-380 by ARM) provides security<br>address region control functions required for intended<br>application. It is used on the path to the DRAM<br>controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| UART-1<br>UART-2<br>UART-3<br>UART-4<br>UART-5 | UART Interface                            | Connectivity<br>Peripherals   | <ul> <li>Each of the UARTv2 modules support the following serial data transmit/receive protocols and configurations:</li> <li>7- or 8-bit data words, 1 or 2 stop bits, programmable parity (even, odd or none)</li> <li>Programmable baud rates up to 4 MHz. This is a higher max baud rate relative to the 1.875 MHz, which is stated by the TIA/EIA-232-F standard and the i.MX31 UART modules.</li> <li>32-byte FIFO on Tx and 32 half-word FIFO on Rx supporting auto-baud</li> <li>IrDA 1.0 support (up to SIR speed of 115200 bps)</li> <li>Option to operate as 8-pins full UART, DCE, or DTE</li> </ul>                                             |

| USBOH3                                         | USB 2.0 High Speed<br>OTG and 3x HS Hosts | Connectivity<br>Peripherals   | <ul> <li>USBOH3 contains:</li> <li>One high-speed OTG module with integrated HS<br/>USB PHY</li> <li>One high-speed Host module with integrated HS<br/>USB PHY</li> <li>Two identical high-speed Host modules connected to<br/>HSIC USB ports.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                    |

| VDOA                                           | VDOA                                      | Multimedia<br>Peripherals     | Video Data Order Adapter (VDOA): used to re-order video data from the "tiled" order used by the VPU to the conventional raster-scan order needed by the IPU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

## Table 2. i.MX 6Solo/6DualLite Modules List (continued)

## 4 Electrical Characteristics

This section provides the device and module-level electrical characteristics for the i.MX 6Solo/6DualLite processors.

## 4.1 Chip-Level Conditions

This section provides the device-level electrical characteristics for the IC. See Table 6 for a quick reference to the individual tables and sections.

| For these characteristics,               | Topic appears |

|------------------------------------------|---------------|

| Absolute Maximum Ratings                 | on page 22    |

| BGA Case 2240 Package Thermal Resistance | on page 23    |

| Operating Ranges                         | on page 24    |

| External Clock Sources                   | on page 26    |

| Maximal Supply Currents                  | on page 27    |

| Low Power Mode Supply Currents           | on page 29    |

| USB PHY Current Consumption              | on page 30    |

| PCIe 2.0 Power Consumption               | on page 30    |

## 4.1.1 Absolute Maximum Ratings

## Table 7. Absolute Maximum Ratings

| Parameter Description                                                 | Symbol                                | Min  | Мах                    | Unit |

|-----------------------------------------------------------------------|---------------------------------------|------|------------------------|------|

| Core supply voltages                                                  | VDDARM_IN<br>VDDSOC_IN                | -0.3 | 1.5                    | V    |

| Internal supply voltages                                              | VDDARM_CAP<br>VDDSOC_CAP<br>VDDPU_CAP | -0.3 | 1.3                    | V    |

| GPIO supply voltage                                                   | Supplies denoted as I/O supply        | -0.5 | 3.6                    | V    |

| DDR I/O supply voltage                                                | Supplies denoted as I/O supply        | -0.4 | 1.975                  | V    |

| LVDS I/O supply voltage                                               | Supplies denoted as I/O supply        | -0.3 | 2.8                    | V    |

| VDD_SNVS_IN supply voltage                                            | VDD_SNVS_IN                           | -0.3 | 3.3                    | V    |

| VDDHIGH_IN supply voltage                                             | VDDHIGH_IN                            | -0.3 | 3.6                    | V    |

| USB VBUS                                                              | VBUS                                  | _    | 5.25                   | V    |

| Input voltage on USB_OTG_DP, USB_OTG_DN,<br>USB_H1_DP, USB_H1_DN pins | USB_DP/USB_DN                         | -0.3 | 3.63                   | V    |

| Input/output voltage range                                            | V <sub>in</sub> /V <sub>out</sub>     | -0.5 | OVDD <sup>1</sup> +0.3 | V    |

| Parameter Description                                                      | Symbol               | Min | Мах         | Unit |

|----------------------------------------------------------------------------|----------------------|-----|-------------|------|

| ESD damage immunity:                                                       | V <sub>esd</sub>     |     |             |      |

| <ul><li>Human Body Model (HBM)</li><li>Charge Device Model (CDM)</li></ul> |                      | _   | 2000<br>500 | V    |

| Storage temperature range                                                  | T <sub>STORAGE</sub> | -40 | 150         | °C   |

### Table 7. Absolute Maximum Ratings (continued)

<sup>1</sup> OVDD is the I/O supply voltage.

## 4.1.2 Thermal Resistance

## 4.1.2.1 BGA Case 2240 Package Thermal Resistance

Table 8 displays the thermal resistance data.

## Table 8. Thermal Resistance Data

| Rating                                 | Test Conditions                                                                                                          | Symbol                                    | Value    | Unit         |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------|--------------|

| Junction to Ambient <sup>1</sup>       | Single-layer board (1s); natural convection <sup>2</sup><br>Four-layer board (2s2p); natural convection <sup>2</sup>     | ${\sf R}_{	heta JA} \ {\sf R}_{	heta JA}$ | 38<br>23 | °C/W<br>°C/W |

| Junction to Ambient <sup>1</sup>       | Single-layer board (1s); airflow 200 ft/min <sup>2,3</sup><br>Four-layer board (2s2p); airflow 200 ft/min <sup>2,3</sup> | ${\sf R}_{	heta JA} \ {\sf R}_{	heta JA}$ | 30<br>20 | °C/W<br>°C/W |

| Junction to Board <sup>1,4</sup>       |                                                                                                                          | $R_{	extsf{	heta}JB}$                     | 14       | °C/W         |

| Junction to Case <sup>1,5</sup>        |                                                                                                                          | $R_{	extsf{	heta}JC}$                     | 6        | °C/W         |

| Junction to Package Top <sup>1,6</sup> | Natural Convection                                                                                                       | $\Psi_{JT}$                               | 2        | °C/W         |

<sup>1</sup> Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

<sup>2</sup> Per JEDEC JESD51-2 with the single layer board horizontal. Thermal test board meets JEDEC specification for the specified package.

<sup>3</sup> Per JEDEC JESD51-6 with the board horizontal.

<sup>4</sup> Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

<sup>5</sup> Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

<sup>6</sup> Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

## 4.1.3 **Operating Ranges**

Table 9 provides the operating ranges of the i.MX 6Solo/6DualLite processors. For details on the chip's power structure, see the "Power Management Unit (PMU)" chapter of the *i.MX 6Solo/6DualLite Reference Manual (IMX6SDLRM)*.

| Parameter<br>Description                         | Symbol                   | Min                  | Тур  | Max <sup>1</sup> | Unit | Comment                                                                                                                                                  |

|--------------------------------------------------|--------------------------|----------------------|------|------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Run mode: LDO<br>enabled                         | VDDARM_IN                | 1.350 <sup>2</sup>   | —    | 1.5              | V    | LDO Output Set Point (VDDARM_CAP) = 1.225 V minimum for operation up to 996 MHz.                                                                         |

|                                                  |                          | 1.275 <sup>2</sup>   | —    | 1.5              | V    | LDO Output Set Point (VDDARM_CAP) = 1.150 V minimum for operation up to 792 MHz.                                                                         |

|                                                  |                          | 1.175 <sup>2</sup>   | —    | 1.5              | V    | LDO Output Set Point (VDDARM_CAP) = 1.05<br>V minimum for operation up to 396 MHz.                                                                       |

|                                                  | VDDSOC_IN <sup>3</sup>   | 1.275 <sup>2,4</sup> | —    | 1.5              | V    | VPU = 328 MHz, VDDSOC and VDDPU LDO<br outputs (VDDSOC_CAP and VDDPU_CAP) =<br>1.225 V maximum and 1.15 V minimum.                                       |

| Run mode: LDO<br>bypassed                        | VDDARM_IN                | 1.250                | —    | 1.3              | V    | LDO bypassed for operation up to 996 MHz                                                                                                                 |

|                                                  |                          | 1.150                | —    | 1.3              | V    | LDO bypassed for operation up to 792 MHz                                                                                                                 |

|                                                  |                          | 1.05                 | —    | 1.3              | V    | LDO bypassed for operation up to 396 MHz                                                                                                                 |

|                                                  | VDDSOC_IN                | 1.15 <sup>4</sup>    | —    | 1.225            | V    | LDO bypassed for operation VPU = 328 MHz</td                                                                                                             |

| Standby/DSM mode                                 | VDDARM_IN                | 0.9                  | —    | 1.3              | V    | Refer to Table 13, "Stop Mode Current and Power Consumption," on page 29.                                                                                |

|                                                  | VDDSOC_IN                | 0.9                  | —    | 1.225            | V    |                                                                                                                                                          |

| VDDHIGH internal regulator                       | VDDHIGH_IN               | 2.8                  | —    | 3.3              | V    | Must match the range of voltges that the rechargeable backup battery supports.                                                                           |

| Backup battery supply range                      | VDD_SNVS_IN <sup>5</sup> | 2.9                  | _    | 3.3              | V    | Should be supplied from the same supply as VDDHIGH_IN if the system does not require keeping real time and other data on OFF state.                      |

| USB supply voltages                              | USB_OTG_VBUS             | 4.4                  | —    | 5.25             | V    |                                                                                                                                                          |

|                                                  | USB_H1_VBUS              | 4.4                  | —    | 5.25             | V    |                                                                                                                                                          |

| DDR I/O supply voltage                           | NVCC_DRAM                | 1.14                 | 1.2  | 1.3              | V    | LPDDR2, DDR3-U                                                                                                                                           |

|                                                  |                          | 1.425                | 1.5  | 1.575            | V    | DDR3                                                                                                                                                     |

|                                                  |                          | 1.283                | 1.35 | 1.45             | V    | DDR3_L                                                                                                                                                   |

| Supply for RGMII I/O<br>power group <sup>6</sup> | NVCC_RGMII               | 1.15                 | _    | 2.625            | V    | 1.15 V – 1.30 V in HSIC 1.2 V mode<br>1.43 V – 1.58 V in RMGII 1.5 V mode<br>1.70 V – 1.90 V in RMGII 1.8 V mode<br>2.25 V – 2.625 V in RMGII 2.5 V mode |

| Table | 9. | Operati | ing | Ranges |

|-------|----|---------|-----|--------|

|-------|----|---------|-----|--------|

- <sup>1</sup> t<sub>SKD</sub> = I t<sub>PHLD</sub> t<sub>PLHD</sub> I, is the magnitude difference in differential propagation delay time between the positive going edge and the negative going edge of the same channel.

- <sup>2</sup> Measurement levels are 20-80% from output voltage.

## 4.8 Output Buffer Impedance Parameters

This section defines the I/O impedance parameters of the i.MX 6Solo/6DualLite processors for the following I/O types:

- General Purpose I/O (GPIO)

- Double Data Rate I/O (DDR) for LPDDR2, and DDR3/DDR3L modes

- LVDS I/O

## NOTE

GPIO and DDR I/O output driver impedance is measured with "long" transmission line of impedance Ztl attached to I/O pad and incident wave launched into transmission line. Rpu/Rpd and Ztl form a voltage divider that defines specific voltage of incident wave relative to OVDD. Output driver impedance is calculated from this voltage divider (see Figure 7).

## 4.9.4 DDR SDRAM Specific Parameters (DDR3/DDR3L and LPDDR2)

## 4.9.4.1 DDR3/DDR3L Parameters

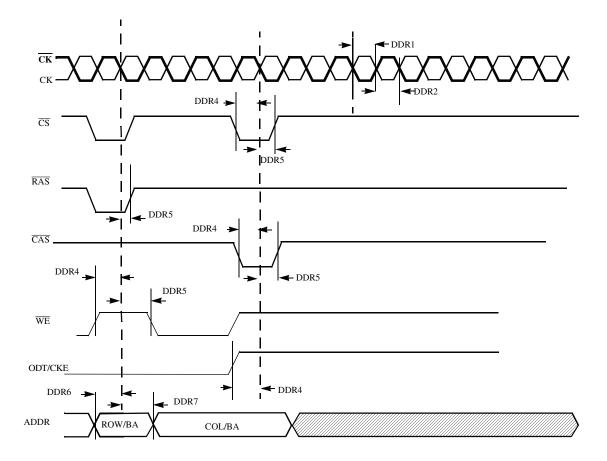

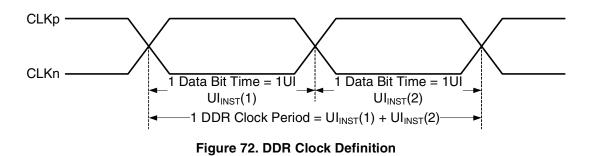

Figure 22 shows the basic timing parameters. The timing parameters for this diagram appear in Table 41.

Figure 22. DDR3 Command and Address Timing Parameters

| ID   | Parameter                             | Sumbol | CK = 40 | Unit |      |  |

|------|---------------------------------------|--------|---------|------|------|--|

| U    | Farameter                             | Symbol | Min     | Мах  | onit |  |

| DDR1 | CK clock high-level width             | tсн    | 0.47    | 0.53 | tск  |  |

| DDR2 | CK clock low-level width              | tCL    | 0.47    | 0.53 | tск  |  |

| DDR4 | CS, RAS, CAS, CKE, WE, ODT setup time | tis    | 800     | _    | ps   |  |

| DDR5 | CS, RAS, CAS, CKE, WE, ODT hold time  | tıн    | 580     | —    | ps   |  |

| DDR6 | Address output setup time             | tis    | 800     | _    | ps   |  |

| DDR7 | Address output hold time              | tıн    | 580     | _    | ps   |  |

| Table 41. DDR3/DDR3L Ti | ming Parameter Table |

|-------------------------|----------------------|

|-------------------------|----------------------|

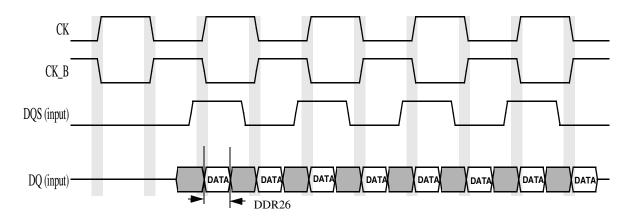

Figure 24 shows the read DDR3/DDR3L timing parameters. The timing parameters for this diagram appear in Table 43.

## Figure 24. DDR3/DDR3L Read Cycle

## Table 43. DDR3/DDR3L Read Cycle

|       | ID Parameter                           |  | CK = 400 MHz |     | Unit |

|-------|----------------------------------------|--|--------------|-----|------|

|       |                                        |  | Min          | Max | onne |

| DDR26 | Minimum required DQ valid window width |  | 450          | —   | ps   |

<sup>1</sup> To receive the reported setup and hold values, read calibration should be performed in order to locate the DQS in the middle of DQ window.

<sup>2</sup> All measurements are in reference to Vref level.

$^3\,$  Measurements were done using balanced load and 25  $\Omega$  resistor from outputs to VDD\_REF.

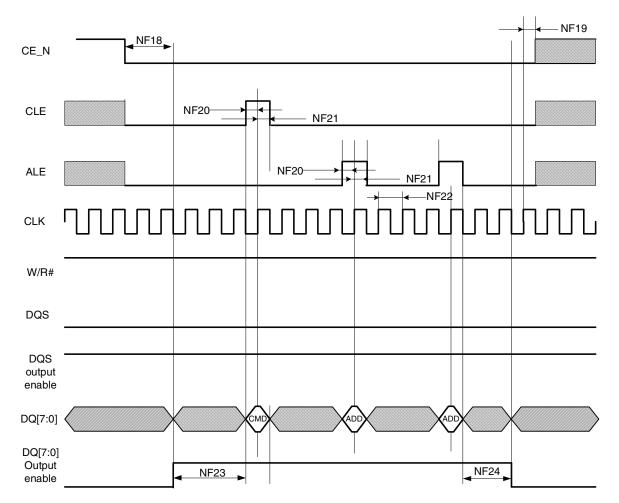

## 4.10.2 Source Synchronous Mode AC Timing (ONFI 2.x Compatible)

Figure 32 to Figure 34 show the write and read timing of Source Synchronous Mode.

Figure 32. Source Synchronous Mode Command and Address Timing Diagram

# 4.11.4 Ultra High Speed SD/SDIO/MMC Host Interface (uSDHC) AC timing

This section describes the electrical information of the uSDHC, which includes SD/eMMC4.3 (Single Data Rate) timing, eMMC4.4 (Dual Date Rate) timing and SDR104/50(SD3.0) timing.

## 4.11.4.1 SD/eMMC4.3 (Single Data Rate) AC Timing

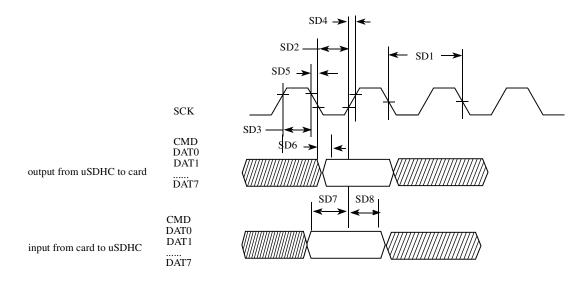

Figure 42 depicts the timing of SD/eMMC4.3, and Table 53 lists the SD/eMMC4.3 timing characteristics.

Figure 42. SD/eMMC4.3 Timing

| ID  | Parameter                                            | Symbols                      | Min  | Мах   | Unit |  |  |  |

|-----|------------------------------------------------------|------------------------------|------|-------|------|--|--|--|

|     | Card Input Clock                                     |                              |      |       |      |  |  |  |

| SD1 | Clock Frequency (Low Speed)                          | f <sub>PP</sub> <sup>1</sup> | 0    | 400   | kHz  |  |  |  |

|     | Clock Frequency (SD/SDIO Full Speed/High Speed)      | f <sub>PP</sub> <sup>2</sup> | 0    | 25/50 | MHz  |  |  |  |

|     | Clock Frequency (MMC Full Speed/High Speed)          | f <sub>PP</sub> <sup>3</sup> | 0    | 20/52 | MHz  |  |  |  |

|     | Clock Frequency (Identification Mode)                | f <sub>OD</sub>              | 100  | 400   | kHz  |  |  |  |

| SD2 | Clock Low Time                                       | t <sub>WL</sub>              | 7    | —     | ns   |  |  |  |

| SD3 | Clock High Time                                      | t <sub>WH</sub>              | 7    | —     | ns   |  |  |  |

| SD4 | Clock Rise Time                                      | t <sub>TLH</sub>             | —    | 3     | ns   |  |  |  |

| SD5 | Clock Fall Time                                      | t <sub>THL</sub>             | —    | 3     | ns   |  |  |  |

|     | uSDHC Output/Card Inputs CMD, DAT (Reference to CLK) |                              |      |       |      |  |  |  |

| SD6 | uSDHC Output Delay                                   | t <sub>OD</sub>              | -6.6 | 3.6   | ns   |  |  |  |

| Table 53. S | SD/eMMC4.3 | Interface | Timing | Specification |

|-------------|------------|-----------|--------|---------------|

|-------------|------------|-----------|--------|---------------|

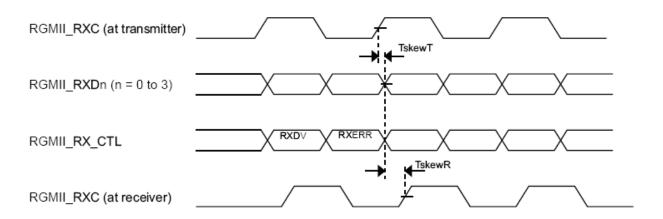

Figure 51. RGMII Receive Signal Timing Diagram Original

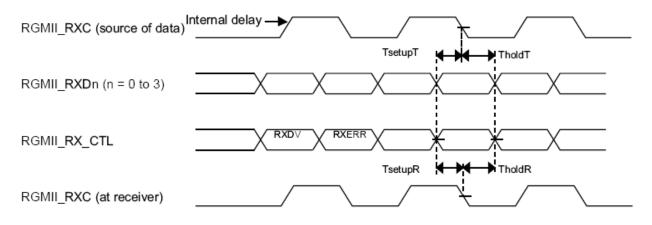

Figure 52. RGMII Receive Signal Timing Diagram with Internal Delay

# 4.11.6 Flexible Controller Area Network (FLEXCAN) AC Electrical Specifications

The Flexible Controller Area Network (FlexCAN) module is a communication controller implementing the CAN protocol according to the CAN 2.0B protocol specification. The processor has two CAN modules available for systems design. Tx and Rx ports for both modules are multiplexed with other I/O pins. See the IOMUXC chapter of the *i.MX 6Solo/6DualLite Reference Manual (IMX6SDLRM)* to see which pins expose Tx and Rx pins; these ports are named TXCAN and RXCAN, respectively.

## 4.11.7 HDMI Module Timing Parameters

## 4.11.7.1 Latencies and Timing Information

Power-up time (time between TX\_PWRON assertion and TX\_READY assertion) for the HDMI 3D Tx PHY while operating with the slowest input reference clock supported (13.5 MHz) is 3.35 ms.

| Symbol              | mbol Parameter Conditions   |                                                     | Min. | Тур. | Max. | Unit            |  |  |  |  |

|---------------------|-----------------------------|-----------------------------------------------------|------|------|------|-----------------|--|--|--|--|

|                     | TMDS Drivers Specifications |                                                     |      |      |      |                 |  |  |  |  |

| _                   | Maximum serial data rate    | —                                                   | —    | —    | 3.4  | Gbps            |  |  |  |  |

| F<br>TMDSCLK        | TMDSCLK frequency           | On TMDSCLKP/N outputs                               | 25   | —    | 340  | MHz             |  |  |  |  |

| P<br>TMDSCLK        | TMDSCLK period              | RL = 50 Ω<br>See Figure 56.                         | 2.94 | _    | 40   | ns              |  |  |  |  |

| <sup>t</sup> CDC    | TMDSCLK duty cycle          | $t = t / P TMDSCLK$ $RL = 50 \Omega$ See Figure 56. | 40   | 50   | 60   | %               |  |  |  |  |

| <sup>t</sup><br>CPH | TMDSCLK high time           | RL = 50 Ω<br>See Figure 56.                         | 4    | 5    | 6    | UI <sup>1</sup> |  |  |  |  |

| t<br>CPL            | TMDSCLK low time            | RL = 50 Ω<br>See Figure 56.                         | 4    | 5    | 6    | UI <sup>1</sup> |  |  |  |  |

| —                   | TMDSCLK jitter <sup>2</sup> | RL = 50 Ω                                           | —    | —    | 0.25 | UI <sup>1</sup> |  |  |  |  |

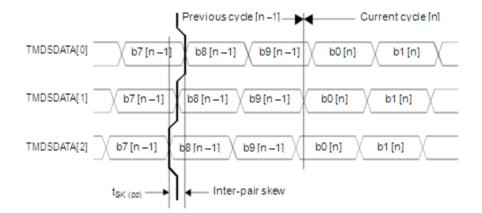

| t<br>SK(p)          | Intra-pair (pulse) skew     | $RL = 50 \Omega$<br>See Figure 58.                  | —    |      | 0.15 | UI <sup>1</sup> |  |  |  |  |

**Table 63. Switching Characteristics**

| <sup>t</sup><br>SK(pp) | Inter-pair skew                         | $RL = 50 \Omega$<br>See Figure 59.                                                    | _  | _ | 1      | UI <sup>1</sup> |

|------------------------|-----------------------------------------|---------------------------------------------------------------------------------------|----|---|--------|-----------------|

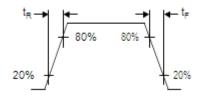

| t <sub>R</sub>         | Differential output signal rise<br>time | 20-80%<br>RL = 50 $\Omega$<br>See Figure 60.                                          | 75 | _ | 0.4 UI | ps              |

| t <sub>F</sub>         | Differential output signal fall time    | $\begin{array}{l} 20-80\%\\ \text{RL}=50\ \Omega\\ \text{See Figure 60.} \end{array}$ | 75 | — | 0.4 UI | ps              |

| _                      | Differential signal overshoot           | Referred to 2x V <sub>SWING</sub>                                                     | _  | — | 15     | %               |

| —                      | Differential signal undershoot          | Referred to $2x V_{SWING}$                                                            | _  | — | 25     | %               |

Table 63. Switching Characteristics (continued)

<sup>1</sup> UI means TMDS clock unit.

<sup>2</sup> Relative to ideal recovery clock, as specified in the HDMI specification, version 1.4a, section 4.2.3.

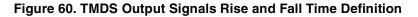

## 4.11.9 I<sup>2</sup>C Module Timing Parameters

This section describes the timing parameters of the  $I^2C$  module. Figure 61 depicts the timing of  $I^2C$  module, and Table 64 lists the  $I^2C$  module timing characteristics.

Figure 61. I<sup>2</sup>C Bus Timing

## Table 64. I<sup>2</sup>C Module Timing Parameters

| ID  | ID Parameter                               |                | ard Mode          | Fast Mode      |                  | Unit |

|-----|--------------------------------------------|----------------|-------------------|----------------|------------------|------|

|     |                                            |                | Мах               | Min            | Max              |      |

| IC1 | I2CLK cycle time                           | 10             | _                 | 2.5            |                  | μs   |

| IC2 | Hold time (repeated) START condition       | 4.0            | _                 | 0.6            |                  | μs   |

| IC3 | Set-up time for STOP condition             | 4.0            | _                 | 0.6            |                  | μs   |

| IC4 | Data hold time                             | 0 <sup>1</sup> | 3.45 <sup>2</sup> | 0 <sup>1</sup> | 0.9 <sup>2</sup> | μs   |

| IC5 | HIGH Period of I2CLK Clock                 | 4.0            | _                 | 0.6            |                  | μs   |

| IC6 | LOW Period of the I2CLK Clock              | 4.7            | _                 | 1.3            |                  | μs   |

| IC7 | Set-up time for a repeated START condition | 4.7            | _                 | 0.6            |                  | μs   |

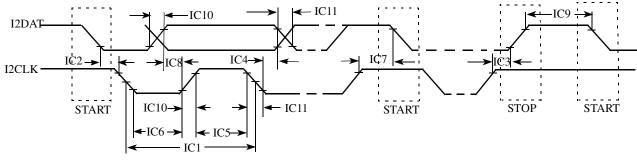

## 4.11.10.6 Synchronous Interfaces to Standard Active Matrix TFT LCD Panels

## 4.11.10.6.1 IPU Display Operating Signals

The IPU uses four control signals and data to operate a standard synchronous interface:

- IPP\_DISP\_CLK—Clock to display

- HSYNC—Horizontal synchronization

- VSYNC—Vertical synchronization

- DRDY—Active data

All synchronous display controls are generated on the base of an internally generated "local start point". The synchronous display controls can be placed on time axis with DI's offset, up and down parameters. The display access can be whole number of DI clock (Tdiclk) only. The IPP\_DATA can not be moved relative to the local start point. The data bus of the synchronous interface is output direction only.

## 4.11.10.6.2 LCD Interface Functional Description

Figure 65 depicts the LCD interface timing for a generic active matrix color TFT panel. In this figure, signals are shown with negative polarity. The sequence of events for active matrix interface timing is:

- DI\_CLK internal DI clock is used for calculation of other controls.

- IPP\_DISP\_CLK latches data into the panel on its negative edge (when positive polarity is selected). In active mode, IPP\_DISP\_CLK runs continuously.

- HSYNC causes the panel to start a new line. (Usually IPP\_PIN\_2 is used as HSYNC.)

- VSYNC causes the panel to start a new frame. It always encompasses at least one HSYNC pulse. (Usually IPP\_PIN\_3 is used as VSYNC.)

- DRDY acts like an output enable signal to the CRT display. This output enables the data to be shifted onto the display. When disabled, the data is invalid and the trace is off. (DRDY can be used either synchronous or asynchronous generic purpose pin as well.)

Figure 65. Interface Timing Diagram for TFT (Active Matrix) Panels

| Symbol                             | Parameters                                           | Test Conditions                   | MIN       | ТҮР     | МАХ  | Unit  |

|------------------------------------|------------------------------------------------------|-----------------------------------|-----------|---------|------|-------|

| $\Delta V_{CMTX(LF)}$              | Common level variation between 50 MHz and 450 MHz.   | 80 Ω<= RL< = 125 Ω                |           |         | 25   | mVp   |

|                                    | LP Line D                                            | rivers AC Specifications          | •         |         |      | •     |

| t <sub>rlp,</sub> t <sub>flp</sub> | Single ended output rise/fall time                   | 15% to 85%, C <sub>L</sub> <70 pF |           |         | 25   | ns    |

| t <sub>reo</sub>                   |                                                      | 30% to 85%, C <sub>L</sub> <70 pF |           |         | 35   | ns    |

| $\delta V/\delta t_{SR}$           | Signal slew rate                                     | 15% to 85%, C <sub>L</sub> <70 pF |           |         | 120  | mV/ns |

| CL                                 | Load capacitance                                     |                                   | 0         |         | 70   | pF    |

|                                    | HS Line Re                                           | eceiver AC Specifications         | •         | 1       |      | •     |

| $\Delta V_{CMRX(HF)}$              | Common mode interference beyond 450 MHz              |                                   |           |         | 200  | mVpp  |

| $\Delta V_{CMRX(LF)}$              | Common mode interference between 50 MHz and 450 MHz. |                                   | -50       |         | 50   | mVpp  |

| C <sub>CM</sub>                    | Common mode termination                              |                                   |           |         | 60   | pF    |

|                                    | LP Line Re                                           | eceiver AC Specifications         | 1         | 1       |      | 1     |

| e <sub>SPIKE</sub>                 | Input pulse rejection                                |                                   |           |         | 300  | Vps   |

| T <sub>MIN</sub>                   | Minimum pulse response                               |                                   | 50        |         |      | ns    |

| V <sub>INT</sub>                   | Pk-to-Pk interference voltage                        |                                   |           |         | 400  | mV    |

| f <sub>INT</sub>                   | Interference frequency                               |                                   | 450       |         |      | MHz   |

|                                    | Model Parameters used for Dr                         | river Load switching perforr      | nance eva | luation |      | 1     |

| C <sub>PAD</sub>                   | Equivalent Single ended I/O PAD capacitance.         |                                   |           |         | 1    | pF    |

| C <sub>PIN</sub>                   | Equivalent Single ended Package + PCB capacitance.   |                                   |           |         | 2    | pF    |

| L <sub>S</sub>                     | Equivalent wire bond series inductance               |                                   |           |         | 1.5  | nH    |

| R <sub>S</sub>                     | Equivalent wire bond series resistance               |                                   |           |         | 0.15 | Ω     |

| RL                                 | Load resistance                                      |                                   | 80        | 100     | 125  | Ω     |

#### Table 72. Electrical and Timing Information

## 4.11.12.6 High-Speed Clock Timing

## 4.11.14 PCIe PHY Parameters

The PCIe interface complies with PCIe specification Gen2 x1 lane and supports the PCI Express 1.1/2.0 standard.

## 4.11.14.1 PCIE\_REXT Reference Resistor Connection

The impedance calibration process requires connection of reference resistor 200  $\Omega$ . 1% precision resistor on PCIE\_REXT pads to ground. It is used for termination impedance calibration.

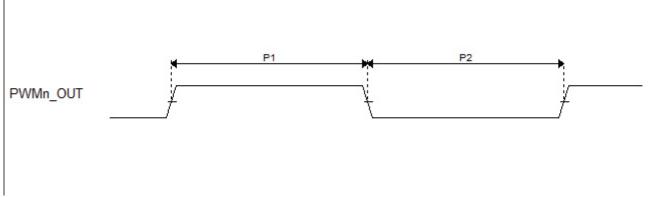

## 4.11.15 Pulse Width Modulator (PWM) Timing Parameters

This section describes the electrical information of the PWM. The PWM can be programmed to select one of three clock signals as its source frequency. The selected clock signal is passed through a prescaler before being input to the counter. The output is available at the pulse-width modulator output (PWMO) external pin.

Figure 84 depicts the timing of the PWM, and Table 74 lists the PWM timing parameters.

| Figure | 84. | PWM | Timing |

|--------|-----|-----|--------|

|--------|-----|-----|--------|

Table 74. PWM Output Timing Parameters

| ID | Parameter                   | Min | Мах     | Unit |

|----|-----------------------------|-----|---------|------|

|    | PWM Module Clock Frequency  | 0   | ipg_clk | MHz  |

| P1 | PWM output pulse width high | 15  |         | ns   |

| P2 | PWM output pulse width low  | 15  |         | ns   |

| ID                                   | Parameter                            |      | Мах | Unit |  |  |

|--------------------------------------|--------------------------------------|------|-----|------|--|--|

| Synchronous Internal Clock Operation |                                      |      |     |      |  |  |

| SS42                                 | SRXD setup before (Tx) CK falling    | 10.0 | —   | ns   |  |  |

| SS43                                 | SS43 SRXD hold after (Tx) CK falling |      | _   | ns   |  |  |

## Table 78. SSI Transmitter Timing with Internal Clock (continued)

## NOTE

- All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal STCK/SRCK and/or the frame sync STFS/SRFS shown in the tables and in the figures.

- All timings are on Audiomux Pads when SSI is being used for data transfer.

- The terms, WL and BL, refer to Word Length (WL) and Bit Length (BL).

- "Tx" and "Rx" refer to the Transmit and Receive sections of the SSI.

- For internal Frame Sync operation using external clock, the FS timing is same as that of Tx Data (for example, during AC97 mode of operation).

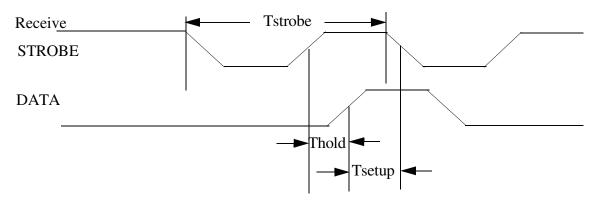

## 4.11.20.2 Receive Timing

Figure 100. USB HSIC Receive Waveform

| Table 88. U | JSB HSIC Receiv | ve Parameters <sup>1</sup> |

|-------------|-----------------|----------------------------|

|-------------|-----------------|----------------------------|

| Name    | Parameter                       | Min   | Max   | Unit | Comment                        |

|---------|---------------------------------|-------|-------|------|--------------------------------|

| Tstrobe | strobe period                   | 4.166 | 4.167 | ns   |                                |

| Thold   | data hold time                  | 300   |       | ps   | Measured at 50% point          |

| Tsetup  | data setup time                 | 365   |       | ps   | Measured at 50% point          |

| Tslew   | strobe/data rising/falling time | 0.7   | 2     | V/ns | Averaged from 30% – 70% points |

<sup>1</sup> The timings in the table are guaranteed when:

-AC I/O voltage is between 0.9x to 1x of the I/O supply

-DDR\_SEL configuration bits of the I/O are set to (10)b

## 4.11.21 USB PHY Parameters

This section describes the USB-OTG PHY and the USB Host port PHY parameters.

The USB PHY meets the electrical compliance requirements defined in the Universal Serial Bus Revision 2.0 OTG, USB Host with the amendments below (On-The-Go and Embedded Host Supplement to the USB Revision 2.0 Specification is not applicable to Host port).

- USB ENGINEERING CHANGE NOTICE

- Title: 5V Short Circuit Withstand Requirement Change

- Applies to: Universal Serial Bus Specification, Revision 2.0

- Errata for USB Revision 2.0 April 27, 2000 as of 12/7/2000

- USB ENGINEERING CHANGE NOTICE

- Title: Pull-up/Pull-down resistors

- Applies to: Universal Serial Bus Specification, Revision 2.0

- USB ENGINEERING CHANGE NOTICE

- Title: Suspend Current Limit Changes

- Applies to: Universal Serial Bus Specification, Revision 2.0

#### Package Information and Contact Assignments

|                |      |             |              |                                    | Out of Reset Con   | dition <sup>2</sup>  |       |

|----------------|------|-------------|--------------|------------------------------------|--------------------|----------------------|-------|

| Ball Name      | Ball | Power Group | Ball<br>Type | Default<br>Mode<br>(Reset<br>Mode) | Default Function   | Input/<br>Outpu<br>t | Value |

| DRAM_DQM0      | AC3  | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_DQM[0]   | Output               | Low   |

| DRAM_DQM1      | AC6  | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_DQM[1]   | Output               | Low   |

| DRAM_DQM2      | AB8  | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_DQM[2]   | Output               | Low   |

| DRAM_DQM3      | AE10 | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_DQM[3]   | Output               | Low   |

| DRAM_DQM4      | AB18 | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_DQM[4]   | Output               | Low   |

| DRAM_DQM5      | AC20 | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_DQM[5]   | Output               | Low   |

| DRAM_DQM6      | AD24 | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_DQM[6]   | Output               | Low   |

| DRAM_DQM7      | Y21  | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_DQM[7]   | Output               | Low   |

| DRAM_RAS       | AB15 | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_RAS      | Output               | Low   |

| DRAM_RESET     | Y6   | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_RESET    | Output               | Low   |

| DRAM_SDBA0     | AC15 | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_SDBA[0]  | Output               | Low   |

| DRAM_SDBA1     | Y15  | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_SDBA[1]  | Output               | Low   |

| DRAM_SDBA2     | AB12 | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_SDBA[2]  | Output               | Low   |

| DRAM_SDCKE0    | Y11  | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_SDCKE[0] | Output               | Low   |

| DRAM_SDCKE1    | AA11 | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_SDCKE[1] | Output               | Low   |

| DRAM_SDCLK_0   | AD15 | NVCC_DRAM   | DDRCLK       | ALT0                               | mmdc.DRAM_SDCLK0   | Output               | Low   |

| DRAM_SDCLK_0_B | AE15 | NVCC_DRAM   |              |                                    | DRAM_SDCLK_0_B     | -                    | -     |

| DRAM_SDCLK_1   | AD14 | NVCC_DRAM   | DDRCLK       | ALT0                               | mmdc.DRAM_SDCLK1   | Output               | Low   |

| DRAM_SDCLK_1_B | AE14 | NVCC_DRAM   |              |                                    | DRAM_SDCLK_1_B     | -                    | -     |

| DRAM_SDODT0    | AC16 | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_ODT[0]   | Output               | Low   |

| DRAM_SDODT1    | AB17 | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_ODT[1]   | Output               | Low   |

| DRAM_SDQS0     | AE3  | NVCC_DRAM   | DDRCLK       | ALT0                               | mmdc.DRAM_SDQS[0]  | Input                | Hi-Z  |

| DRAM_SDQS0_B   | AD3  | NVCC_DRAM   |              |                                    | DRAM_SDQS0_B       | -                    | -     |

| DRAM_SDQS1     | AD6  | NVCC_DRAM   | DDRCLK       | ALT0                               | mmdc.DRAM_SDQS[1]  | Input                | Hi-Z  |

| DRAM_SDQS1_B   | AE6  | NVCC_DRAM   |              |                                    | DRAM_SDQS1_B       | -                    | -     |

| DRAM_SDQS2     | AD8  | NVCC_DRAM   | DDRCLK       | ALT0                               | mmdc.DRAM_SDQS[2]  | Input                | Hi-Z  |

| DRAM_SDQS2_B   | AE8  | NVCC_DRAM   |              |                                    | DRAM_SDQS2_B       | -                    | -     |

| DRAM_SDQS3     | AC10 | NVCC_DRAM   | DDRCLK       | ALT0                               | mmdc.DRAM_SDQS[3]  | Input                | Hi-Z  |

| DRAM_SDQS3_B   | AB10 | NVCC_DRAM   |              |                                    | DRAM_SDQS3_B       | -                    | -     |

| DRAM_SDQS4     | AD18 | NVCC_DRAM   | DDRCLK       | ALT0                               | mmdc.DRAM_SDQS[4]  | Input                | Hi-Z  |

Table 92. 21 x 21 mm Functional Contact Assignments<sup>1</sup> (continued)

### Package Information and Contact Assignments

| ۲           | 8           | >            | 5           | F           | æ           | ٩            | z            |

|-------------|-------------|--------------|-------------|-------------|-------------|--------------|--------------|

| LVDS1_TX0_N | LVDS0_TX3_P | LVDS0_TX2_P  | LVDS0_TX0_P | GPI0_2      | GPI0_17     | CSI0_PIXCLK  | CSI0_DAT4    |

| LVDS1_TX0_P | LVDS0_TX3_N | LVDS0_TX2_N  | LVDS0_TX0_N | GPIO_9      | GPIO_16     | CSI0_DAT5    | CSI0_VSYNC   |

| LVDS1_CLK_N | GND         | LVDS0_CLK_P  | LVDS0_TX1_P | GPIO_6      | GPIO_7      | CSI0_DATA_EN | CSI0_DAT7    |

| LVDS1_CLK_P | KEY_ROW2    | LVDS0_CLK_N  | LVDS0_TX1_N | GPI0_1      | GPIO_5      | CSI0_MCLK    | CSI0_DAT6    |

| GND         | KEY_COL0    | KEY_ROW4     | KEY_COL3    | GPIO_0      | GPIO_8      | GPIO_19      | CSI0_DAT9    |

| DRAM_RESET  | KEY_COL2    | KEY_ROW0     | KEY_ROW1    | KEY_COL4    | GPIO_4      | GPIO_18      | CSI0_DAT8    |

| DRAM_D20    | GND         | NVCC_LVDS2P5 | KEY_COL1    | KEY_ROW3    | GPIO_3      | NVCC_GPIO    | NVCC_CSI     |

| DRAM_D21    | GND         | GND          | GND         | GND         | GND         | GND          | GND          |

| DRAM_D19    | GND         | NVCC_DRAM    | VDDARM_IN   | VDDARM_IN   | VDDARM_IN   | VDDARM_IN    | VDDARM_IN    |

| DRAM_D25    | GND         | NVCC_DRAM    | VDDSOC_CAP  | VDDSOC_CAP  | VDDSOC_CAP  | GND          | GND          |

| DRAM_SDCKE0 | GND         | NVCC_DRAM    | GND         | GND         | VDDARM_CAP  | VDDARM_CAP   | VDDARM_CAP   |

| DRAM_A15    | GND         | NVCC_DRAM    | GND         | GND         | GND         | GND          | NC           |

| DRAM_A7     | GND         | NVCC_DRAM    | VDDSOC_CAP  | VDDSOC_CAP  | VDDARM_CAP  | VDDARM_CAP   | VDDARM_CAP   |

| DRAM_A3     | DRAM_A4     | NVCC_DRAM    | VDDSOC_CAP  | VDDSOC_CAP  | VDDARM_IN   | VDDARM_IN    | VDDARM_IN    |

| DRAM_SDBA1  | GND         | NVCC_DRAM    | GND         | GND         | GND         | GND          | GND          |

| DRAM_CS0    | GND         | NVCC_DRAM    | VDDSOC_IN   | VDDSOC_IN   | VDDSOC_IN   | VDDSOC_IN    | VDDSOC_IN    |

| DRAM_D36    | GND         | NVCC_DRAM    | GND         | GND         | GND         | VDDPU_CAP    | VDDPU_CAP    |

| DRAM_D37    | GND         | NVCC_DRAM    | NVCC_DRAM   | NVCC_DRAM   | NVCC_DRAM   | GND          | GND          |

| DRAM_D40    | GND         | GND          | GND         | GND         | NVCC_ENET   | NVCC_LCD     | DI0_DISP_CLK |

| DRAM_D44    | ENET_TXD1   | ENET_MDC     | ENET_TXD0   | DISP0_DAT21 | DISP0_DAT13 | DISP0_DAT4   | DI0_PIN3     |

| DRAM_DQM7   | ENET_RXD0   | ENET_TX_EN   | ENET_CRS_DV | DISP0_DAT16 | DISP0_DAT10 | DISP0_DAT3   | DI0_PIN15    |

| DRAM_D59    | ENET_RXD1   | ENET_REF_CLK | DISP0_DAT20 | DISP0_DAT15 | DISP0_DAT8  | DISP0_DAT1   | EIM_BCLK     |

| DRAM_D62    | ENET_RX_ER  | ENET_MDIO    | DISP0_DAT19 | DISP0_DAT11 | DISP0_DAT6  | DISP0_DAT2   | EIM_DA14     |

| GND         | DISP0_DAT23 | DISP0_DAT22  | DISP0_DAT17 | DISP0_DAT12 | DISP0_DAT7  | DISP0_DAT0   | EIM_DA15     |

| DRAM_D58    | DRAM_D63    | DISP0_DAT18  | DISP0_DAT14 | DISP0_DAT9  | DISP0_DAT5  | DI0_PIN4     | DI0_PIN2     |

| ٨           | M           | >            | D           | F           | æ           | ٩            | z            |

## Table 94. 21 x 21 mm, 0.8 mm Pitch Ball Map (continued)