#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Betuns                             |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Active                                                                                                              |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 1 Core, 32-Bit                                                                                                      |

| Speed                              | 1.0GHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON <sup>™</sup> SIMD                                                                                  |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | -                                                                                                                   |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | 0°C ~ 95°C (TJ)                                                                                                     |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-LFBGA                                                                                                           |

| Supplier Device Package            | 624-MAPBGA (21x21)                                                                                                  |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6s5dvm10acr                                            |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Introduction

- Sony Philips Digital Interconnect Format (SPDIF), Rx and Tx

- Two Controller Area Network (FlexCAN), 1 Mbps each

- Two Watchdog timers (WDOG)

- Audio MUX (AUDMUX)

The i.MX 6Solo/6DualLite processors integrate advanced power management unit and controllers:

- Provide PMU, including LDO supplies, for on-chip resources

- Use Temperature Sensor for monitoring the die temperature

- Support DVFS techniques for low power modes

- Use SW State Retention and Power Gating for ARM and MPE

- Support various levels of system power modes

- Use flexible clock gating control scheme

The i.MX 6Solo/6DualLite processors use dedicated hardware accelerators to meet the targeted multimedia performance. The use of hardware accelerators is a key factor in obtaining high performance at low power consumption numbers, while having the CPU core relatively free for performing other tasks.

The i.MX 6Solo/6DualLite processors incorporate the following hardware accelerators:

- VPU—Video Processing Unit

- IPUv3H—Image Processing Unit version 3H

- GPU3Dv5—3D Graphics Processing Unit (OpenGL ES 2.0) version 5

- GPU2Dv2—2D Graphics Processing Unit (BitBlt)

- PXP—PiXel Processing Pipeline. Off loading key pixel processing operations are required to support the EPD display applications.

- ASRC—Asynchronous Sample Rate Converter

Security functions are enabled and accelerated by the following hardware:

- ARM TrustZone including the TZ architecture (separation of interrupts, memory mapping, etc.)

- SJC—System JTAG Controller. Protecting JTAG from debug port attacks by regulating or blocking the access to the system debug features.

- CAAM—Cryptographic Acceleration and Assurance Module, containing cryptographic and hash engines, 16 KB secure RAM, and True and Pseudo Random Number Generator (NIST certified).

- SNVS—Secure Non-Volatile Storage, including Secure Real Time Clock

- CSU—Central Security Unit. Enhancement for the IC Identification Module (IIM). Will be configured during boot and by eFUSEs and will determine the security level operation mode as well as the TZ policy.

- A-HAB—Advanced High Assurance Boot—HABv4 with the new embedded enhancements: SHA-256, 2048-bit RSA key, version control mechanism, warm boot, CSU, and TZ initialization.

| Block Mnemonic                                 | Block Name                                | Subsystem                     | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------|-------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSI-1<br>SSI-2<br>SSI-3                        | I2S/SSI/AC97 Interface                    | Connectivity<br>Peripherals   | The SSI is a full-duplex synchronous interface, which is<br>used on the AP to provide connectivity with off-chip<br>audio peripherals. The SSI supports a wide variety of<br>protocols (SSI normal, SSI network, I2S, and AC-97), bit<br>depths (up to 24 bits per word), and clock / frame sync<br>options.<br>The SSI has two pairs of 8x24 FIFOs and hardware<br>support for an external DMA controller in order to<br>minimize its impact on system performance. The<br>second pair of FIFOs provides hardware interleaving of<br>a second audio stream that reduces CPU overhead in<br>use cases where two time slots are being used<br>simultaneously. |

| TEMPMON                                        | Temperature Monitor                       | System Control<br>Peripherals | The Temperature sensor IP is used for detecting die<br>temperature. The temperature read out does not reflect<br>case or ambient temperature. It reflects the temperature<br>in proximity of the sensor location on the die.<br>Temperature distribution may not be uniformly<br>distributed, therefore the read out value may not be the<br>reflection of the temperature value of the entire die.                                                                                                                                                                                                                                                          |

| TZASC                                          | Trust-Zone Address<br>Space Controller    | Security                      | The TZASC (TZC-380 by ARM) provides security<br>address region control functions required for intended<br>application. It is used on the path to the DRAM<br>controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| UART-1<br>UART-2<br>UART-3<br>UART-4<br>UART-5 | UART Interface                            | Connectivity<br>Peripherals   | <ul> <li>Each of the UARTv2 modules support the following serial data transmit/receive protocols and configurations:</li> <li>7- or 8-bit data words, 1 or 2 stop bits, programmable parity (even, odd or none)</li> <li>Programmable baud rates up to 4 MHz. This is a higher max baud rate relative to the 1.875 MHz, which is stated by the TIA/EIA-232-F standard and the i.MX31 UART modules.</li> <li>32-byte FIFO on Tx and 32 half-word FIFO on Rx supporting auto-baud</li> <li>IrDA 1.0 support (up to SIR speed of 115200 bps)</li> <li>Option to operate as 8-pins full UART, DCE, or DTE</li> </ul>                                             |

| USBOH3                                         | USB 2.0 High Speed<br>OTG and 3x HS Hosts | Connectivity<br>Peripherals   | <ul> <li>USBOH3 contains:</li> <li>One high-speed OTG module with integrated HS<br/>USB PHY</li> <li>One high-speed Host module with integrated HS<br/>USB PHY</li> <li>Two identical high-speed Host modules connected to<br/>HSIC USB ports.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                    |

| VDOA                                           | VDOA                                      | Multimedia<br>Peripherals     | Video Data Order Adapter (VDOA): used to re-order video data from the "tiled" order used by the VPU to the conventional raster-scan order needed by the IPU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

### Table 2. i.MX 6Solo/6DualLite Modules List (continued)

### **Modules List**

| Block Mnemonic | Block Name                    | Subsystem                            | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|-------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VPU            | Video Processing Unit         | Multimedia<br>Peripherals            | A high-performing video processing unit (VPU), which<br>covers many SD-level and HD-level video decoders and<br>SD-level encoders as a multi-standard video codec<br>engine as well as several important video processing,<br>such as rotation and mirroring.<br>See the i. <i>MX 6Solo/6DualLite Reference Manual</i><br>( <i>IMX6SDLRM</i> ) for complete list of VPU's<br>decoding/encoding capabilities.                                                                                                                                                                                                                                                                                                                                                                                            |

| WDOG-1         | Watch Dog                     | Timer Peripherals                    | The Watch Dog Timer supports two comparison points<br>during each counting period. Each of the comparison<br>points is configurable to evoke an interrupt to the ARM<br>core, and a second point evokes an external event on<br>the WDOG line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| WDOG-2<br>(TZ) | Watch Dog (TrustZone)         | Timer Peripherals                    | The TrustZone Watchdog (TZ WDOG) timer module<br>protects against TrustZone starvation by providing a<br>method of escaping normal mode and forcing a switch<br>to the TZ mode. TZ starvation is a situation where the<br>normal OS prevents switching to the TZ mode. Such<br>situation is undesirable as it can compromise the<br>system's security. Once the TZ WDOG module is<br>activated, it must be serviced by TZ software on a<br>periodic basis. If servicing does not take place, the timer<br>times out. Upon a time-out, the TZ WDOG asserts a TZ<br>mapped interrupt that forces switching to the TZ mode.<br>If it is still not served, the TZ WDOG asserts a security<br>violation signal to the CSU. The TZ WDOG module<br>cannot be programmed or deactivated by a normal<br>mode SW. |

| WEIM           | NOR-Flash /PSRAM<br>interface | Connectivity<br>Peripherals          | <ul> <li>The WEIM NOR-FLASH / PSRAM provides:</li> <li>Support 16-bit (in muxed IO mode only) PSRAM memories (sync and async operating modes), at slow frequency</li> <li>Support 16-bit (in muxed IO mode only) NOR-Flash memories, at slow frequency</li> <li>Multiple chip selects</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| XTALOSC        | Crystal Oscillator I/F        | Clocks, Resets, and<br>Power Control | The XTALOSC module enables connectivity to external crystal oscillator device. In a typical application use-case, it is used for 24 MHz oscillator to provide USB required frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Power Line | Conditions | Max Current                          | Unit |

|------------|------------|--------------------------------------|------|

| NVCC_DRAM  | —          | 4                                    |      |

| NVCC_ENET  | N=10       | Use maximal IO equation <sup>5</sup> |      |

| NVCC_LCD   | N=29       | Use maximal IO equation <sup>5</sup> |      |

| NVCC_GPIO  | N=24       | Use maximal IO equation <sup>5</sup> |      |

| NVCC_CSI   | N=20       | Use maximal IO equation <sup>5</sup> |      |

| NVCC_EIM   | N=53       | Use maximal IO equation <sup>5</sup> |      |

| NVCC_JTAG  | N=6        | Use maximal IO equation <sup>5</sup> |      |

| NVCC_RGMII | N=12       | Use maximal IO equation <sup>5</sup> |      |

| NVCC_SD1   | N=6        | Use maximal IO equation <sup>5</sup> |      |

| NVCC_SD2   | N=6        | Use maximal IO equation <sup>5</sup> |      |

| NVCC_SD3   | N=11       | Use maximal IO equation <sup>5</sup> |      |

| NVCC_NANDF | N=26       | Use maximal IO equation <sup>5</sup> |      |

|            | MISC       |                                      |      |

| DDR_VREF   | —          | 1                                    | mA   |

### Table 12. Maximal Supply Currents (continued)

<sup>1</sup> The actual maximum current drawn from VDDHIGH\_IN will be as shown plus any additional current drawn from the VDDHIGH\_CAP outputs, depending upon actual application configuration (for example, NVCC\_LVDS2P5, NVCC\_MIPI, or HDMI and PCIe VPH supplies).

<sup>2</sup> The maximum VDD\_SNVS\_IN current may be higher depending on specific operating configurations, such as BOOT\_MODE[1:0] not equal to 00, or use of the Tamper feature. During initial power on, VDD\_SNVS\_IN can draw up to 1 mA, if available. VDD\_SNVS\_CAP charge time will increase if less than 1 mA is available.

<sup>3</sup> This is the maximum current per active USB physical interface.

<sup>4</sup> The DRAM power consumption is dependent on several factors, such as external signal termination. DRAM power calculators are typically available from the memory vendors. They take in account factors, such as signal termination. See the i.MX 6Solo/DualLite Power Consumption Measurement Application Note (AN4576) for examples of DRAM power consumption during specific use case scenarios.

<sup>5</sup> General equation for estimated, maximal power consumption of an IO power supply:

$Imax = N \times C \times V \times (0.5 \times F)$

Where:

N—Number of IO pins supplied by the power line

C—Equivalent external capacitive load

V—IO voltage

(0.5 xF)—Data change rate. Up to 0.5 of the clock rate (F)

In this equation, Imax is in Amps, C in Farads, V in Volts, and F in Hertz.

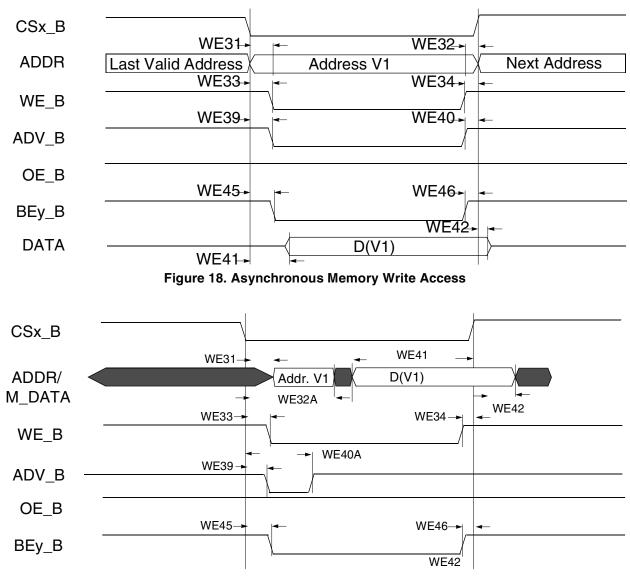

Figure 19. Asynchronous A/D Muxed Write Access

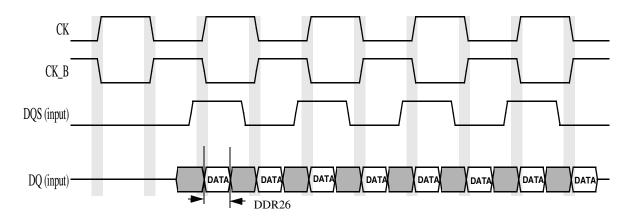

Figure 24 shows the read DDR3/DDR3L timing parameters. The timing parameters for this diagram appear in Table 43.

### Figure 24. DDR3/DDR3L Read Cycle

### Table 43. DDR3/DDR3L Read Cycle

| ID    | Parameter                              | Symbol | CK = 400 MHz |     | Unit |

|-------|----------------------------------------|--------|--------------|-----|------|

|       | Falanetei                              |        | Min          | Max | onne |

| DDR26 | Minimum required DQ valid window width |        | 450          | —   | ps   |

<sup>1</sup> To receive the reported setup and hold values, read calibration should be performed in order to locate the DQS in the middle of DQ window.

<sup>2</sup> All measurements are in reference to Vref level.

$^3\,$  Measurements were done using balanced load and 25  $\Omega$  resistor from outputs to VDD\_REF.

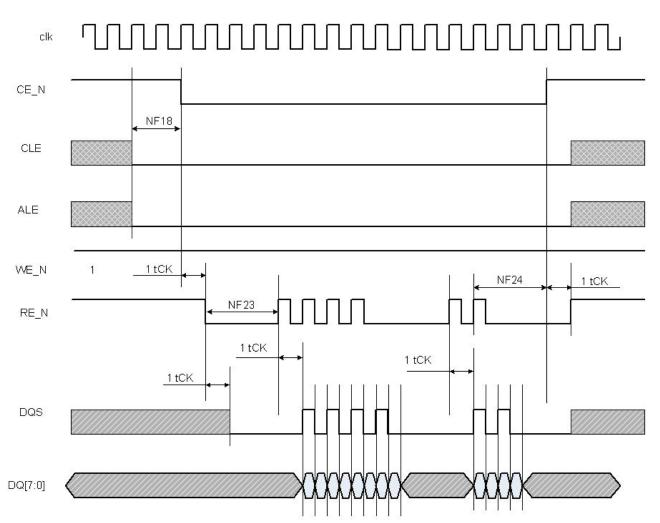

| ID   | Parameter                                      | Symbol | Tim<br>T = GPMI C | Unit |    |

|------|------------------------------------------------|--------|-------------------|------|----|

|      |                                                |        | Min.              | Max. |    |

| NF18 | CE# access time                                | tCE    | CE_DELAY x tCK    | —    | ns |

| NF19 | CE# hold time                                  | tCH    | 0.5 x tCK         | —    | ns |

| NF20 | Command/address DQ setup time                  | tCAS   | 0.5 x tCK         | _    | ns |

| NF21 | Command/address DQ<br>hold time                | tCAH   | 0.5 x tCK         | _    | ns |

| NF22 | clock period                                   | tCK    | 5                 |      | ns |

| NF23 | preamble delay                                 | tPRE   | PRE_DELAY x tCK   | —    | ns |

| NF24 | postamble delay                                | tPOST  | POST_DELAY x tCK  | —    | ns |

| NF25 | CLE and ALE setup time                         | tCALS  | 0.5 x tCK         | —    | ns |

| NF26 | CLE and ALE hold time                          | tCALH  | 0.5 x tCK         | —    | ns |

| NF27 | Data input to first DQS<br>latching transition | tDQSS  | tCK               | —    | ns |

Table 48. Source Synchronous Mode Timing Parameters<sup>1</sup>

<sup>1</sup> GPMI's Sync Mode output timing could be controlled by module's internal registers, say

HW\_GPMI\_TIMING2\_CE\_DELAY, HW\_GPMI\_TIMING\_PREAMBLE\_DELAY, and

HW\_GPMI\_TIMING2\_POST\_DELAY. This AC timing depends on these registers' settings. In the above table, we use CE\_DELAY/PRE\_DELAY/POST\_DELAY to represent each of these settings.

For DDR Source sync mode, Figure 35 shows the timing diagram of DQS/DQ read valid window. The typical value of tDQSQ is 0.85ns (max) and 1ns (max) for tQHS at 200MB/s. GPMI will sample DQ[7:0] at both rising and falling edge of an delayed DQS signal, which can be provided by an internal DPLL. The delay value can be controlled by GPMI register GPMI\_READ\_DDR\_DLL\_CTRL.SLV\_DLY\_TARGET(see the GPMI chapter of the i.MX 6Solo/6DualLite reference manual). Generally, the typical delay value of this register is equal to 0x7 which means 1/4 clock cycle delay expected. But if the board delay is big enough and cannot be ignored, the delay value should be made larger to compensate the board delay.

### 4.10.3 Samsung Toggle Mode AC Timing

### 4.10.3.1 Command and Address Timing

NOTE

Samsung Toggle Mode command and address timing is the same as ONFI 1.0 compatible Async mode AC timing. See Section 4.10.1, "Asynchronous Mode AC Timing (ONFI 1.0 Compatible)," for details.

Figure 37. Samsung Toggle Mode Data Read Timing

| ID   | Parameter                       | Symbol | Tim<br>T = GPMI C |      | Unit |  |

|------|---------------------------------|--------|-------------------|------|------|--|

|      |                                 |        | Min.              | Max. |      |  |

| NF18 | CE# access time                 | tCE    | CE_DELAY x tCK    | —    | ns   |  |

| NF19 | CE# hold time                   | tCH    | 0.5 x tCK         | —    | ns   |  |

| NF20 | Command/address DQ setup time   | tCAS   | 0.5 x tCK         | _    | ns   |  |

| NF21 | Command/address DQ<br>hold time | tCAH   | 0.5 x tCK         | _    | ns   |  |

| NF22 | clock period                    | tCK    | 7.5               |      | ns   |  |

Table 49. Samsung Toggle Mode Timing Parameters

### 4.11.2.2 ECSPI Slave Mode Timing

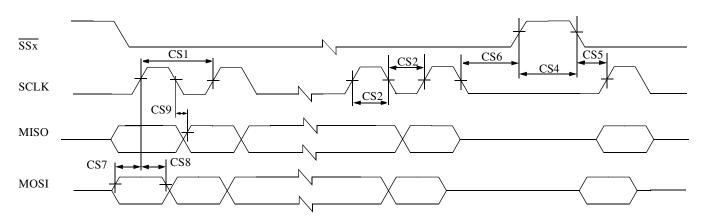

Figure 39 depicts the timing of ECSPI in slave mode. Table 51 lists the ECSPI slave mode timing characteristics.

Figure 39. ECSPI Slave Mode Timing Diagram

| ID  | Parameter                                                 | Symbol              | Min              | Max | Unit |

|-----|-----------------------------------------------------------|---------------------|------------------|-----|------|

| CS1 | SCLK Cycle Time-Read<br>SCLK Cycle Time-Write             | t <sub>clk</sub>    | 43<br>15         | _   | ns   |

| CS2 | SCLK High or Low Time–Read<br>SCLK High or Low Time–Write | t <sub>SW</sub>     | 21.5<br>7        | _   | ns   |

| CS4 | SSx pulse width                                           | t <sub>CSLH</sub>   | Half SCLK period | _   | ns   |

| CS5 | SSx Lead Time (CS setup time)                             | t <sub>SCS</sub>    | 5                | _   | ns   |

| CS6 | SSx Lag Time (CS hold time)                               | t <sub>HCS</sub>    | 5                | _   | ns   |

| CS7 | MOSI Setup Time                                           | t <sub>Smosi</sub>  | 4                | _   | ns   |

| CS8 | MOSI Hold Time                                            | t <sub>Hmosi</sub>  | 4                | _   | ns   |

| CS9 | MISO Propagation Delay ( $C_{LOAD} = 20 \text{ pF}$ )     | t <sub>PDmiso</sub> | 4                | 19  | ns   |

### Table 51. ECSPI Slave Mode Timing Parameters

| No. | Characteristics <sup>1,2</sup>                                      | Symbol | Expression <sup>2</sup> | Min         | Max          | Condition <sup>3</sup> | Unit |

|-----|---------------------------------------------------------------------|--------|-------------------------|-------------|--------------|------------------------|------|

| 81  | SCKT rising edge to FST out (wr) low <sup>5</sup>                   |        |                         | _           | 22.0<br>12.0 | x ck<br>i ck           | ns   |

| 82  | SCKT rising edge to FST out (wl) high                               | —      | —                       | _           | 19.0<br>9.0  | x ck<br>i ck           | ns   |

| 83  | SCKT rising edge to FST out (wl) low                                | —      | —                       | _           | 20.0<br>10.0 | x ck<br>i ck           | ns   |

| 84  | SCKT rising edge to data out enable from high impedance             | —      |                         | _           | 22.0<br>17.0 | x ck<br>i ck           | ns   |

| 86  | SCKT rising edge to data out valid                                  | —      |                         | _           | 18.0<br>13.0 | x ck<br>i ck           | ns   |

| 87  | SCKT rising edge to data out high impedance <sup>67</sup>           | —      |                         | _           | 21.0<br>16.0 | x ck<br>i ck           | ns   |

| 89  | FST input (bl, wr) setup time before SCKT falling edge <sup>5</sup> | —      | —                       | 2.0<br>18.0 | —            | x ck<br>i ck           | ns   |

| 90  | FST input (wl) setup time before SCKT falling edge                  | —      |                         | 2.0<br>18.0 | _            | x ck<br>i ck           | ns   |

| 91  | FST input hold time after SCKT falling edge                         |        |                         | 4.0<br>5.0  |              | x ck<br>i ck           | ns   |

| 95  | HCKR/HCKT clock cycle                                               | —      | 2 x T <sub>C</sub>      | 15          |              | —                      | ns   |

| 96  | HCKT input rising edge to SCKT output                               | —      | —                       | —           | 18.0         | —                      | ns   |

| 97  | HCKR input rising edge to SCKR output                               | —      | —                       | _           | 18.0         | —                      | ns   |

#### Table 52. Enhanced Serial Audio Interface (ESAI) Timing (continued)

<sup>1</sup> i ck = internal clock

x ck = external clock

i ck a = internal clock, asynchronous mode

(asynchronous implies that SCKT and SCKR are two different clocks)

i ck s = internal clock, synchronous mode

(synchronous implies that SCKT and SCKR are the same clock)

- <sup>2</sup> bl = bit length

- wl = word length

wr = word length relative

- <sup>3</sup> SCKT(SCKT pin) = transmit clock SCKR(SCKR pin) = receive clock FST(FST pin) = transmit frame sync FSR(FSR pin) = receive frame sync HCKT(HCKT pin) = transmit high frequency clock HCKR(HCKR pin) = receive high frequency clock

- <sup>4</sup> For the internal clock, the external clock cycle is defined by lcyc and the ESAI control register.

- <sup>5</sup> The word-relative frame sync signal waveform relative to the clock operates in the same manner as the bit-length frame sync signal waveform, but it spreads from one serial clock before the first bit clock (like the bit length frame sync signal), until the second-to-last bit clock of the first word in the frame.

- <sup>6</sup> Periodically sampled and not 100% tested.

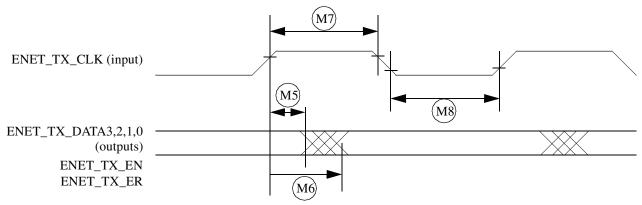

Figure 46 shows MII transmit signal timings. Table 57 describes the timing parameters (M5–M8) shown in the figure.

Figure 46. MII Transmit Signal Timing Diagram

Table 57. MII Transmit Signal Timing

| ID | Characteristic <sup>1</sup>                                         | Min. | Max. | Unit               |

|----|---------------------------------------------------------------------|------|------|--------------------|

| M5 | ENET_TX_CLK to ENET_TX_DATA3,2,1,0, ENET_TX_EN, ENET_TX_ER invalid  | 5    | _    | ns                 |

| M6 | ENET_TX_CLK to ENET_TX_DATA3,2,1,0, ENET_TX_EN,<br>ENET_TX_ER valid | _    | 20   | ns                 |

| M7 | ENET_TX_CLK pulse width high                                        | 35%  | 65%  | ENET_TX_CLK period |

| M8 | ENET_TX_CLK pulse width low                                         | 35%  | 65%  | ENET_TX_CLK period |

<sup>1</sup> ENET\_TX\_EN, ENET\_TX\_CLK, and ENET0\_TXD0 have the same timing in 10-Mbps 7-wire interface mode.

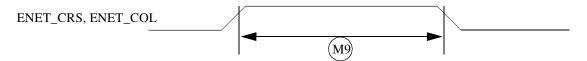

# 4.11.5.1.3 MII Asynchronous Inputs Signal Timing (ENET\_CRS and ENET\_COL)

Figure 47 shows MII asynchronous input timings. Table 58 describes the timing parameter (M9) shown in the figure.

Figure 47. MII Async Inputs Timing Diagram

| Table 58. MII Asynchronous | Inputs Signal Timing |

|----------------------------|----------------------|

|----------------------------|----------------------|

| ID              | Characteristic                           | Min. | Max. | Unit               |

|-----------------|------------------------------------------|------|------|--------------------|

| M9 <sup>1</sup> | ENET_CRS to ENET_COL minimum pulse width | 1.5  | _    | ENET_TX_CLK period |

<sup>1</sup> ENET\_COL has the same timing in 10-Mbit 7-wire interface mode.

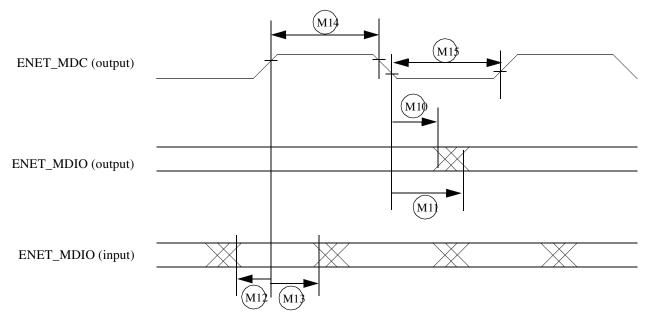

### 4.11.5.1.4 MII Serial Management Channel Timing (ENET\_MDIO and ENET\_MDC)

The MDC frequency is designed to be equal to or less than 2.5 MHz to be compatible with the IEEE 802.3 MII specification. However the ENET can function correctly with a maximum MDC frequency of 15 MHz.

Figure 48 shows MII asynchronous input timings. Table 59 describes the timing parameters (M10–M15) shown in the figure.

Figure 48. MII Serial Management Channel Timing Diagram

| ID  | Characteristic                                                             | Min. | Max. | Unit            |

|-----|----------------------------------------------------------------------------|------|------|-----------------|

| M10 | ENET_MDC falling edge to ENET_MDIO output invalid (min. propagation delay) | 0    | —    | ns              |

| M11 | ENET_MDC falling edge to ENET_MDIO output valid (max. propagation delay)   | _    | 5    | ns              |

| M12 | ENET_MDIO (input) to ENET_MDC rising edge setup                            | 18   | —    | ns              |

| M13 | ENET_MDIO (input) to ENET_MDC rising edge hold                             | 0    | —    | ns              |

| M14 | ENET_MDC pulse width high                                                  | 40%  | 60%  | ENET_MDC period |

| M15 | ENET_MDC pulse width low                                                   | 40%  | 60%  | ENET_MDC period |

### 4.11.5.2 RMII Mode Timing

In RMII mode, ENET\_CLK is used as the REF\_CLK, which is a 50 MHz ± 50 ppm continuous reference clock. ENET\_RX\_EN is used as the CRS\_DV in RMII. Other signals under RMII mode include ENET\_TX\_EN, ENET0\_TXD[1:0], ENET0\_RXD[1:0] and ENET\_RX\_ER.

| i.MX 6Solo/6DualLite  |                             |               |               | LCD           |                             |                 |                 |                                                                     |

|-----------------------|-----------------------------|---------------|---------------|---------------|-----------------------------|-----------------|-----------------|---------------------------------------------------------------------|

|                       | RGB,                        | R             | GB/TV S       | Signal A      | llocation                   | (Examp          | ole)            | Comment <sup>1</sup>                                                |

| Port Name<br>(x=0, 1) | Signal<br>Name<br>(General) | 16-bit<br>RGB | 18-bit<br>RGB | 24 Bit<br>RGB | 8-bit<br>YCrCb <sup>2</sup> | 16-bit<br>YCrCb | 20-bit<br>YCrCb |                                                                     |

| DISPx_DAT0            | DAT[0]                      | B[0]          | B[0]          | B[0]          | Y/C[0]                      | C[0]            | C[0]            | The restrictions are as follows:<br>• There are maximal three       |

| DISPx_DAT1            | DAT[1]                      | B[1]          | B[1]          | B[1]          | Y/C[1]                      | C[1]            | C[1]            | continuous groups of bits that<br>could be independently            |

| DISPx_DAT2            | DAT[2]                      | B[2]          | B[2]          | B[2]          | Y/C[2]                      | C[2]            | C[2]            | mapped to the external bus.<br>Groups should not be                 |

| DISPx_DAT3            | DAT[3]                      | B[3]          | B[3]          | B[3]          | Y/C[3]                      | C[3]            | C[3]            | <ul><li>overlapped.</li><li>The bit order is expressed in</li></ul> |

| DISPx_DAT4            | DAT[4]                      | B[4]          | B[4]          | B[4]          | Y/C[4]                      | C[4]            | C[4]            | each of the bit groups, for<br>example, B[0] = least significant    |

| DISPx_DAT5            | DAT[5]                      | G[0]          | B[5]          | B[5]          | Y/C[5]                      | C[5]            | C[5]            | blue pixel bit                                                      |

| DISPx_DAT6            | DAT[6]                      | G[1]          | G[0]          | B[6]          | Y/C[6]                      | C[6]            | C[6]            |                                                                     |

| DISPx_DAT7            | DAT[7]                      | G[2]          | G[1]          | B[7]          | Y/C[7]                      | C[7]            | C[7]            |                                                                     |

| DISPx_DAT8            | DAT[8]                      | G[3]          | G[2]          | G[0]          |                             | Y[0]            | C[8]            |                                                                     |

| DISPx_DAT9            | DAT[9]                      | G[4]          | G[3]          | G[1]          |                             | Y[1]            | C[9]            |                                                                     |

| DISPx_DAT10           | DAT[10]                     | G[5]          | G[4]          | G[2]          | _                           | Y[2]            | Y[0]            | -                                                                   |

| DISPx_DAT11           | DAT[11]                     | R[0]          | G[5]          | G[3]          | _                           | Y[3]            | Y[1]            | -                                                                   |

| DISPx_DAT12           | DAT[12]                     | R[1]          | R[0]          | G[4]          | _                           | Y[4]            | Y[2]            |                                                                     |

| DISPx_DAT13           | DAT[13]                     | R[2]          | R[1]          | G[5]          | _                           | Y[5]            | Y[3]            | -                                                                   |

| DISPx_DAT14           | DAT[14]                     | R[3]          | R[2]          | G[6]          | _                           | Y[6]            | Y[4]            | -                                                                   |

| DISPx_DAT15           | DAT[15]                     | R[4]          | R[3]          | G[7]          |                             | Y[7]            | Y[5]            |                                                                     |

| DISPx_DAT16           | DAT[16]                     | —             | R[4]          | R[0]          |                             |                 | Y[6]            |                                                                     |

| DISPx_DAT17           | DAT[17]                     |               | R[5]          | R[1]          |                             |                 | Y[7]            |                                                                     |

| DISPx_DAT18           | DAT[18]                     | _             |               | R[2]          |                             |                 | Y[8]            |                                                                     |

| DISPx_DAT19           | DAT[19]                     | _             |               | R[3]          | _                           | -               | Y[9]            |                                                                     |

| DISPx_DAT20           | DAT[20]                     |               |               | R[4]          | _                           | —               |                 |                                                                     |

| DISPx_DAT21           | DAT[21]                     | _             | _             | R[5]          |                             |                 |                 |                                                                     |

### Table 67. Video Signal Cross-Reference

# 4.11.14 PCIe PHY Parameters

The PCIe interface complies with PCIe specification Gen2 x1 lane and supports the PCI Express 1.1/2.0 standard.

### 4.11.14.1 PCIE\_REXT Reference Resistor Connection

The impedance calibration process requires connection of reference resistor 200  $\Omega$ . 1% precision resistor on PCIE\_REXT pads to ground. It is used for termination impedance calibration.

# 4.11.15 Pulse Width Modulator (PWM) Timing Parameters

This section describes the electrical information of the PWM. The PWM can be programmed to select one of three clock signals as its source frequency. The selected clock signal is passed through a prescaler before being input to the counter. The output is available at the pulse-width modulator output (PWMO) external pin.

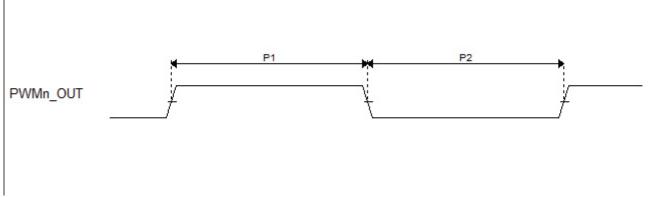

Figure 84 depicts the timing of the PWM, and Table 74 lists the PWM timing parameters.

| Figure | 84. | PWM | Timing |

|--------|-----|-----|--------|

|--------|-----|-----|--------|

Table 74. PWM Output Timing Parameters

| ID | Parameter                   | Min | Мах     | Unit |

|----|-----------------------------|-----|---------|------|

|    | PWM Module Clock Frequency  | 0   | ipg_clk | MHz  |

| P1 | PWM output pulse width high | 15  |         | ns   |

| P2 | PWM output pulse width low  | 15  |         | ns   |

# 4.11.16 SCAN JTAG Controller (SJC) Timing Parameters

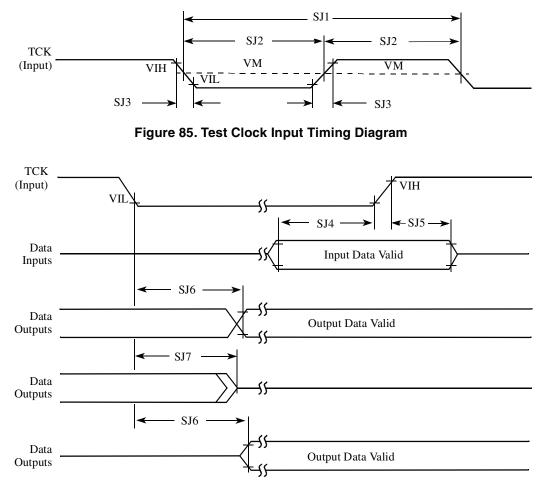

Figure 85 depicts the SJC test clock input timing. Figure 86 depicts the SJC boundary scan timing. Figure 87 depicts the SJC test access port. Signal parameters are listed in Table 75.

Figure 86. Boundary Scan (JTAG) Timing Diagram

### NOTE

- All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal STCK/SRCK and/or the frame sync STFS/SRFS shown in the tables and in the figures.

- All timings are on Audiomux Pads when SSI is being used for data transfer.

- "Tx" and "Rx" refer to the Transmit and Receive sections of the SSI.

- The terms, WL and BL, refer to Word Length (WL) and Bit Length (BL).

- For internal Frame Sync operation using external clock, the FS timing is same as that of Tx Data (for example, during AC97 mode of operation).

# 4.11.19 UART I/O Configuration and Timing Parameters

### 4.11.19.1 UART RS-232 I/O Configuration in Different Modes

The i.MX 6Solo/6DualLite UART interfaces can serve both as DTE or DCE device. This can be configured by the DCEDTE control bit (default 0 — DCE mode). Table 82 shows the UART I/O configuration based on the enabled mode.

| Port    |           | DTE Mode                    |           | DCE Mode                    |

|---------|-----------|-----------------------------|-----------|-----------------------------|

| Pon     | Direction | Description                 | Direction | Description                 |

| RTS     | Output    | RTS from DTE to DCE         | Input     | RTS from DTE to DCE         |

| CTS     | Input     | CTS from DCE to DTE         | Output    | CTS from DCE to DTE         |

| DTR     | Output    | DTR from DTE to DCE         | Input     | DTR from DTE to DCE         |

| DSR     | Input     | DSR from DCE to DTE         | Output    | DSR from DCE to DTE         |

| DCD     | Input     | DCD from DCE to DTE         | Output    | DCD from DCE to DTE         |

| RI      | Input     | RING from DCE to DTE        | Output    | RING from DCE to DTE        |

| TXD_MUX | Input     | Serial data from DCE to DTE | Output    | Serial data from DCE to DTE |

| RXD_MUX | Output    | Serial data from DTE to DCE | Input     | Serial data from DTE to DCE |

Table 82. UART I/O Configuration vs. Mode

### 4.11.19.2 UART RS-232 Serial Mode Timing

The following sections describe the electrical information of the UART module in the RS-232 mode.

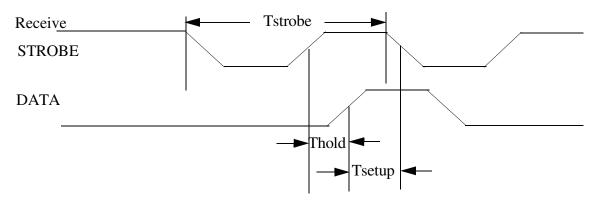

## 4.11.20.2 Receive Timing

Figure 100. USB HSIC Receive Waveform

| Table 88. U | JSB HSIC Receiv | ve Parameters <sup>1</sup> |

|-------------|-----------------|----------------------------|

|-------------|-----------------|----------------------------|

| Name    | Parameter                       | Min   | Max   | Unit | Comment                        |

|---------|---------------------------------|-------|-------|------|--------------------------------|

| Tstrobe | strobe period                   | 4.166 | 4.167 | ns   |                                |

| Thold   | data hold time                  | 300   |       | ps   | Measured at 50% point          |

| Tsetup  | data setup time                 | 365   |       | ps   | Measured at 50% point          |

| Tslew   | strobe/data rising/falling time | 0.7   | 2     | V/ns | Averaged from 30% – 70% points |

<sup>1</sup> The timings in the table are guaranteed when:

-AC I/O voltage is between 0.9x to 1x of the I/O supply

-DDR\_SEL configuration bits of the I/O are set to (10)b

# 4.11.21 USB PHY Parameters

This section describes the USB-OTG PHY and the USB Host port PHY parameters.

The USB PHY meets the electrical compliance requirements defined in the Universal Serial Bus Revision 2.0 OTG, USB Host with the amendments below (On-The-Go and Embedded Host Supplement to the USB Revision 2.0 Specification is not applicable to Host port).

- USB ENGINEERING CHANGE NOTICE

- Title: 5V Short Circuit Withstand Requirement Change

- Applies to: Universal Serial Bus Specification, Revision 2.0

- Errata for USB Revision 2.0 April 27, 2000 as of 12/7/2000

- USB ENGINEERING CHANGE NOTICE

- Title: Pull-up/Pull-down resistors

- Applies to: Universal Serial Bus Specification, Revision 2.0

- USB ENGINEERING CHANGE NOTICE

- Title: Suspend Current Limit Changes

- Applies to: Universal Serial Bus Specification, Revision 2.0

Package Information and Contact Assignments

# 6 Package Information and Contact Assignments

This section includes the contact assignment information and mechanical package drawing.

# 6.1 21x21 mm Package Information

### 6.1.1 Case 2240, 21 x 21 mm, 0.8 mm Pitch, 25 x 25 Ball Matrix

Figure 101 shows the top, bottom, and side views of the 21×21 mm BGA package.

NOTES:

1. ALL DIMENSIONS IN MILLIMETERS.

2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

$\$  MAXIMUM SOLDER BALL DIAMETER MEASURED PARALLEL TO DATUM A.

DATUM A, THE SEATING PLANE, IS DETERMINED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS.

$\label{eq:parallelism}$  measurement shall exclude any effect of mark on top surface of package.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OU | TLINE   | PRINT VERSION NO   | T TO SCALE  |

|---------------------------------------------------------|---------------|---------|--------------------|-------------|

| TITLE: PBGA, LOW PRO                                    | FILE,         | DOCUME  | NT NO: 98ASA00404D | REV: O      |

| FINE PITCH, 624                                         | , .           | CASE NU | JMBER: 2240-01     | 27 SEP 2011 |

| 21 X 21 PKG, 0.8 MM F                                   | РІТСН (МАР)   | STANDAF | RD: NON-JEDEC      |             |

#### Figure 101. 21 x 21 mm BGA, Case 2240 Package Top, Bottom, and Side Views

|    | AE             | AD           | AC          | AB           | AA           |

|----|----------------|--------------|-------------|--------------|--------------|

| -  | GND            | DRAM_D5      | DRAM_D4     | LVDS1_TX2_N  | LVDS1_TX1_P  |

| 2  | DRAM_D1        | DRAM_D0      | DRAM_VREF   | LVDS1_TX2_P  | LVDS1_TX1_N  |

| e  | DRAM_SDQS0     | DRAM_SDQS0_B | DRAM_DQM0   | GND          | LVDS1_TX3_N  |

| 4  | DRAM_D7        | GND          | DRAM_D2     | DRAM_D6      | LVDS1_TX3_P  |

| 2  | DRAM_D9        | DRAM_D8      | DRAM_D13    | DRAM_D12     | DRAM_D3      |

| 9  | DRAM_SDQS1_B   | DRAM_SDQS1   | DRAM_DQM1   | DRAM_D14     | DRAM_D10     |

| 2  | DRAM_D11       | GND          | DRAM_D15    | DRAM_D16     | GND          |

| œ  | DRAM_SDQS2_B   | DRAM_SDQS2   | DRAM_D22    | DRAM_DQM2    | DRAM_D17     |

| თ  | DRAM_D24       | DRAM_D29     | DRAM_D28    | DRAM_D18     | DRAM_D23     |

| 10 | DRAM_DQM3      | GND          | DRAM_SDQS3  | DRAM_SDQS3_B | GND          |

| ÷  | DRAM_D26       | DRAM_D30     | DRAM_D31    | DRAM_D27     | DRAM_SDCKE1  |

| 12 | DRAM_A9        | DRAM_A12     | DRAM_A11    | DRAM_SDBA2   | DRAM_A14     |

| 13 | DRAM_A5        | GND          | DRAM_A6     | DRAM_A8      | GND          |

| 14 | DRAM_SDCLK_1_B | DRAM_SDCLK_1 | DRAM_A0     | DRAM_A1      | DRAM_A2      |

| 15 | DRAM_SDCLK_0_B | DRAM_SDCLK_0 | DRAM_SDBA0  | DRAM_RAS     | DRAM_A10     |

| 16 | DRAM_CAS       | GND          | DRAM_SDODT0 | DRAM_SDWE    | GND          |

| 17 | ZQPAD          | DRAM_CS1     | DRAM_A13    | DRAM_SDODT1  | DRAM_D32     |

| 18 | DRAM_SDQS4_B   | DRAM_SDQS4   | DRAM_D34    | DRAM_DQM4    | DRAM_D33     |

| 19 | DRAM_D35       | GND          | DRAM_D39    | DRAM_D38     | GND          |

| 20 | DRAM_SDQS5_B   | DRAM_SDQS5   | DRAM_DQM5   | DRAM_D41     | DRAM_D45     |

| 21 | DRAM_D46       | DRAM_D43     | DRAM_D47    | DRAM_D42     | DRAM_D57     |

| 22 | DRAM_D49       | GND          | DRAM_D48    | DRAM_D52     | GND          |

| 23 | DRAM_SDQS6_B   | DRAM_SDQS6   | DRAM_D53    | DRAM_D60     | DRAM_D61     |

| 24 | DRAM_D50       | DRAM_DQM6    | DRAM_D51    | GND          | DRAM_SDQS7_B |

| 25 | GND            | DRAM_D54     | DRAM_D55    | DRAM_D56     | DRAM_SDQS7   |

|    | AE             | AD           | AC          | AB           | АА           |

Table 94. 21 x 21 mm, 0.8 mm Pitch Ball Map (continued)