#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Betuns                             |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Active                                                                                                              |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 1 Core, 32-Bit                                                                                                      |

| Speed                              | 1.0GHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON™ SIMD                                                                                              |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | -                                                                                                                   |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | 0°C ~ 95°C (TJ)                                                                                                     |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-LFBGA                                                                                                           |

| Supplier Device Package            | 624-MAPBGA (21x21)                                                                                                  |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6s8dvm10ac                                             |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Block Mnemonic                                                                       | Block Name                            | Subsystem                     | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------|---------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 512x8 Fuse Box                                                                       | Electrical Fuse Array                 | Security                      | Electrical Fuse Array. Enables to setup Boot Modes,<br>Security Levels, Security Keys, and many other system<br>parameters.<br>The i.MX 6Solo/6DualLite processors consist of<br>512x8-bit fuse fox accessible through OCOTP_CTRL<br>interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| GPIO-1<br>GPIO-2<br>GPIO-3<br>GPIO-4<br>GPIO-5<br>GPIO-6<br>GPIO-7                   | General Purpose I/O<br>Modules        | System Control<br>Peripherals | Used for general purpose input/output to external ICs.<br>Each GPIO module supports 32 bits of I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GPMI                                                                                 | General Media Interface               | Connectivity<br>Peripherals   | The GPMI module supports up to 8x NAND devices.<br>40-bit ECC encryption/decryption for NAND Flash<br>controller (GPMI2). The GPMI supports separate DMA<br>channels per NAND device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| GPT                                                                                  | General Purpose Timer                 | Timer Peripherals             | Each GPT is a 32-bit "free-running" or "set and forget"<br>mode timer with programmable prescaler and compare<br>and capture register. A timer counter value can be<br>captured using an external event and can be configured<br>to trigger a capture event on either the leading or trailing<br>edges of an input pulse. When the timer is configured to<br>operate in "set and forget" mode, it is capable of<br>providing precise interrupts at regular intervals with<br>minimal processor intervention. The counter has output<br>compare logic to provide the status and interrupt at<br>comparison. This timer can be configured to run either<br>on an external clock or on an internal clock. |

| GPU3Dv5                                                                              | Graphics Processing<br>Unit, ver.5    | Multimedia<br>Peripherals     | The GPU3Dv5 provides hardware acceleration for 3D graphics algorithms with sufficient processor power to run desktop quality interactive graphics applications on displays up to HD1080 resolution. The GPU3D provides OpenGL ES 2.0, including extensions, OpenGL ES 1.1, and OpenVG 1.1                                                                                                                                                                                                                                                                                                                                                                                                              |

| GPU2Dv2                                                                              | Graphics Processing<br>Unit-2D, ver 2 | Multimedia<br>Peripherals     | The GPU2Dv2 provides hardware acceleration for 2D graphics algorithms, such as Bit BLT, stretch BLT, and many other 2D functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| HDMI Tx                                                                              | HDMI Tx i/f                           | Multimedia<br>Peripherals     | The HDMI module provides HDMI standard i/f port to an HDMI 1.4 compliant display.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| HSI                                                                                  | MIPI HSI i/f                          | Connectivity<br>Peripherals   | The MIPI HSI provides a standard MIPI interface to the applications processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| l <sup>2</sup> C-1<br>l <sup>2</sup> C-2<br>l <sup>2</sup> C-3<br>l <sup>2</sup> C-4 | I <sup>2</sup> C Interface            | Connectivity<br>Peripherals   | I <sup>2</sup> C provide serial interface for external devices. Data rates of up to 400 kbps are supported.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### **Modules List**

| Block Mnemonic | Block Name                    | Subsystem                            | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|-------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VPU            | Video Processing Unit         | Multimedia<br>Peripherals            | A high-performing video processing unit (VPU), which<br>covers many SD-level and HD-level video decoders and<br>SD-level encoders as a multi-standard video codec<br>engine as well as several important video processing,<br>such as rotation and mirroring.<br>See the i. <i>MX 6Solo/6DualLite Reference Manual</i><br>( <i>IMX6SDLRM</i> ) for complete list of VPU's<br>decoding/encoding capabilities.                                                                                                                                                                                                                                                                                                                                                                                            |

| WDOG-1         | Watch Dog                     | Timer Peripherals                    | The Watch Dog Timer supports two comparison points<br>during each counting period. Each of the comparison<br>points is configurable to evoke an interrupt to the ARM<br>core, and a second point evokes an external event on<br>the WDOG line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| WDOG-2<br>(TZ) | Watch Dog (TrustZone)         | Timer Peripherals                    | The TrustZone Watchdog (TZ WDOG) timer module<br>protects against TrustZone starvation by providing a<br>method of escaping normal mode and forcing a switch<br>to the TZ mode. TZ starvation is a situation where the<br>normal OS prevents switching to the TZ mode. Such<br>situation is undesirable as it can compromise the<br>system's security. Once the TZ WDOG module is<br>activated, it must be serviced by TZ software on a<br>periodic basis. If servicing does not take place, the timer<br>times out. Upon a time-out, the TZ WDOG asserts a TZ<br>mapped interrupt that forces switching to the TZ mode.<br>If it is still not served, the TZ WDOG asserts a security<br>violation signal to the CSU. The TZ WDOG module<br>cannot be programmed or deactivated by a normal<br>mode SW. |

| WEIM           | NOR-Flash /PSRAM<br>interface | Connectivity<br>Peripherals          | <ul> <li>The WEIM NOR-FLASH / PSRAM provides:</li> <li>Support 16-bit (in muxed IO mode only) PSRAM memories (sync and async operating modes), at slow frequency</li> <li>Support 16-bit (in muxed IO mode only) NOR-Flash memories, at slow frequency</li> <li>Multiple chip selects</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| XTALOSC        | Crystal Oscillator I/F        | Clocks, Resets, and<br>Power Control | The XTALOSC module enables connectivity to external crystal oscillator device. In a typical application use-case, it is used for 24 MHz oscillator to provide USB required frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Parameter Description                                                      | Symbol               | Min | Мах         | Unit |

|----------------------------------------------------------------------------|----------------------|-----|-------------|------|

| ESD damage immunity:                                                       | V <sub>esd</sub>     |     |             |      |

| <ul><li>Human Body Model (HBM)</li><li>Charge Device Model (CDM)</li></ul> |                      | _   | 2000<br>500 | V    |

| Storage temperature range                                                  | T <sub>STORAGE</sub> | -40 | 150         | °C   |

### Table 7. Absolute Maximum Ratings (continued)

<sup>1</sup> OVDD is the I/O supply voltage.

# 4.1.2 Thermal Resistance

## 4.1.2.1 BGA Case 2240 Package Thermal Resistance

Table 8 displays the thermal resistance data.

### Table 8. Thermal Resistance Data

| Rating                                 | Test Conditions                                                                                                          | Symbol                                    | Value    | Unit         |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------|--------------|

| Junction to Ambient <sup>1</sup>       | Single-layer board (1s); natural convection <sup>2</sup><br>Four-layer board (2s2p); natural convection <sup>2</sup>     | ${\sf R}_{	heta JA} \ {\sf R}_{	heta JA}$ | 38<br>23 | °C/W<br>°C/W |

| Junction to Ambient <sup>1</sup>       | Single-layer board (1s); airflow 200 ft/min <sup>2,3</sup><br>Four-layer board (2s2p); airflow 200 ft/min <sup>2,3</sup> | ${\sf R}_{	heta JA} \ {\sf R}_{	heta JA}$ | 30<br>20 | °C/W<br>°C/W |

| Junction to Board <sup>1,4</sup>       |                                                                                                                          | $R_{	extsf{	heta}JB}$                     | 14       | °C/W         |

| Junction to Case <sup>1,5</sup>        |                                                                                                                          | $R_{	extsf{	heta}JC}$                     | 6        | °C/W         |

| Junction to Package Top <sup>1,6</sup> | Natural Convection                                                                                                       | $\Psi_{JT}$                               | 2        | °C/W         |

<sup>1</sup> Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

<sup>2</sup> Per JEDEC JESD51-2 with the single layer board horizontal. Thermal test board meets JEDEC specification for the specified package.

<sup>3</sup> Per JEDEC JESD51-6 with the board horizontal.

<sup>4</sup> Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

<sup>5</sup> Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

<sup>6</sup> Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

- VDDARM\_IN supply must be turned ON together with VDDSOC\_IN supply or not delayed more than 1 ms

- VDDARM\_CAP must not exceed VDDSOC\_CAP by more than 50 mV.

## NOTE

The POR\_B input (if used) must be immediately asserted at power-up and remain asserted until after the last power rail reaches its working voltage. In the absence of an external reset feeding the POR\_B input, the internal POR module takes control. See the *i.MX 6Solo/6DualLite Reference Manual* for further details and to ensure that all necessary requirements are being met.

### NOTE

Need to ensure that there is no back voltage (leakage) from any supply on the board towards the 3.3 V supply (for example, from the external components that use both the 1.8 V and 3.3 V supplies).

## NOTE

USB\_OTG\_VBUS and USB\_H1\_VBUS are not part of the power supply sequence and may be powered at any time.

# 4.2.2 Power-Down Sequence

No special restrictions for i.MX 6Solo/6DualLite IC.

# 4.2.3 **Power Supplies Usage**

All I/O pins should not be externally driven while the I/O power supply for the pin (NVCC\_xxx) is OFF. This can cause internal latch-up and malfunctions due to reverse current flows. For information about I/O power supply of each pin, see "Power Rail" columns in pin list tables of Section 6, "Package Information and Contact Assignments."

# 4.3 Integrated LDO Voltage Regulator Parameters

Various internal supplies can be powered ON from internal LDO voltage regulators. All the supply pins named \*\_CAP must be connected to external capacitors. The onboard LDOs are intended for internal use only and should not be used to power any external circuitry. See the *i.MX 6Solo/6DualLite Reference Manual (IMX6SDLRM)* for details on the power tree scheme.

## NOTE

The \*\_CAP signals should not be powered externally. These signals are intended for internal LDO or LDO bypass operation only.

# 4.3.1 Digital Regulators (LDO\_ARM, LDO\_PU, LDO\_SOC)

There are three digital LDO regulators ("Digital", because of the logic loads that they drive, not because of their construction). The advantages of the regulators are to reduce the input supply variation because of

# 4.4.3 Ethernet PLL

| Parameter          | Value                   |

|--------------------|-------------------------|

| Clock output range | 500 MHz                 |

| Reference clock    | 24 MHz                  |

| Lock time          | <11250 reference cycles |

### Table 19. Ethernet PLL's Electrical Parameters

# 4.4.4 480 MHz PLL

### Table 20. 480 MHz PLL's Electrical Parameters

| Parameter          | Value                 |

|--------------------|-----------------------|

| Clock output range | 480 MHz PLL output    |

| Reference clock    | 24 MHz                |

| Lock time          | <383 reference cycles |

# 4.4.5 ARM PLL

### Table 21. ARM PLL's Electrical Parameters

| Parameter          | Value                  |

|--------------------|------------------------|

| Clock output range | 650 MHz ~ 1.3 GHz      |

| Reference clock    | 24 MHz                 |

| Lock time          | <2250 reference cycles |

# 4.5 **On-Chip Oscillators**

## 4.5.1 OSC24M

This block implements an amplifier that when combined with a suitable quartz crystal and external load capacitors implements an oscillator. The oscillator is powered from NVCC\_PLL\_OUT.

The system crystal oscillator consists of a Pierce-type structure running off the digital supply. A straight forward biased-inverter implementation is used.

# 4.5.2 OSC32K

This block implements an amplifier that when combined with a suitable quartz crystal and external load capacitors implements a low power oscillator. It also implements a power mux such that it can be powered from either a ~3 V backup battery (VDD\_SNVS\_IN) or VDDHIGH\_IN such as the oscillator consumes

| Table 25. DDR3/DDR3L I/O DC Electrical Char | racteristics (continued) |

|---------------------------------------------|--------------------------|

|---------------------------------------------|--------------------------|

| Parameters                               | Symbol | Test Conditions  | Min  | Мах | Unit |

|------------------------------------------|--------|------------------|------|-----|------|

| 240 $\Omega$ unit calibration resolution | Rres   |                  |      | 10  | Ω    |

| Keeper Circuit Resistance                | Rkeep  |                  | 105  | 165 | kΩ   |

| Input current (no pull-up/down)          | lin    | VI = 0,VI = OVDD | -2.9 | 2.9 | μA   |

<sup>1</sup> OVDD – I/O power supply (1.425 V–1.575 V for DDR3 and 1.283 V–1.45 V for DDR3L)

<sup>2</sup> Vref – DDR3/DDR3L external reference voltage

<sup>3</sup> The single-ended signals need to be within the respective limits (Vih(dc) max, Vil(dc) min) for single-ended signals as well as the limitations for overshoot and undershoot.

## 4.6.3 LVDS I/O DC Parameters

The LVDS interface complies with TIA/EIA 644-A standard. See TIA/EIA STANDARD 644-A, "Electrical Characteristics of Low Voltage Differential Signaling (LVDS) Interface Circuits" for details.

Table 26 shows the Low Voltage Differential Signaling (LVDS) I/O DC parameters.

| Parameter                   | Symbol | Test Conditions         | Min   | Тур   | Мах   | Unit |

|-----------------------------|--------|-------------------------|-------|-------|-------|------|

| Output Differential Voltage | VOD    | Rload-100 $\Omega$ Diff | 250   | 350   | 450   | mV   |

| Output High Voltage         | VOH    | IOH = 0 mA              | 1.25  | 1.375 | 1.6   | V    |

| Output Low Voltage          | VOL    | IOL = 0 mA              | 0.9   | 1.025 | 1.25  | V    |

| Offset Voltage              | VOS    |                         | 1.125 | 1.2   | 1.375 | V    |

Table 26. LVDS I/O DC Characteristics

# 4.7 I/O AC Parameters

This section includes the AC parameters of the following I/O types:

- General Purpose I/O (GPIO)

- Double Data Rate I/O (DDR) for LPDDR2 and DDR3/DDR3L modes

- LVDS I/O

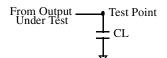

The GPIO and DDR I/O load circuit and output transition time waveforms are shown in Figure 4 and Figure 5.

CL includes package, probe and fixture capacitance

Figure 4. Load Circuit for Output

# 4.8.1 GPIO Output Buffer Impedance

Table 32 shows the GPIO output buffer impedance (OVDD 1.8 V).

| Parameter     | Symbol | Drive Strength (DSE) | Typ Value | Unit |

|---------------|--------|----------------------|-----------|------|

|               |        | 001                  | 260       |      |

|               |        | 010                  | 130       |      |

| Output Driver | Rdrv   | 011                  | 90        |      |

| Impedance     |        | 100                  | 60        | Ω    |

|               |        | 101                  | 50        |      |

|               |        | 110                  | 40        |      |

|               |        | 111                  | 33        |      |

### Table 32. GPIO Output Buffer Average Impedance (OVDD 1.8 V)

Table 33 shows the GPIO output buffer impedance (OVDD 3.3 V).

| Parameter     | Symbol | Drive Strength (DSE) | Typ Value | Unit |

|---------------|--------|----------------------|-----------|------|

|               |        | 001                  | 150       |      |

|               |        | 010                  | 75        |      |

| Output Driver | Rdrv   | 011                  | 50        |      |

| Impedance     |        | 100                  | 37        | Ω    |

|               |        | 101                  | 30        |      |

|               |        | 110                  | 25        |      |

|               |        | 111                  | 20        |      |

# 4.8.2 DDR I/O Output Buffer Impedance

The LPDDR2 interface fully complies with JESD209-2B LPDDR2 JEDEC standard release June, 2009. The DDR3 interface fully complies with JESD79-3D DDR3 JEDEC standard release April, 2008.

Table 34 shows DDR I/O output buffer impedance of i.MX 6Solo/6DualLite processors.

| Table 34. DE | DR I/O Output B | uffer Impedance |

|--------------|-----------------|-----------------|

|              |                 |                 |

|                            |        |                                                      | Тур                                              | ical                                             |      |

|----------------------------|--------|------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|------|

| Parameter                  | Symbol | Test Conditions DSE(Drive<br>Strength)               | NVCC_DRAM=1.5 V<br>(DDR3)<br>DDR_SEL=11          | NVCC_DRAM=1.2 V<br>(LPDDR2)<br>DDR_SEL=10        | Unit |

| Output Driver<br>Impedance | Rdrv   | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | Hi-Z<br>240<br>120<br>80<br>60<br>48<br>40<br>34 | Hi-Z<br>240<br>120<br>80<br>60<br>48<br>40<br>34 | Ω    |

#### Note:

1. Output driver impedance is controlled across PVTs using ZQ calibration procedure.

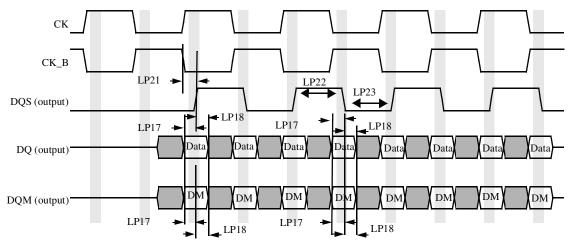

Figure 26 shows the write timing parameters. The timing parameters for this diagram appear in Table 45.

Figure 26. LPDDR2 Write Cycle

| Table 45. | LPDDR2 | Write C | ycle |

|-----------|--------|---------|------|

|-----------|--------|---------|------|

| ID   | Parameter                                                 | Symbol        | CK = 40 | Unit  |     |

|------|-----------------------------------------------------------|---------------|---------|-------|-----|

|      | Farameter                                                 |               | Min     | Max   | Om  |

| LP17 | DQ and DQM setup time to DQS (differential strobe)        | tDS           | 375     | _     | ps  |

| LP18 | DQ and DQM hold time to DQS (differential strobe)         | tdн           | 375     | —     | ps  |

| LP21 | DQS latching rising transitions to associated clock edges | tDQSS         | -0.25   | +0.25 | tCK |

| LP22 | DQS high level width                                      | <b>t</b> DQSH | 0.4     | -     | tCK |

| LP23 | DQS low level width                                       | tDQSL         | 0.4     | -     | tCK |

<sup>1</sup> To receive the reported setup and hold values, write calibration should be performed in order to locate the DQS in the middle of DQ window.

<sup>2</sup> All measurements are in reference to Vref level.

$^3\,$  Measurements were done using balanced load and 25  $\Omega$  resistor from outputs to VDD\_REF.

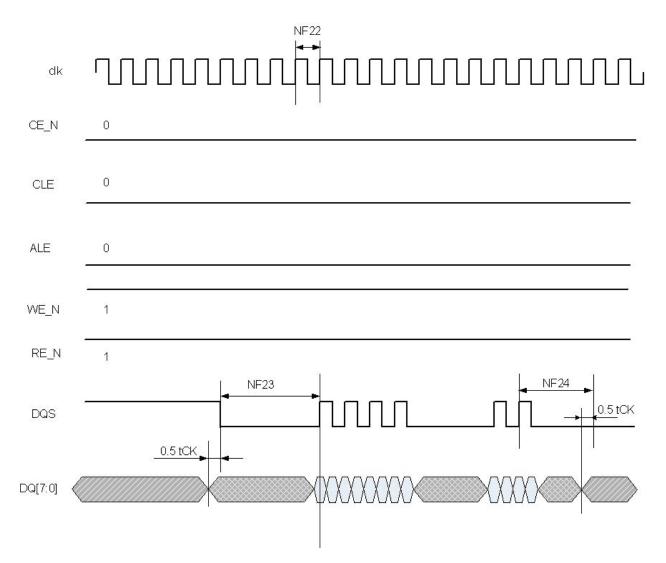

## 4.10.3.2 Read and Write Timing

Figure 36. Samsung Toggle Mode Data Write Timing

# 4.11.3 Enhanced Serial Audio Interface (ESAI) Timing Parameters

The ESAI consists of independent transmitter and receiver sections, each section with its own clock generator. Table 52 shows the interface timing values. The number field in the table refers to timing signals found in Figure 40 and Figure 41.

| No. | Characteristics <sup>1,2</sup>                                        | Symbol | Expression <sup>2</sup>                                         | Min          | Max          | Condition <sup>3</sup> | Unit |

|-----|-----------------------------------------------------------------------|--------|-----------------------------------------------------------------|--------------|--------------|------------------------|------|

|     |                                                                       |        |                                                                 |              |              |                        |      |

| 62  | Clock cycle <sup>4</sup>                                              | tssicc | $\begin{array}{c} 4 \times T_{c} \\ 4 \times T_{c} \end{array}$ | 30.0<br>30.0 | _            | i ck<br>i ck           | ns   |

| 63  | Clock high period:<br>• For internal clock<br>• For external clock    |        | $2 \times T_{c} - 9.0$ $2 \times T_{c}$                         | 6<br>15      | _            | _                      | ns   |

| 64  | Clock low period:<br>• For internal clock<br>• For external clock     | _      | $2 \times T_{c} - 9.0$ $2 \times T_{c}$                         | 6<br>15      | _            |                        | ns   |

| 65  | SCKR rising edge to FSR out (bl) high                                 |        | _                                                               |              | 17.0<br>7.0  | x ck<br>i ck a         | ns   |

| 66  | SCKR rising edge to FSR out (bl) low                                  |        |                                                                 |              | 17.0<br>7.0  | x ck<br>i ck a         | ns   |

| 67  | SCKR rising edge to FSR out (wr) high <sup>5</sup>                    | _      |                                                                 |              | 19.0<br>9.0  | x ck<br>i ck a         | ns   |

| 68  | SCKR rising edge to FSR out (wr) low <sup>5</sup>                     |        | —                                                               |              | 19.0<br>9.0  | x ck<br>i ck a         | ns   |

| 69  | SCKR rising edge to FSR out (wl) high                                 |        |                                                                 |              | 16.0<br>6.0  | x ck<br>i ck a         | ns   |

| 70  | SCKR rising edge to FSR out (wl) low                                  |        |                                                                 |              | 17.0<br>7.0  | x ck<br>i ck a         | ns   |

| 71  | Data in setup time before SCKR (SCK in synchronous mode) falling edge |        | —                                                               | 12.0<br>19.0 | —            | x ck<br>i ck           | ns   |

| 72  | Data in hold time after SCKR falling edge                             |        |                                                                 | 3.5<br>9.0   |              | x ck<br>i ck           | ns   |

| 73  | FSR input (bl, wr) high before SCKR falling edge <sup>5</sup>         | -      | -                                                               | 2.0<br>12.0  | _            | x ck<br>i ck a         | ns   |

| 74  | FSR input (wl) high before SCKR falling edge                          |        |                                                                 | 2.0<br>12.0  | _            | x ck<br>i ck a         | ns   |

| 75  | FSR input hold time after SCKR falling edge                           |        |                                                                 | 2.5<br>8.5   | _            | x ck<br>i ck a         | ns   |

| 78  | SCKT rising edge to FST out (bl) high                                 |        | —                                                               |              | 18.0<br>8.0  | x ck<br>i ck           | ns   |

| 79  | SCKT rising edge to FST out (bl) low                                  |        |                                                                 |              | 20.0<br>10.0 | x ck<br>i ck           | ns   |

| 80  | SCKT rising edge to FST out (wr) high <sup>5</sup>                    | _      |                                                                 |              | 20.0<br>10.0 | x ck<br>i ck           | ns   |

### Table 52. Enhanced Serial Audio Interface (ESAI) Timing

### NOTE

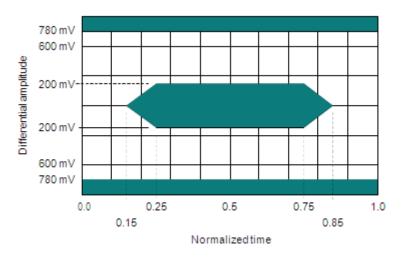

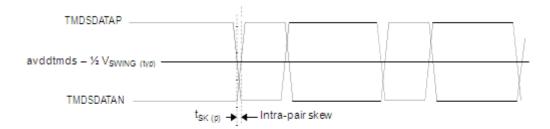

All dynamic parameters related to the TMDS line drivers' performance imply the use of assembly guidelines.

Figure 56. TMDS Clock Signal Definitions

Figure 57. Eye Diagram Mask Definition for HDMI Driver Signal Specification at TP1

Figure 58. Intra-Pair Skew Definition

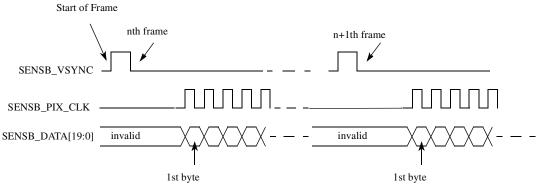

### 4.11.10.2.3 Non-Gated Clock Mode

The timing is the same as the gated-clock mode (described in Section 4.11.10.2.2, "Gated Clock Mode,") except for the SENSB\_HSYNC signal, which is not used (see Figure 63). All incoming pixel clocks are valid and cause data to be latched into the input FIFO. The SENSB\_PIX\_CLK signal is inactive (states low) until valid data is going to be transmitted over the bus.

Figure 63. Non-Gated Clock Mode Timing Diagram

The timing described in Figure 63 is that of a typical sensor. Some other sensors may have a slightly different timing. The CSI can be programmed to support rising/falling-edge triggered SENSB\_VSYNC; active-high/low SENSB\_HSYNC; and rising/falling-edge triggered SENSB\_PIX\_CLK.

# NOTE

Table 67 provides information for both the Disp0 and Disp1 ports. However, Disp1 port has reduced pinout depending on IOMUXC configuration and therefore may not support all the above configurations. See the IOMUXC table for details.

# 4.11.10.5 IPU Display Interface Timing

The IPU Display Interface supports two kinds of display accesses: synchronous and asynchronous. There are two groups of external interface pins to provide synchronous and asynchronous controls accordantly.

## 4.11.10.5.1 Synchronous Controls

The synchronous control changes its value as a function of a system or of an external clock. This control has a permanent period and a permanent wave form.

There are special physical outputs to provide synchronous controls:

- The ipp\_disp\_clk is a dedicated base synchronous signal that is used to generate a base display (component, pixel) clock for a display.

- The ipp\_pin\_1- ipp\_pin\_7 are general purpose synchronous pins, that can be used to provide HSYNC, VSYNC, DRDY or any else independent signal to a display.

The IPU has a system of internal binding counters for internal events (such as, HSYNC/VSYCN) calculation. The internal event (local start point) is synchronized with internal DI\_CLK. A suitable control starts from the local start point with predefined UP and DOWN values to calculate control's changing points with half DI\_CLK resolution. A full description of the counters system can be found in the IPU chapter of the *i.MX* 6Solo/6DualLite Reference Manual (IMX6SDLRM).

## 4.11.10.5.2 Asynchronous Controls

The asynchronous control is a data-oriented signal that changes its value with an output data according to additional internal flags coming with the data.

There are special physical outputs to provide asynchronous controls, as follows:

- The ipp\_d0\_cs and ipp\_d1\_cs pins are dedicated to provide chip select signals to two displays.

- The ipp\_pin\_11- ipp\_pin\_17 are general purpose asynchronous pins, that can be used to provide WR. RD, RS or any other data oriented signal to display.

## NOTE

The IPU has independent signal generators for asynchronous signals toggling. When a DI decides to put a new asynchronous data in the bus, a new internal start (local start point) is generated. The signals generators calculate predefined UP and DOWN values to change pins states with half DI\_CLK resolution.

### Table 68 shows timing characteristics of signals presented in Figure 66 and Figure 67.

| ID   | Parameter                      | Symbol | Value                                 | Description                                                                                                                                                                                                                                                                                                      | Unit |

|------|--------------------------------|--------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| IP5  | Display interface clock period | Tdicp  | (1)                                   | Display interface clock. IPP_DISP_CLK                                                                                                                                                                                                                                                                            | ns   |

| IP6  | Display pixel clock period     | Tdpcp  | DISP_CLK_PER_PIXEL<br>X Tdicp         | Time of translation of one pixel to display,<br>DISP_CLK_PER_PIXEL—number of pixel<br>components in one pixel (1.n). The<br>DISP_CLK_PER_PIXEL is virtual<br>parameter to define Display pixel clock<br>period.<br>The DISP_CLK_PER_PIXEL is received by<br>DC/DI one access division to <b>n</b><br>components. | ns   |

| IP7  | Screen width time              | Tsw    | (SCREEN_WIDTH)<br>× Tdicp             | SCREEN_WIDTH—screen width in,<br>interface clocks. horizontal blanking<br>included.<br>The SCREEN_WIDTH should be built by<br>suitable DI's counter <sup>2</sup> .                                                                                                                                               | ns   |

| IP8  | HSYNC width time               | Thsw   | (HSYNC_WIDTH)                         | HSYNC_WIDTH—Hsync width in DI_CLK<br>with 0.5 DI_CLK resolution. Defined by DI's<br>counter.                                                                                                                                                                                                                     | ns   |

| IP9  | Horizontal blank interval 1    | Thbi1  | BGXP × Tdicp                          | BGXP—width of a horizontal blanking<br>before a first active data in a line (in<br>interface clocks). The BGXP should be built<br>by suitable DI's counter.                                                                                                                                                      | ns   |

| IP10 | Horizontal blank interval 2    | Thbi2  | (SCREEN_WIDTH -<br>BGXP - FW) × Tdicp | Width a horizontal blanking after a last<br>active data in a line (in interface clocks)<br>FW—with of active line in interface clocks.<br>The FW should be built by suitable DI's<br>counter.                                                                                                                    | ns   |

| IP12 | Screen height                  | Tsh    | (SCREEN_HEIGHT)<br>X Tsw              | SCREEN_HEIGHT— screen height in lines<br>with blanking.<br>The SCREEN_HEIGHT is a distance<br>between 2 VSYNCs.<br>The SCREEN_HEIGHT should be built by<br>suitable DI's counter.                                                                                                                                | ns   |

| IP13 | VSYNC width                    | Tvsw   | VSYNC_WIDTH                           | VSYNC_WIDTH—Vsync width in DI_CLK<br>with 0.5 DI_CLK resolution. Defined by DI's<br>counter                                                                                                                                                                                                                      | ns   |

| IP14 | Vertical blank interval 1      | Tvbi1  | BGYP × Tsw                            | BGYP—width of first Vertical<br>blanking interval in line. The BGYP should<br>be built by suitable DI's counter.                                                                                                                                                                                                 | ns   |

| IP15 | Vertical blank interval 2      | Tvbi2  | (SCREEN_HEIGHT -<br>BGYP - FH) × Tsw  | Width of second Vertical<br>blanking interval in line. The FH should be<br>built by suitable DI's counter.                                                                                                                                                                                                       | ns   |

### Table 68. Synchronous Display Interface Timing Characteristics (Pixel Level)

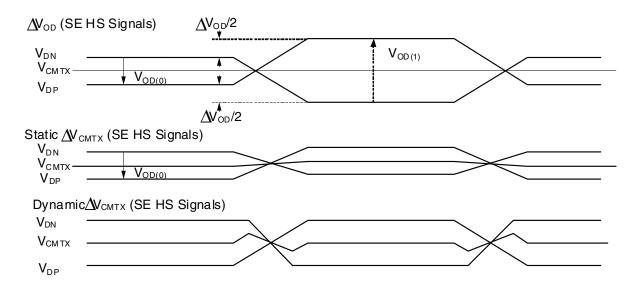

### 4.11.12.4 Possible $\triangle VCMTX$ and $\triangle VOD$ Distortions of the Single-ended HS Signals

Figure 71. Possible  $\triangle$ VCMTX and  $\triangle$ VOD Distortions of the Single-ended HS Signals

## 4.11.12.5 MIPI D-PHY Switching Characteristics

| Symbol                 | Parameters                                   | Test Conditions                                          | MIN   | ТҮР   | MAX   | Unit              |

|------------------------|----------------------------------------------|----------------------------------------------------------|-------|-------|-------|-------------------|

|                        | HS Line D                                    | rivers AC Specifications                                 |       | 1     | I     |                   |

|                        | Maximum serial data rate (forward direction) | On DATAP/N outputs.<br>80 $\Omega$ <= RL <= 125 $\Omega$ | 80    | _     | 1000  | Mbps              |

| F <sub>DDRCLK</sub>    | DDR CLK frequency                            | On DATAP/N outputs.                                      | 40    | —     | 500   | MHz               |

| P <sub>DDRCLK</sub>    | DDR CLK period                               | 80 Ω<= RL< = 125 Ω                                       | 2     | —     | 25    | ns                |

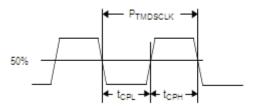

| t <sub>CDC</sub>       | DDR CLK duty cycle                           | $t_{CDC} = t_{CPH} / P_{DDRCLK}$                         | —     | 50    | —     | %                 |

| t <sub>CPH</sub>       | DDR CLK high time                            |                                                          | —     | 1     | —     | UI                |

| t <sub>CPL</sub>       | DDR CLK low time                             |                                                          | —     | 1     | —     | UI                |

| _                      | DDR CLK / DATA Jitter                        |                                                          | —     | 75    | —     | ps pk–pk          |

| t <sub>SKEW[PN]</sub>  | Intra-Pair (Pulse) skew                      |                                                          |       | 0.075 |       | UI                |

| t <sub>SKEW[TX]</sub>  | Data to Clock Skew                           |                                                          | 0.350 |       | 0.650 | UI                |

| t <sub>SETUP[RX]</sub> | Data to Clock Receiver Setup time            |                                                          | 0.15  |       |       | UI                |

| t <sub>HOLD[RX]</sub>  | Clock to Data Receiver Hold time             |                                                          | 0.15  |       |       | UI                |

| t <sub>r</sub>         | Differential output signal rise time         | 20% to 80%, RL = 50 $\Omega$                             | 150   |       | 0.3UI | ps                |

| t <sub>f</sub>         | Differential output signal fall time         | 20% to 80%, RL = 50 $\Omega$                             | 150   |       | 0.3UI | ps                |

| $\Delta V_{CMTX(HF)}$  | Common level variation above 450 MHz         | 80 Ω<= RL< = 125 Ω                                       |       |       | 15    | mV <sub>rms</sub> |

### Table 72. Electrical and Timing Information

# 4.11.14 PCIe PHY Parameters

The PCIe interface complies with PCIe specification Gen2 x1 lane and supports the PCI Express 1.1/2.0 standard.

## 4.11.14.1 PCIE\_REXT Reference Resistor Connection

The impedance calibration process requires connection of reference resistor 200  $\Omega$ . 1% precision resistor on PCIE\_REXT pads to ground. It is used for termination impedance calibration.

# 4.11.15 Pulse Width Modulator (PWM) Timing Parameters

This section describes the electrical information of the PWM. The PWM can be programmed to select one of three clock signals as its source frequency. The selected clock signal is passed through a prescaler before being input to the counter. The output is available at the pulse-width modulator output (PWMO) external pin.

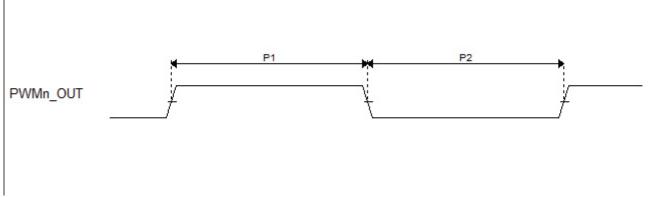

Figure 84 depicts the timing of the PWM, and Table 74 lists the PWM timing parameters.

| Figure | 84. | PWM | Timing |

|--------|-----|-----|--------|

|--------|-----|-----|--------|

Table 74. PWM Output Timing Parameters

| ID | Parameter                   | Min | Мах     | Unit |

|----|-----------------------------|-----|---------|------|

|    | PWM Module Clock Frequency  | 0   | ipg_clk | MHz  |

| P1 | PWM output pulse width high | 15  |         | ns   |

| P2 | PWM output pulse width low  | 15  |         | ns   |

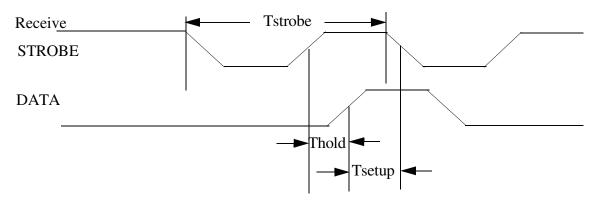

# 4.11.20.2 Receive Timing

Figure 100. USB HSIC Receive Waveform

| Table 88. U | JSB HSIC Receiv | ve Parameters <sup>1</sup> |

|-------------|-----------------|----------------------------|

|-------------|-----------------|----------------------------|

| Name    | Parameter                       | Min   | Max   | Unit | Comment                        |

|---------|---------------------------------|-------|-------|------|--------------------------------|

| Tstrobe | strobe period                   | 4.166 | 4.167 | ns   |                                |

| Thold   | data hold time                  | 300   |       | ps   | Measured at 50% point          |

| Tsetup  | data setup time                 | 365   |       | ps   | Measured at 50% point          |

| Tslew   | strobe/data rising/falling time | 0.7   | 2     | V/ns | Averaged from 30% – 70% points |

<sup>1</sup> The timings in the table are guaranteed when:

-AC I/O voltage is between 0.9x to 1x of the I/O supply

-DDR\_SEL configuration bits of the I/O are set to (10)b

# 4.11.21 USB PHY Parameters

This section describes the USB-OTG PHY and the USB Host port PHY parameters.

The USB PHY meets the electrical compliance requirements defined in the Universal Serial Bus Revision 2.0 OTG, USB Host with the amendments below (On-The-Go and Embedded Host Supplement to the USB Revision 2.0 Specification is not applicable to Host port).

- USB ENGINEERING CHANGE NOTICE

- Title: 5V Short Circuit Withstand Requirement Change

- Applies to: Universal Serial Bus Specification, Revision 2.0

- Errata for USB Revision 2.0 April 27, 2000 as of 12/7/2000

- USB ENGINEERING CHANGE NOTICE

- Title: Pull-up/Pull-down resistors

- Applies to: Universal Serial Bus Specification, Revision 2.0

- USB ENGINEERING CHANGE NOTICE

- Title: Suspend Current Limit Changes

- Applies to: Universal Serial Bus Specification, Revision 2.0

### Package Information and Contact Assignments

|                |      |             |              |                                    | Out of Reset Con   | dition <sup>2</sup>  |       |

|----------------|------|-------------|--------------|------------------------------------|--------------------|----------------------|-------|

| Ball Name      | Ball | Power Group | Ball<br>Type | Default<br>Mode<br>(Reset<br>Mode) | Default Function   | Input/<br>Outpu<br>t | Value |

| DRAM_DQM0      | AC3  | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_DQM[0]   | Output               | Low   |

| DRAM_DQM1      | AC6  | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_DQM[1]   | Output               | Low   |

| DRAM_DQM2      | AB8  | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_DQM[2]   | Output               | Low   |

| DRAM_DQM3      | AE10 | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_DQM[3]   | Output               | Low   |

| DRAM_DQM4      | AB18 | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_DQM[4]   | Output               | Low   |

| DRAM_DQM5      | AC20 | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_DQM[5]   | Output               | Low   |

| DRAM_DQM6      | AD24 | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_DQM[6]   | Output               | Low   |

| DRAM_DQM7      | Y21  | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_DQM[7]   | Output               | Low   |

| DRAM_RAS       | AB15 | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_RAS      | Output               | Low   |

| DRAM_RESET     | Y6   | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_RESET    | Output               | Low   |

| DRAM_SDBA0     | AC15 | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_SDBA[0]  | Output               | Low   |

| DRAM_SDBA1     | Y15  | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_SDBA[1]  | Output               | Low   |

| DRAM_SDBA2     | AB12 | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_SDBA[2]  | Output               | Low   |

| DRAM_SDCKE0    | Y11  | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_SDCKE[0] | Output               | Low   |

| DRAM_SDCKE1    | AA11 | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_SDCKE[1] | Output               | Low   |

| DRAM_SDCLK_0   | AD15 | NVCC_DRAM   | DDRCLK       | ALT0                               | mmdc.DRAM_SDCLK0   | Output               | Low   |

| DRAM_SDCLK_0_B | AE15 | NVCC_DRAM   |              |                                    | DRAM_SDCLK_0_B     | -                    | -     |

| DRAM_SDCLK_1   | AD14 | NVCC_DRAM   | DDRCLK       | ALT0                               | mmdc.DRAM_SDCLK1   | Output               | Low   |

| DRAM_SDCLK_1_B | AE14 | NVCC_DRAM   |              |                                    | DRAM_SDCLK_1_B     | -                    | -     |

| DRAM_SDODT0    | AC16 | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_ODT[0]   | Output               | Low   |

| DRAM_SDODT1    | AB17 | NVCC_DRAM   | DDR          | ALT0                               | mmdc.DRAM_ODT[1]   | Output               | Low   |

| DRAM_SDQS0     | AE3  | NVCC_DRAM   | DDRCLK       | ALT0                               | mmdc.DRAM_SDQS[0]  | Input                | Hi-Z  |

| DRAM_SDQS0_B   | AD3  | NVCC_DRAM   |              |                                    | DRAM_SDQS0_B       | -                    | -     |

| DRAM_SDQS1     | AD6  | NVCC_DRAM   | DDRCLK       | ALT0                               | mmdc.DRAM_SDQS[1]  | Input                | Hi-Z  |

| DRAM_SDQS1_B   | AE6  | NVCC_DRAM   |              |                                    | DRAM_SDQS1_B       | -                    | -     |

| DRAM_SDQS2     | AD8  | NVCC_DRAM   | DDRCLK       | ALT0                               | mmdc.DRAM_SDQS[2]  | Input                | Hi-Z  |

| DRAM_SDQS2_B   | AE8  | NVCC_DRAM   |              |                                    | DRAM_SDQS2_B       | -                    | -     |

| DRAM_SDQS3     | AC10 | NVCC_DRAM   | DDRCLK       | ALT0                               | mmdc.DRAM_SDQS[3]  | Input                | Hi-Z  |

| DRAM_SDQS3_B   | AB10 | NVCC_DRAM   |              |                                    | DRAM_SDQS3_B       | -                    | -     |

| DRAM_SDQS4     | AD18 | NVCC_DRAM   | DDRCLK       | ALT0                               | mmdc.DRAM_SDQS[4]  | Input                | Hi-Z  |

Table 92. 21 x 21 mm Functional Contact Assignments<sup>1</sup> (continued)

### Package Information and Contact Assignments

|                  | ٩.     | z            | Σ          | L          | ×           | 7           | т           |

|------------------|--------|--------------|------------|------------|-------------|-------------|-------------|

| CSI0_PIXCLK C    | 0      | CSI0_DAT4    | CSI0_DAT10 | CSI0_DAT13 | HDMI_HPD    | HDMI_REF    | DSI_D1P     |

| CSI0_DAT5 CSI    | CSI    | CSI0_VSYNC   | CSI0_DAT12 | GND        | HDMI_DDCCEC | GND         | DSI_D1M     |

| CSI0_DATA_EN CS  |        | CSI0_DAT7    | CSI0_DAT11 | CSI0_DAT17 | HDMI_D2M    | HDMI_D1M    | DSI_CLK0M   |

| CSI0_MCLK CSI    | CSI    | CSI0_DAT6    | CSI0_DAT14 | CSI0_DAT16 | HDMI_D2P    | HDMI_D1P    | DSI_CLK0P   |

| GPIO_19 CSI0     | CSIC   | CSI0_DAT9    | CSI0_DAT15 | GND        | HDMI_D0M    | HDMI_CLKM   | JTAG_TCK    |

| GPIO_18 CSI0     | CSIC   | CSI0_DAT8    | CSI0_DAT18 | CSI0_DAT19 | HDMI_D0P    | HDMI_CLKP   | JTAG_MOD    |

| NVCC_GPIO NVC    | NVO    | NVCC_CSI     | HDMI_VPH   | HDMI_VP    | NVCC_MIPI   | NVCC_JTAG   | PCIE_VP     |

| GND G            | G      | GND          | GND        | GND        | GND         | GND         | GND         |

| VDDARM_IN VDDA   | VDDA   | VDDARM_IN    | VDDARM_IN  | VDDARM_IN  | VDDARM_IN   | VDDHIGH_IN  | VDDHIGH_IN  |

| GND G            | G      | GND          | GND        | GND        | GND         | VDDHIGH_CAP | VDDHIGH_CAP |

| VDDARM_CAP VDDAF | VDDAF  | VDDARM_CAP   | VDDARM_CAP | VDDARM_CAP | VDDARM_CAP  | VDDARM_CAP  | VDDARM_CAP  |

| GND              | Z      | NC           | GND        | GND        | GND         | GND         | GND         |

| VDDARM_CAP VDDAR | VDDAR  | VDDARM_CAP   | VDDARM_CAP | VDDARM_CAP | VDDARM_CAP  | VDDARM_CAP  | VDDARM_CAP  |

|                  | VDDA   | VDDARM_IN    | VDDARM_IN  | VDDARM_IN  | VDDARM_IN   | VDDARM_IN   | VDDARM_IN   |

| GND              | G      | GND          | GND        | GND        | GND         | GND         | GND         |

|                  | VDDS(  | DC_IN        | VDDSOC_IN  | VDDSOC_IN  | VDDSOC_IN   |             | VDDSOC_IN   |

| VDDPU_CAP VDDP   | VDDPI  | VDDPU_CAP    | VDDPU_CAP  | VDDPU_CAP  | VDDPU_CAP   | VDDPU_CAP   | VDDPU_CAP   |

| GND              | G      | GND          | GND        | GND        | GND         | GND         | GND         |

| NVCC_LCD DI0_DI  | DIO_DI | DI0_DISP_CLK | NVCC_EIM   | NVCC_EIM   | NVCC_EIM    | EIM_D29     | EIM_A25     |

| DISP0_DAT4 DI0   | DIO    | DI0_PIN3     | EIM_DA11   | EIM_DA0    | EIM_RW      | EIM_D30     | EIM_D21     |

| DISP0_DAT3 DI0_  | DIO    | DI0_PIN15    | EIM_DA9    | EIM_DA2    | EIM_EB0     | EIM_A23     | EIM_D31     |

| DISP0_DAT1 EIM   | EIM    | EIM_BCLK     | EIM_DA10   | EIM_DA4    | EIM_LBA     | EIM_A18     | EIM_A20     |

| DISP0_DAT2 EIM   | EIM    | EIM_DA14     | EIM_DA13   | EIM_DA5    | EIM_EB1     | EIM_CS1     | EIM_A21     |

| DISP0_DAT0 EIM   | EIM    | EIM_DA15     | EIM_DA12   | EIM_DA8    | EIM_DA3     | EIM_OE      | EIM_CS0     |

| DI0_PIN4 DI0     | DIG    | DI0_PIN2     | EIM_WAIT   | EIM_DA7    | EIM_DA6     | EIM_DA1     | EIM_A16     |

| ٩                |        | z            | Σ          | Ч          | ×           | 7           | т           |

|                  |        |              |            |            |             |             |             |

### Table 93. 21 x 21 mm, 0.8 mm Pitch Ball Map (continued)

### Package Information and Contact Assignments

| ۲           | 8           | >            | 5           | F           | æ           | ٩            | z            |

|-------------|-------------|--------------|-------------|-------------|-------------|--------------|--------------|

| LVDS1_TX0_N | LVDS0_TX3_P | LVDS0_TX2_P  | LVDS0_TX0_P | GPI0_2      | GPI0_17     | CSI0_PIXCLK  | CSI0_DAT4    |

| LVDS1_TX0_P | LVDS0_TX3_N | LVDS0_TX2_N  | LVDS0_TX0_N | GPIO_9      | GPIO_16     | CSI0_DAT5    | CSI0_VSYNC   |

| LVDS1_CLK_N | GND         | LVDS0_CLK_P  | LVDS0_TX1_P | GPIO_6      | GPIO_7      | CSI0_DATA_EN | CSI0_DAT7    |

| LVDS1_CLK_P | KEY_ROW2    | LVDS0_CLK_N  | LVDS0_TX1_N | GPI0_1      | GPIO_5      | CSI0_MCLK    | CSI0_DAT6    |

| GND         | KEY_COL0    | KEY_ROW4     | KEY_COL3    | GPIO_0      | GPIO_8      | GPIO_19      | CSI0_DAT9    |

| DRAM_RESET  | KEY_COL2    | KEY_ROW0     | KEY_ROW1    | KEY_COL4    | GPIO_4      | GPIO_18      | CSI0_DAT8    |

| DRAM_D20    | GND         | NVCC_LVDS2P5 | KEY_COL1    | KEY_ROW3    | GPIO_3      | NVCC_GPIO    | NVCC_CSI     |

| DRAM_D21    | GND         | GND          | GND         | GND         | GND         | GND          | GND          |

| DRAM_D19    | GND         | NVCC_DRAM    | VDDARM_IN   | VDDARM_IN   | VDDARM_IN   | VDDARM_IN    | VDDARM_IN    |

| DRAM_D25    | GND         | NVCC_DRAM    | VDDSOC_CAP  | VDDSOC_CAP  | VDDSOC_CAP  | GND          | GND          |

| DRAM_SDCKE0 | GND         | NVCC_DRAM    | GND         | GND         | VDDARM_CAP  | VDDARM_CAP   | VDDARM_CAP   |

| DRAM_A15    | GND         | NVCC_DRAM    | GND         | GND         | GND         | GND          | NC           |

| DRAM_A7     | GND         | NVCC_DRAM    | VDDSOC_CAP  | VDDSOC_CAP  | VDDARM_CAP  | VDDARM_CAP   | VDDARM_CAP   |

| DRAM_A3     | DRAM_A4     | NVCC_DRAM    | VDDSOC_CAP  | VDDSOC_CAP  | VDDARM_IN   | VDDARM_IN    | VDDARM_IN    |

| DRAM_SDBA1  | GND         | NVCC_DRAM    | GND         | GND         | GND         | GND          | GND          |

| DRAM_CS0    | GND         | NVCC_DRAM    | VDDSOC_IN   | VDDSOC_IN   | VDDSOC_IN   | VDDSOC_IN    | VDDSOC_IN    |

| DRAM_D36    | GND         | NVCC_DRAM    | GND         | GND         | GND         | VDDPU_CAP    | VDDPU_CAP    |

| DRAM_D37    | GND         | NVCC_DRAM    | NVCC_DRAM   | NVCC_DRAM   | NVCC_DRAM   | GND          | GND          |

| DRAM_D40    | GND         | GND          | GND         | GND         | NVCC_ENET   | NVCC_LCD     | DI0_DISP_CLK |

| DRAM_D44    | ENET_TXD1   | ENET_MDC     | ENET_TXD0   | DISP0_DAT21 | DISP0_DAT13 | DISP0_DAT4   | DI0_PIN3     |

| DRAM_DQM7   | ENET_RXD0   | ENET_TX_EN   | ENET_CRS_DV | DISP0_DAT16 | DISP0_DAT10 | DISP0_DAT3   | DI0_PIN15    |

| DRAM_D59    | ENET_RXD1   | ENET_REF_CLK | DISP0_DAT20 | DISP0_DAT15 | DISP0_DAT8  | DISP0_DAT1   | EIM_BCLK     |

| DRAM_D62    | ENET_RX_ER  | ENET_MDIO    | DISP0_DAT19 | DISP0_DAT11 | DISP0_DAT6  | DISP0_DAT2   | EIM_DA14     |

| GND         | DISP0_DAT23 | DISP0_DAT22  | DISP0_DAT17 | DISP0_DAT12 | DISP0_DAT7  | DISP0_DAT0   | EIM_DA15     |

| DRAM_D58    | DRAM_D63    | DISP0_DAT18  | DISP0_DAT14 | DISP0_DAT9  | DISP0_DAT5  | DI0_PIN4     | DI0_PIN2     |

| ٨           | Μ           | >            | D           | F           | æ           | ٩            | z            |

### Table 94. 21 x 21 mm, 0.8 mm Pitch Ball Map (continued)