Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                            |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Not For New Designs                                                                                                 |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 2 Core, 32-Bit                                                                                                      |

| Speed                              | 1.0GHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON™ SIMD                                                                                              |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | -                                                                                                                   |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | 0°C ~ 95°C (TJ)                                                                                                     |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-LFBGA                                                                                                           |

| Supplier Device Package            | 624-MAPBGA (21x21)                                                                                                  |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6u5dvm10abr                                            |

# 4.1.7 USB PHY Current Consumption

### 4.1.7.1 Power Down Mode

In power down mode, everything is powered down, including the VBUS valid detectors in typical condition. Table 14 shows the USB interface current consumption in power down mode..

Table 14. USB PHY Current Consumption in Power Down Mode

|         | VDDUSB_CAP (3.0 V) | VDDHIGH_CAP (2.5 V) | NVCC_PLL_OUT (1.1 V) |

|---------|--------------------|---------------------|----------------------|

| Current | 5.1 μΑ             | 1.7 μΑ              | <0.5 μΑ              |

### NOTE

The currents on the VDDHIGH\_CAP and VDDUSB\_CAP were identified to be the voltage divider circuits in the USB-specific level shifters.

# 4.1.8 PCle 2.0 Power Consumption

Table 15 provides PCIe PHY currents under certain Tx operating modes.

**Table 15. PCIe PHY Current Drain**

| Mode                        | Test Conditions | Supply            | Max Current | Unit |

|-----------------------------|-----------------|-------------------|-------------|------|

| PO: Normal Operation        | 5G Operations   | PCIE_VP (1.1 V)   | 40          | mA   |

|                             |                 | PCIE_VPTX (1.1 V) | 20          |      |

|                             |                 | PCIE_VPH (2.5 V)  | 21          |      |

|                             | 2.5G Operations | PCIE_VP (1.1 V)   | 27          |      |

|                             |                 | PCIE_VPTX (1.1 V) | 20          |      |

|                             |                 | PCIE_VPH (2.5 V)  | 20          |      |

| POs: Low Recovery Time      | 5G Operations   | PCIE_VP (1.1 V)   | 30          | mA   |

| Latency, Power Saving State |                 | PCIE_VPTX (1.1 V) | 2.4         |      |

|                             |                 | PCIE_VPH (2.5 V)  | 18          |      |

|                             | 2.5G Operations | PCIE_VP (1.1 V)   | 20          |      |

|                             |                 | PCIE_VPTX (1.1 V) | 2.4         |      |

|                             |                 | PCIE_VPH (2.5 V)  | 18          |      |

| P1: Longer Reocvery Time    |                 | PCIE_VP (1.1 V)   | 12          | mA   |

| Latency, Lower Power State  |                 | PCIE_VPTX (1.1 V) | 2.4         |      |

|                             |                 | PCIE_VPH (2.5 V)  | 12          |      |

| Power Down                  |                 | PCIE_VP (1.1 V)   | 1.3         | mA   |

|                             |                 | PCIE_VPTX (1.1 V) | 0.18        |      |

|                             |                 | PCIE_VPH (2.5 V)  | 0.36        |      |

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 1

- VDDARM\_IN supply must be turned ON together with VDDSOC\_IN supply or not delayed more than 1 ms

- VDDARM\_CAP must not exceed VDDSOC\_CAP by more than 50 mV.

#### NOTE

The POR\_B input (if used) must be immediately asserted at power-up and remain asserted until after the last power rail reaches its working voltage. In the absence of an external reset feeding the POR\_B input, the internal POR module takes control. See the *i.MX 6Solo/6DualLite Reference Manual* for further details and to ensure that all necessary requirements are being met.

#### NOTE

Need to ensure that there is no back voltage (leakage) from any supply on the board towards the 3.3 V supply (for example, from the external components that use both the 1.8 V and 3.3 V supplies).

#### NOTE

USB\_OTG\_VBUS and USB\_H1\_VBUS are not part of the power supply sequence and may be powered at any time.

### 4.2.2 Power-Down Sequence

No special restrictions for i.MX 6Solo/6DualLite IC.

# 4.2.3 Power Supplies Usage

All I/O pins should not be externally driven while the I/O power supply for the pin (NVCC\_xxx) is OFF. This can cause internal latch-up and malfunctions due to reverse current flows. For information about I/O power supply of each pin, see "Power Rail" columns in pin list tables of Section 6, "Package Information and Contact Assignments."

# 4.3 Integrated LDO Voltage Regulator Parameters

Various internal supplies can be powered ON from internal LDO voltage regulators. All the supply pins named \*\_CAP must be connected to external capacitors. The onboard LDOs are intended for internal use only and should not be used to power any external circuitry. See the *i.MX 6Solo/6DualLite Reference Manual (IMX6SDLRM)* for details on the power tree scheme.

#### NOTE

The \*\_CAP signals should not be powered externally. These signals are intended for internal LDO or LDO bypass operation only.

# 4.3.1 Digital Regulators (LDO\_ARM, LDO\_PU, LDO\_SOC)

There are three digital LDO regulators ("Digital", because of the logic loads that they drive, not because of their construction). The advantages of the regulators are to reduce the input supply variation because of

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 1

Table 23. GPIO DC Parameters (continued)

| Low-Level input voltage <sup>1,2</sup> | VIL          |                            | 0            | 0.3*OVD<br>D | V  |

|----------------------------------------|--------------|----------------------------|--------------|--------------|----|

| Input Hysteresis(OVDD= 1.8V)           | VHYS_LowVDD  | OVDD=1.8V                  | 250          |              | mV |

| Input Hysteresis(OVDD=3.3V             | VHYS_HighVDD | OVDD=3.3V                  | 250          |              | mV |

| Schmitt trigger VT+ <sup>2,3</sup>     | VTH+         |                            | 0.5*OVD<br>D |              | mV |

| Schmitt trigger VT- <sup>2,3</sup>     | VTH-         |                            |              | 0.5*OVD<br>D | mV |

| Pull-up resistor (22_kΩ PU)            | RPU_22K      | Vin=0V                     |              | 212          | uA |

| Pull-up resistor (22_kΩ PU)            | RPU_22K      | Vin=OVDD                   |              | 1            | uA |

| Pull-up resistor (47_kΩ PU)            | RPU_47K      | Vin=0V                     |              | 100          | uA |

| Pull-up resistor (47_kΩ PU)            | RPU_47K      | Vin=oOVDD                  |              | 1            | uA |

| Pull-up resistor (100_kΩ PU)           | RPU_100K     | Vin=0V                     |              | 48           | uA |

| Pull-up resistor (100_kΩ PU)           | RPU_100K     | Vin=OVDD                   |              | 1            | uA |

| Pull-down resistor (100_kΩ PD)         | RPD_100K     | Vin=OVDD                   |              | 48           | uA |

| Pull-down resistor (100_kΩ PD)         | RPD_100K     | Vin=0V                     |              | 1            | uA |

| Input current (no PU/PD)               | IIN          | VI = 0, VI = OVDD          | -1           | 1            | uA |

| Keeper Circuit Resistance              | R_Keeper     | VI =.3*OVDD, VI = .7* OVDD | 105          | 175          | kΩ |

Overshoot and undershoot conditions (transitions above OVDD and below GND) on switching pads must be held below 0.6 V, and the duration of the overshoot/undershoot must not exceed 10% of the system clock cycle. Overshoot/undershoot must be controlled through printed circuit board layout, transmission line impedance matching, signal line termination, or other methods. Non-compliance to this specification may affect device reliability or cause permanent damage to the device.

### 4.6.2 DDR I/O DC Parameters

The DDR I/O pads support LPDDR2 and DDR3/DDR3L operational modes.

### 4.6.2.1 LPDDR2 Mode I/O DC Parameters

The LPDDR2 interface mode fully complies with JESD209-2B LPDDR2 JEDEC standard release June, 2009.

Table 24. LPDDR2 I/O DC Electrical Parameters<sup>1</sup>

| Parameters                | Symbol | Test Conditions | Min       | Max       | Unit |

|---------------------------|--------|-----------------|-----------|-----------|------|

| High-level output voltage | VOH    | loh= -0.1mA     | 0.9*OVDD  |           | V    |

| Low-level output voltage  | VOL    | Iol= 0.1mA      |           | 0.1*OVDD  | V    |

| Input Reference Voltage   | Vref   |                 | 0.49*OVDD | 0.51*OVDD | V    |

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 1

<sup>&</sup>lt;sup>2</sup> To maintain a valid level, the transition edge of the input must sustain a constant slew rate (monotonic) from the current DC level through to the target DC level, Vil or Vih. Monotonic input transition time is from 0.1 ns to 1 s.

<sup>&</sup>lt;sup>3</sup> Hysteresis of 250 mV is guaranteed over all operating conditions when hysteresis is enabled.

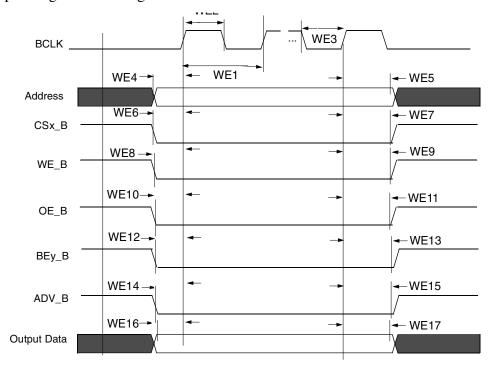

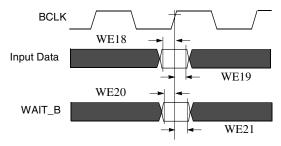

# 4.9.3.3 General EIM Timing-Synchronous Mode

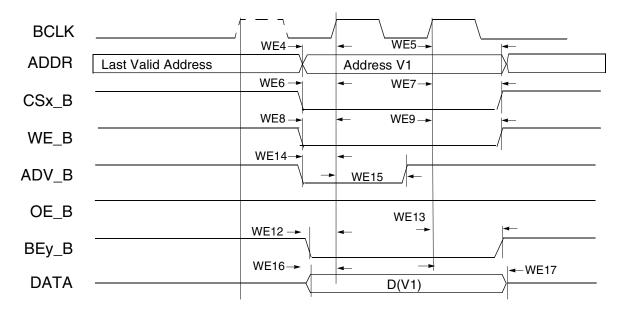

Figure 10, Figure 11, and Table 39 specify the timings related to the EIM module. All EIM output control signals may be asserted and deasserted by an internal clock synchronized to the BCLK rising edge according to corresponding assertion/negation control fields.

Figure 10. EIM Outputs Timing Diagram

Figure 11. EIM Inputs Timing Diagram

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 1

| ID   | Parameter                                  | BCD = 0 |     | BCD = 1 |     | BCD = 2 |     | BCD = 3 |     |

|------|--------------------------------------------|---------|-----|---------|-----|---------|-----|---------|-----|

|      | raiailletei                                | Min     | Max | Min     | Max | Min     | Max | Min     | Max |

| WE19 | Input Data hold<br>time from Clock<br>rise | 2       | _   | 2       | _   | _       | _   | _       | _   |

| WE20 | WAIT_B setup time to Clock rise            | 2       | _   | 4       | _   | _       | _   | _       | _   |

| WE21 | WAIT_B hold time from Clock rise           | 2       | _   | 2       | _   | _       | _   | _       | _   |

t is the maximal EIM logic (axi\_clk) cycle time. The maximum allowed axi\_clk frequency depends on the fixed/non-fixed latency configuration, whereas the maximum allowed BCLK frequency is:

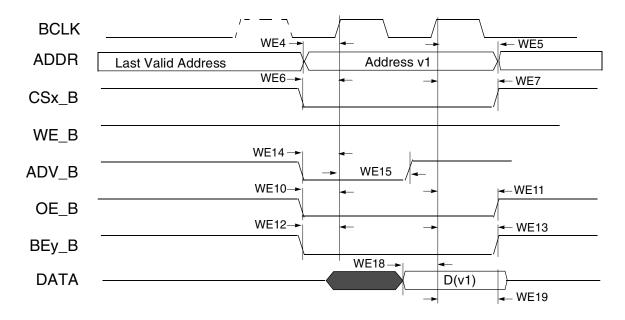

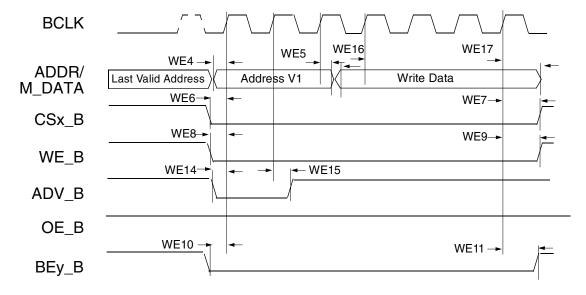

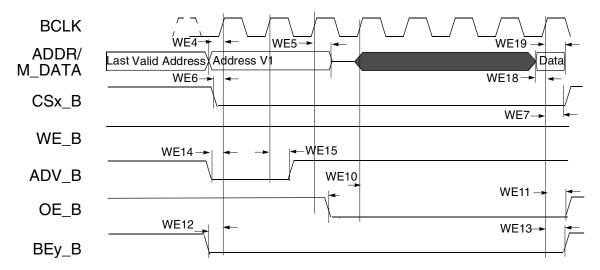

Figure 12 to Figure 15 provide few examples of basic EIM accesses to external memory devices with the timing parameters mentioned previously for specific control parameters settings.

Figure 12. Synchronous Memory Read Access, WSC=1

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 1

<sup>-</sup>Fixed latency for both read and write is 132 MHz.

<sup>-</sup>Variable latency for read only is 132 MHz.

<sup>-</sup>Variable latency for write only is 52 MHz.

In variable latency configuration for write, if BCD = 0 & WBCDD = 1 or BCD = 1, axi\_clk must be 104 MHz.Write BCD = 1 and 104 MHz axi\_clk, will result in a BCLK of 52 MHz. When the clock branch to EIM is decreased to 104 MHz, other buses are impacted which are clocked from this source. See the CCM chapter of the *i.MX* 6Solo/6DualLite Reference Manual (IMX6SDLRM) for a detailed clock tree description.

BCLK parameters are being measured from the 50% point, that is, high is defined as 50% of signal value and low is defined as 50% as signal value.

<sup>&</sup>lt;sup>3</sup> For signal measurements, "High" is defined as 80% of signal value and "Low" is defined as 20% of signal value.

Figure 13. Synchronous Memory, Write Access, WSC=1, WBEA=0 and WADVN=0

Figure 14. Muxed Address/Data (A/D) Mode, Synchronous Write Access, WSC=6,ADVA=0, ADVN=1, and ADH=1

#### NOTE

In 32-bit muxed address/data (A/D) mode the 16 MSBs are driven on the data bus.

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 1

Figure 15. 16-Bit Muxed A/D Mode, Synchronous Read Access, WSC=7, RADVN=1, ADH=1, OEA=0

#### 4.9.3.5 **General EIM Timing-Asynchronous Mode**

Figure 16 through Figure 20, and Table 40 help you determine timing parameters relative to the chip select (CS) state for asynchronous and DTACK EIM accesses with corresponding EIM bit fields and the timing parameters mentioned above.

Asynchronous read & write access length in cycles may vary from what is shown in Figure 16 through Figure 19 as RWSC, OEN & CSN is configured differently. See the i.MX 6Solo/6DualLite Reference Manual (IMX6SDLRM) for the EIM programming model.

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 1 54 Freescale Semiconductor

# 4.9.4 DDR SDRAM Specific Parameters (DDR3/DDR3L and LPDDR2)

### 4.9.4.1 DDR3/DDR3L Parameters

Figure 22 shows the basic timing parameters. The timing parameters for this diagram appear in Table 41.

Figure 22. DDR3 Command and Address Timing Parameters

Table 41. DDR3/DDR3L Timing Parameter Table

| ID   | Dawanastan                            | Combal | CK = 40 | Unit |      |

|------|---------------------------------------|--------|---------|------|------|

|      | Parameter                             | Symbol | Min     | Max  | Unit |

| DDR1 | CK clock high-level width             | tсн    | 0.47    | 0.53 | tcĸ  |

| DDR2 | CK clock low-level width              | tCL    | 0.47    | 0.53 | tcĸ  |

| DDR4 | CS, RAS, CAS, CKE, WE, ODT setup time | tis    | 800     | _    | ps   |

| DDR5 | CS, RAS, CAS, CKE, WE, ODT hold time  | tıн    | 580     | _    | ps   |

| DDR6 | Address output setup time             | tıs    | 800     | _    | ps   |

| DDR7 | Address output hold time              | tıн    | 580     | _    | ps   |

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 1

Table 47. Asynchronous Mode Timing Parameters<sup>1</sup> (continued)

| ID   | Parameter          | Symbol | Timing<br>T = GPMI Clock Cycle |        | Example GPMI Clock | Unit |    |

|------|--------------------|--------|--------------------------------|--------|--------------------|------|----|

|      |                    |        | Min.                           | Max.   | Min.               | Max. |    |

| NF5  | WE pulse width     | tWP    | DS                             | хТ     | 1                  | 0    | ns |

| NF6  | ALE setup time     | tALS   | (AS+1) x T                     | _      | 10                 | _    | ns |

| NF7  | ALE hold time      | tALH   | (DH+1) x T                     |        | 20                 | _    | ns |

| NF8  | Data setup time    | tDS    | DS x T                         | _      | 10                 | _    | ns |

| NF9  | Data hold time     | tDH    | DHxT                           | _      | 10                 | _    | ns |

| NF10 | Write cycle time   | tWC    | (DS+D                          | H) x T | l) x T 20          |      | ns |

| NF11 | WE hold time       | tWH    | DH                             | kT 10  |                    | ns   |    |

| NF12 | Ready to RE low    | tRR    | (AS+1) x T                     | _      | 10                 | _    | ns |

| NF13 | RE pulse width     | tRP    | DS x T                         |        | 10                 | _    | ns |

| NF14 | READ cycle time    | tRC    | (DS+DH) x T                    | _      | 20                 | _    | ns |

| NF15 | RE high hold time  | tREH   | DH                             | DH x T |                    | _    | ns |

| NF16 | Data setup on read | tDSR   | N/A                            |        | 10                 | _    | ns |

| NF17 | Data hold on read  | tDHR   | N/                             | Ά      | 10                 | _    | ns |

GPMI's Async Mode output timing could be controlled by module's internal registers, say

HW\_GPMI\_TIMING0\_ADDRESS\_SETUP, HW\_GPMI\_TIMING0\_DATA\_SETUP, and HW\_GPMI\_TIMING0\_DATA\_HOLD.

This AC timing depends on these registers' settings. In the above table, we use AS/DS/DH to represent each of these settings.

In EDO mode (Figure 31), NF16/NF17 are different from the definition in non-EDO mode (Figure 30). They are called tREA/tRHOH (RE# access time/RE# HIGH to output hold). The typical value for them are 16 ns (max for tREA)/15 ns (min for tRHOH) at 50 MB/s EDO mode. In EDO mode, GPMI will sample IO[7:0] at rising edge of delayed RE provided by an internal DPLL. The delay value can be controlled by GPMI\_CTRL1.RDN\_DELAY (see the GPMI chapter of the i.MX 6Solo/6DualLite reference manual). The typical value of this control register is 0x8 at 50 MT/s EDO mode. But if the board delay is big enough and cannot be ignored, the delay value should be made larger to compensate the board delay.

<sup>2)</sup> AS minimum value could be 0, while DS/DH minimum value is 1.

<sup>3)</sup> T represents for the GPMI clock period.

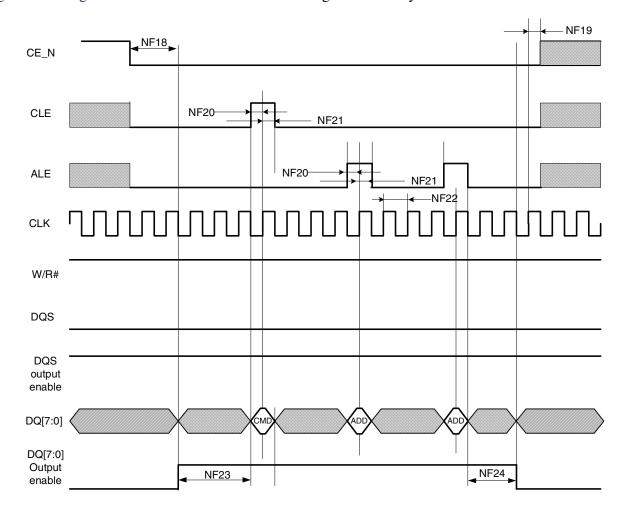

# 4.10.2 Source Synchronous Mode AC Timing (ONFI 2.x Compatible)

Figure 32 to Figure 34 show the write and read timing of Source Synchronous Mode.

Figure 32. Source Synchronous Mode Command and Address Timing Diagram

| ID Parameter |                        | Symbol | Tim<br>T = GPMI C   | Unit |    |

|--------------|------------------------|--------|---------------------|------|----|

|              |                        |        | Min.                | Max. |    |

| NF23         | preamble delay         | tPRE   | (PRE_DELAY+1) x tCK | _    | ns |

| NF24         | postamble delay        | tPOST  | POST_DELAY x tCK    | _    | ns |

| NF25         | CLE and ALE setup time | tCALS  | 0.5 x tCK           | _    | ns |

| NF26         | CLE and ALE hold time  | tCALH  | 0.5 x tCK           | _    | ns |

Table 49. Samsung Toggle Mode Timing Parameters (continued)

For DDR Toggle mode, Figure 35 shows the timing diagram of DQS/DQ read valid window. The typical value of tDQSQ is 1.4 ns(max) and 1.4 ns (max) for tQHS at 133 MB/s. GPMI will sample DQ[7:0] at both rising and falling edge of an delayed DQS signal, which is provided by an internal DPLL. The delay value of this register can be controlled by GPMI register

GPMI\_READ\_DDR\_DLL\_CTRL.SLV\_DLY\_TARGET (see the GPMI chapter of the i.MX 6Solo/6DualLite reference manual). Generally, the typical delay value is equal to 0x7 which means 1/4 clock cycle delay expected. But if the board delay is big enough and cannot be ignored, the delay value should be made larger to compensate the board delay.

# 4.11 External Peripheral Interface Parameters

The following subsections provide information on external peripheral interfaces.

### 4.11.1 AUDMUX Timing Parameters

The AUDMUX provides a programmable interconnect logic for voice, audio, and data routing between internal serial interfaces (SSIs) and external serial interfaces (audio and voice codecs). The AC timing of AUDMUX external pins is governed by the SSI module. For more information, see the respective SSI electrical specifications found within this document.

# 4.11.2 ECSPI Timing Parameters

This section describes the timing parameters of the ECSPI blocks. The ECSPI have separate timing parameters for master and slave modes.

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 1

Table 54. eMMC4.4 Interface Timing Specification (continued)

| ID                                                     | Parameter              | Symbols          | Min | Max | Unit |  |  |

|--------------------------------------------------------|------------------------|------------------|-----|-----|------|--|--|

| uSDHC Input / Card Outputs CMD, DAT (Reference to CLK) |                        |                  |     |     |      |  |  |

| SD3                                                    | uSDHC Input Setup Time | t <sub>ISU</sub> | 2.6 | _   | ns   |  |  |

| SD4                                                    | uSDHC Input Hold Time  | t <sub>IH</sub>  | 1.5 | _   | ns   |  |  |

# 4.11.4.3 SDR50/SDR104 AC Timing

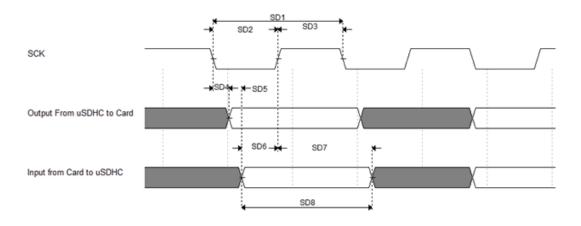

Figure 44 depicts the timing of SDR50/SDR104, and Table 55 lists the SDR50/SDR104 timing characteristics.

Figure 44. SDR50/SDR104 Timing

Table 55. SDR50/SDR104 Interface Timing Specification

| ID  | Parameter                                                     | Symbols          | Min                  | Max                  | Unit |  |  |  |  |

|-----|---------------------------------------------------------------|------------------|----------------------|----------------------|------|--|--|--|--|

|     | Card Input Clock                                              |                  |                      |                      |      |  |  |  |  |

| SD1 | Clock Frequency Period                                        | t <sub>CLK</sub> | 4.8                  | _                    | ns   |  |  |  |  |

| SD2 | Clock Low Time                                                | t <sub>CL</sub>  | 0.3*t <sub>CLK</sub> | 0.7*t <sub>CLK</sub> | ns   |  |  |  |  |

| SD2 | Clock High Time                                               | t <sub>СН</sub>  | 0.3*t <sub>CLK</sub> | 0.7*t <sub>CLK</sub> | ns   |  |  |  |  |

|     | uSDHC Output/Card Inputs 0                                    | CMD, DAT in SDF  | R50 (Reference       | e to CLK)            |      |  |  |  |  |

| SD4 | uSDHC Output Delay                                            | t <sub>OD</sub>  | -3                   | 1                    | ns   |  |  |  |  |

|     | uSDHC Output/Card Inputs C                                    | MD, DAT in SDR   | 104 (Referenc        | e to CLK)            |      |  |  |  |  |

| SD5 | uSDHC Output Delay                                            | t <sub>OD</sub>  | -1.6                 | 1                    | ns   |  |  |  |  |

|     | uSDHC Input/Card Outputs CMD, DAT in SDR50 (Reference to CLK) |                  |                      |                      |      |  |  |  |  |

| SD6 | uSDHC Input Setup Time                                        | t <sub>ISU</sub> | 2.5                  | _                    | ns   |  |  |  |  |

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 1

85

Table 55. SDR50/SDR104 Interface Timing Specification (continued)

| ID  | Parameter                                                                   | Symbols          | Min                  | Max | Unit |  |  |

|-----|-----------------------------------------------------------------------------|------------------|----------------------|-----|------|--|--|

| SD7 | uSDHC Input Hold Time                                                       | t <sub>IH</sub>  | 1.5                  | _   | ns   |  |  |

|     | uSDHC Input/Card Outputs CMD, DAT in SDR104 (Reference to CLK) <sup>1</sup> |                  |                      |     |      |  |  |

| SD8 | Card Output Data Window                                                     | t <sub>ODW</sub> | 0.5*t <sub>CLK</sub> | _   | ns   |  |  |

<sup>&</sup>lt;sup>1</sup>Data window in SDR100 mode is variable.

### 4.11.4.4 Bus Operation Condition for 3.3 V and 1.8 V Signaling

Signaling level of SD/eMMC4.3 and eMMC4.4 modes is 3.3 V. Signaling level of SDR104/SDR50 mode is 1.8 V. The DC parameters for the NVCC\_SD1, NVCC\_SD2 and NVCC\_SD3 supplies are identical to those shown in Table 23, "GPIO DC Parameters," on page 37.

# 4.11.5 Ethernet Controller (ENET) AC Electrical Specifications

The following timing specs are defined at the chip I/O pin and must be translated appropriately to arrive at timing specs/constraints for the physical interface.

### 4.11.5.1 ENET MII Mode Timing

This subsection describes MII receive, transmit, asynchronous inputs, and serial management signal timings.

# 4.11.5.1.1 MII Receive Signal Timing (ENET\_RX\_DATA3,2,1,0, ENET\_RX\_EN, ENET\_RX\_ER, and ENET\_RX\_CLK)

The receiver functions correctly up to an ENET\_RX\_CLK maximum frequency of 25 MHz + 1%. There is no minimum frequency requirement. Additionally, the processor clock frequency must exceed twice the ENET\_RX\_CLK frequency.

| Table 64. I <sup>2</sup> C Module Ti | ming Parameters ( | (continued) | ) |

|--------------------------------------|-------------------|-------------|---|

|--------------------------------------|-------------------|-------------|---|

| ID   | Parameter                                           | Standa | ard Mode | Fast Mode         |     | Unit |

|------|-----------------------------------------------------|--------|----------|-------------------|-----|------|

|      |                                                     | Min    | Max      | Min               | Max |      |

| IC8  | Data set-up time                                    | 250    | _        | 100 <sup>3</sup>  | _   | ns   |

| IC9  | Bus free time between a STOP and START condition    | 4.7    | _        | 1.3               | _   | μs   |

| IC10 | Rise time of both I2DAT and I2CLK signals           | _      | 1000     | $20 + 0.1C_b^{4}$ | 300 | ns   |

| IC11 | Fall time of both I2DAT and I2CLK signals           | _      | 300      | $20 + 0.1C_b^{4}$ | 300 | ns   |

| IC12 | Capacitive load for each bus line (C <sub>b</sub> ) | _      | 400      | _                 | 400 | pF   |

<sup>&</sup>lt;sup>1</sup> A device must internally provide a hold time of at least 300 ns for I2DAT signal in order to bridge the undefined region of the falling edge of I2CLK.

# 4.11.10 Image Processing Unit (IPU) Module Parameters

The purpose of the IPU is to provide comprehensive support for the flow of data from an image sensor and/or to a display device. This support covers all aspects of these activities:

- Connectivity to relevant devices—cameras, displays, graphics accelerators, and TV encoders.

- Related image processing and manipulation: sensor image signal processing, display processing, image conversions, and other related functions.

- Synchronization and control capabilities, such as avoidance of tearing artifacts.

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 1

<sup>&</sup>lt;sup>2</sup> The maximum hold time has only to be met if the device does not stretch the LOW period (ID no IC5) of the I2CLK signal.

A Fast-mode I<sup>2</sup>C-bus device can be used in a Standard-mode I<sup>2</sup>C-bus system, but the requirement of Set-up time (ID No IC7) of 250 ns must be met. This automatically is the case if the device does not stretch the LOW period of the I2CLK signal. If such a device does stretch the LOW period of the I2CLK signal, it must output the next data bit to the I2DAT line max\_rise\_time (IC9) + data\_setup\_time (IC7) = 1000 + 250 = 1250 ns (according to the Standard-mode I<sup>2</sup>C-bus specification) before the I2CLK line is released.

<sup>&</sup>lt;sup>4</sup> C<sub>b</sub> = total capacitance of one bus line in pF.

Table 67. Video Signal Cross-Reference

| i.MX 6Solo/6DualLite  |                             |               |               | LCD           |                             |                 |                 |                                                               |

|-----------------------|-----------------------------|---------------|---------------|---------------|-----------------------------|-----------------|-----------------|---------------------------------------------------------------|

|                       | RGB,                        | R             | GB/TV S       | Signal A      | Illocation                  | (Examp          | le)             | Comment <sup>1</sup>                                          |

| Port Name<br>(x=0, 1) | Signal<br>Name<br>(General) | 16-bit<br>RGB | 18-bit<br>RGB | 24 Bit<br>RGB | 8-bit<br>YCrCb <sup>2</sup> | 16-bit<br>YCrCb | 20-bit<br>YCrCb |                                                               |

| DISPx_DAT0            | DAT[0]                      | B[0]          | B[0]          | B[0]          | Y/C[0]                      | C[0]            | C[0]            | The restrictions are as follows:  • There are maximal three   |

| DISPx_DAT1            | DAT[1]                      | B[1]          | B[1]          | B[1]          | Y/C[1]                      | C[1]            | C[1]            | continuous groups of bits that could be independently         |

| DISPx_DAT2            | DAT[2]                      | B[2]          | B[2]          | B[2]          | Y/C[2]                      | C[2]            | C[2]            | mapped to the external bus. Groups should not be              |

| DISPx_DAT3            | DAT[3]                      | B[3]          | B[3]          | B[3]          | Y/C[3]                      | C[3]            | C[3]            | overlapped.  The bit order is expressed in                    |

| DISPx_DAT4            | DAT[4]                      | B[4]          | B[4]          | B[4]          | Y/C[4]                      | C[4]            | C[4]            | each of the bit groups, for example, B[0] = least significant |

| DISPx_DAT5            | DAT[5]                      | G[0]          | B[5]          | B[5]          | Y/C[5]                      | C[5]            | C[5]            | blue pixel bit                                                |

| DISPx_DAT6            | DAT[6]                      | G[1]          | G[0]          | B[6]          | Y/C[6]                      | C[6]            | C[6]            |                                                               |

| DISPx_DAT7            | DAT[7]                      | G[2]          | G[1]          | B[7]          | Y/C[7]                      | C[7]            | C[7]            |                                                               |

| DISPx_DAT8            | DAT[8]                      | G[3]          | G[2]          | G[0]          | _                           | Y[0]            | C[8]            |                                                               |

| DISPx_DAT9            | DAT[9]                      | G[4]          | G[3]          | G[1]          | _                           | Y[1]            | C[9]            |                                                               |

| DISPx_DAT10           | DAT[10]                     | G[5]          | G[4]          | G[2]          | _                           | Y[2]            | Y[0]            |                                                               |

| DISPx_DAT11           | DAT[11]                     | R[0]          | G[5]          | G[3]          | _                           | Y[3]            | Y[1]            |                                                               |

| DISPx_DAT12           | DAT[12]                     | R[1]          | R[0]          | G[4]          | _                           | Y[4]            | Y[2]            |                                                               |

| DISPx_DAT13           | DAT[13]                     | R[2]          | R[1]          | G[5]          | _                           | Y[5]            | Y[3]            |                                                               |

| DISPx_DAT14           | DAT[14]                     | R[3]          | R[2]          | G[6]          | _                           | Y[6]            | Y[4]            |                                                               |

| DISPx_DAT15           | DAT[15]                     | R[4]          | R[3]          | G[7]          | _                           | Y[7]            | Y[5]            |                                                               |

| DISPx_DAT16           | DAT[16]                     | _             | R[4]          | R[0]          | _                           | _               | Y[6]            |                                                               |

| DISPx_DAT17           | DAT[17]                     | _             | R[5]          | R[1]          | _                           | _               | Y[7]            |                                                               |

| DISPx_DAT18           | DAT[18]                     | _             | _             | R[2]          | _                           | _               | Y[8]            |                                                               |

| DISPx_DAT19           | DAT[19]                     | _             | _             | R[3]          | _                           | _               | Y[9]            |                                                               |

| DISPx_DAT20           | DAT[20]                     | _             | _             | R[4]          | _                           | _               | _               |                                                               |

| DISPx_DAT21           | DAT[21]                     | _             | _             | R[5]          | _                           | _               | _               |                                                               |

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 1

Table 71. Electrical and Timing Information (continued)

| V <sub>IDTL</sub>   | Differential input low voltage threshold |                             | -70     |     | mV |

|---------------------|------------------------------------------|-----------------------------|---------|-----|----|

| V <sub>IHHS</sub>   | Single ended input high voltage          |                             |         | 460 | mV |

| V <sub>ILHS</sub>   | Single ended input low voltage           |                             | -40     |     | mV |

| V <sub>CMRXDC</sub> | Input common mode voltage                |                             | 70      | 330 | mV |

| Z <sub>ID</sub>     | Differential input impedance             |                             | 80      | 125 | Ω  |

|                     | LP Lir                                   | e Receiver DC Specification | ns      |     | •  |

| V <sub>IL</sub>     | Input low voltage                        |                             |         | 550 | mV |

| V <sub>IH</sub>     | Input high voltage                       |                             | 920     |     | mV |

| V <sub>HYST</sub>   | Input hysteresis                         |                             | 25      |     | mV |

|                     | Contention                               | Line Receiver DC Specific   | cations |     | •  |

| V <sub>ILF</sub>    | Input low fault threshold                |                             | 200     | 450 | mV |

# 4.11.13 HSI Host Controller Timing Parameters

This section describes the timing parameters of the HSI Host Controller which are compliant with High-speed Synchronous Serial Interface (HSI) Physical Layer specification version 1.01.

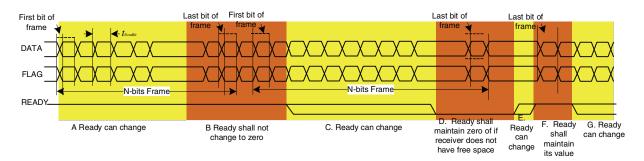

### 4.11.13.1 Synchronous Data Flow

Figure 76. Synchronized Data Flow READY Signal Timing (Frame and Stream Transmission)

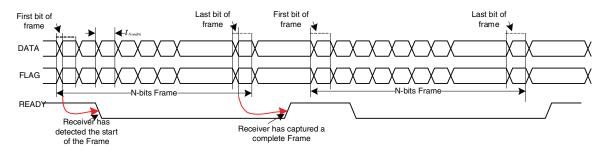

### 4.11.13.2 Pipelined Data Flow

Figure 77. Pipelined Data Flow Ready Signal Timing (Frame Transmission Mode)

### 4.11.13.3 Receiver Real-Time Data Flow

Figure 78. Receiver Real-Time Data Flow READY Signal Timing

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 1 Freescale Semiconductor 117

### 4.11.14 PCIe PHY Parameters

The PCIe interface complies with PCIe specification Gen2 x1 lane and supports the PCI Express 1.1/2.0 standard.

### 4.11.14.1 PCIE\_REXT Reference Resistor Connection

The impedance calibration process requires connection of reference resistor 200  $\Omega$ . 1% precision resistor on PCIE\_REXT pads to ground. It is used for termination impedance calibration.

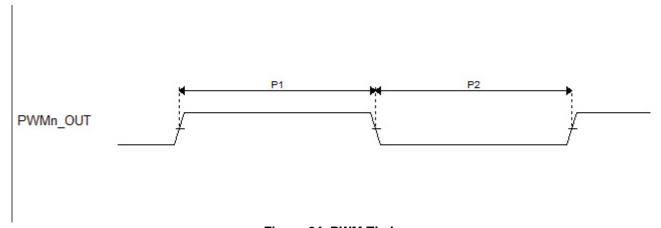

# 4.11.15 Pulse Width Modulator (PWM) Timing Parameters

This section describes the electrical information of the PWM. The PWM can be programmed to select one of three clock signals as its source frequency. The selected clock signal is passed through a prescaler before being input to the counter. The output is available at the pulse-width modulator output (PWMO) external pin.

Figure 84 depicts the timing of the PWM, and Table 74 lists the PWM timing parameters.

Figure 84. PWM Timing

**Table 74. PWM Output Timing Parameters**

| ID | Parameter                   | Min | Max     | Unit |

|----|-----------------------------|-----|---------|------|

|    | PWM Module Clock Frequency  | 0   | ipg_clk | MHz  |

| P1 | PWM output pulse width high | 15  |         | ns   |

| P2 | PWM output pulse width low  | 15  |         | ns   |

# 4.11.18.4 SSI Receiver Timing with External Clock

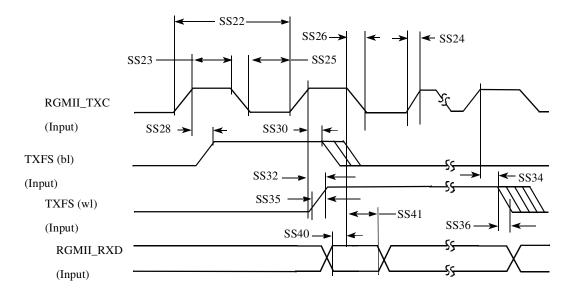

Figure 94 depicts the SSI receiver external clock timing and Table 81 lists the timing parameters for the receiver timing with the external clock.

Figure 94. SSI Receiver External Clock Timing Diagram

**Table 81. SSI Receiver Timing with External Clock**

| ID   | Parameter                          | Min  | Max  | Unit |  |  |  |

|------|------------------------------------|------|------|------|--|--|--|

|      | External Clock Operation           |      |      |      |  |  |  |

| SS22 | (Tx/Rx) CK clock period            | 81.4 | _    | ns   |  |  |  |

| SS23 | (Tx/Rx) CK clock high period       | 36   | _    | ns   |  |  |  |

| SS24 | (Tx/Rx) CK clock rise time         | _    | 6.0  | ns   |  |  |  |

| SS25 | (Tx/Rx) CK clock low period        | 36   | _    | ns   |  |  |  |

| SS26 | (Tx/Rx) CK clock fall time         | _    | 6.0  | ns   |  |  |  |

| SS28 | (Rx) CK high to FS (bl) high       | -10  | 15.0 | ns   |  |  |  |

| SS30 | (Rx) CK high to FS (bl) low        | 10   | _    | ns   |  |  |  |

| SS32 | (Rx) CK high to FS (wl) high       | -10  | 15.0 | ns   |  |  |  |

| SS34 | (Rx) CK high to FS (wl) low        | 10   | _    | ns   |  |  |  |

| SS35 | (Tx/Rx) External FS rise time      | _    | 6.0  | ns   |  |  |  |

| SS36 | (Tx/Rx) External FS fall time      | _    | 6.0  | ns   |  |  |  |

| SS40 | SRXD setup time before (Rx) CK low | 10   | _    | ns   |  |  |  |

| SS41 | SRXD hold time after (Rx) CK low   | 2    | _    | ns   |  |  |  |

# 6.1.2 21 x 21 mm Supplies Contact Assignments and Functional Contact Assignments

Table 91 shows supplies contact assignments for the 21 x 21 mm package.

Table 91. 21 x 21 mm Supplies Contact Assignments

| Supply Rail Name | Ball(s) Position(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Remark                                                   |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| CSI_REXT         | D4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |

| DRAM_VREF        | AC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                          |

| DSI_REXT         | G4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |

| GND              | A4, A8, A13, A25, B4, C1, C4, C6, C10, D3, D6, D8, E5, E6, E7, F5, F6, F7, F8, G3, G10, G19, H8, H12, H15, H18, J2, J8, J12, J15, J18, K8, K10, K12, K15, K18, L2, L5, L8, L10, L12, L15, L18, M8, M10, M12, M15, M18, N8, N10, N15, N18, P8, P10, P12, P15, P18, R8, R12, R15, R17, T8, T11, T12, T15, T17, T19, U8, U11, U12, U15, U17, U19, V8, V19, W3, W7, W8, W9, W10, W11, W12, W13, W15, W16, W17, W18, W19, Y5, Y24, AA7, AA10, AA13, AA16, AA19, AA22, AB3, AB24, AD4, AD7, AD10, AD13, AD16, AD19, AD22, AE1, AE25 |                                                          |

| HDMI_REF         | J1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |

| HDMI_VP          | L7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |

| HDMI_VPH         | M7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |

| NVCC_CSI         | N7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Supply of the camera sensor interface                    |

| NVCC_DRAM        | R18, T18, U18, V9, V10, V11, V12, V13, V14, V15, V16, V17, V18                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Supply of the DDR interface                              |

| NVCC_EIM         | K19, L19, M19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Supply of the EIM interface                              |

| NVCC_ENET        | R19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Supply of the ENET interface                             |

| NVCC_GPIO        | P7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Supply of the GPIO interface                             |

| NVCC_JTAG        | J7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Supply of the JTAG tap controller interface              |

| NVCC_LCD         | P19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Supply of the LCD interface                              |

| NVCC_LVDS2P5     | V7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Supply of the LVDS display interface and DDR pre-drivers |

| NVCC_MIPI        | K7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Supply of the MIPI interface                             |

| NVCC_NANDF       | G15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Supply of the raw NAND Flash memories interface          |

| NVCC_PLL_OUT     | E8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |

| NVCC_RGMII       | G18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Supply of the ENET interface                             |

| NVCC_SD1         | G16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Supply of the SD card interface                          |

| NVCC_SD2         | G17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Supply of the SD card interface                          |

| NVCC_SD3         | G14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Supply of the SD card interface                          |