#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Betuns                             |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Active                                                                                                              |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 2 Core, 32-Bit                                                                                                      |

| Speed                              | 1.0GHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON™ SIMD                                                                                              |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | -                                                                                                                   |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | 0°C ~ 95°C (TJ)                                                                                                     |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-LFBGA                                                                                                           |

| Supplier Device Package            | 624-MAPBGA (21x21)                                                                                                  |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6u5dvm10ac                                             |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

software downloads. The security features will be discussed in detail in the *i.MX 6Solo/6DualLite Security Reference Manual* (to be released soon).

• Integrated power management—The processors integrate linear regulators and internally generate voltage levels for different domains. This significantly simplifies system power management structure.

# **1.1 Ordering Information**

Table 1 shows the orderable part numbers covered by this datasheet. Table 1 does not include all possible orderable part numbers. The latest part numbers are available on the web page freescale.com/imx6series. If the desired part number is not listed in Table 1, or there may be any questions about available parts, see the web page freescale.com/imx6series or contact a Freescale representative.

| Part Number     | Solo/DualLite<br>CPU | Options                          | Speed<br>Grade | Temperature<br>Grade | Package                                |

|-----------------|----------------------|----------------------------------|----------------|----------------------|----------------------------------------|

| MCIMX6U8DVM10AB | i.MX 6DualLite       | With VPU, GPU, EPD, no<br>MLB    | 1 GHz          | Consumer             | 21 mm x 21 mm, 0.8 mm<br>pitch, MAPBGA |

| MCIMX6U5DVM10AB | i.MX 6DualLite       | With VPU, GPU, no EPD, no<br>MLB | 1 GHz          | Consumer             | 21 mm x 21 mm, 0.8 mm<br>pitch, MAPBGA |

| MCIMX6U5EVM10AB | i.MX 6DualLite       | With VPU, GPU, no EPD, no<br>MLB | 1 GHz          | Extended<br>Consumer | 21 mm x 21 mm, 0.8 mm<br>pitch, MAPBGA |

| MCIMX6S8DVM10AB | i.MX 6Solo           | With VPU, GPU, EPD, no<br>MLB    | 1 GHz          | Consumer             | 21 mm x 21 mm, 0.8 mm<br>pitch, MAPBGA |

| MCIMX6S5DVM10AB | i.MX 6Solo           | With VPU, GPU, no EPD, no<br>MLB | 1 GHz          | Consumer             | 21 mm x 21 mm, 0.8 mm<br>pitch, MAPBGA |

| MCIMX6S5EVM10AB | i.MX 6Solo           | With VPU, GPU, no EPD, no<br>MLB | 1 GHz          | Extended<br>Consumer | 21 mm x 21 mm, 0.8 mm<br>pitch, MAPBGA |

Table 1. Orderable Part Numbers

Figure 1 describe the part number nomenclature so that the users can identify the characteristics of the specific part number they have (for example, cores, frequency, temperature grade, fuse options, and silicon revision). The primary characteristic which describes which datasheet applies to a specific part is the temperature grade (junction) field.

- The i.MX 6Solo/6DualLite Automotive and Infotainment Applications Processors datasheet (IMX6SDLAEC) covers parts listed with an "A (Automotive temp)"

- The i.MX 6Solo/6DualLite Applications Processors for Consumer Products datasheet (IMX6SDLCEC) covers parts listed with a "D (Consumer temp)" or "E (Extended Consumer temp)"

- The i.MX 6Solo/6DualLite Applications Processors for Industrial Products datasheet (IMX6SDLIEC) covers parts listed with "C (Industrial temp)"

Ensure to have the proper datasheet for specific part by verifying the temperature grade (junction) field and matching it to the proper datasheet. If there will be any questions, visit see the web page freescale.com/imx6series or contact a Freescale representative for details.

## NOTE

The actual feature set depends on the part numbers as described in Table 1, "Orderable Part Numbers," on page 3. Functions, such as video hardware acceleration, and 2D and 3D hardware graphics acceleration may not be enabled for specific part numbers.

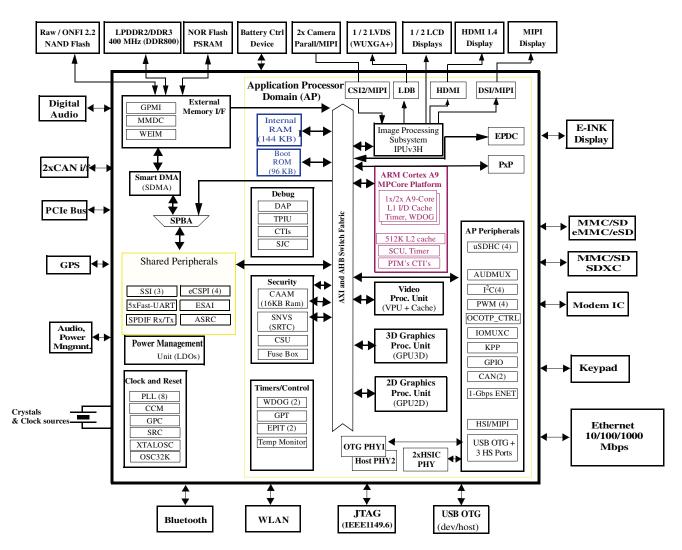

# 2 Architectural Overview

The following subsections provide an architectural overview of the i.MX 6Solo/6DualLite processor system.

# 2.1 Block Diagram

Figure 2 shows the functional modules in the i.MX 6Solo/6DualLite processor system.

<sup>1</sup> 144 KB RAM including 16 KB RAM inside the CAAM.

| Block Mnemonic                   | Block Name                    | Subsystem                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------|-------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OCOTP_CTRL                       | OTP Controller                | Security                    | The On-Chip OTP controller (OCOTP_CTRL) provides<br>an interface for reading, programming, and/or overriding<br>identification and control information stored in on-chip<br>fuse elements. The module supports<br>electrically-programmable poly fuses (eFUSEs). The<br>OCOTP_CTRL also provides a set of volatile<br>software-accessible signals that can be used for<br>software control of hardware elements, not requiring<br>non-volatility. The OCOTP_CTRL provides the primary<br>user-visible mechanism for interfacing with on-chip fuse<br>elements. Among the uses for the fuses are unique chip<br>identifiers, mask revision numbers, cryptographic keys,<br>JTAG secure mode, boot characteristics, and various<br>control signals, requiring permanent non-volatility. |

| OCRAM                            | On-Chip Memory<br>controller  | Data Path                   | The On-Chip Memory controller (OCRAM) module is<br>designed as an interface between system's AXI bus and<br>internal (on-chip) SRAM memory module.<br>In i.MX 6Solo/6DualLite processors, the OCRAM is<br>used for controlling the 128 KB multimedia RAM through<br>a 64-bit AXI bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| OSC32KHz                         | OSC32KHz                      | Clocking                    | Generates 32.768 KHz clock from external crystal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PCle                             | PCI Express 2.0               | Connectivity<br>Peripherals | The PCIe IP provides PCI Express Gen 2.0 functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PMU                              | Power-Management<br>functions | Data Path                   | Integrated power management unit. Used to provide power to various SoC domains.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PWM-1<br>PWM-2<br>PWM-3<br>PWM-4 | Pulse Width Modulation        | Connectivity<br>Peripherals | The pulse-width modulator (PWM) has a 16-bit counter<br>and is optimized to generate sound from stored sample<br>audio images and it can also generate tones. It uses<br>16-bit resolution and a $4x16$ data FIFO to generate<br>sound.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| РХР                              | PiXel Processing Pipeline     | Display Peripherals         | A high-performance pixel processor capable of 1<br>pixel/clock performance for combined operations, such<br>as color-space conversion, alpha blending,<br>gamma-mapping, and rotation. The PXP is enhanced<br>with features specifically for gray scale applications. In<br>addition, the PXP supports traditional pixel/frame<br>processing paths for still-image and video processing<br>applications, allowing it to interface with the integrated<br>EPD.                                                                                                                                                                                                                                                                                                                         |

| RAM<br>128 KB                    | Internal RAM                  | Internal Memory             | Internal RAM, which is accessed through OCRAM memory controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RAM<br>16 KB                     | Secure/non-secure RAM         | Secured Internal<br>Memory  | Secure/non-secure Internal RAM, interfaced through the CAAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ROM<br>96KB                      | Boot ROM                      | Internal Memory             | Supports secure and regular Boot Modes. Includes read protection on 4K region for content protection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ROMCP                            | ROM Controller with<br>Patch  | Data Path                   | ROM Controller with ROM Patch support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

### Table 2. i.MX 6Solo/6DualLite Modules List (continued)

### **Modules List**

| Signal Name      | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRAM_VREF        | When using DDR_VREF with DDR I/O, the nominal reference voltage must be half of the NVCC_DRAM supply. The user must tie DDR_VREF to a precision external resistor divider. Use a 1 k $\Omega$ 0.5% resistor to GND and a 1 k $\Omega$ 0.5% resistor to NVCC_DRAM. Shunt each resistor with a closely-mounted 0.1 $\mu$ F capacitor.                                                                                                                                                               |

|                  | To reduce supply current, a pair of 1.5 k $\Omega$ 0.1% resistors can be used. Using resistors with recommended tolerances ensures the ± 2% DDR_VREF tolerance (per the DDR3 specification) is maintained when four DDR3 ICs plus the i.MX 6Solo/6DualLite are drawing current on the resistor divider.                                                                                                                                                                                           |

|                  | It is recommended to use regulated power supply for "big" memory configurations (more that eight devices)                                                                                                                                                                                                                                                                                                                                                                                         |

| ZQPAD            | DRAM calibration resistor 240 $\Omega$ 1% used as reference during DRAM output buffer driver calibration should be connected between this pad and GND.                                                                                                                                                                                                                                                                                                                                            |

| NVCC_LVDS2P5     | The DDR pre-drivers share the NVCC_LVDS2P5 ball with the LVDS interface. This ball can be shorted to VDDHIGH_CAP on the circuit board.                                                                                                                                                                                                                                                                                                                                                            |

| VDD_FA<br>FA_ANA | These signals are reserved for Freescale manufacturing use only. User must tie both connections to GND.                                                                                                                                                                                                                                                                                                                                                                                           |

| GPANAIO          | This signal is reserved for Freescale manufacturing use only. User must leave this connection floating.                                                                                                                                                                                                                                                                                                                                                                                           |

| JTAG_nnnn        | The JTAG interface is summarized in Table 4. Use of external resistors is unnecessary. However, if external resistors are used, the user must ensure that the on-chip pull-up/down configuration is followed. For example, do not use an external pull down on an input that has on-chip pull-up.                                                                                                                                                                                                 |

|                  | JTAG_TDO is configured with a keeper circuit such that the floating condition is eliminated if an external pull resistor is not present. An external pull resistor on JTAG_TDO is detrimental and should be avoided.                                                                                                                                                                                                                                                                              |

|                  | JTAG_MOD is referenced as SJC_MOD in the i.MX 6Solo/6DualLite reference manual. Both names refer to the same signal. JTAG_MOD must be externally connected to GND for normal operation. Termination to GND through an external pull-down resistor (such as 1 k $\Omega$ ) is allowed. JTAG_MOD set to hi configures the JTAG interface to mode compliant with IEEE1149.1 standard. JTAG_MOD set to low configures the JTAG interface for common SW debug adding all the system TAPs to the chain. |

| NC               | These signals are No Connect (NC) and should be floated by the user.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| POR_B            | This cold reset negative logic input resets all modules and logic in the IC.<br>May be used in addition to internally generated power on reset signal (logical AND, both internal<br>and external signals are considered active low).                                                                                                                                                                                                                                                             |

| ONOFF            | In normal mode may be connected to ON/OFF button (De-bouncing provided at this input).<br>Internally this pad is pulled up. Short connection to GND in OFF mode causes internal power<br>management state machine to change state to ON. In ON mode short connection to GND<br>generates interrupt (intended to SW controllable power down). Long above ~5s connection to GND<br>causes "forced" OFF.                                                                                             |

| TEST_MODE        | TEST_MODE is for Freescale factory use. This signal is internally connected to an on-chip pull-down device. The user must either float this signal or tie it to GND.                                                                                                                                                                                                                                                                                                                              |

| PCIE_REXT        | The impedance calibration process requires connection of reference resistor 200 $\Omega$ 1% precision resistor on PCIE_REXT pad to ground.                                                                                                                                                                                                                                                                                                                                                        |

# 4.1.3 **Operating Ranges**

Table 9 provides the operating ranges of the i.MX 6Solo/6DualLite processors. For details on the chip's power structure, see the "Power Management Unit (PMU)" chapter of the *i.MX 6Solo/6DualLite Reference Manual (IMX6SDLRM)*.

| Parameter<br>Description                         | Symbol                   | Min                  | Тур  | Max <sup>1</sup> | Unit | Comment                                                                                                                                                  |

|--------------------------------------------------|--------------------------|----------------------|------|------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Run mode: LDO<br>enabled                         | VDDARM_IN                | 1.350 <sup>2</sup>   | —    | 1.5              | V    | LDO Output Set Point (VDDARM_CAP) = 1.225 V minimum for operation up to 996 MHz.                                                                         |

|                                                  |                          | 1.275 <sup>2</sup>   | —    | 1.5              | V    | LDO Output Set Point (VDDARM_CAP) = 1.150 V minimum for operation up to 792 MHz.                                                                         |

|                                                  |                          | 1.175 <sup>2</sup>   | —    | 1.5              | V    | LDO Output Set Point (VDDARM_CAP) = 1.05<br>V minimum for operation up to 396 MHz.                                                                       |

|                                                  | VDDSOC_IN <sup>3</sup>   | 1.275 <sup>2,4</sup> | —    | 1.5              | V    | VPU = 328 MHz, VDDSOC and VDDPU LDO<br outputs (VDDSOC_CAP and VDDPU_CAP) =<br>1.225 V maximum and 1.15 V minimum.                                       |

| Run mode: LDO<br>bypassed                        | VDDARM_IN                | 1.250                | —    | 1.3              | V    | LDO bypassed for operation up to 996 MHz                                                                                                                 |

|                                                  |                          | 1.150                | —    | 1.3              | V    | LDO bypassed for operation up to 792 MHz                                                                                                                 |

|                                                  |                          | 1.05                 | —    | 1.3              | V    | LDO bypassed for operation up to 396 MHz                                                                                                                 |

|                                                  | VDDSOC_IN                | 1.15 <sup>4</sup>    | —    | 1.225            | V    | LDO bypassed for operation VPU = 328 MHz</td                                                                                                             |

| Standby/DSM mode                                 | VDDARM_IN                | 0.9                  | —    | 1.3              | V    | Refer to Table 13, "Stop Mode Current and Power Consumption," on page 29.                                                                                |

|                                                  | VDDSOC_IN                | 0.9                  | —    | 1.225            | V    |                                                                                                                                                          |

| VDDHIGH internal<br>regulator                    | VDDHIGH_IN               | 2.8                  | —    | 3.3              | V    | Must match the range of voltges that the rechargeable backup battery supports.                                                                           |

| Backup battery supply range                      | VDD_SNVS_IN <sup>5</sup> | 2.9                  | _    | 3.3              | V    | Should be supplied from the same supply as VDDHIGH_IN if the system does not require keeping real time and other data on OFF state.                      |

| USB supply voltages                              | USB_OTG_VBUS             | 4.4                  | —    | 5.25             | V    |                                                                                                                                                          |

|                                                  | USB_H1_VBUS              | 4.4                  | —    | 5.25             | V    |                                                                                                                                                          |

| DDR I/O supply voltage                           | NVCC_DRAM                | 1.14                 | 1.2  | 1.3              | V    | LPDDR2, DDR3-U                                                                                                                                           |

|                                                  |                          | 1.425                | 1.5  | 1.575            | V    | DDR3                                                                                                                                                     |

|                                                  |                          | 1.283                | 1.35 | 1.45             | V    | DDR3_L                                                                                                                                                   |

| Supply for RGMII I/O<br>power group <sup>6</sup> | NVCC_RGMII               | 1.15                 | _    | 2.625            | V    | 1.15 V – 1.30 V in HSIC 1.2 V mode<br>1.43 V – 1.58 V in RMGII 1.5 V mode<br>1.70 V – 1.90 V in RMGII 1.8 V mode<br>2.25 V – 2.625 V in RMGII 2.5 V mode |

| Table | 9. | Operati | ing | Ranges |

|-------|----|---------|-----|--------|

|-------|----|---------|-----|--------|

| Voltage Source | Load      | Comment                                             |

|----------------|-----------|-----------------------------------------------------|

| VDDSOC_CAP     | HDMI_VP   | Board-level connection to VDDSOC_CAP <sup>2 3</sup> |

|                | PCIE_VP   |                                                     |

|                | PCIE_VPTX |                                                     |

Table 10. On-Chip LDOs<sup>1</sup> and their On-Chip Loads (continued)

<sup>1</sup> On-chip LDOs are designed to supply i.MX6 loads and must not be used to supply external loads.

<sup>2</sup> VDDARM\_CAP should not exceed VDDSOC\_CAP by more than 50 mV.

<sup>3</sup> There is no requirement for VDDSOC\_CAP to track within 50 mV as long as it is greater than VDDARM\_CAP.

## 4.1.4 External Clock Sources

Each i.MX 6Solo/6DualLite processor has two external input system clocks: a low frequency (CKIL) and a high frequency (XTAL).

The CKIL is used for low-frequency functions. It supplies the clock for wake-up circuit, power-down real time clock operation, and slow system and watch-dog counters. The clock input can be connected to either external oscillator or a crystal using internal oscillator amplifier. Additionally, there is an internal ring oscillator, which can substitute the CKIL, in case accuracy is not important.

The system clock input XTAL is used to generate the main system clock. It supplies the PLLs and other peripherals. The system clock input can be connected to either external oscillator or a crystal using internal oscillator amplifier.

Table 11 shows the interface frequency requirements.

| Parameter Description          | Symbol            | Min | Тур                       | Max | Unit |

|--------------------------------|-------------------|-----|---------------------------|-----|------|

| CKIL Oscillator <sup>1,2</sup> | f <sub>ckil</sub> | _   | 32.768 <sup>3</sup> /32.0 | _   | kHz  |

| XTAL Oscillator <sup>2,4</sup> | f <sub>xtal</sub> |     | 24                        |     | MHz  |

<sup>1</sup> External oscillator or a crystal with internal oscillator amplifier.

<sup>2</sup> The required frequency stability of this clock source is application dependent. For recommendations, see the Hardware Development Guide for i.MX 6Dual, 6Quad, 6Solo, 6DualLite Families of Applications Processors (IMX6DQ6SDLHDG).

<sup>3</sup> Recommended nominal frequency 32.768 kHz.

their input supply ripple rejection and their on-die trimming. This translates into more stable voltage for the on-chip logics.

These regulators have three basic modes:

- Bypass. The regulation FET is switched fully on passing the external voltage, to the load unaltered. The analog part of the regulator is powered down in this state, removing any loss other than the IR drop through the power grid and FET.

- Power Gate. The regulation FET is switched fully off limiting the current draw from the supply. The analog part of the regulator is powered down here limiting the power consumption.

- Analog regulation mode. The regulation FET is controlled such that the output voltage of the regulator equals the programmed target voltage. The target voltage is fully programmable in 25 mV steps.

For additional information, see the i.MX 6Solo/6DualLite reference manual.

## 4.3.2 Analog Regulators

## 4.3.2.1 LDO\_1P1

The LDO\_1P1 regulator implements a programmable linear-regulator function from VDDHIGH\_IN (see Table 9 for minimum and maximum input requirements). Typical Programming Operating Range is 1.0 V to 1.2 V with the nominal default setting as 1.1 V. Since the accuracy or the % regulation is not tested, and only tested with the LDO set to either 1.0V or 1.2V, this is the only range that is guaranteed. The regulator has been designed to be stable with a minimum external low ESR decoupling capacitor of 1  $\mu$ F (2.2  $\mu$ F should be considered the recommended minimum value for component selection), though the actual capacitance required should be determined by the application. A programmable brown-out detector is included in the regulator that can be used by the system to determine when the load capability of the regulator is being exceeded to take the necessary steps. Current-limiting can be enabled to allow for in-rush current requirements during start-up, if needed. Active-pull-down can also be enabled for systems requiring this feature.

For additional information, see the i.MX 6Solo/6DualLite reference manual.

## 4.3.2.2 LDO\_2P5

The LDO\_2P5 module implements a programmable linear-regulator function from VDDHIGH\_IN (see Table 9 for minimum and maximum input requirements). Typical Programming Operating Range is 2.25 V to 2.75 V with the nominal default setting as 2.5 V. Since the accuracy or the % regulation is not tested, and only tested with the LDO set to either 2.25V or 2.75V, this is the only range that is guaranteed. The regulator has been designed to be stable with a minimum external low ESR decoupling capacitor of 1  $\mu$ F (2.2  $\mu$ F should be considered the recommended minimum value for component selection), though the actual capacitance required should be determined by the application. A programmable brown-out detector is included in the regulator that can be used by the system to determine when the load capability of the regulator is being exceeded, to take the necessary steps. Current-limiting can be enabled to allow for in-rush current requirements during start-up, if needed. Active-pull-down can also be enabled for systems requiring this feature. An alternate self-biased low-precision weak-regulator is included that can be

# 4.4.3 Ethernet PLL

| Parameter          | Value                   |

|--------------------|-------------------------|

| Clock output range | 500 MHz                 |

| Reference clock    | 24 MHz                  |

| Lock time          | <11250 reference cycles |

### Table 19. Ethernet PLL's Electrical Parameters

## 4.4.4 480 MHz PLL

### Table 20. 480 MHz PLL's Electrical Parameters

| Parameter          | Value                 |

|--------------------|-----------------------|

| Clock output range | 480 MHz PLL output    |

| Reference clock    | 24 MHz                |

| Lock time          | <383 reference cycles |

## 4.4.5 ARM PLL

### Table 21. ARM PLL's Electrical Parameters

| Parameter          | Value                  |

|--------------------|------------------------|

| Clock output range | 650 MHz ~ 1.3 GHz      |

| Reference clock    | 24 MHz                 |

| Lock time          | <2250 reference cycles |

# 4.5 **On-Chip Oscillators**

## 4.5.1 OSC24M

This block implements an amplifier that when combined with a suitable quartz crystal and external load capacitors implements an oscillator. The oscillator is powered from NVCC\_PLL\_OUT.

The system crystal oscillator consists of a Pierce-type structure running off the digital supply. A straight forward biased-inverter implementation is used.

# 4.5.2 OSC32K

This block implements an amplifier that when combined with a suitable quartz crystal and external load capacitors implements a low power oscillator. It also implements a power mux such that it can be powered from either a ~3 V backup battery (VDD\_SNVS\_IN) or VDDHIGH\_IN such as the oscillator consumes

## 4.9.4.2 LPDDR2 Parameters

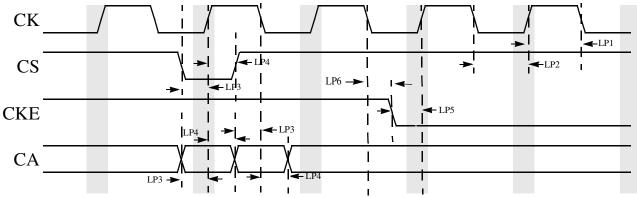

Figure 25 shows the basic timing parameters. The timing parameters for this diagram appear in Table 44.

Figure 25. LPDDR2 Command and Address Timing Parameters

| Table 44. LPDDR | 2 Timing Parameter |

|-----------------|--------------------|

|-----------------|--------------------|

|     | ID Parameter                 |                  | CK = 40 | Unit |      |

|-----|------------------------------|------------------|---------|------|------|

|     | Farameter                    | rameter Symbol – |         | Мах  | Unit |

| LP1 | SDRAM clock high-level width | tсн              | 0.45    | 0.55 | tск  |

| LP2 | SDRAM clock low-level width  | tCL              | 0.45    | 0.55 | tск  |

| LP3 | CA, CS setup time            | tis              | 380     | —    | ps   |

| LP4 | CA, CS hold time             | tін              | 380     | —    | ps   |

| LP5 | CKE setup time               | tiscke           | 770     | —    | tck  |

| LP6 | CKE hold time                | tihcke           | 770     | _    | tck  |

<sup>1</sup> All measurements are in reference to Vref level.

$^2~$  Measurements were done using balanced load and 25  $\Omega$  resistor from outputs to VDD\_REF.

| ID   | Parameter              | Symbol | Tim<br>T = GPMI C   | 0    | Unit |

|------|------------------------|--------|---------------------|------|------|

|      |                        |        | Min.                | Max. |      |

| NF23 | preamble delay         | tPRE   | (PRE_DELAY+1) x tCK | _    | ns   |

| NF24 | postamble delay        | tPOST  | POST_DELAY x tCK    | _    | ns   |

| NF25 | CLE and ALE setup time | tCALS  | 0.5 x tCK           | _    | ns   |

| NF26 | CLE and ALE hold time  | tCALH  | 0.5 x tCK           | —    | ns   |

Table 49. Samsung Toggle Mode Timing Parameters (continued)

For DDR Toggle mode, Figure 35 shows the timing diagram of DQS/DQ read valid window. The typical value of tDQSQ is 1.4 ns(max) and 1.4 ns (max) for tQHS at 133 MB/s. GPMI will sample DQ[7:0] at both rising and falling edge of an delayed DQS signal, which is provided by an internal DPLL. The delay value of this register can be controlled by GPMI register

GPMI\_READ\_DDR\_DLL\_CTRL.SLV\_DLY\_TARGET (see the GPMI chapter of the i.MX 6Solo/6DualLite reference manual). Generally, the typical delay value is equal to 0x7 which means 1/4 clock cycle delay expected. But if the board delay is big enough and cannot be ignored, the delay value should be made larger to compensate the board delay.

# 4.11 External Peripheral Interface Parameters

The following subsections provide information on external peripheral interfaces.

# 4.11.1 AUDMUX Timing Parameters

The AUDMUX provides a programmable interconnect logic for voice, audio, and data routing between internal serial interfaces (SSIs) and external serial interfaces (audio and voice codecs). The AC timing of AUDMUX external pins is governed by the SSI module. For more information, see the respective SSI electrical specifications found within this document.

# 4.11.2 ECSPI Timing Parameters

This section describes the timing parameters of the ECSPI blocks. The ECSPI have separate timing parameters for master and slave modes.

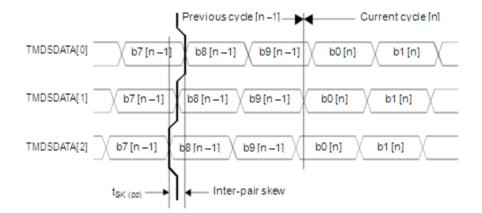

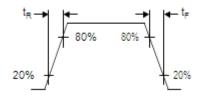

| Symbol              | Parameter                                          | Conditions                                          | Min. | Тур. | Max. | Unit            |  |  |

|---------------------|----------------------------------------------------|-----------------------------------------------------|------|------|------|-----------------|--|--|

|                     | TMDS Drivers Specifications                        |                                                     |      |      |      |                 |  |  |

| _                   | Maximum serial data rate                           | —                                                   | —    | —    | 3.4  | Gbps            |  |  |

| F<br>TMDSCLK        | TMDSCLK frequency                                  | On TMDSCLKP/N outputs                               | 25   | —    | 340  | MHz             |  |  |

| P<br>TMDSCLK        | TMDSCLK period                                     | eriod $RL = 50 \Omega$<br>See Figure 56.            |      | _    | 40   | ns              |  |  |

| <sup>t</sup> CDC    | TMDSCLK duty cycle                                 | $t = t / P TMDSCLK$ $RL = 50 \Omega$ See Figure 56. | 40   | 50   | 60   | %               |  |  |

| <sup>t</sup><br>CPH | TMDSCLK high time                                  | RL = 50 Ω<br>See Figure 56.                         | 4    | 5    | 6    | UI <sup>1</sup> |  |  |

| t<br>CPL            | TMDSCLK low timeRL = 50 $\Omega$<br>See Figure 56. |                                                     | 4    | 5    | 6    | UI <sup>1</sup> |  |  |

| —                   | TMDSCLK jitter <sup>2</sup>                        | RL = 50 Ω                                           | —    | —    | 0.25 | UI <sup>1</sup> |  |  |

| t<br>SK(p)          | Intra-pair (pulse) skew                            | $RL = 50 \Omega$<br>See Figure 58.                  | —    |      | 0.15 | UI <sup>1</sup> |  |  |

**Table 63. Switching Characteristics**

| i.MX 6Solo/6DualLite  |                             |               |                                    | LCD           |                             |                 |                 |                                                                     |

|-----------------------|-----------------------------|---------------|------------------------------------|---------------|-----------------------------|-----------------|-----------------|---------------------------------------------------------------------|

|                       | RGB,                        | R             | RGB/TV Signal Allocation (Example) |               |                             |                 |                 | Comment <sup>1</sup>                                                |

| Port Name<br>(x=0, 1) | Signal<br>Name<br>(General) | 16-bit<br>RGB | 18-bit<br>RGB                      | 24 Bit<br>RGB | 8-bit<br>YCrCb <sup>2</sup> | 16-bit<br>YCrCb | 20-bit<br>YCrCb |                                                                     |

| DISPx_DAT0            | DAT[0]                      | B[0]          | B[0]                               | B[0]          | Y/C[0]                      | C[0]            | C[0]            | The restrictions are as follows:<br>• There are maximal three       |

| DISPx_DAT1            | DAT[1]                      | B[1]          | B[1]                               | B[1]          | Y/C[1]                      | C[1]            | C[1]            | continuous groups of bits that<br>could be independently            |

| DISPx_DAT2            | DAT[2]                      | B[2]          | B[2]                               | B[2]          | Y/C[2]                      | C[2]            | C[2]            | mapped to the external bus.<br>Groups should not be                 |

| DISPx_DAT3            | DAT[3]                      | B[3]          | B[3]                               | B[3]          | Y/C[3]                      | C[3]            | C[3]            | <ul><li>overlapped.</li><li>The bit order is expressed in</li></ul> |

| DISPx_DAT4            | DAT[4]                      | B[4]          | B[4]                               | B[4]          | Y/C[4]                      | C[4]            | C[4]            | each of the bit groups, for<br>example, B[0] = least significant    |

| DISPx_DAT5            | DAT[5]                      | G[0]          | B[5]                               | B[5]          | Y/C[5]                      | C[5]            | C[5]            | blue pixel bit                                                      |

| DISPx_DAT6            | DAT[6]                      | G[1]          | G[0]                               | B[6]          | Y/C[6]                      | C[6]            | C[6]            |                                                                     |

| DISPx_DAT7            | DAT[7]                      | G[2]          | G[1]                               | B[7]          | Y/C[7]                      | C[7]            | C[7]            |                                                                     |

| DISPx_DAT8            | DAT[8]                      | G[3]          | G[2]                               | G[0]          |                             | Y[0]            | C[8]            |                                                                     |

| DISPx_DAT9            | DAT[9]                      | G[4]          | G[3]                               | G[1]          |                             | Y[1]            | C[9]            |                                                                     |

| DISPx_DAT10           | DAT[10]                     | G[5]          | G[4]                               | G[2]          | _                           | Y[2]            | Y[0]            | -                                                                   |

| DISPx_DAT11           | DAT[11]                     | R[0]          | G[5]                               | G[3]          | _                           | Y[3]            | Y[1]            |                                                                     |

| DISPx_DAT12           | DAT[12]                     | R[1]          | R[0]                               | G[4]          | _                           | Y[4]            | Y[2]            |                                                                     |

| DISPx_DAT13           | DAT[13]                     | R[2]          | R[1]                               | G[5]          | _                           | Y[5]            | Y[3]            |                                                                     |

| DISPx_DAT14           | DAT[14]                     | R[3]          | R[2]                               | G[6]          | _                           | Y[6]            | Y[4]            | -                                                                   |

| DISPx_DAT15           | DAT[15]                     | R[4]          | R[3]                               | G[7]          |                             | Y[7]            | Y[5]            |                                                                     |

| DISPx_DAT16           | DAT[16]                     | _             | R[4]                               | R[0]          | _                           | —               | Y[6]            |                                                                     |

| DISPx_DAT17           | DAT[17]                     | _             | R[5]                               | R[1]          |                             |                 | Y[7]            |                                                                     |

| DISPx_DAT18           | DAT[18]                     | _             | _                                  | R[2]          |                             |                 | Y[8]            |                                                                     |

| DISPx_DAT19           | DAT[19]                     | _             | _                                  | R[3]          | _                           | —               | Y[9]            |                                                                     |

| DISPx_DAT20           | DAT[20]                     | _             |                                    | R[4]          | _                           | —               |                 |                                                                     |

| DISPx_DAT21           | DAT[21]                     | _             | _                                  | R[5]          |                             |                 |                 |                                                                     |

### Table 67. Video Signal Cross-Reference

| ID   | Parameter <sup>1,2</sup>      | All Freq | Unit |      |

|------|-------------------------------|----------|------|------|

|      |                               | Min      | Мах  | Onit |

| SJ9  | TMS, TDI data hold time       | 25       | _    | ns   |

| SJ10 | TCK low to TDO data valid     | —        | 44   | ns   |

| SJ11 | TCK low to TDO high impedance | —        | 44   | ns   |

| SJ12 | TRST assert time              | 100      | —    | ns   |

| SJ13 | TRST set-up time to TCK low   | 40       | _    | ns   |

### Table 75. JTAG Timing (continued)

<sup>1</sup>  $T_{DC}$  = target frequency of SJC

<sup>2</sup>  $V_{M}$  = mid-point voltage

## 4.11.17 SPDIF Timing Parameters

The Sony/Philips Digital Interconnect Format (SPDIF) data is sent using the bi-phase marking code. When encoding, the SPDIF data signal is modulated by a clock that is twice the bit rate of the data signal.

Table 76 and Figure 89 and Figure 90 show SPDIF timing parameters for the Sony/Philips Digital Interconnect Format (SPDIF), including the timing of the modulating Rx clock (SRCK) for SPDIF in Rx mode and the timing of the modulating Tx clock (STCLK) for SPDIF in Tx mode.

| Characteristics                                                                                                | Symbol  | Timing Para | Timing Parameter Range |        |  |

|----------------------------------------------------------------------------------------------------------------|---------|-------------|------------------------|--------|--|

| Characteristics                                                                                                |         | Min         | Max                    | - Unit |  |

| SPDIFIN Skew: asynchronous inputs, no specs apply                                                              | —       |             | 0.7                    | ns     |  |

| SPDIFOUT output (Load = 50pf) <ul> <li>Skew</li> <li>Transition rising</li> <li>Transition falling</li> </ul>  |         |             | 1.5<br>24.2<br>31.3    | ns     |  |

| SPDIFOUT1 output (Load = 30pf) <ul> <li>Skew</li> <li>Transition rising</li> <li>Transition falling</li> </ul> | <br>    |             | 1.5<br>13.6<br>18.0    | ns     |  |

| Modulating Rx clock (SRCK) period                                                                              | srckp   | 40.0        | —                      | ns     |  |

| SRCK high period                                                                                               | srckph  | 16.0        | —                      | ns     |  |

| SRCK low period                                                                                                | srckpl  | 16.0        | —                      | ns     |  |

| Modulating Tx clock (STCLK) period                                                                             | stclkp  | 40.0        | —                      | ns     |  |

| STCLK high period                                                                                              | stclkph | 16.0        | _                      | ns     |  |

| STCLK low period                                                                                               | stclkpl | 16.0        | —                      | ns     |  |

Table 76. SPDIF Timing Parameters

## 4.11.18.1 SSI Transmitter Timing with Internal Clock

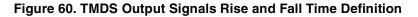

Figure 91 depicts the SSI transmitter internal clock timing and Table 78 lists the timing parameters for the SSI transmitter internal clock.

Note: SRXD input in synchronous mode only

### Figure 91. SSI Transmitter Internal Clock Timing Diagram

| ID   | Parameter                                      | Min  | Мах  | Unit |  |  |  |

|------|------------------------------------------------|------|------|------|--|--|--|

|      | Internal Clock Operation                       |      |      |      |  |  |  |

| SS1  | (Tx/Rx) CK clock period                        | 81.4 | —    | ns   |  |  |  |

| SS2  | (Tx/Rx) CK clock high period                   | 36.0 | _    | ns   |  |  |  |

| SS4  | (Tx/Rx) CK clock low period                    | 36.0 | _    | ns   |  |  |  |

| SS6  | (Tx) CK high to FS (bl) high                   | —    | 15.0 | ns   |  |  |  |

| SS8  | (Tx) CK high to FS (bl) low                    | —    | 15.0 | ns   |  |  |  |

| SS10 | (Tx) CK high to FS (wl) high                   | —    | 15.0 | ns   |  |  |  |

| SS12 | (Tx) CK high to FS (wl) low                    | —    | 15.0 | ns   |  |  |  |

| SS14 | (Tx/Rx) Internal FS rise time                  | —    | 6.0  | ns   |  |  |  |

| SS15 | (Tx/Rx) Internal FS fall time                  | —    | 6.0  | ns   |  |  |  |

| SS16 | (Tx) CK high to STXD valid from high impedance | —    | 15.0 | ns   |  |  |  |

| SS17 | (Tx) CK high to STXD high/low                  | —    | 15.0 | ns   |  |  |  |

| SS18 | (Tx) CK high to STXD high impedance            | —    | 15.0 | ns   |  |  |  |

#### Table 78. SSI Transmitter Timing with Internal Clock

| ID   | Parameter                      | Min   | Мах | Unit |

|------|--------------------------------|-------|-----|------|

| SS47 | Oversampling clock period      | 15.04 | _   | ns   |

| SS48 | Oversampling clock high period | 6.0   | _   | ns   |

| SS49 | Oversampling clock rise time   | _     | 3.0 | ns   |

| SS50 | Oversampling clock low period  | 6.0   | _   | ns   |

| SS51 | Oversampling clock fall time   | _     | 3.0 | ns   |

Table 79. SSI Receiver Timing with Internal Clock (continued)

### NOTE

- All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal STCK/SRCK and/or the frame sync STFS/SRFS shown in the tables and in the figures.

- All timings are on Audiomux Pads when SSI is being used for data transfer.

- "Tx" and "Rx" refer to the Transmit and Receive sections of the SSI.

- The terms, WL and BL, refer to Word Length (WL) and Bit Length (BL).

- For internal Frame Sync operation using external clock, the FS timing is same as that of Tx Data (for example, during AC97 mode of operation).

| ID   | Parameter                            | Min  | Max  | Unit |

|------|--------------------------------------|------|------|------|

| SS39 | (Tx) CK high to STXD high impedance  | —    | 15.0 | ns   |

|      | Synchronous External Clock Operation |      |      |      |

| SS44 | SRXD setup before (Tx) CK falling    | 10.0 | —    | ns   |

| SS45 | SRXD hold after (Tx) CK falling      | 2.0  | _    | ns   |

| SS46 | SRXD rise/fall time                  | _    | 6.0  | ns   |

### Table 80. SSI Transmitter Timing with External Clock (continued)

### NOTE

- All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal STCK/SRCK and/or the frame sync STFS/SRFS shown in the tables and in the figures.

- All timings are on Audiomux Pads when SSI is being used for data transfer.

- "Tx" and "Rx" refer to the Transmit and Receive sections of the SSI.

- The terms WL and BL refer to Word Length (WL) and Bit Length (BL).

- For internal Frame Sync operation using external clock, the FS timing is same as that of Tx Data (for example, during AC97 mode of operation).

### NOTE

- All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal STCK/SRCK and/or the frame sync STFS/SRFS shown in the tables and in the figures.

- All timings are on Audiomux Pads when SSI is being used for data transfer.

- "Tx" and "Rx" refer to the Transmit and Receive sections of the SSI.

- The terms, WL and BL, refer to Word Length (WL) and Bit Length (BL).

- For internal Frame Sync operation using external clock, the FS timing is same as that of Tx Data (for example, during AC97 mode of operation).

# 4.11.19 UART I/O Configuration and Timing Parameters

## 4.11.19.1 UART RS-232 I/O Configuration in Different Modes

The i.MX 6Solo/6DualLite UART interfaces can serve both as DTE or DCE device. This can be configured by the DCEDTE control bit (default 0 — DCE mode). Table 82 shows the UART I/O configuration based on the enabled mode.

| Port    | DTE Mode  |                             | DCE Mode  |                             |  |

|---------|-----------|-----------------------------|-----------|-----------------------------|--|

| Pon     | Direction | Description                 | Direction | Description                 |  |

| RTS     | Output    | RTS from DTE to DCE         | Input     | RTS from DTE to DCE         |  |

| CTS     | Input     | CTS from DCE to DTE         | Output    | CTS from DCE to DTE         |  |

| DTR     | Output    | DTR from DTE to DCE         | Input     | DTR from DTE to DCE         |  |

| DSR     | Input     | DSR from DCE to DTE         | Output    | DSR from DCE to DTE         |  |

| DCD     | Input     | DCD from DCE to DTE         | Output    | DCD from DCE to DTE         |  |

| RI      | Input     | RING from DCE to DTE        | Output    | RING from DCE to DTE        |  |

| TXD_MUX | Input     | Serial data from DCE to DTE | Output    | Serial data from DCE to DTE |  |

| RXD_MUX | Output    | Serial data from DTE to DCE | Input     | Serial data from DTE to DCE |  |

Table 82. UART I/O Configuration vs. Mode

## 4.11.19.2 UART RS-232 Serial Mode Timing

The following sections describe the electrical information of the UART module in the RS-232 mode.

NOTES:

1. ALL DIMENSIONS IN MILLIMETERS.

2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

$\$  MAXIMUM SOLDER BALL DIAMETER MEASURED PARALLEL TO DATUM A.

DATUM A, THE SEATING PLANE, IS DETERMINED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS.

$\label{eq:parallelism}$  measurement shall exclude any effect of mark on top surface of package.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OU | TLINE   | PRINT VERSION NO   | T TO SCALE  |

|---------------------------------------------------------|---------------|---------|--------------------|-------------|

| TITLE: PBGA, LOW PRO                                    | FILE,         | DOCUME  | NT NO: 98ASA00404D | REV: O      |

| FINE PITCH, 624                                         | , .           | CASE NU | JMBER: 2240-01     | 27 SEP 2011 |

| 21 X 21 PKG, 0.8 MM F                                   | РІТСН (МАР)   | STANDAF | RD: NON-JEDEC      |             |

#### Figure 101. 21 x 21 mm BGA, Case 2240 Package Top, Bottom, and Side Views

### Package Information and Contact Assignments

| Supply Rail Name | Ball(s) Position(s)                                                            | Remark                                                                                                                        |

|------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| PCIE_REXT        | A2                                                                             |                                                                                                                               |

| PCIE_VP          | Н7                                                                             |                                                                                                                               |

| PCIE_VPH         | G7                                                                             | PCI PHY supply                                                                                                                |

| PCIE_VPTX        | G8                                                                             | PCI PHY supply                                                                                                                |

| VDD_SNVS_CAP     | G9                                                                             | Secondary supply for the SNVS (internal regulator output—requires capacitor if internal regulator is used)                    |

| VDD_SNVS_IN      | G11                                                                            | Primary supply for the SNVS regulator                                                                                         |

| VDDARM_CAP       | H11, H13, J11, J13, K11, K13, L11, L13, M11, M13, N11, N13, P11, P13, R11, R13 | Secondary supply for core (internal regulator<br>output—requires capacitor if internal regulator<br>is used)                  |

| VDDARM_IN        | H14, J14, K9, K14, L9, L14, M9, M14, N9, N14, P9, P14, R9, R14, T9, U9         | Primary supply for the ARM core's regulator                                                                                   |

| VDDHIGH_CAP      | H10, J10                                                                       | Secondary supply for the 2.5 V domain<br>(internal regulator output—requires capacitor<br>if internal regulator is used)      |

| VDDHIGH_IN       | H9, J9                                                                         | Primary supply for the 2.5 V regulator                                                                                        |

| VDDPU_CAP        | H17, J17, K17, L17, M17, N17, P17                                              | Secondary supply for VPU and GPUs<br>(internal regulator output—requires capacitor<br>if internal regulator is used)          |

| VDDSOC_CAP       | R10, T10, T13, T14, U10, U13, U14                                              | Secondary supply for SoC and PU regulators<br>(internal regulator output—requires capacitor<br>if internal regulator is used) |

| VDDSOC_IN        | H16, J16, K16, L16, M16, N16, P16, R16, T16, U16                               | Primary supply for SoC and PU regulators                                                                                      |

| VDDUSB_CAP       | F9                                                                             | Secondary supply for the 3 V Domain (internal regulator output—requires capacitor if internal regulator is used)              |

| USB_H1_VBUS      | D10                                                                            | Primary supply for the 3 V regulator                                                                                          |

| USB_OTG_VBUS     | E9                                                                             | Primary supply for the 3 V regulator                                                                                          |

| HDMI_DDCCEC      | K2                                                                             | Analog Ground(Ground reference for the Hot Plug Detect signal)                                                                |

| FA_ANA           | A5                                                                             |                                                                                                                               |

| GPANAIO          | C8                                                                             |                                                                                                                               |

| VDD_FA           | В5                                                                             |                                                                                                                               |

| ZQPAD            | AE17                                                                           |                                                                                                                               |

| NC               | C14                                                                            |                                                                                                                               |

| NC               | G12                                                                            |                                                                                                                               |

### Table 91. 21 x 21 mm Supplies Contact Assignments (continued)

### Package Information and Contact Assignments

| ۲           | 8           | >            | 5           | F           | æ           | ٩            | z            |

|-------------|-------------|--------------|-------------|-------------|-------------|--------------|--------------|

| LVDS1_TX0_N | LVDS0_TX3_P | LVDS0_TX2_P  | LVDS0_TX0_P | GPI0_2      | GPI0_17     | CSI0_PIXCLK  | CSI0_DAT4    |

| LVDS1_TX0_P | LVDS0_TX3_N | LVDS0_TX2_N  | LVDS0_TX0_N | GPIO_9      | GPIO_16     | CSI0_DAT5    | CSI0_VSYNC   |

| LVDS1_CLK_N | GND         | LVDS0_CLK_P  | LVDS0_TX1_P | GPIO_6      | GPIO_7      | CSI0_DATA_EN | CSI0_DAT7    |

| LVDS1_CLK_P | KEY_ROW2    | LVDS0_CLK_N  | LVDS0_TX1_N | GPI0_1      | GPIO_5      | CSI0_MCLK    | CSI0_DAT6    |

| GND         | KEY_COL0    | KEY_ROW4     | KEY_COL3    | GPIO_0      | GPIO_8      | GPIO_19      | CSI0_DAT9    |

| DRAM_RESET  | KEY_COL2    | KEY_ROW0     | KEY_ROW1    | KEY_COL4    | GPIO_4      | GPIO_18      | CSI0_DAT8    |

| DRAM_D20    | GND         | NVCC_LVDS2P5 | KEY_COL1    | KEY_ROW3    | GPIO_3      | NVCC_GPIO    | NVCC_CSI     |

| DRAM_D21    | GND         | GND          | GND         | GND         | GND         | GND          | GND          |

| DRAM_D19    | GND         | NVCC_DRAM    | VDDARM_IN   | VDDARM_IN   | VDDARM_IN   | VDDARM_IN    | VDDARM_IN    |

| DRAM_D25    | GND         | NVCC_DRAM    | VDDSOC_CAP  | VDDSOC_CAP  | VDDSOC_CAP  | GND          | GND          |

| DRAM_SDCKE0 | GND         | NVCC_DRAM    | GND         | GND         | VDDARM_CAP  | VDDARM_CAP   | VDDARM_CAP   |

| DRAM_A15    | GND         | NVCC_DRAM    | GND         | GND         | GND         | GND          | NC           |

| DRAM_A7     | GND         | NVCC_DRAM    | VDDSOC_CAP  | VDDSOC_CAP  | VDDARM_CAP  | VDDARM_CAP   | VDDARM_CAP   |

| DRAM_A3     | DRAM_A4     | NVCC_DRAM    | VDDSOC_CAP  | VDDSOC_CAP  | VDDARM_IN   | VDDARM_IN    | VDDARM_IN    |

| DRAM_SDBA1  | GND         | NVCC_DRAM    | GND         | GND         | GND         | GND          | GND          |

| DRAM_CS0    | GND         | NVCC_DRAM    | VDDSOC_IN   | VDDSOC_IN   | VDDSOC_IN   | VDDSOC_IN    | VDDSOC_IN    |

| DRAM_D36    | GND         | NVCC_DRAM    | GND         | GND         | GND         | VDDPU_CAP    | VDDPU_CAP    |

| DRAM_D37    | GND         | NVCC_DRAM    | NVCC_DRAM   | NVCC_DRAM   | NVCC_DRAM   | GND          | GND          |

| DRAM_D40    | GND         | GND          | GND         | GND         | NVCC_ENET   | NVCC_LCD     | DI0_DISP_CLK |

| DRAM_D44    | ENET_TXD1   | ENET_MDC     | ENET_TXD0   | DISP0_DAT21 | DISP0_DAT13 | DISP0_DAT4   | DI0_PIN3     |

| DRAM_DQM7   | ENET_RXD0   | ENET_TX_EN   | ENET_CRS_DV | DISP0_DAT16 | DISP0_DAT10 | DISP0_DAT3   | DI0_PIN15    |

| DRAM_D59    | ENET_RXD1   | ENET_REF_CLK | DISP0_DAT20 | DISP0_DAT15 | DISP0_DAT8  | DISP0_DAT1   | EIM_BCLK     |

| DRAM_D62    | ENET_RX_ER  | ENET_MDIO    | DISP0_DAT19 | DISP0_DAT11 | DISP0_DAT6  | DISP0_DAT2   | EIM_DA14     |

| GND         | DISP0_DAT23 | DISP0_DAT22  | DISP0_DAT17 | DISP0_DAT12 | DISP0_DAT7  | DISP0_DAT0   | EIM_DA15     |

| DRAM_D58    | DRAM_D63    | DISP0_DAT18  | DISP0_DAT14 | DISP0_DAT9  | DISP0_DAT5  | DI0_PIN4     | DI0_PIN2     |

| ٨           | M           | >            | D           | F           | æ           | ٩            | z            |

### Table 94. 21 x 21 mm, 0.8 mm Pitch Ball Map (continued)