Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                            |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Not For New Designs                                                                                                 |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 2 Core, 32-Bit                                                                                                      |

| Speed                              | 1.0GHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON™ SIMD                                                                                              |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | -                                                                                                                   |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | -20°C ~ 105°C (TJ)                                                                                                  |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-LFBGA                                                                                                           |

| Supplier Device Package            | 624-MAPBGA (21x21)                                                                                                  |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6u5evm10abr                                            |

#### Introduction

- Color eReaders

- IPTV

- Human Machine Interfaces (HMI)

- Portable medical

- IP phones

- Home energy management systems

The i.MX 6Solo/6DualLite processors have some very exciting features, for example:

- Applications processors—The processors enhance the capabilities of high-tier portable

applications by fulfilling the ever increasing MIPS needs of operating systems and games.

Freescale's Dynamic Voltage and Frequency Scaling (DVFS) provides significant power reduction,

allowing the device to run at lower voltage and frequency with sufficient MIPS for tasks, such as

audio decode.

- Multilevel memory system—The multilevel memory system of each processor is based on the L1 instruction and data caches, L2 cache, and internal and external memory. The processors support many types of external memory devices, including DDR3, low voltage DDR3, LPDDR2, NOR Flash, PSRAM, cellular RAM, NAND Flash (MLC and SLC), OneNAND<sup>TM</sup>, and managed NAND, including eMMC up to rev 4.4.

- Smart speed technology—The processors have power management throughout the IC that enables the rich suite of multimedia features and peripherals to consume minimum power in both active and various low power modes. Smart speed technology enables the designer to deliver a feature-rich product, requiring levels of power far lower than industry expectations.

- Dynamic voltage and frequency scaling—The processors improve the power efficiency of devices by scaling the voltage and frequency to optimize performance.

- Multimedia powerhouse—The multimedia performance of each processor is enhanced by a

multilevel cache system, Neon MPE (Media Processor Engine) co-processor, a multi-standard

hardware video codec, an image processing unit (IPU), and a programmable smart DMA (SDMA)

controller.

- Powerful graphics acceleration—Each processor provides two independent, integrated graphics processing units: an OpenGL<sup>®</sup> ES 2.0 3D graphics accelerator with a shader and a 2D graphics accelerator.

- Interface flexibility—Each processor supports connections to a variety of interfaces: LCD controller for up to two displays (including parallel display, HDMI1.4, MIPI display, and LVDS display), dual CMOS sensor interface (parallel or through MIPI), high-speed USB on-the-go with PHY, high-speed USB host with PHY, multiple expansion card ports (high-speed MMC/SDIO host and other), 10/100/1000 Mbps Gigabit Ethernet controller, and a variety of other popular interfaces (such as UART, I<sup>2</sup>C, and I<sup>2</sup>S serial audio, and PCIe-II).

- Eink Panel Display Controller—The processors integrate EPD controller that supports E-INK color and monochrome with up to 1650x2332 resolution and 5-bit grayscale (32-levels per color channel).

- Advanced security—The processors deliver hardware-enabled security features that enable secure e-commerce, digital rights management (DRM), information encryption, secure boot, and secure

#### Introduction

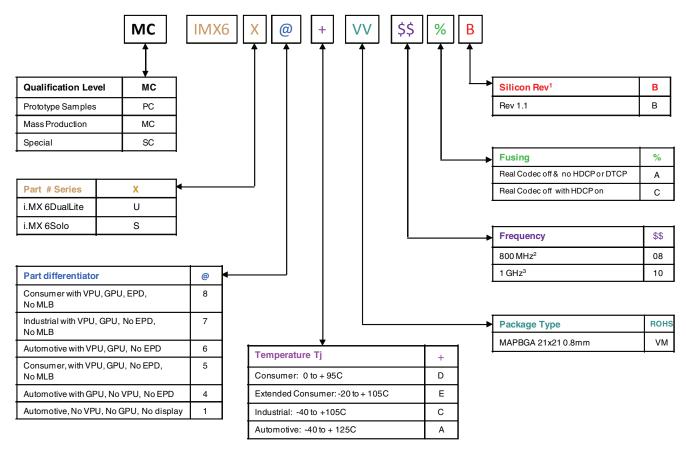

- 1. See the freescale.com\imx6series Web page for latest information on the available silicon revision.

- 2. If a 24 MHz input clock is used (required for USB), the maximum SoC speed is limited to 792 MHz.

- 3. If a 24 MHz input clock is used (required for USB), the maximum SoC speed is limited to 996 MHz.

Figure 1. Part Number Nomenclature—i.MX 6DualLite and 6Solo

## 1.2 Features

The i.MX 6Solo/6DualLite processors are based on ARM Cortex-A9 MPCore<sup>TM</sup> Platform, which has the following features:

- The i.MX 6Solo supports single ARM Cortex-A9 MPCore (with TrustZone)

- The i.MX 6DualLite supports dual ARM Cortex-A9 MPCore (with TrustZone)

- The core configuration is symmetric, where each core includes:

- 32 KByte L1 Instruction Cache

- 32 KByte L1 Data Cache

- Private Timer and Watchdog

- Cortex-A9 NEON MPE (Media Processing Engine) Co-processor

The ARM Cortex-A9 MPCore complex includes:

- General Interrupt Controller (GIC) with 128 interrupt support

- Global Timer

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 1

#### NOTE

The actual feature set depends on the part numbers as described in Table 1, "Orderable Part Numbers," on page 3. Functions, such as video hardware acceleration, and 2D and 3D hardware graphics acceleration may not be enabled for specific part numbers.

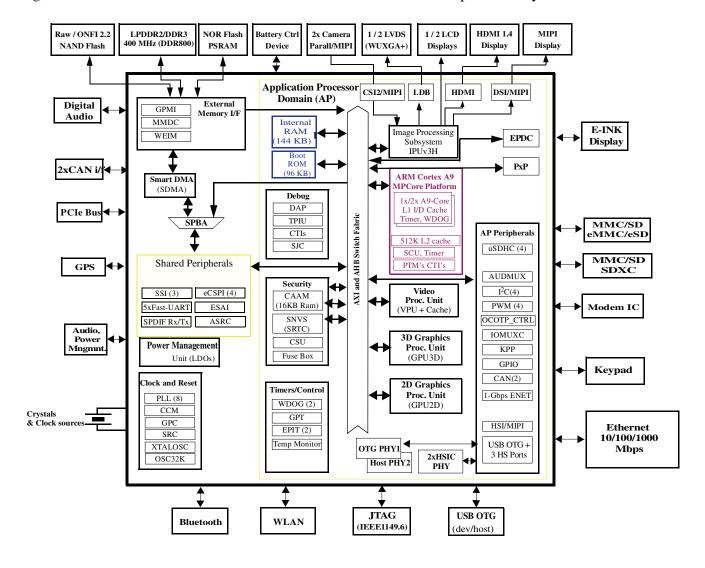

## 2 Architectural Overview

The following subsections provide an architectural overview of the i.MX 6Solo/6DualLite processor system.

## 2.1 Block Diagram

Figure 2 shows the functional modules in the i.MX 6Solo/6DualLite processor system.

<sup>1 144</sup> KB RAM including 16 KB RAM inside the CAAM.

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 1

**Electrical Characteristics**

## 4 Electrical Characteristics

This section provides the device and module-level electrical characteristics for the i.MX 6Solo/6DualLite processors.

# 4.1 Chip-Level Conditions

This section provides the device-level electrical characteristics for the IC. See Table 6 for a quick reference to the individual tables and sections.

Table 6. i.MX 6Solo/6DualLite Chip-Level Conditions

| For these characteristics,               | Topic appears |

|------------------------------------------|---------------|

| Absolute Maximum Ratings                 | on page 22    |

| BGA Case 2240 Package Thermal Resistance | on page 23    |

| Operating Ranges                         | on page 24    |

| External Clock Sources                   | on page 26    |

| Maximal Supply Currents                  | on page 27    |

| Low Power Mode Supply Currents           | on page 29    |

| USB PHY Current Consumption              | on page 30    |

| PCIe 2.0 Power Consumption               | on page 30    |

# 4.1.1 Absolute Maximum Ratings

**Table 7. Absolute Maximum Ratings**

| Parameter Description                                              | Symbol                                | Min  | Max                    | Unit |

|--------------------------------------------------------------------|---------------------------------------|------|------------------------|------|

| Core supply voltages                                               | VDDARM_IN<br>VDDSOC_IN                | -0.3 | 1.5                    | V    |

| Internal supply voltages                                           | VDDARM_CAP<br>VDDSOC_CAP<br>VDDPU_CAP | -0.3 | 1.3                    | V    |

| GPIO supply voltage                                                | Supplies denoted as I/O supply        | -0.5 | 3.6                    | V    |

| DDR I/O supply voltage                                             | Supplies denoted as I/O supply        | -0.4 | 1.975                  | V    |

| LVDS I/O supply voltage                                            | Supplies denoted as I/O supply        | -0.3 | 2.8                    | V    |

| VDD_SNVS_IN supply voltage                                         | VDD_SNVS_IN                           | -0.3 | 3.3                    | V    |

| VDDHIGH_IN supply voltage                                          | VDDHIGH_IN                            | -0.3 | 3.6                    | V    |

| USB VBUS                                                           | VBUS                                  | _    | 5.25                   | V    |

| Input voltage on USB_OTG_DP, USB_OTG_DN, USB_H1_DP, USB_H1_DN pins | USB_DP/USB_DN                         | -0.3 | 3.63                   | V    |

| Input/output voltage range                                         | V <sub>in</sub> /V <sub>out</sub>     | -0.5 | OVDD <sup>1</sup> +0.3 | V    |

The typical values shown in Table 11 are required for use with Freescale BSPs to ensure precise time keeping and USB operation. For RTC\_XTAL operation, two clock sources are available.

On-chip 40 kHz ring oscillator—this clock source has the following characteristics:

Approximately 25 µA more Idd than crystal oscillator

Approximately ±50% tolerance

No external component required

Starts up quicker than 32 kHz crystal oscillator

External crystal oscillator with on-chip support circuit:

At power up, ring oscillator is utilized. After crystal oscillator is stable, the clock circuit switches over to the crystal oscillator automatically.

Higher accuracy than ring oscillator

If no external crystal is present, then the ring oscillator is utilized

The decision of choosing a clock source should be taken based on real-time clock use and precision timeout.

## 4.1.5 Maximal Supply Currents

The Power Virus numbers shown in Table 12 represent a use case designed specifically to show the maximum current consumption possible. All cores are running at the defined maximum frequency and are limited to L1 cache accesses only to ensure no pipeline stalls. Although a valid condition, it would have a very limited practical use case, if at all, and be limited to an extremely low duty cycle unless the intention was to specifically show the worst case power consumption.

The MMPF0100xxxx, Freescale's power management IC targeted for the i.MX 6x family, supports the Power Virus mode operating at 1% duty cycle. Higher duty cycles are allowed, but a robust thermal design is required for the increased system power dissipation.

See the i.MX 6Solo/6DualLite Power Consumption Measurement Application Note (AN4576) for more details on typical power consumption under various use case definitions.

| Power Line                         | Conditions                                             | Max Current      | Unit |  |  |  |  |  |

|------------------------------------|--------------------------------------------------------|------------------|------|--|--|--|--|--|

| VDDARM_IN                          | 996 MHz ARM clock<br>based on Power Virus<br>operation | 2200             | mA   |  |  |  |  |  |

| VDDSOC_IN                          | 996 MHz ARM clock                                      | 1260             | mA   |  |  |  |  |  |

| VDDHIGH_IN                         |                                                        | 125 <sup>1</sup> | mA   |  |  |  |  |  |

| VDD_SNVS_IN                        |                                                        | 275 <sup>2</sup> | μΑ   |  |  |  |  |  |

| USB_OTG_VBUS/USB_H1_VBUS (LDO 3P0) |                                                        | 25 <sup>3</sup>  | mA   |  |  |  |  |  |

| Primary Interface (IO) Supplies    |                                                        |                  |      |  |  |  |  |  |

**Table 12. Maximal Supply Currents**

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 1

<sup>&</sup>lt;sup>4</sup> External oscillator or a fundamental frequency crystal with internal oscillator amplifier.

their input supply ripple rejection and their on-die trimming. This translates into more stable voltage for the on-chip logics.

These regulators have three basic modes:

- Bypass. The regulation FET is switched fully on passing the external voltage, to the load unaltered. The analog part of the regulator is powered down in this state, removing any loss other than the IR drop through the power grid and FET.

- Power Gate. The regulation FET is switched fully off limiting the current draw from the supply. The analog part of the regulator is powered down here limiting the power consumption.

- Analog regulation mode. The regulation FET is controlled such that the output voltage of the regulator equals the programmed target voltage. The target voltage is fully programmable in 25 mV steps.

For additional information, see the i.MX 6Solo/6DualLite reference manual.

## 4.3.2 Analog Regulators

#### 4.3.2.1 LDO 1P1

The LDO\_1P1 regulator implements a programmable linear-regulator function from VDDHIGH\_IN (see Table 9 for minimum and maximum input requirements). Typical Programming Operating Range is 1.0 V to 1.2 V with the nominal default setting as 1.1 V. Since the accuracy or the % regulation is not tested, and only tested with the LDO set to either 1.0V or 1.2V, this is the only range that is guaranteed. The regulator has been designed to be stable with a minimum external low ESR decoupling capacitor of 1  $\mu F$  (2.2  $\mu F$  should be considered the recommended minimum value for component selection), though the actual capacitance required should be determined by the application. A programmable brown-out detector is included in the regulator that can be used by the system to determine when the load capability of the regulator is being exceeded to take the necessary steps. Current-limiting can be enabled to allow for in-rush current requirements during start-up, if needed. Active-pull-down can also be enabled for systems requiring this feature.

For additional information, see the i.MX 6Solo/6DualLite reference manual.

#### 4.3.2.2 LDO 2P5

The LDO\_2P5 module implements a programmable linear-regulator function from VDDHIGH\_IN (see Table 9 for minimum and maximum input requirements). Typical Programming Operating Range is 2.25 V to 2.75 V with the nominal default setting as 2.5 V. Since the accuracy or the % regulation is not tested, and only tested with the LDO set to either 2.25V or 2.75V, this is the only range that is guaranteed. The regulator has been designed to be stable with a minimum external low ESR decoupling capacitor of 1  $\mu$ F (2.2  $\mu$ F should be considered the recommended minimum value for component selection), though the actual capacitance required should be determined by the application. A programmable brown-out detector is included in the regulator that can be used by the system to determine when the load capability of the regulator is being exceeded, to take the necessary steps. Current-limiting can be enabled to allow for in-rush current requirements during start-up, if needed. Active-pull-down can also be enabled for systems requiring this feature. An alternate self-biased low-precision weak-regulator is included that can be

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 1

## 4.7.2 DDR I/O AC Parameters

The LPDDR2 interface mode fully complies with JESD209-2B LPDDR2 JEDEC standard release June, 2009. The DDR3/DDR3L interface mode fully complies with JESD79-3D DDR3 JEDEC standard release April, 2008.

Table 29 shows the AC parameters for DDR I/O operating in LPDDR2 mode.

Table 29. DDR I/O LPDDR2 Mode AC Parameters<sup>1</sup>

| Parameter                                                 | Symbol           | Test Condition                                                            | Min         | Max         | Unit |

|-----------------------------------------------------------|------------------|---------------------------------------------------------------------------|-------------|-------------|------|

| AC input logic high                                       | Vih(ac)          | _                                                                         | Vref + 0.22 | OVDD        | V    |

| AC input logic low                                        | Vil(ac)          | _                                                                         | 0           | Vref - 0.22 | V    |

| AC differential input high voltage <sup>2</sup>           | Vidh(ac)         | _                                                                         | 0.44        | _           | V    |

| AC differential input low voltage                         | Vidl(ac)         | _                                                                         | _           | 0.44        | ٧    |

| Input AC differential cross point voltage <sup>3</sup>    | Vix(ac)          | Relative to Vref                                                          | -0.12       | 0.12        | V    |

| Over/undershoot peak                                      | Vpeak            | _                                                                         | _           | 0.35        | V    |

| Over/undershoot area (above OVDD or below OVSS)           | Varea            | 400 MHz                                                                   | _           | 0.3         | V-ns |

| Single output slew rate, measured between                 | tsr              | 50 $\Omega$ to Vref.<br>5 pF load.<br>Drive impedance = 40 $\Omega$ ± 30% | 1.5         | 3.5         | V/ns |

| Vol(ac) and Voh(ac)                                       |                  | 50 $\Omega$ to Vref.<br>5pF load.Drive<br>impedance = 60 $\Omega$ ± 30%   | 1           | 2.5         |      |

| Skew between pad rise/fall asymmetry + skew caused by SSN | t <sub>SKD</sub> | clk = 400 MHz                                                             | _           | 0.1         | ns   |

<sup>&</sup>lt;sup>1</sup> Note that the JEDEC LPDDR2 specification (JESD209\_2B) supersedes any specification in this document.

Table 30 shows the AC parameters for DDR I/O operating in DDR3/DDR3L mode.

Table 30. DDR I/O DDR3/DDR3L Mode AC Parameters<sup>1</sup>

| Parameter                                              | Symbol  | Test Condition   | Min          | Тур | Max          | Unit |

|--------------------------------------------------------|---------|------------------|--------------|-----|--------------|------|

| AC input logic high                                    | Vih(ac) | _                | Vref + 0.175 | _   | OVDD         | V    |

| AC input logic low                                     | Vil(ac) | _                | 0            | _   | Vref - 0.175 | V    |

| AC differential input voltage <sup>2</sup>             | Vid(ac) | _                | 0.35         | _   | _            | V    |

| Input AC differential cross point voltage <sup>3</sup> | Vix(ac) | Relative to Vref | Vref - 0.15  | _   | Vref + 0.15  | V    |

| Over/undershoot peak                                   | Vpeak   | _                | _            | _   | 0.4          | V    |

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 1

<sup>&</sup>lt;sup>2</sup> Vid(ac) specifies the input differential voltage | Vtr - Vcp | required for switching, where Vtr is the "true" input signal and Vcp is the "complementary" input signal. The Minimum value is equal to Vih(ac) - Vil(ac).

The typical value of Vix(ac) is expected to be about 0.5 x OVDD. and Vix(ac) is expected to track variation of OVDD. Vix(ac) indicates the voltage at which differential input signal must cross.

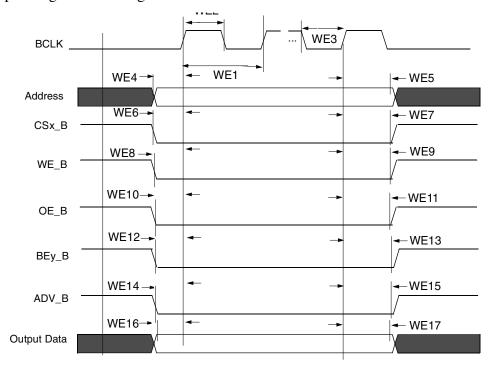

## 4.9.3.3 General EIM Timing-Synchronous Mode

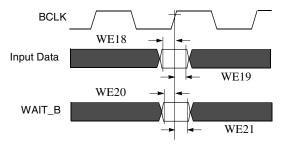

Figure 10, Figure 11, and Table 39 specify the timings related to the EIM module. All EIM output control signals may be asserted and deasserted by an internal clock synchronized to the BCLK rising edge according to corresponding assertion/negation control fields.

Figure 10. EIM Outputs Timing Diagram

Figure 11. EIM Inputs Timing Diagram

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 1

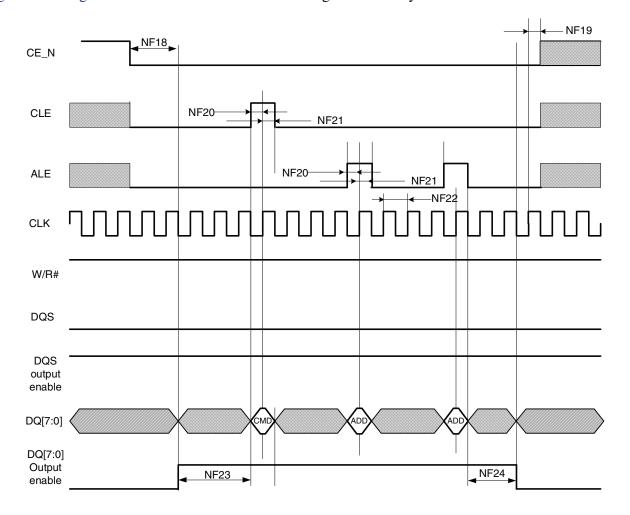

# 4.10.2 Source Synchronous Mode AC Timing (ONFI 2.x Compatible)

Figure 32 to Figure 34 show the write and read timing of Source Synchronous Mode.

Figure 32. Source Synchronous Mode Command and Address Timing Diagram

Table 52. Enhanced Serial Audio Interface (ESAI) Timing (continued)

| No. | Characteristics <sup>1,2</sup>                                      | Symbol | Expression <sup>2</sup> | Min         | Max          | Condition <sup>3</sup> | Unit |

|-----|---------------------------------------------------------------------|--------|-------------------------|-------------|--------------|------------------------|------|

| 81  | SCKT rising edge to FST out (wr) low <sup>5</sup>                   |        | _<br>_                  | _           | 22.0<br>12.0 | x ck<br>i ck           | ns   |

| 82  | SCKT rising edge to FST out (wl) high                               | _      | _                       | _           | 19.0<br>9.0  | x ck<br>i ck           | ns   |

| 83  | SCKT rising edge to FST out (wl) low                                | _      | _                       | _           | 20.0<br>10.0 | x ck<br>i ck           | ns   |

| 84  | SCKT rising edge to data out enable from high impedance             | _      |                         | _           | 22.0<br>17.0 | x ck<br>i ck           | ns   |

| 86  | SCKT rising edge to data out valid                                  | _      | _                       | _           | 18.0<br>13.0 | x ck<br>i ck           | ns   |

| 87  | SCKT rising edge to data out high impedance <sup>67</sup>           | _      |                         | _           | 21.0<br>16.0 | x ck<br>i ck           | ns   |

| 89  | FST input (bl, wr) setup time before SCKT falling edge <sup>5</sup> |        | _<br>_                  | 2.0<br>18.0 | _            | x ck<br>i ck           | ns   |

| 90  | FST input (wl) setup time before SCKT falling edge                  | _      | _                       | 2.0<br>18.0 | _            | x ck<br>i ck           | ns   |

| 91  | FST input hold time after SCKT falling edge                         | _      | _                       | 4.0<br>5.0  | _            | x ck<br>i ck           | ns   |

| 95  | HCKR/HCKT clock cycle                                               | _      | 2 x T <sub>C</sub>      | 15          | _            | _                      | ns   |

| 96  | HCKT input rising edge to SCKT output                               | _      | _                       | _           | 18.0         | _                      | ns   |

| 97  | HCKR input rising edge to SCKR output                               | _      | _                       | _           | 18.0         | _                      | ns   |

<sup>&</sup>lt;sup>1</sup> i ck = internal clock

(asynchronous implies that SCKT and SCKR are two different clocks)

i ck s = internal clock, synchronous mode

(synchronous implies that SCKT and SCKR are the same clock)

<sup>2</sup> bl = bit length

wl = word length

wr = word length relative

SCKT(SCKT pin) = transmit clock

SCKR(SCKR pin) = receive clock

FST(FST pin) = transmit frame sync FSR(FSR pin) = receive frame sync

HCKT(HCKT pin) = transmit high frequency clock

HCKR(HCKR pin) = receive high frequency clock

- <sup>4</sup> For the internal clock, the external clock cycle is defined by Icyc and the ESAI control register.

- <sup>5</sup> The word-relative frame sync signal waveform relative to the clock operates in the same manner as the bit-length frame sync signal waveform, but it spreads from one serial clock before the first bit clock (like the bit length frame sync signal), until the second-to-last bit clock of the first word in the frame.

- <sup>6</sup> Periodically sampled and not 100% tested.

x ck = external clock

i ck a = internal clock, asynchronous mode

#### **NOTE**

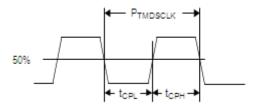

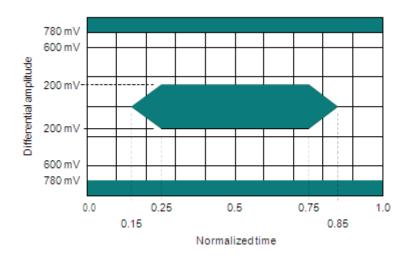

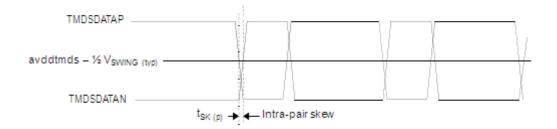

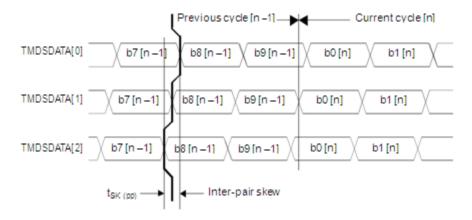

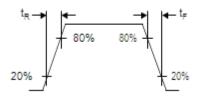

All dynamic parameters related to the TMDS line drivers' performance imply the use of assembly guidelines.

Figure 56. TMDS Clock Signal Definitions

Figure 57. Eye Diagram Mask Definition for HDMI Driver Signal Specification at TP1

Figure 58. Intra-Pair Skew Definition

Figure 59. Inter-Pair Skew Definition

Figure 60. TMDS Output Signals Rise and Fall Time Definition

| Symbol           | Parameter                   | Conditions                                                                                                                             | Min. | Тур. | Max. | Unit            |  |  |  |  |  |

|------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-----------------|--|--|--|--|--|

|                  | TMDS Drivers Specifications |                                                                                                                                        |      |      |      |                 |  |  |  |  |  |

| _                | Maximum serial data rate    | _                                                                                                                                      | _    | _    | 3.4  | Gbps            |  |  |  |  |  |

| F<br>TMDSCLK     | TMDSCLK frequency           | On TMDSCLKP/N outputs                                                                                                                  | 25   | _    | 340  | MHz             |  |  |  |  |  |

| PTMDSCLK         | TMDSCLK period              | RL = $50 \Omega$<br>See Figure 56.                                                                                                     | 2.94 | _    | 40   | ns              |  |  |  |  |  |

| <sup>t</sup> CDC | TMDSCLK duty cycle          | $\begin{array}{c} t = t / P \\ \text{CDC}  \text{CPH}  \text{TMDSCLK} \\ \text{RL} = 50 \ \Omega \\ \text{See Figure 56}. \end{array}$ | 40   | 50   | 60   | %               |  |  |  |  |  |

| t<br>CPH         | TMDSCLK high time           | RL = $50 \Omega$<br>See Figure 56.                                                                                                     | 4    | 5    | 6    | UI <sup>1</sup> |  |  |  |  |  |

| t<br>CPL         | TMDSCLK low time            | RL = $50 \Omega$<br>See Figure $56$ .                                                                                                  | 4    | 5    | 6    | UI <sup>1</sup> |  |  |  |  |  |

| _                | TMDSCLK jitter <sup>2</sup> | RL = 50 Ω                                                                                                                              | _    | _    | 0.25 | UI <sup>1</sup> |  |  |  |  |  |

| t<br>SK(p)       | Intra-pair (pulse) skew     | RL = $50 \Omega$<br>See Figure $58$ .                                                                                                  | _    | _    | 0.15 | UI <sup>1</sup> |  |  |  |  |  |

**Table 63. Switching Characteristics**

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 1

| Table 64. I <sup>2</sup> C Module Ti | ming Parameters ( | (continued) | ) |

|--------------------------------------|-------------------|-------------|---|

|--------------------------------------|-------------------|-------------|---|

| ID   | Parameter                                           | Standa | ard Mode | Fast Mod          | Unit |    |

|------|-----------------------------------------------------|--------|----------|-------------------|------|----|

|      |                                                     | Min    | Max      | Min               | Max  |    |

| IC8  | Data set-up time                                    | 250    | _        | 100 <sup>3</sup>  | _    | ns |

| IC9  | Bus free time between a STOP and START condition    | 4.7    | _        | 1.3               | _    | μs |

| IC10 | Rise time of both I2DAT and I2CLK signals           | _      | 1000     | $20 + 0.1C_b^{4}$ | 300  | ns |

| IC11 | Fall time of both I2DAT and I2CLK signals           | _      | 300      | $20 + 0.1C_b^{4}$ | 300  | ns |

| IC12 | Capacitive load for each bus line (C <sub>b</sub> ) | _      | 400      | _                 | 400  | pF |

<sup>&</sup>lt;sup>1</sup> A device must internally provide a hold time of at least 300 ns for I2DAT signal in order to bridge the undefined region of the falling edge of I2CLK.

## 4.11.10 Image Processing Unit (IPU) Module Parameters

The purpose of the IPU is to provide comprehensive support for the flow of data from an image sensor and/or to a display device. This support covers all aspects of these activities:

- Connectivity to relevant devices—cameras, displays, graphics accelerators, and TV encoders.

- Related image processing and manipulation: sensor image signal processing, display processing, image conversions, and other related functions.

- Synchronization and control capabilities, such as avoidance of tearing artifacts.

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 1

<sup>&</sup>lt;sup>2</sup> The maximum hold time has only to be met if the device does not stretch the LOW period (ID no IC5) of the I2CLK signal.

A Fast-mode I<sup>2</sup>C-bus device can be used in a Standard-mode I<sup>2</sup>C-bus system, but the requirement of Set-up time (ID No IC7) of 250 ns must be met. This automatically is the case if the device does not stretch the LOW period of the I2CLK signal. If such a device does stretch the LOW period of the I2CLK signal, it must output the next data bit to the I2DAT line max\_rise\_time (IC9) + data\_setup\_time (IC7) = 1000 + 250 = 1250 ns (according to the Standard-mode I<sup>2</sup>C-bus specification) before the I2CLK line is released.

<sup>&</sup>lt;sup>4</sup> C<sub>b</sub> = total capacitance of one bus line in pF.

#### **Electrical Characteristics**

## 4.11.10.1 IPU Sensor Interface Signal Mapping

The IPU supports a number of sensor input formats. Table 65 defines the mapping of the Sensor Interface Pins used for various supported interface formats.

Table 65. Camera Input Signal Cross Reference, Format, and Bits Per Cycle

| Signal<br>Name <sup>1</sup> | RGB565<br>8 bits<br>2 cycles | RGB565 <sup>2</sup><br>8 bits<br>3 cycles | RGB666 <sup>3</sup><br>8 bits<br>3 cycles | RGB888<br>8 bits<br>3 cycles | YCbCr <sup>4</sup><br>8 bits<br>2 cycles | RGB565 <sup>5</sup><br>16 bits<br>2 cycles | YCbCr <sup>6</sup><br>16 bits<br>1 cycle | YCbCr <sup>7</sup><br>16 bits<br>1 cycle | YCbCr <sup>8</sup><br>20 bits<br>1 cycle |

|-----------------------------|------------------------------|-------------------------------------------|-------------------------------------------|------------------------------|------------------------------------------|--------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|

| CSIx_DAT0                   | _                            | _                                         | _                                         | _                            | _                                        | _                                          | _                                        | 0                                        | C[0]                                     |

| CSIx_DAT1                   | _                            | _                                         | _                                         | _                            | _                                        | _                                          | _                                        | 0                                        | C[1]                                     |

| CSIx_DAT2                   | _                            | _                                         | _                                         | _                            | _                                        | _                                          | _                                        | C[0]                                     | C[2]                                     |

| CSIx_DAT3                   | _                            | _                                         | _                                         | _                            | _                                        | _                                          | _                                        | C[1]                                     | C[3]                                     |

| CSIx_DAT4                   | _                            | _                                         |                                           | _                            | _                                        | B[0]                                       | C[0]                                     | C[2]                                     | C[4]                                     |

| CSIx_DAT5                   | _                            | _                                         | _                                         | _                            | _                                        | B[1]                                       | C[1]                                     | C[3]                                     | C[5]                                     |

| CSIx_DAT6                   | _                            | _                                         | _                                         | _                            | _                                        | B[2]                                       | C[2]                                     | C[4]                                     | C[6]                                     |

| CSIx_DAT7                   | _                            | _                                         | _                                         | _                            | _                                        | B[3]                                       | C[3]                                     | C[5]                                     | C[7]                                     |

| CSIx_DAT8                   | _                            | _                                         | _                                         | _                            | _                                        | B[4]                                       | C[4]                                     | C[6]                                     | C[8]                                     |

| CSIx_DAT9                   | _                            | _                                         | _                                         | _                            | _                                        | G[0]                                       | C[5]                                     | C[7]                                     | C[9]                                     |

| CSIx_DAT10                  | _                            | _                                         | _                                         | _                            | _                                        | G[1]                                       | C[6]                                     | 0                                        | Y[0]                                     |

| CSIx_DAT11                  | _                            | _                                         | _                                         | _                            | _                                        | G[2]                                       | C[7]                                     | 0                                        | Y[1]                                     |

| CSIx_DAT12                  | B[0], G[3]                   | R[2],G[4],B[2]                            | R/G/B[4]                                  | R/G/B[0]                     | Y/C[0]                                   | G[3]                                       | Y[0]                                     | Y[0]                                     | Y[2]                                     |

| CSIx_DAT13                  | B[1], G[4]                   | R[3],G[5],B[3]                            | R/G/B[5]                                  | R/G/B[1]                     | Y/C[1]                                   | G[4]                                       | Y[1]                                     | Y[1]                                     | Y[3]                                     |

| CSIx_DAT14                  | B[2], G[5]                   | R[4],G[0],B[4]                            | R/G/B[0]                                  | R/G/B[2]                     | Y/C[2]                                   | G[5]                                       | Y[2]                                     | Y[2]                                     | Y[4]                                     |

| CSIx_DAT15                  | B[3], R[0]                   | R[0],G[1],B[0]                            | R/G/B[1]                                  | R/G/B[3]                     | Y/C[3]                                   | R[0]                                       | Y[3]                                     | Y[3]                                     | Y[5]                                     |

| CSIx_DAT16                  | B[4], R[1]                   | R[1],G[2],B[1]                            | R/G/B[2]                                  | R/G/B[4]                     | Y/C[4]                                   | R[1]                                       | Y[4]                                     | Y[4]                                     | Y[6]                                     |

| CSIx_DAT17                  | G[0], R[2]                   | R[2],G[3],B[2]                            | R/G/B[3]                                  | R/G/B[5]                     | Y/C[5]                                   | R[2]                                       | Y[5]                                     | Y[5]                                     | Y[7]                                     |

| CSIx_DAT18                  | G[1], R[3]                   | R[3],G[4],B[3]                            | R/G/B[4]                                  | R/G/B[6]                     | Y/C[6]                                   | R[3]                                       | Y[6]                                     | Y[6]                                     | Y[8]                                     |

| CSIx_DAT19                  | G[2], R[4]                   | R[4],G[5],B[4]                            | R/G/B[5]                                  | R/G/B[7]                     | Y/C[7]                                   | R[4]                                       | Y[7]                                     | Y[7]                                     | Y[9]                                     |

CSIx stands for CSI1 or CSI2

<sup>&</sup>lt;sup>2</sup> The MSB bits are duplicated on LSB bits implementing color extension

<sup>&</sup>lt;sup>3</sup> The two MSB bits are duplicated on LSB bits implementing color extension

<sup>&</sup>lt;sup>4</sup> YCbCr, 8 bits—Supported within the BT.656 protocol (sync embedded within the data stream).

<sup>&</sup>lt;sup>5</sup> RGB 16 bits— Supported in two ways: (1) As a "generic data" input, with no on-the-fly processing; (2) With on-the-fly processing, but only under some restrictions on the control protocol.

<sup>&</sup>lt;sup>6</sup> YCbCr 16 bits— Supported as a "generic-data" input, with no on-the-fly processing.

YCbCr 16 bits— Supported as a sub-case of the YCbCr, 20 bits, under the same conditions (BT.1120 protocol).

<sup>&</sup>lt;sup>8</sup> YCbCr, 20 bits, supported only within the BT.1120 protocol (syncs embedded within the data stream).

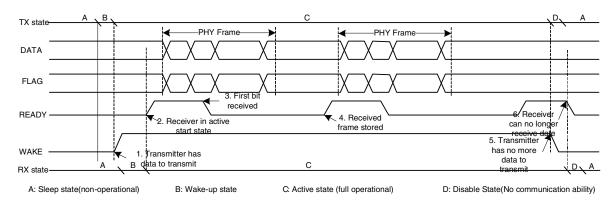

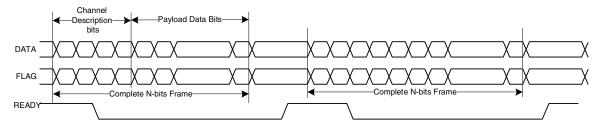

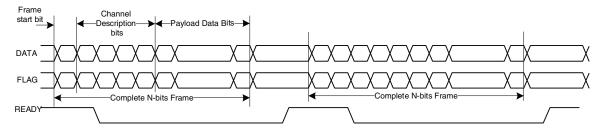

## 4.11.13.4 Synchronized Data Flow Transmission with Wake

Figure 79. Synchronized Data Flow Transmission with WAKE

## 4.11.13.5 Stream Transmission Mode Frame Transfer

Figure 80. Stream Transmission Mode Frame Transfer (Synchronized Data Flow)

## 4.11.13.6 Frame Transmission Mode (Synchronized Data Flow)

Figure 81. Frame Transmission Mode Transfer of Two Frames (Synchronized Data Flow)

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 1 118 Freescale Semiconductor

#### **Electrical Characteristics**

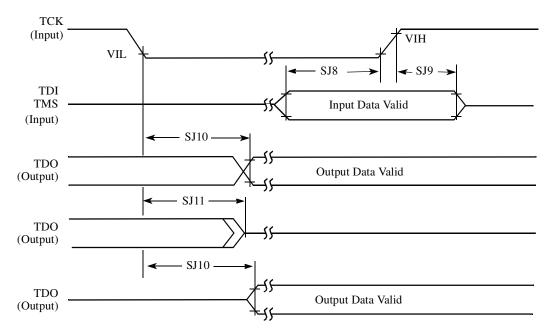

Figure 87. Test Access Port Timing Diagram

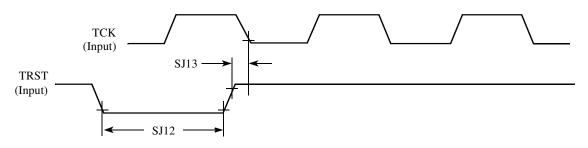

Figure 88. TRST Timing Diagram

**Table 75. JTAG Timing**

| ID   | Parameter <sup>1,2</sup>                                       | All Freq | Unit |       |

|------|----------------------------------------------------------------|----------|------|-------|

| l ID | Parameter *                                                    | Min      | Max  | Oilit |

| SJ0  | TCK frequency of operation 1/(3•T <sub>DC</sub> ) <sup>1</sup> | 0.001    | 22   | MHz   |

| SJ1  | TCK cycle time in crystal mode                                 | 45       | _    | ns    |

| SJ2  | TCK clock pulse width measured at V <sub>M</sub> <sup>2</sup>  | 22.5     | _    | ns    |

| SJ3  | TCK rise and fall times                                        | _        | 3    | ns    |

| SJ4  | Boundary scan input data set-up time                           | 5        | _    | ns    |

| SJ5  | Boundary scan input data hold time                             | 24       | _    | ns    |

| SJ6  | TCK low to output data valid                                   | _        | 40   | ns    |

| SJ7  | TCK low to output high impedance                               | _        | 40   | ns    |

| SJ8  | TMS, TDI data set-up time                                      | 5        | _    | ns    |

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 1

| ID   | Parameter <sup>1,2</sup>      | All Freq | Unit  |    |

|------|-------------------------------|----------|-------|----|

|      | raiameter                     | Min      | Oilit |    |

| SJ9  | TMS, TDI data hold time       | 25       | _     | ns |

| SJ10 | TCK low to TDO data valid     | _        | 44    | ns |

| SJ11 | TCK low to TDO high impedance | _        | 44    | ns |

| SJ12 | TRST assert time              | 100      | _     | ns |

| SJ13 | TRST set-up time to TCK low   | 40       | _     | ns |

$<sup>^{1}</sup>$  T<sub>DC</sub> = target frequency of SJC

## 4.11.17 SPDIF Timing Parameters

The Sony/Philips Digital Interconnect Format (SPDIF) data is sent using the bi-phase marking code. When encoding, the SPDIF data signal is modulated by a clock that is twice the bit rate of the data signal.

Table 76 and Figure 89 and Figure 90 show SPDIF timing parameters for the Sony/Philips Digital Interconnect Format (SPDIF), including the timing of the modulating Rx clock (SRCK) for SPDIF in Rx mode and the timing of the modulating Tx clock (STCLK) for SPDIF in Tx mode.

**Table 76. SPDIF Timing Parameters**

| Characteristics                                                                   | Cymphal     | Timing Parameter Range |                     | I I m ! t |  |

|-----------------------------------------------------------------------------------|-------------|------------------------|---------------------|-----------|--|

| Characteristics                                                                   | Symbol      | Min                    | Max                 | - Unit    |  |

| SPDIFIN Skew: asynchronous inputs, no specs apply                                 | _           | _                      | 0.7                 | ns        |  |

| SPDIFOUT output (Load = 50pf)  • Skew  • Transition rising  • Transition falling  | _<br>_<br>_ | _<br>_<br>_            | 1.5<br>24.2<br>31.3 | ns        |  |

| SPDIFOUT1 output (Load = 30pf)  • Skew  • Transition rising  • Transition falling | _<br>_<br>_ | _<br>_<br>_<br>_       | 1.5<br>13.6<br>18.0 | ns        |  |

| Modulating Rx clock (SRCK) period                                                 | srckp       | 40.0                   | _                   | ns        |  |

| SRCK high period                                                                  | srckph      | 16.0                   | _                   | ns        |  |

| SRCK low period                                                                   | srckpl      | 16.0                   | _                   | ns        |  |

| Modulating Tx clock (STCLK) period                                                | stclkp      | 40.0                   | _                   | ns        |  |

| STCLK high period                                                                 | stclkph     | 16.0                   | _                   | ns        |  |

| STCLK low period                                                                  | stclkpl     | 16.0                   | _                   | ns        |  |

$<sup>^{2}</sup>$   $V_{M} = mid-point voltage$

# 6.1.2 21 x 21 mm Supplies Contact Assignments and Functional Contact Assignments

Table 91 shows supplies contact assignments for the 21 x 21 mm package.

Table 91. 21 x 21 mm Supplies Contact Assignments

| Supply Rail Name | Ball(s) Position(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Remark                                                   |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|--|--|

| CSI_REXT         | D4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |  |  |  |

| DRAM_VREF        | AC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                          |  |  |  |

| DSI_REXT         | G4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |  |  |  |

| GND              | A4, A8, A13, A25, B4, C1, C4, C6, C10, D3, D6, D8, E5, E6, E7, F5, F6, F7, F8, G3, G10, G19, H8, H12, H15, H18, J2, J8, J12, J15, J18, K8, K10, K12, K15, K18, L2, L5, L8, L10, L12, L15, L18, M8, M10, M12, M15, M18, N8, N10, N15, N18, P8, P10, P12, P15, P18, R8, R12, R15, R17, T8, T11, T12, T15, T17, T19, U8, U11, U12, U15, U17, U19, V8, V19, W3, W7, W8, W9, W10, W11, W12, W13, W15, W16, W17, W18, W19, Y5, Y24, AA7, AA10, AA13, AA16, AA19, AA22, AB3, AB24, AD4, AD7, AD10, AD13, AD16, AD19, AD22, AE1, AE25 |                                                          |  |  |  |

| HDMI_REF         | J1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |  |  |  |

| HDMI_VP          | L7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |  |  |  |

| HDMI_VPH         | M7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |  |  |  |

| NVCC_CSI         | N7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Supply of the camera sensor interface                    |  |  |  |

| NVCC_DRAM        | R18, T18, U18, V9, V10, V11, V12, V13, V14, V15, V16, V17, V18                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Supply of the DDR interface                              |  |  |  |

| NVCC_EIM         | K19, L19, M19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Supply of the EIM interface                              |  |  |  |

| NVCC_ENET        | R19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Supply of the ENET interface                             |  |  |  |

| NVCC_GPIO        | P7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Supply of the GPIO interface                             |  |  |  |

| NVCC_JTAG        | J7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Supply of the JTAG tap controller interface              |  |  |  |

| NVCC_LCD         | P19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Supply of the LCD interface                              |  |  |  |

| NVCC_LVDS2P5     | V7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Supply of the LVDS display interface and DDR pre-drivers |  |  |  |

| NVCC_MIPI        | K7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Supply of the MIPI interface                             |  |  |  |

| NVCC_NANDF       | G15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Supply of the raw NAND Flash memories interface          |  |  |  |

| NVCC_PLL_OUT     | E8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |  |  |  |

| NVCC_RGMII       | G18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Supply of the ENET interface                             |  |  |  |

| NVCC_SD1         | G16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Supply of the SD card interface                          |  |  |  |

| NVCC_SD2         | G17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Supply of the SD card interface                          |  |  |  |

| NVCC_SD3         | G14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Supply of the SD card interface                          |  |  |  |

## **Package Information and Contact Assignments**

Table 92. 21 x 21 mm Functional Contact Assignments<sup>1</sup> (continued)

|            |      | Ball Power Group | Ball<br>Type | Out of Reset Condition <sup>2</sup> |                  |                      |                |

|------------|------|------------------|--------------|-------------------------------------|------------------|----------------------|----------------|

| Ball Name  | Ball |                  |              | Default<br>Mode<br>(Reset<br>Mode)  | Default Function | Input/<br>Outpu<br>t | Value          |

| DISP0_DAT3 | P21  | NVCC_LCD         | GPIO         | ALT5                                | gpio4.GPIO[24]   | Input                | 100 kΩ pull-up |

| DISP0_DAT4 | P20  | NVCC_LCD         | GPIO         | ALT5                                | gpio4.GPIO[25]   | Input                | 100 kΩ pull-up |

| DISP0_DAT5 | R25  | NVCC_LCD         | GPIO         | ALT5                                | gpio4.GPIO[26]   | Input                | 100 kΩ pull-up |

| DISP0_DAT6 | R23  | NVCC_LCD         | GPIO         | ALT5                                | gpio4.GPIO[27]   | Input                | 100 kΩ pull-up |

| DISP0_DAT7 | R24  | NVCC_LCD         | GPIO         | ALT5                                | gpio4.GPIO[28]   | Input                | 100 kΩ pull-up |

| DISP0_DAT8 | R22  | NVCC_LCD         | GPIO         | ALT5                                | gpio4.GPIO[29]   | Input                | 100 kΩ pull-up |

| DISP0_DAT9 | T25  | NVCC_LCD         | GPIO         | ALT5                                | gpio4.GPIO[30]   | Input                | 100 kΩ pull-up |

| DRAM_A0    | AC14 | NVCC_DRAM        | DDR          | ALT0                                | mmdc.DRAM_A[0]   | Output               | Low            |

| DRAM_A1    | AB14 | NVCC_DRAM        | DDR          | ALT0                                | mmdc.DRAM_A[1]   | Output               | Low            |

| DRAM_A10   | AA15 | NVCC_DRAM        | DDR          | ALT0                                | mmdc.DRAM_A[10]  | Output               | Low            |

| DRAM_A11   | AC12 | NVCC_DRAM        | DDR          | ALT0                                | mmdc.DRAM_A[11]  | Output               | Low            |

| DRAM_A12   | AD12 | NVCC_DRAM        | DDR          | ALT0                                | mmdc.DRAM_A[12]  | Output               | Low            |

| DRAM_A13   | AC17 | NVCC_DRAM        | DDR          | ALT0                                | mmdc.DRAM_A[13]  | Output               | Low            |

| DRAM_A14   | AA12 | NVCC_DRAM        | DDR          | ALT0                                | mmdc.DRAM_A[14]  | Output               | Low            |

| DRAM_A15   | Y12  | NVCC_DRAM        | DDR          | ALT0                                | mmdc.DRAM_A[15]  | Output               | Low            |

| DRAM_A2    | AA14 | NVCC_DRAM        | DDR          | ALT0                                | mmdc.DRAM_A[2]   | Output               | Low            |

| DRAM_A3    | Y14  | NVCC_DRAM        | DDR          | ALT0                                | mmdc.DRAM_A[3]   | Output               | Low            |

| DRAM_A4    | W14  | NVCC_DRAM        | DDR          | ALT0                                | mmdc.DRAM_A[4]   | Output               | Low            |

| DRAM_A5    | AE13 | NVCC_DRAM        | DDR          | ALT0                                | mmdc.DRAM_A[5]   | Output               | Low            |

| DRAM_A6    | AC13 | NVCC_DRAM        | DDR          | ALT0                                | mmdc.DRAM_A[6]   | Output               | Low            |

| DRAM_A7    | Y13  | NVCC_DRAM        | DDR          | ALT0                                | mmdc.DRAM_A[7]   | Output               | Low            |

| DRAM_A8    | AB13 | NVCC_DRAM        | DDR          | ALT0                                | mmdc.DRAM_A[8]   | Output               | Low            |

| DRAM_A9    | AE12 | NVCC_DRAM        | DDR          | ALT0                                | mmdc.DRAM_A[9]   | Output               | Low            |

| DRAM_CAS   | AE16 | NVCC_DRAM        | DDR          | ALT0                                | mmdc.DRAM_CAS    | Output               | Low            |

| DRAM_CS0   | Y16  | NVCC_DRAM        | DDR          | ALT0                                | mmdc.DRAM_CS[0]  | Output               | Low            |

| DRAM_CS1   | AD17 | NVCC_DRAM        | DDR          | ALT0                                | mmdc.DRAM_CS[1]  | Output               | Low            |

| DRAM_D0    | AD2  | NVCC_DRAM        | DDR          | ALT0                                | mmdc.DRAM_D[0]   | Input                | 100 kΩ pull-up |

| DRAM_D1    | AE2  | NVCC_DRAM        | DDR          | ALT0                                | mmdc.DRAM_D[1]   | Input                | 100 kΩ pull-up |

| DRAM_D10   | AA6  | NVCC_DRAM        | DDR          | ALT0                                | mmdc.DRAM_D[10]  | Input                | 100 kΩ pull-up |

| DRAM_D11   | AE7  | NVCC_DRAM        | DDR          | ALT0                                | mmdc.DRAM_D[11]  | Input                | 100 kΩ pull-up |

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 1

## **Package Information and Contact Assignments**

Table 92. 21 x 21 mm Functional Contact Assignments<sup>1</sup> (continued)

|             |        | Power Group  |              | Out of Reset Condition <sup>2</sup> |                  |                      |                  |

|-------------|--------|--------------|--------------|-------------------------------------|------------------|----------------------|------------------|

| Ball Name   | e Ball |              | Ball<br>Type | Default<br>Mode<br>(Reset<br>Mode)  | Default Function | Input/<br>Outpu<br>t | Value            |

| GPIO_9      | T2     | NVCC_GPIO    | GPIO         | ALT5                                | gpio1.GPIO[9]    | Input                | 100 kΩ pull-up   |

| HDMI_CLKM   | J5     | HDMI_VPH     |              |                                     |                  |                      |                  |

| HDMI_CLKP   | J6     | HDMI_VPH     |              |                                     |                  |                      |                  |

| HDMI_D0M    | K5     | HDMI_VPH     |              |                                     |                  |                      |                  |

| HDMI_D0P    | K6     | HDMI_VPH     |              |                                     |                  |                      |                  |

| HDMI_D1M    | J3     | HDMI_VPH     |              |                                     |                  |                      |                  |

| HDMI_D1P    | J4     | HDMI_VPH     |              |                                     |                  |                      |                  |

| HDMI_D2M    | КЗ     | HDMI_VPH     |              |                                     |                  |                      |                  |

| HDMI_D2P    | K4     | HDMI_VPH     |              |                                     |                  |                      |                  |

| HDMI_HPD    | K1     | HDMI_VPH     |              |                                     |                  |                      |                  |

| JTAG_MOD    | H6     | NVCC_JTAG    | GPIO         | ALT0                                | sjc.MOD          | Input                | 100 kΩ pull-up   |

| JTAG_TCK    | H5     | NVCC_JTAG    | GPIO         | ALT0                                | sjc.TCK          | Input                | 47 kΩ pull-up    |

| JTAG_TDI    | G5     | NVCC_JTAG    | GPIO         | ALT0                                | sjc.TDI          | Input                | 47 kΩ pull-up    |

| JTAG_TDO    | G6     | NVCC_JTAG    | GPIO         | ALT0                                | sjc.TDO          | Output               | Low              |

| JTAG_TMS    | СЗ     | NVCC_JTAG    | GPIO         | ALT0                                | sjc.TMS          | Input                | 47 kΩ pull-up    |

| JTAG_TRSTB  | C2     | NVCC_JTAG    | GPIO         | ALT0                                | sjc.TRSTB        | Input                | 47 kΩ pull-up    |

| KEY_COL0    | W5     | NVCC_GPIO    | GPIO         | ALT5                                | gpio4.GPIO[6]    | Input                | 100 kΩ pull-up   |

| KEY_COL1    | U7     | NVCC_GPIO    | GPIO         | ALT5                                | gpio4.GPIO[8]    | Input                | 100 kΩ pull-up   |

| KEY_COL2    | W6     | NVCC_GPIO    | GPIO         | ALT5                                | gpio4.GPIO[10]   | Input                | 100 kΩ pull-up   |

| KEY_COL3    | U5     | NVCC_GPIO    | GPIO         | ALT5                                | gpio4.GPIO[12]   | Input                | 100 kΩ pull-up   |

| KEY_COL4    | T6     | NVCC_GPIO    | GPIO         | ALT5                                | gpio4.GPIO[14]   | Input                | 100 kΩ pull-up   |

| KEY_ROW0    | V6     | NVCC_GPIO    | GPIO         | ALT5                                | gpio4.GPIO[7]    | Input                | 100 kΩ pull-up   |

| KEY_ROW1    | U6     | NVCC_GPIO    | GPIO         | ALT5                                | gpio4.GPIO[9]    | Input                | 100 kΩ pull-up   |

| KEY_ROW2    | W4     | NVCC_GPIO    | GPIO         | ALT5                                | gpio4.GPIO[11]   | Input                | 100 kΩ pull-up   |

| KEY_ROW3    | T7     | NVCC_GPIO    | GPIO         | ALT5                                | gpio4.GPIO[13]   | Input                | 100 kΩ pull-up   |

| KEY_ROW4    | V5     | NVCC_GPIO    | GPIO         | ALT5                                | gpio4.GPIO[15]   | Input                | 100 kΩ pull-down |

| LVDS0_CLK_N | V4     | NVCC_LVDS2P5 |              |                                     |                  |                      |                  |

| LVDS0_CLK_P | V3     | NVCC_LVDS2P5 |              | ALT0                                | ldb.LVDS0_CLK    | Input                | Keeper           |

| LVDS0_TX0_N | U2     | NVCC_LVDS2P5 |              |                                     |                  |                      |                  |

| LVDS0_TX0_P | U1     | NVCC_LVDS2P5 |              | ALT0                                | ldb.LVDS0_TX0    | Input                | Keeper           |

i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 1