#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                     | Not For New Designs                                                                                                 |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 2 Core, 32-Bit                                                                                                      |

| Speed                              | 1.0GHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON <sup>™</sup> SIMD                                                                                  |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | -                                                                                                                   |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | 0°C ~ 95°C (TJ)                                                                                                     |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-LFBGA                                                                                                           |

| Supplier Device Package            | 624-MAPBGA (21x21)                                                                                                  |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6u8dvm10ab                                             |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Introduction

- Color eReaders

- IPTV

- Human Machine Interfaces (HMI)

- Portable medical

- IP phones

- Home energy management systems

The i.MX 6Solo/6DualLite processors have some very exciting features, for example:

- Applications processors—The processors enhance the capabilities of high-tier portable applications by fulfilling the ever increasing MIPS needs of operating systems and games. Freescale's Dynamic Voltage and Frequency Scaling (DVFS) provides significant power reduction, allowing the device to run at lower voltage and frequency with sufficient MIPS for tasks, such as audio decode.

- Multilevel memory system—The multilevel memory system of each processor is based on the L1 instruction and data caches, L2 cache, and internal and external memory. The processors support many types of external memory devices, including DDR3, low voltage DDR3, LPDDR2, NOR Flash, PSRAM, cellular RAM, NAND Flash (MLC and SLC), OneNAND<sup>TM</sup>, and managed NAND, including eMMC up to rev 4.4.

- Smart speed technology—The processors have power management throughout the IC that enables the rich suite of multimedia features and peripherals to consume minimum power in both active and various low power modes. Smart speed technology enables the designer to deliver a feature-rich product, requiring levels of power far lower than industry expectations.

- Dynamic voltage and frequency scaling—The processors improve the power efficiency of devices by scaling the voltage and frequency to optimize performance.

- Multimedia powerhouse—The multimedia performance of each processor is enhanced by a multilevel cache system, Neon MPE (Media Processor Engine) co-processor, a multi-standard hardware video codec, an image processing unit (IPU), and a programmable smart DMA (SDMA) controller.

- Powerful graphics acceleration—Each processor provides two independent, integrated graphics processing units: an OpenGL<sup>®</sup> ES 2.0 3D graphics accelerator with a shader and a 2D graphics accelerator.

- Interface flexibility—Each processor supports connections to a variety of interfaces: LCD controller for up to two displays (including parallel display, HDMI1.4, MIPI display, and LVDS display), dual CMOS sensor interface (parallel or through MIPI), high-speed USB on-the-go with PHY, high-speed USB host with PHY, multiple expansion card ports (high-speed MMC/SDIO host and other), 10/100/1000 Mbps Gigabit Ethernet controller, and a variety of other popular interfaces (such as UART, I<sup>2</sup>C, and I<sup>2</sup>S serial audio, and PCIe-II).

- Eink Panel Display Controller—The processors integrate EPD controller that supports E-INK color and monochrome with up to 1650x2332 resolution and 5-bit grayscale (32-levels per color channel).

- Advanced security—The processors deliver hardware-enabled security features that enable secure e-commerce, digital rights management (DRM), information encryption, secure boot, and secure

# 4.1.3 **Operating Ranges**

Table 9 provides the operating ranges of the i.MX 6Solo/6DualLite processors. For details on the chip's power structure, see the "Power Management Unit (PMU)" chapter of the *i.MX 6Solo/6DualLite Reference Manual (IMX6SDLRM)*.

| Parameter<br>Description                         | Symbol                   | Min                  | Тур  | Max <sup>1</sup> | Unit | Comment                                                                                                                                                  |

|--------------------------------------------------|--------------------------|----------------------|------|------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Run mode: LDO<br>enabled                         | VDDARM_IN                | 1.350 <sup>2</sup>   | —    | 1.5              | V    | LDO Output Set Point (VDDARM_CAP) = 1.225 V minimum for operation up to 996 MHz.                                                                         |

|                                                  |                          | 1.275 <sup>2</sup>   | —    | 1.5              | V    | LDO Output Set Point (VDDARM_CAP) = 1.150 V minimum for operation up to 792 MHz.                                                                         |

|                                                  |                          | 1.175 <sup>2</sup>   | —    | 1.5              | V    | LDO Output Set Point (VDDARM_CAP) = 1.05<br>V minimum for operation up to 396 MHz.                                                                       |

|                                                  | VDDSOC_IN <sup>3</sup>   | 1.275 <sup>2,4</sup> | —    | 1.5              | V    | VPU = 328 MHz, VDDSOC and VDDPU LDO<br outputs (VDDSOC_CAP and VDDPU_CAP) =<br>1.225 V maximum and 1.15 V minimum.                                       |

| Run mode: LDO<br>bypassed                        | VDDARM_IN                | 1.250                | —    | 1.3              | V    | LDO bypassed for operation up to 996 MHz                                                                                                                 |

|                                                  |                          | 1.150                | —    | 1.3              | V    | LDO bypassed for operation up to 792 MHz                                                                                                                 |

|                                                  |                          | 1.05                 | —    | 1.3              | V    | LDO bypassed for operation up to 396 MHz                                                                                                                 |

|                                                  | VDDSOC_IN                | 1.15 <sup>4</sup>    | —    | 1.225            | V    | LDO bypassed for operation VPU = 328 MHz</td                                                                                                             |

| Standby/DSM mode                                 | VDDARM_IN                | 0.9                  | —    | 1.3              | V    | Refer to Table 13, "Stop Mode Current and Power Consumption," on page 29.                                                                                |

|                                                  | VDDSOC_IN                | 0.9                  | —    | 1.225            | V    |                                                                                                                                                          |

| VDDHIGH internal<br>regulator                    | VDDHIGH_IN               | 2.8                  | —    | 3.3              | V    | Must match the range of voltges that the rechargeable backup battery supports.                                                                           |

| Backup battery supply range                      | VDD_SNVS_IN <sup>5</sup> | 2.9                  | _    | 3.3              | V    | Should be supplied from the same supply as VDDHIGH_IN if the system does not require keeping real time and other data on OFF state.                      |

| USB supply voltages                              | USB_OTG_VBUS             | 4.4                  | —    | 5.25             | V    |                                                                                                                                                          |

|                                                  | USB_H1_VBUS              | 4.4                  | —    | 5.25             | V    |                                                                                                                                                          |

| DDR I/O supply voltage                           | NVCC_DRAM                | 1.14                 | 1.2  | 1.3              | V    | LPDDR2, DDR3-U                                                                                                                                           |

|                                                  |                          | 1.425                | 1.5  | 1.575            | V    | DDR3                                                                                                                                                     |

|                                                  |                          | 1.283                | 1.35 | 1.45             | V    | DDR3_L                                                                                                                                                   |

| Supply for RGMII I/O<br>power group <sup>6</sup> | NVCC_RGMII               | 1.15                 | _    | 2.625            | V    | 1.15 V – 1.30 V in HSIC 1.2 V mode<br>1.43 V – 1.58 V in RMGII 1.5 V mode<br>1.70 V – 1.90 V in RMGII 1.8 V mode<br>2.25 V – 2.625 V in RMGII 2.5 V mode |

| Table | 9. | Operati | ing | Ranges |

|-------|----|---------|-----|--------|

|-------|----|---------|-----|--------|

| Power Line | Conditions | Max Current                          | Unit |

|------------|------------|--------------------------------------|------|

| NVCC_DRAM  | —          | 4                                    |      |

| NVCC_ENET  | N=10       | Use maximal IO equation <sup>5</sup> |      |

| NVCC_LCD   | N=29       | Use maximal IO equation <sup>5</sup> |      |

| NVCC_GPIO  | N=24       | Use maximal IO equation <sup>5</sup> |      |

| NVCC_CSI   | N=20       | Use maximal IO equation <sup>5</sup> |      |

| NVCC_EIM   | N=53       | Use maximal IO equation <sup>5</sup> |      |

| NVCC_JTAG  | N=6        | Use maximal IO equation <sup>5</sup> |      |

| NVCC_RGMII | N=12       | Use maximal IO equation <sup>5</sup> |      |

| NVCC_SD1   | N=6        | Use maximal IO equation <sup>5</sup> |      |

| NVCC_SD2   | N=6        | Use maximal IO equation <sup>5</sup> |      |

| NVCC_SD3   | N=11       | Use maximal IO equation <sup>5</sup> |      |

| NVCC_NANDF | N=26       | Use maximal IO equation <sup>5</sup> |      |

|            | MISC       |                                      |      |

| DDR_VREF   | —          | 1                                    | mA   |

## Table 12. Maximal Supply Currents (continued)

<sup>1</sup> The actual maximum current drawn from VDDHIGH\_IN will be as shown plus any additional current drawn from the VDDHIGH\_CAP outputs, depending upon actual application configuration (for example, NVCC\_LVDS2P5, NVCC\_MIPI, or HDMI and PCIe VPH supplies).

<sup>2</sup> The maximum VDD\_SNVS\_IN current may be higher depending on specific operating configurations, such as BOOT\_MODE[1:0] not equal to 00, or use of the Tamper feature. During initial power on, VDD\_SNVS\_IN can draw up to 1 mA, if available. VDD\_SNVS\_CAP charge time will increase if less than 1 mA is available.

<sup>3</sup> This is the maximum current per active USB physical interface.

<sup>4</sup> The DRAM power consumption is dependent on several factors, such as external signal termination. DRAM power calculators are typically available from the memory vendors. They take in account factors, such as signal termination. See the i.MX 6Solo/DualLite Power Consumption Measurement Application Note (AN4576) for examples of DRAM power consumption during specific use case scenarios.

<sup>5</sup> General equation for estimated, maximal power consumption of an IO power supply:

$Imax = N \times C \times V \times (0.5 \times F)$

Where:

N—Number of IO pins supplied by the power line

C—Equivalent external capacitive load

V—IO voltage

(0.5 xF)—Data change rate. Up to 0.5 of the clock rate (F)

In this equation, Imax is in Amps, C in Farads, V in Volts, and F in Hertz.

power from VDDHIGH\_IN when that supply is available and transitions to the back up battery when VDDHIGH IN is lost.

In addition, if the clock monitor determines that the OSC32K is not present, then the source of the 32 K will automatically switch to a crude internal ring oscillator. The frequency range of this block is approximately 10-45 kHz. It highly depends on the process, voltage, and temperature.

The OSC32k runs from VDD\_SNVS\_CAP supply, which comes from the

VDDHIGH\_IN/VDD\_SNVS\_IN. The target battery is a ~3 V coin cell. Proper choice of coin cell type is necessary for chosen VDDHIGH\_IN range. Appropriate series resistor (Rs) must be used when connecting the coin cell. Rs depends on the charge current limit that depends on the chosen coin cell. For example, for Panasonic ML621:

- Average Discharge Voltage is 2.5 V

- Maximum Charge Current is 0.6 mA •

For a charge voltage of 3.2 V, Rs = (3.2-2.5)/0.6 m = 1.17 k

## Min Тур Max Comments

Table 22. OSC32K Main Characteristics

| Fosc                   | 32.768 KHz |                   | This frequency is nominal and determined mainly by the crystal selected. 32.0 K would work as well.                                                                                                                                                                                                                                                                                                                                             |

|------------------------|------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Current<br>consumption | 4 μΑ       |                   | The 4 $\mu$ A is the consumption of the oscillator alone (OSC32k). Total supply consumption will depend on what the digital portion of the RTC consumes. The ring oscillator consumes 1 $\mu$ A when ring oscillator is inactive, 20 $\mu$ A when the ring oscillator is running. Another 1.5 $\mu$ A is drawn from vdd_rtc in the power_detect block. So, the total current is 6.5 $\mu$ A on vdd_rtc when the ring oscillator is not running. |

| Bias resistor          | 14 MΩ      |                   | This the integrated bias resistor that sets the amplifier<br>into a high gain state. Any leakage through the ESD<br>network, external board leakage, or even a scope<br>probe that is significant relative to this value will<br>debias the amp. The debiasing will result in low gain,<br>and will impact the circuit's ability to start up and<br>maintain oscillations.                                                                      |

|                        | Ċ          | Crystal Propertie | ls                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Cload                  | 10 pF      |                   | Usually crystals can be purchased tuned for different<br>Cloads. This Cload value is typically 1/2 of the<br>capacitances realized on the PCB on either side of<br>the quartz. A higher Cload will decrease oscillation<br>margin, but increases current oscillating through the<br>crystal.                                                                                                                                                    |

| ESR                    | 50 kΩ      | 100 kΩ            | Equivalent series resistance of the crystal. Choosing<br>a crystal with a higher value will decrease the<br>oscillating margin.                                                                                                                                                                                                                                                                                                                 |

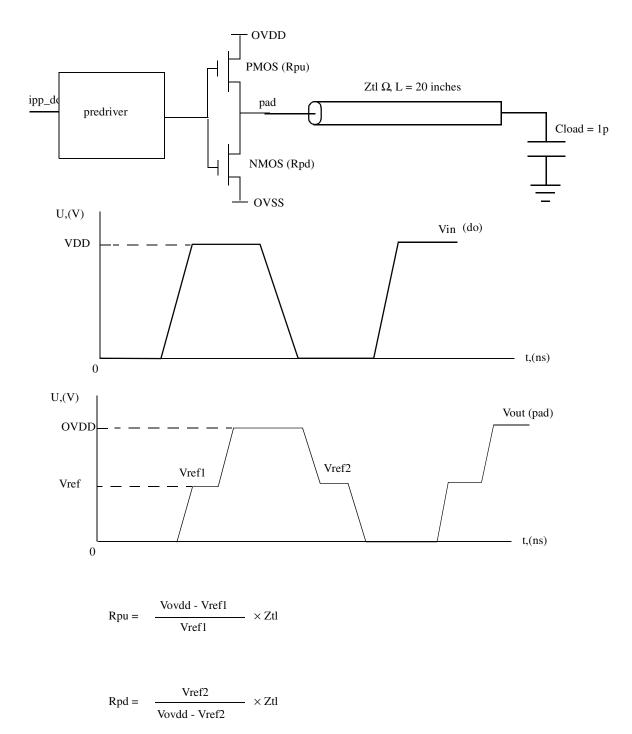

Figure 7. Impedance Matching Load for Measurement

## 4.8.1 GPIO Output Buffer Impedance

Table 32 shows the GPIO output buffer impedance (OVDD 1.8 V).

| Parameter     | Symbol | Drive Strength (DSE) | Typ Value | Unit |

|---------------|--------|----------------------|-----------|------|

|               |        | 001                  | 260       |      |

|               |        | 010                  | 130       |      |

| Output Driver | Rdrv   | 011                  | 90        |      |

| Impedance     |        | 100                  | 60        | Ω    |

|               |        | 101                  | 50        |      |

|               |        | 110                  | 40        |      |

|               |        | 111                  | 33        |      |

## Table 32. GPIO Output Buffer Average Impedance (OVDD 1.8 V)

Table 33 shows the GPIO output buffer impedance (OVDD 3.3 V).

| Parameter     | Symbol | Drive Strength (DSE) | Typ Value | Unit |

|---------------|--------|----------------------|-----------|------|

|               |        | 001                  | 150       |      |

|               |        | 010                  | 75        |      |

| Output Driver | Rdrv   | 011                  | 50        |      |

| Impedance     |        | 100                  | 37        | Ω    |

|               |        | 101                  | 30        |      |

|               |        | 110                  | 25        |      |

|               |        | 111                  | 20        |      |

## 4.8.2 DDR I/O Output Buffer Impedance

The LPDDR2 interface fully complies with JESD209-2B LPDDR2 JEDEC standard release June, 2009. The DDR3 interface fully complies with JESD79-3D DDR3 JEDEC standard release April, 2008.

Table 34 shows DDR I/O output buffer impedance of i.MX 6Solo/6DualLite processors.

| Table 34. DE | DR I/O Output B | uffer Impedance |

|--------------|-----------------|-----------------|

|              |                 |                 |

| Parameter                  | Symbol | Test Conditions DSE(Drive<br>Strength)               | Тур                                              |                                                  |      |

|----------------------------|--------|------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|------|

|                            |        |                                                      | NVCC_DRAM=1.5 V<br>(DDR3)<br>DDR_SEL=11          | NVCC_DRAM=1.2 V<br>(LPDDR2)<br>DDR_SEL=10        | Unit |

| Output Driver<br>Impedance | Rdrv   | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | Hi-Z<br>240<br>120<br>80<br>60<br>48<br>40<br>34 | Hi-Z<br>240<br>120<br>80<br>60<br>48<br>40<br>34 | Ω    |

### Note:

1. Output driver impedance is controlled across PVTs using ZQ calibration procedure.

- 2. Calibration is done against 240  $\Omega$  external reference resistor.

- 3. Output driver impedance deviation (calibration accuracy) is ±5% (max/min impedance) across PVTs.

## 4.8.3 LVDS I/O Output Buffer Impedance

The LVDS interface complies with TIA/EIA 644-A standard. See, TIA/EIA STANDARD 644-A, "Electrical Characteristics of Low Voltage Differential Signaling (LVDS) Interface Circuits" for details.

# 4.9 System Modules Timing

This section contains the timing and electrical parameters for the modules in each i.MX 6Solo/6DualLite processor.

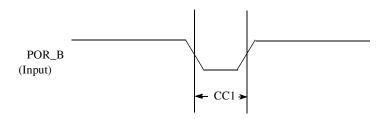

## 4.9.1 Reset Timings Parameters

Figure 8 shows the reset timing and Table 35 lists the timing parameters.

Figure 8. Reset Timing Diagram

**Table 35. Reset Timing Parameters**

| ID  | Parameter                                                       | Min | Max | Unit               |

|-----|-----------------------------------------------------------------|-----|-----|--------------------|

| CC1 | Duration of POR_B to be qualified as valid (input slope = 5 ns) | 1   | _   | RTC_XTALI<br>cycle |

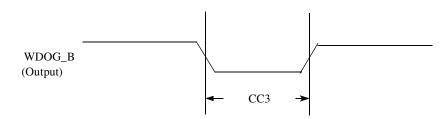

## 4.9.2 WDOG Reset Timing Parameters

Figure 9 shows the WDOG reset timing and Table 36 lists the timing parameters.

Figure 9. WDOG\_B Timing Diagram

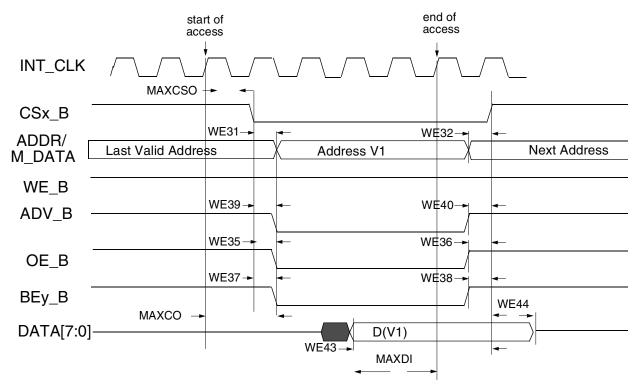

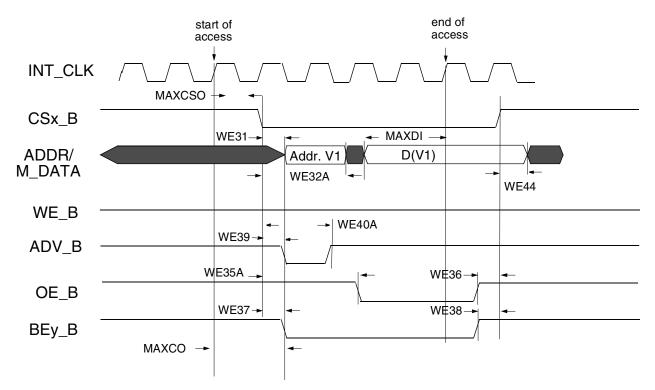

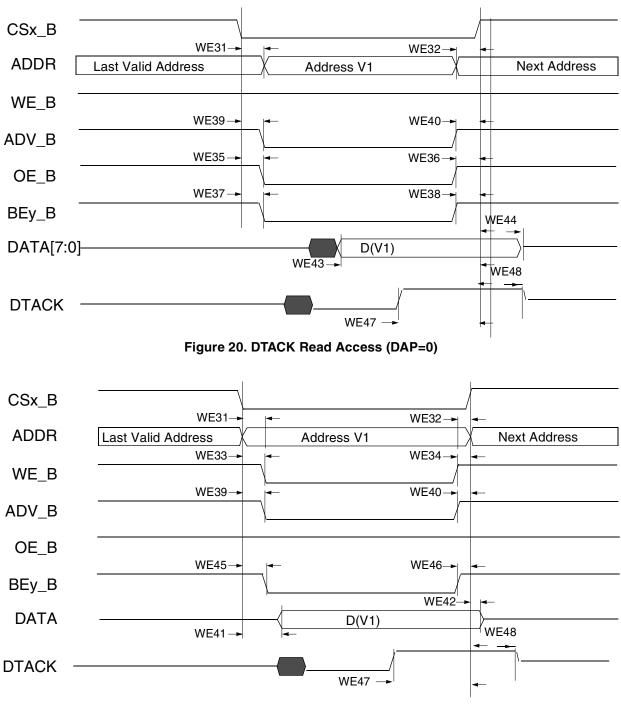

Figure 16. Asynchronous Memory Read Access (RWSC = 5)

**Electrical Characteristics**

Figure 21. DTACK Write Access (DAP=0)

| Ref No.                 | Parameter                                                                 | Determination by<br>Synchronous measured<br>parameters <sup>1</sup>               | Min                                        | Max<br>(If 132 MHz is<br>supported by SoC) | Unit |

|-------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------------|------|

| WE31                    | CSx_B valid to Address Valid                                              | WE4 - WE6 - CSA <sup>2</sup>                                                      | _                                          | 3 - CSA                                    | ns   |

| WE32                    | Address Invalid to CSx_B invalid                                          | WE7 - WE5 - CSN <sup>3</sup>                                                      | _                                          | 3 - CSN                                    | ns   |

| WE32A(<br>muxed<br>A/D  | CSx_B valid to Address Invalid                                            | t <sup>4</sup> + WE4 - WE7 + (ADVN <sup>5</sup> +<br>ADVA <sup>6</sup> + 1 - CSA) | -3 + (ADVN +<br>ADVA + 1 - CSA)            | _                                          | ns   |

| WE33                    | CSx_B Valid to WE_B Valid                                                 | WE8 - WE6 + (WEA - WCSA)                                                          | _                                          | 3 + (WEA - WCSA)                           | ns   |

| WE34                    | WE_B Invalid to CSx_B Invalid                                             | WE7 - WE9 + (WEN - WCSN)                                                          | _                                          | 3 - (WEN_WCSN)                             | ns   |

| WE35                    | CSx_B Valid to OE_B Valid                                                 | WE10 - WE6 + (OEA - RCSA)                                                         |                                            | 3 + (OEA - RCSA)                           | ns   |

| WE35A<br>(muxed<br>A/D) | CSx_B Valid to OE_B Valid                                                 | WE10 - WE6 + (OEA + RADVN<br>+ RADVA + ADH + 1 - RCSA)                            | -3 + (OEA +<br>RADVN+RADVA+<br>ADH+1-RCSA) | 3 + (OEA +<br>RADVN+RADVA+AD<br>H+1-RCSA)  | ns   |

| WE36                    | OE_B Invalid to CSx_B Invalid                                             | WE7 - WE11 + (OEN - RCSN)                                                         |                                            | 3 - (OEN - RCSN)                           | ns   |

| WE37                    | CSx_B Valid to BEy_B Valid (Read access)                                  | WE12 - WE6 + (RBEA - RCSA)                                                        | —                                          | 3 + (RBEA - RCSA)                          | ns   |

| WE38                    | BEy_B Invalid to CSx_B Invalid (Read access)                              | WE7 - WE13 + (RBEN - RCSN)                                                        | —                                          | 3 - (RBEN- RCSN)                           | ns   |

| WE39                    | CSx_B Valid to ADV_B Valid                                                | WE14 - WE6 + (ADVA - CSA)                                                         |                                            | 3 + (ADVA - CSA)                           | ns   |

| WE40                    | ADV_B Invalid to CSx_B Invalid (ADVL is asserted)                         | WE7 - WE15 - CSN                                                                  | _                                          | 3 - CSN                                    | ns   |

| WE40A<br>(muxed<br>A/D) | CSx_B Valid to ADV_B Invalid                                              | WE14 - WE6 + (ADVN + ADVA<br>+ 1 - CSA)                                           | -3 + (ADVN +<br>ADVA + 1 - CSA)            | 3 + (ADVN + ADVA +<br>1 - CSA)             | ns   |

| WE41                    | CSx_B Valid to Output Data<br>Valid                                       | WE16 - WE6 - WCSA                                                                 | _                                          | 3 - WCSA                                   | ns   |

| WE41A<br>(muxed<br>A/D) | CSx_B Valid to Output Data<br>Valid                                       | WE16 - WE6 + (WADVN +<br>WADVA + ADH + 1 - WCSA)                                  | _                                          | 3 + (WADVN +<br>WADVA + ADH + 1 -<br>WCSA) | ns   |

| WE42                    | Output Data Invalid to CSx_B<br>Invalid                                   | WE17 - WE7 - CSN                                                                  | —                                          | 3 - CSN                                    | ns   |

| MAXCO                   | Output max. delay from internal driving ADDR/control FFs to chip outputs. | 10                                                                                |                                            | -                                          | ns   |

| MAXCS<br>O              | Output max. delay from CSx internal driving FFs to CSx out.               | 10                                                                                | _                                          | _                                          |      |

| MAXDI                   | DATA MAXIMUM delay from chip input data to its internal FF                | 5                                                                                 | _                                          | —                                          |      |

## Table 40. EIM Asynchronous Timing Parameters Table Relative Chip Select

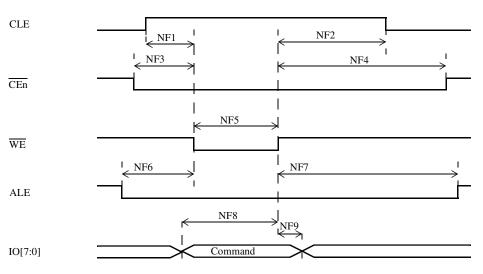

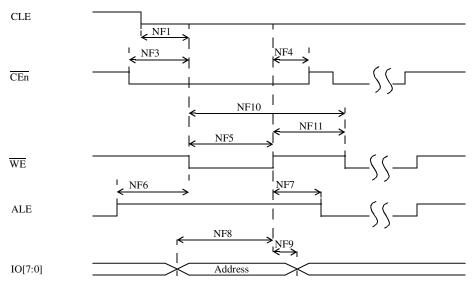

Figure 28. Command Latch Cycle Timing Diagram

Figure 29. Address Latch Cycle Timing Diagram

| ID   | Parameter          | Symbol | Timing<br>T = GPMI Clock Cycle |             | Example T<br>GPMI Clock<br>T = 1 | pprox 100 MHz | Unit |

|------|--------------------|--------|--------------------------------|-------------|----------------------------------|---------------|------|

|      |                    |        | Min.                           | Max.        | Min.                             | Max.          |      |

| NF5  | WE pulse width     | tWP    | DS                             | хΤ          | 1                                | 0             | ns   |

| NF6  | ALE setup time     | tALS   | (AS+1) x T                     | _           | 10                               | —             | ns   |

| NF7  | ALE hold time      | tALH   | (DH+1) x T                     | —           | 20                               | —             | ns   |

| NF8  | Data setup time    | tDS    | DS x T                         | _           | 10                               | —             | ns   |

| NF9  | Data hold time     | tDH    | DH x T                         | _           | 10                               | —             | ns   |

| NF10 | Write cycle time   | tWC    | (DS+D                          | (DS+DH) x T |                                  | 20            |      |

| NF11 | WE hold time       | tWH    | DH                             | хΤ          | 10                               |               | ns   |

| NF12 | Ready to RE low    | tRR    | (AS+1) x T                     | _           | 10                               | —             | ns   |

| NF13 | RE pulse width     | tRP    | DS x T                         | _           | 10                               | —             | ns   |

| NF14 | READ cycle time    | tRC    | (DS+DH) x T                    | —           | 20                               | —             | ns   |

| NF15 | RE high hold time  | tREH   | DH x T                         |             | 10                               | —             | ns   |

| NF16 | Data setup on read | tDSR   | N/                             | N/A         |                                  | —             | ns   |

| NF17 | Data hold on read  | tDHR   | N/                             | A           | 10                               | —             | ns   |

Table 47. Asynchronous Mode Timing Parameters<sup>1</sup> (continued)

<sup>1</sup> GPMI's Async Mode output timing could be controlled by module's internal registers, say

HW\_GPMI\_TIMING0\_ADDRESS\_SETUP, HW\_GPMI\_TIMING0\_DATA\_SETUP, and HW\_GPMI\_TIMING0\_DATA\_HOLD. This AC timing depends on these registers' settings. In the above table, we use AS/DS/DH to represent each of these settings.

2) AS minimum value could be 0, while DS/DH minimum value is 1.

3) T represents for the GPMI clock period.

In EDO mode (Figure 31), NF16/NF17 are different from the definition in non-EDO mode (Figure 30). They are called tREA/tRHOH (RE# access time/RE# HIGH to output hold). The typical value for them are 16 ns (max for tREA)/15 ns (min for tRHOH) at 50 MB/s EDO mode. In EDO mode, GPMI will sample IO[7:0] at rising edge of delayed RE provided by an internal DPLL. The delay value can be controlled by GPMI\_CTRL1.RDN\_DELAY (see the GPMI chapter of the i.MX 6Solo/6DualLite reference manual). The typical value of this control register is 0x8 at 50 MT/s EDO mode. But if the board delay is big enough and cannot be ignored, the delay value should be made larger to compensate the board delay.

## 4.11.3 Enhanced Serial Audio Interface (ESAI) Timing Parameters

The ESAI consists of independent transmitter and receiver sections, each section with its own clock generator. Table 52 shows the interface timing values. The number field in the table refers to timing signals found in Figure 40 and Figure 41.

| Na  | Characteristics <sup>1,2</sup>                                        | Cumhal | Europeania n2                                                         | Min          | Max          | O and itian 3          | 11   |

|-----|-----------------------------------------------------------------------|--------|-----------------------------------------------------------------------|--------------|--------------|------------------------|------|

| No. |                                                                       | Symbol | Expression <sup>2</sup>                                               | Min          | Max          | Condition <sup>3</sup> | Unit |

| 62  | Clock cycle <sup>4</sup>                                              | tssicc | $\begin{array}{c} 4 \times T_{C} \\ 4 \times T_{C} \end{array}$       | 30.0<br>30.0 | _            | i ck<br>i ck           | ns   |

| 63  | Clock high period:<br>• For internal clock<br>• For external clock    | _      | $\begin{array}{c} 2 \times T_{c} - 9.0 \\ 2 \times T_{c} \end{array}$ | 6<br>15      | _            |                        | ns   |

| 64  | Clock low period:<br>• For internal clock<br>• For external clock     | _      | $2 \times T_{c} - 9.0$ $2 \times T_{c}$                               | 6<br>15      | _            |                        | ns   |

| 65  | SCKR rising edge to FSR out (bl) high                                 |        | _                                                                     |              | 17.0<br>7.0  | x ck<br>i ck a         | ns   |

| 66  | SCKR rising edge to FSR out (bl) low                                  |        |                                                                       |              | 17.0<br>7.0  | x ck<br>i ck a         | ns   |

| 67  | SCKR rising edge to FSR out (wr) high <sup>5</sup>                    |        | _                                                                     |              | 19.0<br>9.0  | x ck<br>i ck a         | ns   |

| 68  | SCKR rising edge to FSR out (wr) low <sup>5</sup>                     | —      |                                                                       |              | 19.0<br>9.0  | x ck<br>i ck a         | ns   |

| 69  | SCKR rising edge to FSR out (wl) high                                 | —      |                                                                       |              | 16.0<br>6.0  | x ck<br>i ck a         | ns   |

| 70  | SCKR rising edge to FSR out (wl) low                                  | —      |                                                                       |              | 17.0<br>7.0  | x ck<br>i ck a         | ns   |

| 71  | Data in setup time before SCKR (SCK in synchronous mode) falling edge | —      |                                                                       | 12.0<br>19.0 |              | x ck<br>i ck           | ns   |

| 72  | Data in hold time after SCKR falling edge                             | —      |                                                                       | 3.5<br>9.0   | _            | x ck<br>i ck           | ns   |

| 73  | FSR input (bl, wr) high before SCKR falling edge <sup>5</sup>         | —      |                                                                       | 2.0<br>12.0  | _            | x ck<br>i ck a         | ns   |

| 74  | FSR input (wl) high before SCKR falling edge                          | —      | —                                                                     | 2.0<br>12.0  | _            | x ck<br>i ck a         | ns   |

| 75  | FSR input hold time after SCKR falling edge                           | —      |                                                                       | 2.5<br>8.5   | —            | x ck<br>i ck a         | ns   |

| 78  | SCKT rising edge to FST out (bl) high                                 | —      | —                                                                     |              | 18.0<br>8.0  | x ck<br>i ck           | ns   |

| 79  | SCKT rising edge to FST out (bl) low                                  |        | —                                                                     |              | 20.0<br>10.0 | x ck<br>i ck           | ns   |

| 80  | SCKT rising edge to FST out (wr) high <sup>5</sup>                    | _      |                                                                       |              | 20.0<br>10.0 | x ck<br>i ck           | ns   |

## Table 52. Enhanced Serial Audio Interface (ESAI) Timing

| Symbol                                                                                              | Parameter                                                                                                                                                                                                                                                                                                                                                                 | Condition                                                                                                                                                                              | Min.                 | Тур.        | Max.                 | Unit |

|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------|----------------------|------|

|                                                                                                     | I                                                                                                                                                                                                                                                                                                                                                                         | Operating conditions for HD                                                                                                                                                            | MI                   |             | 11                   |      |

| avddtmds                                                                                            | Termination supply voltage                                                                                                                                                                                                                                                                                                                                                | -                                                                                                                                                                                      | 3.15                 | 3.3         | 3.45                 | V    |

| R <sub>T</sub>                                                                                      | Termination resistance                                                                                                                                                                                                                                                                                                                                                    | -                                                                                                                                                                                      | 45                   | 50          | 55                   | Ω    |

|                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                           | TMDS drivers DC specificati                                                                                                                                                            | ons                  |             |                      |      |

| $V_{OFF}$                                                                                           |                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                        |                      | ldtmds ± 10 | mV                   | mV   |

| V <sub>SWING</sub>                                                                                  | Single-ended output swing voltage                                                                                                                                                                                                                                                                                                                                         | For measurement conditions<br>and definitions, see the first<br>two figures above.<br>Compliance point TP1 as<br>defined in the HDMI<br>specification, version 1.3a,<br>section 4.2.4. | 400                  | -           | 600                  | mV   |

| V <sub>H</sub>                                                                                      | Single-ended output high<br>voltage                                                                                                                                                                                                                                                                                                                                       | If attached sink supports<br>TMDSCLK < or = 165 MHz                                                                                                                                    | avd                  | ldtmds ± 10 | mV                   | mV   |

|                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                           | If attached sink supports<br>TMDSCLK > 165 MHz                                                                                                                                         | avddtmds<br>- 200 mV | -           | avddtmds<br>+ 10 mV  | mV   |

| V <sub>L</sub> Single-ended output low<br>voltage<br>For definition, see the second<br>figure above |                                                                                                                                                                                                                                                                                                                                                                           | If attached sink supports<br>TMDSCLK < or = 165 MHz                                                                                                                                    | avddtmds<br>- 600 mV | -           | avddtmds<br>- 400mV  | mV   |

|                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                           | If attached sink supports<br>TMDSCLK > 165 MHz                                                                                                                                         | avddtmds<br>- 700 mV | -           | avddtmds<br>- 400 mV | mV   |

| R <sub>term</sub>                                                                                   | Differential source termination<br>load (inside HDMI 3D Tx PHY)<br>Although the HDMI 3D Tx<br>PHY includes differential<br>source termination, the<br>user-defined value is set for<br>each single line (for<br>illustration, see the third figure<br>above).<br><b>Note:</b> R <sub>TERM</sub> can also be<br>configured to be open and not<br>present on TMDS channels. | -                                                                                                                                                                                      | 50                   | -           | 200                  | Ω    |

|                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                           | Hot plug detect specificatio                                                                                                                                                           | ns                   |             |                      |      |

| HPD <sup>VH</sup>                                                                                   | Hot plug detect high range                                                                                                                                                                                                                                                                                                                                                | -                                                                                                                                                                                      | 2.0                  | -           | 5.3                  | V    |

| VHPD                                                                                                | Hot plug detect low range                                                                                                                                                                                                                                                                                                                                                 | -                                                                                                                                                                                      | 0                    | -           | 0.8                  | V    |

| HPD                                                                                                 | Hot plug detect input<br>impedance                                                                                                                                                                                                                                                                                                                                        | -                                                                                                                                                                                      | 10                   | -           | -                    | kΩ   |

| HPD                                                                                                 | Hot plug detect time delay                                                                                                                                                                                                                                                                                                                                                | -                                                                                                                                                                                      | -                    | -           | 100                  | μs   |

# 4.11.8 Switching Characteristics

Table 63 describes switching characteristics for the HDMI 3D Tx PHY. Figure 56 to Figure 60 illustrate various parameters specified in table.

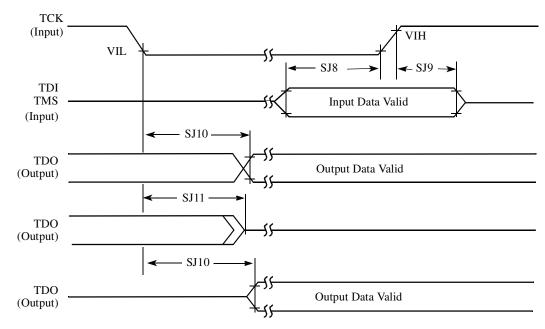

Figure 87. Test Access Port Timing Diagram

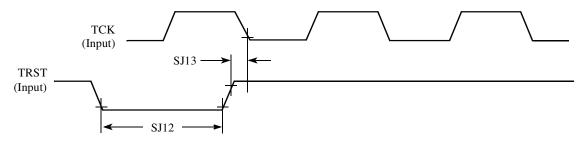

## Figure 88. TRST Timing Diagram

## Table 75. JTAG Timing

| ID  | Parameter <sup>1,2</sup>                                       | All Frequencies |      | Unit |

|-----|----------------------------------------------------------------|-----------------|------|------|

|     | Farameter                                                      | Min             | Onit |      |

| SJ0 | TCK frequency of operation 1/(3•T <sub>DC</sub> ) <sup>1</sup> | 0.001           | 22   | MHz  |

| SJ1 | TCK cycle time in crystal mode                                 | 45              | —    | ns   |

| SJ2 | TCK clock pulse width measured at $V_M^2$                      | 22.5            | —    | ns   |

| SJ3 | TCK rise and fall times                                        | _               | 3    | ns   |

| SJ4 | Boundary scan input data set-up time                           | 5               | —    | ns   |

| SJ5 | Boundary scan input data hold time                             | 24              | —    | ns   |

| SJ6 | TCK low to output data valid                                   | —               | 40   | ns   |

| SJ7 | TCK low to output high impedance                               | —               | 40   | ns   |

| SJ8 | TMS, TDI data set-up time                                      | 5               | —    | ns   |

| ID   | D Parameter                       |     | Мах | Unit |

|------|-----------------------------------|-----|-----|------|

| SS47 | 047 Oversampling clock period     |     | _   | ns   |

| SS48 | Oversampling clock high period    | 6.0 | _   | ns   |

| SS49 | SS49 Oversampling clock rise time |     | 3.0 | ns   |

| SS50 | Oversampling clock low period     | 6.0 | _   | ns   |

| SS51 | SS51 Oversampling clock fall time |     | 3.0 | ns   |

Table 79. SSI Receiver Timing with Internal Clock (continued)

## NOTE

- All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal STCK/SRCK and/or the frame sync STFS/SRFS shown in the tables and in the figures.

- All timings are on Audiomux Pads when SSI is being used for data transfer.

- "Tx" and "Rx" refer to the Transmit and Receive sections of the SSI.

- The terms, WL and BL, refer to Word Length (WL) and Bit Length (BL).

- For internal Frame Sync operation using external clock, the FS timing is same as that of Tx Data (for example, during AC97 mode of operation).

## 4.11.19.2.1 UART Transmitter

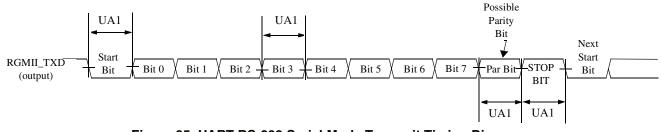

Figure 95 depicts the transmit timing of UART in the RS-232 serial mode, with 8 data bit/1 stop bit format. Table 83 lists the UART RS-232 serial mode transmit timing characteristics.

Figure 95. UART RS-232 Serial Mode Transmit Timing Diagram

| ID  | Parameter         | Symbol            | Min                                                    | Мах                                                | Unit |

|-----|-------------------|-------------------|--------------------------------------------------------|----------------------------------------------------|------|

| UA1 | Transmit Bit Time | t <sub>Tbit</sub> | 1/F <sub>baud_rate</sub> 1 -<br>T <sub>ref_clk</sub> 2 | 1/F <sub>baud_rate</sub> +<br>T <sub>ref_clk</sub> | _    |

| Table 83 | <b>RS-232 Serial Mode</b> | Transmit Timing  | Parameters |

|----------|---------------------------|------------------|------------|

|          | IND-ZUZ UCHAI WOUC        | manishing mining | Falameters |

<sup>1</sup> F<sub>baud\_rate</sub>: Baud rate frequency. The maximum baud rate the UART can support is (*ipg\_perclk* frequency)/16.

<sup>2</sup> T<sub>ref clk</sub>: The period of UART reference clock *ref\_clk* (*ipg\_perclk* after RFDIV divider).

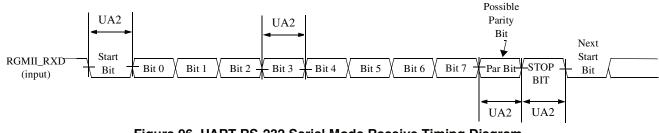

## 4.11.19.2.2 UART Receiver

1

Figure 96 depicts the RS-232 serial mode receive timing with 8 data bit/1 stop bit format. Table 84 lists serial mode receive timing characteristics.

Figure 96. UART RS-232 Serial Mode Receive Timing Diagram

| Table 84. | RS-232 Seria | al Mode Recei | ive Timing Parameters |

|-----------|--------------|---------------|-----------------------|

|-----------|--------------|---------------|-----------------------|

| ID  | Parameter                     | Symbol            | Min                                                                         | Мах                                                            | Unit |

|-----|-------------------------------|-------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------|------|

| UA2 | Receive Bit Time <sup>1</sup> | t <sub>Rbit</sub> | 1/F <sub>baud_rate</sub> <sup>2</sup> - 1/(16<br>x F <sub>baud_rate</sub> ) | 1/F <sub>baud_rate</sub> +<br>1/(16 x F <sub>baud_rate</sub> ) | —    |

<sup>1</sup> The UART receiver can tolerate 1/(16 x F<sub>baud\_rate</sub>) tolerance in each bit. But accumulation tolerance in one frame must not exceed 3/(16 x F<sub>baud\_rate</sub>).

<sup>2</sup> F<sub>baud rate</sub>: Baud rate frequency. The maximum baud rate the UART can support is (*ipg\_perclk* frequency)/16.

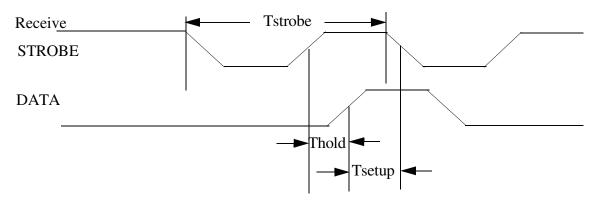

## 4.11.20.2 Receive Timing

Figure 100. USB HSIC Receive Waveform

| Table 88. U | JSB HSIC Receiv | ve Parameters <sup>1</sup> |

|-------------|-----------------|----------------------------|

|-------------|-----------------|----------------------------|

| Name    | Parameter                       | Min   | Max   | Unit | Comment                        |

|---------|---------------------------------|-------|-------|------|--------------------------------|

| Tstrobe | strobe period                   | 4.166 | 4.167 | ns   |                                |

| Thold   | data hold time                  | 300   |       | ps   | Measured at 50% point          |

| Tsetup  | data setup time                 | 365   |       | ps   | Measured at 50% point          |

| Tslew   | strobe/data rising/falling time | 0.7   | 2     | V/ns | Averaged from 30% – 70% points |

<sup>1</sup> The timings in the table are guaranteed when:

-AC I/O voltage is between 0.9x to 1x of the I/O supply

-DDR\_SEL configuration bits of the I/O are set to (10)b

# 4.11.21 USB PHY Parameters

This section describes the USB-OTG PHY and the USB Host port PHY parameters.

The USB PHY meets the electrical compliance requirements defined in the Universal Serial Bus Revision 2.0 OTG, USB Host with the amendments below (On-The-Go and Embedded Host Supplement to the USB Revision 2.0 Specification is not applicable to Host port).

- USB ENGINEERING CHANGE NOTICE

- Title: 5V Short Circuit Withstand Requirement Change

- Applies to: Universal Serial Bus Specification, Revision 2.0

- Errata for USB Revision 2.0 April 27, 2000 as of 12/7/2000

- USB ENGINEERING CHANGE NOTICE

- Title: Pull-up/Pull-down resistors

- Applies to: Universal Serial Bus Specification, Revision 2.0

- USB ENGINEERING CHANGE NOTICE

- Title: Suspend Current Limit Changes

- Applies to: Universal Serial Bus Specification, Revision 2.0

**Boot Mode Configuration**

| Pin      | Direction at Reset | eFuse Name   | Details                                                                             |  |  |

|----------|--------------------|--------------|-------------------------------------------------------------------------------------|--|--|

| EIM_DA0  | Input              | BOOT_CFG1[0] | Boot Options, Pin value overrides fuse                                              |  |  |

| EIM_DA1  | Input              | BOOT_CFG1[1] | settings for BT_FUSE_SEL = '0'. Signal<br>Configuration as Fuse Override Input at   |  |  |

| EIM_DA2  | Input              | BOOT_CFG1[2] | Power Up. These are special I/O lines that control the boot up configuration during |  |  |

| EIM_DA3  | Input              | BOOT_CFG1[3] | product development. In production, the                                             |  |  |

| EIM_DA4  | Input              | BOOT_CFG1[4] | boot configuration can be controlled by fuses.                                      |  |  |

| EIM_DA5  | Input              | BOOT_CFG1[5] |                                                                                     |  |  |

| EIM_DA6  | Input              | BOOT_CFG1[6] |                                                                                     |  |  |

| EIM_DA7  | Input              | BOOT_CFG1[7] |                                                                                     |  |  |

| EIM_DA8  | Input              | BOOT_CFG2[0] |                                                                                     |  |  |

| EIM_DA9  | Input              | BOOT_CFG2[1] |                                                                                     |  |  |

| EIM_DA10 | Input              | BOOT_CFG2[2] |                                                                                     |  |  |

| EIM_DA11 | Input              | BOOT_CFG2[3] |                                                                                     |  |  |

| EIM_DA12 | Input              | BOOT_CFG2[4] |                                                                                     |  |  |

| EIM_DA13 | Input              | BOOT_CFG2[5] |                                                                                     |  |  |

| EIM_DA14 | Input              | BOOT_CFG2[6] |                                                                                     |  |  |

| EIM_DA15 | Input              | BOOT_CFG2[7] |                                                                                     |  |  |

| EIM_A16  | Input              | BOOT_CFG3[0] |                                                                                     |  |  |

| EIM_A17  | Input              | BOOT_CFG3[1] |                                                                                     |  |  |

| EIM_A18  | Input              | BOOT_CFG3[2] |                                                                                     |  |  |

| EIM_A19  | Input              | BOOT_CFG3[3] |                                                                                     |  |  |

| EIM_A20  | Input              | BOOT_CFG3[4] |                                                                                     |  |  |

| EIM_A21  | Input              | BOOT_CFG3[5] |                                                                                     |  |  |

| EIM_A22  | Input              | BOOT_CFG3[6] |                                                                                     |  |  |

| EIM_A23  | Input              | BOOT_CFG3[7] |                                                                                     |  |  |

| EIM_A24  | Input              | BOOT_CFG4[0] |                                                                                     |  |  |

| EIM_WAIT | Input              | BOOT_CFG4[1] |                                                                                     |  |  |

| EIM_LBA  | Input              | BOOT_CFG4[2] |                                                                                     |  |  |

| EIM_EB0  | Input              | BOOT_CFG4[3] |                                                                                     |  |  |

| EIM_EB1  | Input              | BOOT_CFG4[4] |                                                                                     |  |  |

| EIM_RW   | Input              | BOOT_CFG4[5] |                                                                                     |  |  |

| EIM_EB2  | Input              | BOOT_CFG4[6] |                                                                                     |  |  |

| EIM_EB3  | Input              | BOOT_CFG4[7] |                                                                                     |  |  |

## Table 89. Fuses and Associated Pins Used for Boot (continued)

NOTES:

1. ALL DIMENSIONS IN MILLIMETERS.

2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

$\$  MAXIMUM SOLDER BALL DIAMETER MEASURED PARALLEL TO DATUM A.

DATUM A, THE SEATING PLANE, IS DETERMINED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS.

$\label{eq:parallelism}$  measurement shall exclude any effect of mark on top surface of package.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OUTLINE |                          | PRINT VERSION NOT TO SCALE |             |

|---------------------------------------------------------|--------------------|--------------------------|----------------------------|-------------|

| TITLE: PBGA, LOW PROFILE,                               |                    | DOCUMENT NO: 98ASA00404D |                            | REV: O      |

| FINE PITCH, 624 I/O,                                    |                    | CASE NUMBER: 2240-01     |                            | 27 SEP 2011 |

| 21 X 21 PKG, 0.8 MM PITCH (MAP)                         |                    | STANDARD: NON-JEDEC      |                            |             |

### Figure 101. 21 x 21 mm BGA, Case 2240 Package Top, Bottom, and Side Views