Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | HC08                                                        |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 8MHz                                                        |

| Connectivity               | SPI, USB                                                    |

| Peripherals                | LED, LVD, POR, PWM                                          |

| Number of I/O              | 29                                                          |

| Program Memory Size        | 32KB (32K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 1K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                 |

| Data Converters            | -                                                           |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                             |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 48-LQFP                                                     |

| Supplier Device Package    | 48-LQFP (7x7)                                               |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mchc908jw32fae |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **List of Chapters**

\_\_\_\_\_

| Chapter 1 General Description                                 |

|---------------------------------------------------------------|

| Chapter 2 Memory                                              |

| Chapter 3 Configuration Registers (CONFIG)41                  |

| Chapter 4 Central Processor Unit (CPU)45                      |

| Chapter 5 Clock Generator Module (CGM)                        |

| Chapter 6 System Integration Module (SIM)75                   |

| Chapter 7 Monitor Mode (MON)                                  |

| Chapter 8 Timer Interface Module (TIM)107                     |

| Chapter 9 Timebase Module (TBM)123                            |

| Chapter 10 Serial Peripheral Interface Module (SPI)           |

| Chapter 11 USB 2.0 FS Module147                               |

| Chapter 12 PS2 Clock Generator (PS2CLK)163                    |

| Chapter 13 Input/Output (I/O) Ports167                        |

| Chapter 14 External Interrupt (IRQ)185                        |

| Chapter 15 Keyboard Interrupt Module (KBI)                    |

| Chapter 16 Computer Operating Properly (COP)197               |

| Chapter 17 Low-Voltage Inhibit (LVI)                          |

| Chapter 18 Break Module (BRK)                                 |

| Chapter 19 Electrical Specifications                          |

| Chapter 20 Ordering Information and Mechanical Specifications |

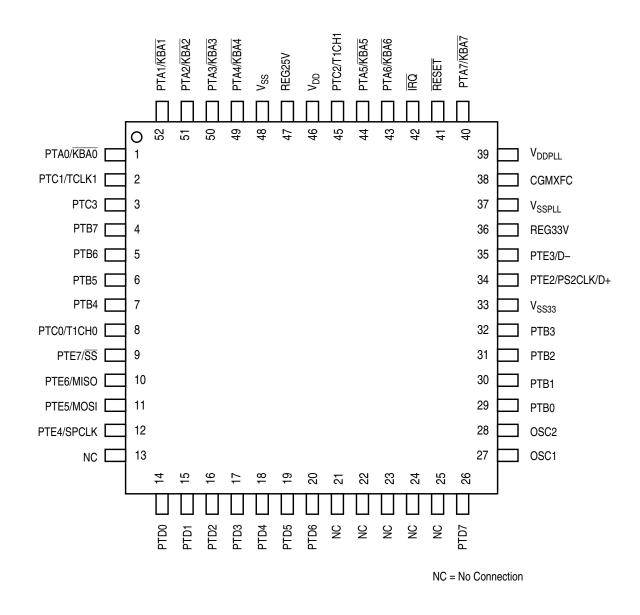

# **1.4 Pin Assignments**

Figure 1-2. 52-Pin LQFP Pin Assignment

#### Memory

Table 2-1 is a list of vector locations.

| Vector  | Vector | Address | Vector                          |  |  |  |  |  |

|---------|--------|---------|---------------------------------|--|--|--|--|--|

| Lowest  | IF15   | \$FFDE  | Timebase Vector (High)          |  |  |  |  |  |

| ▲       |        | \$FFDF  | Timebase Vector (Low)           |  |  |  |  |  |

| T       | IF14   | \$FFE0  | Keyboard Vector (High)          |  |  |  |  |  |

|         |        | \$FFE1  | Keyboard Vector (Low)           |  |  |  |  |  |

|         | IF13   | \$FFE2  | SPI Transmit Vector (High)      |  |  |  |  |  |

|         | 11 15  | \$FFE3  | SPI Transmit Vector (Low)       |  |  |  |  |  |

|         | IF12   | \$FFE4  | SPI Receive Vector (High)       |  |  |  |  |  |

|         | 11 12  | \$FFE5  | SPI Receive Vector (Low)        |  |  |  |  |  |

|         | IF11   | \$FFE6  | Reserved                        |  |  |  |  |  |

|         |        | \$FFE7  | Reserved                        |  |  |  |  |  |

|         | IF10   | \$FFE8  | Reserved                        |  |  |  |  |  |

|         | IFIO   | \$FFE9  | Reserved                        |  |  |  |  |  |

|         | IF9    | \$FFEA  | Reserved                        |  |  |  |  |  |

|         | 11-9   | \$FFEB  | Reserved                        |  |  |  |  |  |

|         | IF8    | \$FFEC  | PS2 Interrupt Vector (High)     |  |  |  |  |  |

|         |        | \$FFED  | PS2 Interrupt Vector (Low)      |  |  |  |  |  |

|         | IF7    | \$FFEE  | Timer 1 Overflow Vector (High)  |  |  |  |  |  |

|         |        | \$FFEF  | Timer 1 Overflow Vector (Low)   |  |  |  |  |  |

|         | IF6    | \$FFF0  | Timer 1 Channel 1 Vector (High) |  |  |  |  |  |

|         |        | \$FFF1  | Timer 1 Channel 1 Vector (Low)  |  |  |  |  |  |

|         | IF5    | \$FFF2  | Timer 1 Channel 0 Vector (High) |  |  |  |  |  |

|         | IFD    | \$FFF3  | Timer 1 Channel 0 Vector (Low)  |  |  |  |  |  |

|         | IF4    | \$FFF4  | PLL Vector (High)               |  |  |  |  |  |

|         | 164    | \$FFF5  | PLL Vector (Low)                |  |  |  |  |  |

|         | IF3    | \$FFF6  | IRQ Vector (High)               |  |  |  |  |  |

|         | 15     | \$FFF7  | IRQ Vector (Low)                |  |  |  |  |  |

|         | IF2    | \$FFF8  | USB Endpoint Vector (High)      |  |  |  |  |  |

|         | 11-2   | \$FFF9  | USB Endpoint Vector (Low)       |  |  |  |  |  |

|         | IF1    | \$FFFA  | USB System Vector (High)        |  |  |  |  |  |

|         | 117 1  | \$FFFB  | USB System Vector (Low)         |  |  |  |  |  |

|         |        | \$FFFC  | SWI Vector (High)               |  |  |  |  |  |

| Ļ       |        | \$FFFD  | SWI Vector (Low)                |  |  |  |  |  |

| ▼       |        | \$FFFE  | Reset Vector (High)             |  |  |  |  |  |

| Highest |        | \$FFFF  | Reset Vector (Low)              |  |  |  |  |  |

| -       |        |         |                                 |  |  |  |  |  |

Table 2-1. Vector Addresses

**Random-Access Memory (RAM)**

# 2.4 Random-Access Memory (RAM)

Addresses \$0060 through \$045F are RAM locations. The location of the stack RAM is programmable. The 16-bit stack pointer allows the stack to be anywhere in the 64k-byte memory space.

#### NOTE

For correct operation, the stack pointer must point only to RAM locations.

Within page zero are 160 bytes of RAM. Because the location of the stack RAM is programmable, all page zero RAM locations can be used for I/O control and user data or code. When the stack pointer is moved from its reset location at \$00FF out of page zero, direct addressing mode instructions can efficiently access all page zero RAM locations. Page zero RAM, therefore, provides ideal locations for frequently accessed global variables.

Before processing an interrupt, the CPU uses five bytes of the stack to save the contents of the CPU registers.

#### NOTE

For M6805 compatibility, the H register is not stacked.

During a subroutine call, the CPU uses two bytes of the stack to store the return address. The stack pointer decrements during pushes and increments during pulls.

#### NOTE

Be careful when using nested subroutines. The CPU may overwrite data in the RAM during a subroutine or during the interrupt stacking operation.

### 2.5 FLASH Memory

This sub-section describes the operation of the embedded FLASH memory. This memory can be read, programmed, and erased from a single external supply. The program and erase operations are enabled through the use of an internal charge pump.

### 2.5.1 Functional Description

The FLASH memory consists of an array of 32,768 bytes for user memory plus a block of 48 bytes for user interrupt vectors and one byte for the mask option register. *An erased bit reads as logic 1 and a programmed bit reads as a logic 0.* The FLASH memory page size is defined as 512 bytes, and is the minimum size that can be erased in a page erase operation. Program and erase operations are facilitated through control bits in FLASH control register (FLCR). The address ranges for the FLASH memory are:

- \$7000-\$EFFF; user memory, 32,768 bytes

- \$FFD0-\$FFFF; user interrupt vectors, 48 bytes

Programming tools are available from Freescale. Contact your local Freescale representative for more information.

#### NOTE

A security feature prevents viewing of the FLASH contents.<sup>(1)</sup>

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

#### STOP — STOP Instruction Enable

STOP enables the STOP instruction.

- 1 = STOP instruction enabled

- 0 = STOP instruction treated as illegal opcode

#### COPD — COP Disable Bit

COPD disables the COP module. (See Chapter 16 Computer Operating Properly (COP).)

1 = COP module disabled

0 = COP module enabled

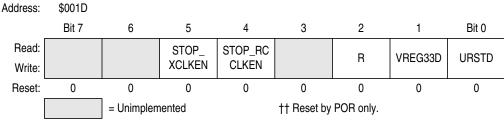

### 3.4 Configuration Register 2 (CONFIG2)

Figure 3-3. Configuration Register 2 (CONFIG2)

#### STOP\_XCLKEN — Crystal Oscillator Stop Mode Enable

Setting STOP\_XCLKEN enables the external crystal (XTAL) oscillator to continue operating during stop mode, in the other words, SIMOSCEN hold high during STOP mode. When this bit is cleared, the external XTAL oscillator will be disabled during stop mode. Reset clears this bit.

1 = XTAL oscillator enabled during stop mode

0 = XTAL oscillator disabled during stop mode

#### STOP\_RCCLKEN — RC clock Stop Mode Enable

Setting STOP\_RCCLKEN enables the internal RC clock to continue operating during STOP mode. When this bit is cleared, the internal RC clock will be disabled during STOP mode. Reset clears this bit.

- 1 = Internal RC clock enabled during stop mode

- 0 = Internal RC clock disable during stop mode

#### VREG33D — 3.3V USB Regulator Disable Bit

VREG33D disables the USB 3.3V regulator completely.

1 = VREG33 regulator is disabled

0 = VREG33 regulator is enabled

#### URSTD — USB Reset Disable Bit

URSTD disables the USB reset signal generating an internal reset to the CPU and internal registers. Instead, it will generate an interrupt request to CPU.

1 = USB reset generates a interrupt request to CPU

0 = USB reset generates a chip reset

56

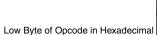

### Table 4-2. Opcode Map

|            | Bit Manipulation Branch Read-Modify-Write Control Register/Memory |                     |                    |                    |                     |                     |                     |                    |                    |                    |                   |                   |                   |                   |                   |                   |                   |                   |                  |

|------------|-------------------------------------------------------------------|---------------------|--------------------|--------------------|---------------------|---------------------|---------------------|--------------------|--------------------|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|

|            | Bit Mani                                                          |                     | Branch             |                    |                     |                     |                     |                    |                    | Cor                |                   |                   |                   |                   |                   | r/Memory          |                   |                   |                  |

| N          | DIR                                                               | DIR                 | REL                | DIR                | INH                 | INH                 | IX1                 | SP1                | IX                 | INH                | INH               | IMM               | DIR               | EXT               | IX2               | SP2               | IX1               | SP1               | IX               |

| MSB<br>LSB | 0                                                                 | 1                   | 2                  | 3                  | 4                   | 5                   | 6                   | 9E6                | 7                  | 8                  | 9                 | Α                 | В                 | с                 | D                 | 9ED               | Е                 | 9EE               | F                |

| 0          |                                                                   | 4<br>BSET0<br>2 DIR |                    |                    |                     |                     | 4<br>NEG<br>2 IX1   |                    | 3<br>NEG<br>1 IX   |                    | 3<br>BGE<br>2 REL |                   |                   |                   |                   | 5<br>SUB<br>4 SP2 |                   | 4<br>SUB<br>3 SP1 | 2<br>SUB<br>1 IX |

| 1          | 5<br>BRCLR0<br>3 DIR                                              | 4<br>BCLR0<br>2 DIR |                    | 5<br>CBEQ<br>3 DIR | 4<br>CBEQA<br>3 IMM |                     | 5<br>CBEQ<br>3 IX1+ | 6<br>CBEQ<br>4 SP1 | 4<br>CBEQ<br>2 IX+ | 4<br>RTS<br>1 INH  |                   |                   |                   | 4<br>CMP<br>3 EXT |                   | 5<br>CMP<br>4 SP2 |                   | 4<br>CMP<br>3 SP1 | 2<br>CMP<br>1 IX |

| 2          | 5<br>BRSET1<br>3 DIR                                              | 4<br>BSET1<br>2 DIR | 3<br>BHI<br>2 REL  |                    | 5<br>MUL<br>1 INH   | DIV                 | 3<br>NSA<br>1 INH   |                    | 2<br>DAA<br>1 INH  |                    | 3<br>BGT<br>2 REL | 2<br>SBC<br>2 IMM | 3<br>SBC<br>2 DIR | 4<br>SBC<br>3 EXT | 4<br>SBC<br>3 IX2 | 5<br>SBC<br>4 SP2 | 3<br>SBC<br>2 IX1 | 4<br>SBC<br>3 SP1 | 2<br>SBC<br>1 IX |

| 3          | 5<br>BRCLR1<br>3 DIR                                              | 4<br>BCLR1<br>2 DIR | BLS<br>2 REL       | 4<br>COM<br>2 DIR  | 1<br>COMA<br>1 INH  | 1<br>COMX<br>1 INH  | 4<br>COM<br>2 IX1   | 5<br>COM<br>3 SP1  |                    | 9<br>SWI<br>1 INH  | 3<br>BLE<br>2 REL | CPX<br>2 IMM      | 3<br>CPX<br>2 DIR | 4<br>CPX<br>3 EXT | 4<br>CPX<br>3 IX2 | 5<br>CPX<br>4 SP2 | 3<br>CPX<br>2 IX1 | 4<br>CPX<br>3 SP1 | 2<br>CPX<br>1 IX |

| 4          | 5<br>BRSET2<br>3 DIR                                              | 4<br>BSET2<br>2 DIR | BCC<br>2 REL       | 4<br>LSR<br>2 DIR  |                     | 1<br>LSRX<br>1 INH  | 4<br>LSR<br>2 IX1   | 5<br>LSR<br>3 SP1  | 3<br>LSR<br>1 IX   | 2<br>TAP<br>1 INH  |                   | 2<br>AND<br>2 IMM |                   | 4<br>AND<br>3 EXT | 4<br>AND<br>3 IX2 | 5<br>AND<br>4 SP2 | 3<br>AND<br>2 IX1 | 4<br>AND<br>3 SP1 | 2<br>AND<br>1 IX |

| 5          | 5<br>BRCLR2<br>3 DIR                                              | 4<br>BCLR2<br>2 DIR | BCS<br>2 REL       | 4<br>STHX<br>2 DIR | 3<br>LDHX<br>3 IMM  | 4<br>LDHX<br>2 DIR  | 3<br>CPHX<br>3 IMM  |                    | 4<br>CPHX<br>2 DIR | 1<br>TPA<br>1 INH  | 2<br>TSX<br>1 INH | BIT<br>2 IMM      | 3<br>BIT<br>2 DIR | 4<br>BIT<br>3 EXT | 4<br>BIT<br>3 IX2 | 5<br>BIT<br>4 SP2 | 3<br>BIT<br>2 IX1 | 4<br>BIT<br>3 SP1 | BIT<br>1 IX      |

| 6          | 5<br>BRSET3<br>3 DIR                                              | 4<br>BSET3<br>2 DIR | BNE<br>2 REL       | 4<br>ROR<br>2 DIR  | 1<br>RORA<br>1 INH  | 1<br>RORX<br>1 INH  | 4<br>ROR<br>2 IX1   | 5<br>ROR<br>3 SP1  | 3<br>ROR<br>1 IX   | 2<br>PULA<br>1 INH |                   | 2<br>LDA<br>2 IMM | 3<br>LDA<br>2 DIR | 4<br>LDA<br>3 EXT | 4<br>LDA<br>3 IX2 | 5<br>LDA<br>4 SP2 | 3<br>LDA<br>2 IX1 | 4<br>LDA<br>3 SP1 | 2<br>LDA<br>1 IX |

| 7          | 5<br>BRCLR3<br>3 DIR                                              | 4<br>BCLR3<br>2 DIR | 3<br>BEQ<br>2 REL  | 4<br>ASR<br>2 DIR  | 1<br>ASRA<br>1 INH  | 1<br>ASRX<br>1 INH  | 4<br>ASR<br>2 IX1   | 5<br>ASR<br>3 SP1  | 3<br>ASR<br>1 IX   | 2<br>PSHA<br>1 INH | 1<br>TAX<br>1 INH | AIS<br>2 IMM      | 3<br>STA<br>2 DIR | 4<br>STA<br>3 EXT | 4<br>STA<br>3 IX2 | 5<br>STA<br>4 SP2 | 3<br>STA<br>2 IX1 | 4<br>STA<br>3 SP1 | 2<br>STA<br>1 IX |

| 8          | 5<br>BRSET4<br>3 DIR                                              | 4<br>BSET4<br>2 DIR | 3<br>BHCC<br>2 REL | 4<br>LSL<br>2 DIR  | 1<br>LSLA<br>1 INH  | 1<br>LSLX<br>1 INH  | 4<br>LSL<br>2 IX1   | 5<br>LSL<br>3 SP1  | 3<br>LSL<br>1 IX   | 2<br>PULX<br>1 INH | 1<br>CLC<br>1 INH | 2<br>EOR<br>2 IMM | 3<br>EOR<br>2 DIR | 4<br>EOR<br>3 EXT | 4<br>EOR<br>3 IX2 | 5<br>EOR<br>4 SP2 | 3<br>EOR<br>2 IX1 | 4<br>EOR<br>3 SP1 | 2<br>EOR<br>1 IX |

| 9          | 5<br>BRCLR4<br>3 DIR                                              | 4<br>BCLR4<br>2 DIR | 3<br>BHCS<br>2 REL | 4<br>ROL<br>2 DIR  | 1<br>ROLA<br>1 INH  | 1<br>ROLX<br>1 INH  | 4<br>ROL<br>2 IX1   | 5<br>ROL<br>3 SP1  | 3<br>ROL<br>1 IX   | 2<br>PSHX<br>1 INH | 1<br>SEC<br>1 INH | ADC<br>2 IMM      | 3<br>ADC<br>2 DIR | 4<br>ADC<br>3 EXT | 4<br>ADC<br>3 IX2 | ADC<br>4 SP2      | 3<br>ADC<br>2 IX1 | 4<br>ADC<br>3 SP1 | ADC<br>1 IX      |

| A          | 5<br>BRSET5<br>3 DIR                                              | 4<br>BSET5<br>2 DIR | 3<br>BPL<br>2 REL  | 4<br>DEC<br>2 DIR  | 1<br>DECA<br>1 INH  | 1<br>DECX<br>1 INH  | 4<br>DEC<br>2 IX1   | 5<br>DEC<br>3 SP1  | 3<br>DEC<br>1 IX   | 2<br>PULH<br>1 INH | 2<br>CLI<br>1 INH | 2<br>ORA<br>2 IMM | 3<br>ORA<br>2 DIR | 4<br>ORA<br>3 EXT | 4<br>ORA<br>3 IX2 | 5<br>ORA<br>4 SP2 | 3<br>ORA<br>2 IX1 | 4<br>ORA<br>3 SP1 | ORA<br>1 IX      |

| В          | 5<br>BRCLR5<br>3 DIR                                              | 4<br>BCLR5<br>2 DIR | 3<br>BMI<br>2 REL  | 5<br>DBNZ<br>3 DIR | 3<br>DBNZA<br>2 INH | 3<br>DBNZX<br>2 INH | 5<br>DBNZ<br>3 IX1  | 6<br>DBNZ<br>4 SP1 |                    | 2<br>PSHH<br>1 INH | 2<br>SEI<br>1 INH | 2<br>ADD<br>2 IMM | 3<br>ADD<br>2 DIR | 4<br>ADD<br>3 EXT | 4<br>ADD<br>3 IX2 | 5<br>ADD<br>4 SP2 | 3<br>ADD<br>2 IX1 | 4<br>ADD<br>3 SP1 | 2<br>ADD<br>1 IX |

| с          | 5<br>BRSET6<br>3 DIR                                              | 4<br>BSET6<br>2 DIR | BMC<br>2 REL       | 4<br>INC<br>2 DIR  | 1<br>INCA<br>1 INH  | 1<br>INCX<br>1 INH  | 4<br>INC<br>2 IX1   | 5<br>INC<br>3 SP1  | 3<br>INC<br>1 IX   | 1<br>CLRH<br>1 INH | 1<br>RSP<br>1 INH |                   | 2<br>JMP<br>2 DIR | 3<br>JMP<br>3 EXT | 4<br>JMP<br>3 IX2 |                   | 3<br>JMP<br>2 IX1 |                   | 2<br>JMP<br>1 IX |

| D          | 5<br>BRCLR6<br>3 DIR                                              | 4<br>BCLR6<br>2 DIR | 3<br>BMS<br>2 REL  | 3<br>TST<br>2 DIR  |                     | 1<br>TSTX<br>1 INH  | 3<br>TST<br>2 IX1   | 4<br>TST<br>3 SP1  |                    |                    | 1<br>NOP<br>1 INH | 4<br>BSR<br>2 REL | 4<br>JSR<br>2 DIR | 5<br>JSR<br>3 EXT | 6<br>JSR<br>3 IX2 |                   | 5<br>JSR<br>2 IX1 |                   | 4<br>JSR<br>1 IX |

| E          | 5<br>BRSET7<br>3 DIR                                              | 4<br>BSET7<br>2 DIR | 3<br>BIL<br>2 REL  |                    | 5<br>MOV<br>3 DD    | 4<br>MOV<br>2 DIX+  | 4<br>MOV<br>3 IMD   |                    | 4<br>MOV<br>2 IX+D | 1<br>STOP<br>1 INH | *                 | 2<br>LDX<br>2 IMM | 3<br>LDX<br>2 DIR | 4<br>LDX<br>3 EXT | 4<br>LDX<br>3 IX2 | 5<br>LDX<br>4 SP2 | 3<br>LDX<br>2 IX1 | 4<br>LDX<br>3 SP1 | 2<br>LDX<br>1 IX |

| F          | 5<br>BRCLR7                                                       | 4<br>BCLR7<br>2 DIR | 3<br>BIH<br>2 REL  | 3<br>CLR<br>2 DIR  | 1<br>CLRA<br>1 INH  | 1<br>CLRX<br>1 INH  | 3<br>CLR<br>2 IX1   | 4<br>CLR<br>3 SP1  | 2<br>CLR<br>1 IX   | 1<br>WAIT<br>1 INH | 1<br>TXA<br>1 INH | AIX<br>2 IMM      | 3<br>STX<br>2 DIR | STX<br>3 EXT      | 4<br>STX<br>3 IX2 | STX<br>4 SP2      | 3<br>STX<br>2 IX1 | 4<br>STX<br>3 SP1 | STX<br>1 IX      |

MC68HC908JW32 Data Sheet, Rev. 6

- INH Inherent IMM Immediate DIR Direct EXT Extended

- REL Relative IX Indexed, No Offset

- Indexed, 8-Bit Offset Indexed, 16-Bit Offset IX1 IX2

- DD Direct-Direct IMD Immediate-Direct IX+D Indexed-Direct DIX+ Direct-Indexed

- SP1 Stack Pointer, 8-Bit Offset SP2 Stack Pointer, 16-Bit Offset IX+ Indexed, No Offset with

- Post Increment IX1+ Indexed, 1-Byte Offset with Post Increment

0 High Byte of Opcode in Hexadecimal

MSB

LSB

0

5 Cycles BRSET0 Opcode Mnemonic 3 DIR Number of Bytes / Addressing Mode

- \*Pre-byte for stack pointer indexed instructions

- Freescale Semiconductor

# Chapter 5 Clock Generator Module (CGM)

## 5.1 Introduction

This section describes the clock generator module (CGM). The CGM generates the base clock signal, CGMOUT, which is based on either the oscillator clock divided by two or the divided phase-locked loop (PLL) clock, CGMVCLK, divided by three. CGMOUT is the clock from which the SIM derives the system clocks, including the bus clock, which is at a frequency of CGMOUT 2.

The PLL is a frequency generator designed for use with a crystal (4MHz) to generate a base frequency and dividing to a maximum bus frequency of 8MHz.

## 5.2 Features

Features of the CGM include:

- Phase-locked loop with output frequency in integer multiples of an integer dividend of the crystal reference

- Low-frequency crystal operation with low-power operation and high-output frequency resolution

- Programmable prescaler for power-of-two increases in frequency

- Programmable hardware voltage-controlled oscillator (VCO) for low-jitter operation

- Automatic bandwidth control mode for low-jitter operation

- Automatic frequency lock detector

- CPU interrupt on entry or exit from locked condition

- Configuration register bit to allow oscillator operation during stop mode

### 5.3 Functional Description

The CGM consists of three major sub-modules:

- Oscillator module The oscillator module generates the constant reference frequency clock, CGMRCLK (buffered CGMXCLK).

- Phase-locked loop (PLL) The PLL generates the programmable VCO frequency clock, CGMVCLK.

- Base clock selector circuit This software-controlled circuit selects either CGMXCLK divided by two or the divided VCO clock, CGMVCLK, divided by three as the base clock, CGMOUT. The SIM derives the system clocks from either CGMOUT or CGMXCLK.

Figure 5-1 shows the structure of the CGM.

Figure 5-2 is a summary of the CGM registers.

#### **Clock Generator Module (CGM)**

#### **BCS** — Base Clock Select Bit

This read/write bit selects either the oscillator output, CGMXCLK, or the VCO clock, CGMVCLK, as the source of the CGM output, CGMOUT. CGMOUT frequency is one-half the frequency of the selected clock. BCS cannot be set while the PLLON bit is clear. After toggling BCS, it may take up to three CGMXCLK and three CGMVCLK cycles to complete the transition from one source clock to the other. During the transition, CGMOUT is held in stasis. (See 5.3.8 Base Clock Selector Circuit.) Reset clears the BCS bit.

1 = CGMVCLK divided by three drives CGMOUT

0 = CGMXCLK divided by two drives CGMOUT

#### NOTE

PLLON and BCS have built-in protection that prevents the base clock selector circuit from selecting the VCO clock as the source of the base clock if the PLL is off. Therefore, PLLON cannot be cleared when BCS is set, and BCS cannot be set when PLLON is clear. If the PLL is off (PLLON = 0), selecting CGMVCLK requires two writes to the PLL control register. (See 5.3.8 Base Clock Selector Circuit.)

#### PRE1 and PRE0 — Prescaler Program Bits

These read/write bits control a prescaler that selects the prescaler power-of-two multiplier, P. (See 5.3.3 PLL Circuits and 5.3.6 Programming the PLL.) PRE1 and PRE0 cannot be written when the PLLON bit is set. Reset clears these bits.

These prescaler bits affects the relationship between the VCO clock and the final system bus clock.

| PRE1 and PRE0 | Р | Prescaler Multiplier |

|---------------|---|----------------------|

| 00            | 0 | 1                    |

| 01            | 1 | 2                    |

| 10            | 2 | 4                    |

| 11            | 3 | 8                    |

Table 5-2. PRE1 and PRE0 Programming

#### VPR1 and VPR0 — VCO Power-of-Two Range Select Bits

These read/write bits control the VCO's hardware power-of-two range multiplier E that, in conjunction with L (See 5.3.3 PLL Circuits, 5.3.6 Programming the PLL, and 5.5.4 PLL VCO Range Select Register.) controls the hardware center-of-range frequency,  $f_{VRS}$ . VPR1:VPR0 cannot be written when the PLLON bit is set. Reset clears these bits.

Table 5-3. VPR1 and VPR0 Programming

| VPR1 and VPR0 | E | VCO Power-of-Two<br>Range Multiplier |

|---------------|---|--------------------------------------|

| 00            | 0 | 1                                    |

| 01            | 1 | 2                                    |

| 10            | 2 | 4                                    |

NOTE: Do not program E to a value of 3.

# Chapter 6 System Integration Module (SIM)

## 6.1 Introduction

•

This section describes the system integration module (SIM). Together with the CPU, the SIM controls all MCU activities. A block diagram of the SIM is shown in Figure 6-1. Figure 6-2 is a summary of the SIM input/output (I/O) registers. The SIM is a system state controller that coordinates CPU and exception timing. The SIM is responsible for:

- Bus clock generation and control for CPU and peripherals:

- Stop/wait/reset/break entry and recovery

- Internal clock control

- Master reset control, including power-on reset (POR) and COP timeout

- Interrupt control:

- Acknowledge timing

- Arbitration control timing

- Vector address generation

- CPU enable/disable timing

Table 6-1 shows the internal signal names used in this section.

#### Table 6-1. Signal Name Conventions

| Signal Name | Description                                                                                |  |  |  |  |

|-------------|--------------------------------------------------------------------------------------------|--|--|--|--|

| ICLK        | Internal RC oscillator clock                                                               |  |  |  |  |

| CGMXCLK     | Selected oscillator clock from oscillator module                                           |  |  |  |  |

| CGMVCLK     | PLL VCO output and the divided PLL output                                                  |  |  |  |  |

| CGMOUT      | CGMVCLK-based or oscillator-based clock output from CGM module<br>(Bus clock = CGMOUT ÷ 2) |  |  |  |  |

| IAB         | Internal address bus                                                                       |  |  |  |  |

| IDB         | Internal data bus                                                                          |  |  |  |  |

| PORRST      | Signal from the power-on reset module to the SIM                                           |  |  |  |  |

| IRST        | Internal reset signal                                                                      |  |  |  |  |

| R/W         | Read/write signal                                                                          |  |  |  |  |

|  | 7 |  |

|--|---|--|

|  |   |  |

|  |   |  |

|  |   |  |

System Integration Module (SIM)

| IAB | WAIT ADDR | WAIT ADDR + 1  | SAME   | X    | SAME |

|-----|-----------|----------------|--------|------|------|

| IDB |           | JS DATA X NEXT | OPCODE | SAME | SAME |

| R/W |           | у              |        |      |      |

NOTE: Previous data can be operand data or the WAIT opcode, depending on the last instruction.

Figure 6-15. Wait Mode Entry Timing

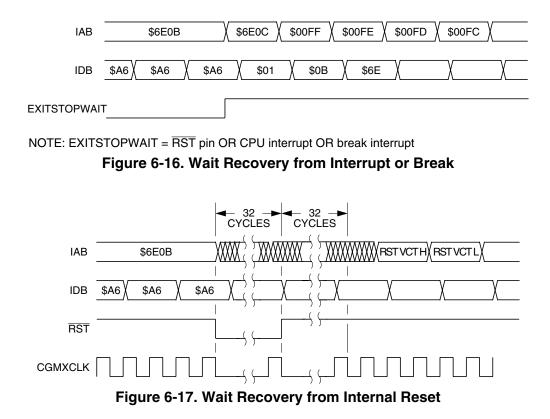

Figure 6-16 and Figure 6-17 show the timing for WAIT recovery.

#### **ROM-Resident Routines**

|                  |                         | ORG          | RAM               |        |                                                                                                        |

|------------------|-------------------------|--------------|-------------------|--------|--------------------------------------------------------------------------------------------------------|

| START_           |                         | DS.W         | 1<br>1<br>1<br>64 | ;<br>; | Indicates 4x bus frequency<br>Data size to be programmed<br>FLASH start address<br>Reserved data array |

| PRGRNG<br>FLASH_ | E<br>START              | EQU<br>EQU   | \$FE10<br>\$EE00  |        |                                                                                                        |

| INITIA<br>MAIN:  | MOV<br>LDHX             | #20,<br>#64, | DATAS:<br>START   | PD     |                                                                                                        |

| HAIN:            | BSR<br>:<br>LDHX<br>JSR |              |                   | 1      |                                                                                                        |

### 7.5.2 ERARNGE

ERARNGE is used to erase a range of locations in FLASH.

| Routine Name               | ERARNGE                                                                                             |  |  |  |  |

|----------------------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|

| <b>Routine Description</b> | Erase a page or the entire array                                                                    |  |  |  |  |

| Calling Address            | \$FE13                                                                                              |  |  |  |  |

| Stack Used                 | 10 bytes                                                                                            |  |  |  |  |

| Data Block Format          | Bus speed (BUS_SPD)<br>Data size (DATASIZE)<br>Starting address (ADDRH)<br>Starting address (ADDRL) |  |  |  |  |

#### Table 7-12. ERARNGE Routine

There are two sizes of erase ranges: a page or the entire array. The ERARNGE will erase the page (512 consecutive bytes) in FLASH specified by the address ADDRH:ADDRL. This address can be any address within the page. Calling ERARNGE with ADDRH:ADDRL equal to \$FFFF will erase the entire FLASH array (mass erase). Therefore, care must be taken when calling this routine to prevent an accidental mass erase.

The ERARNGE routine do not use a data array. The DATASIZE byte is a dummy byte that is also not used.

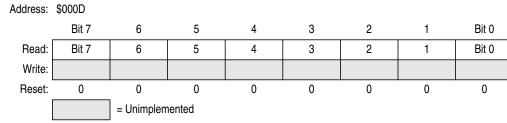

### 8.9.3 TIM Counter Modulo Registers

The read/write TIM modulo registers contain the modulo value for the TIM counter. When the TIM counter reaches the modulo value, the overflow flag (TOF) becomes set, and the TIM counter resumes counting from \$0000 at the next timer clock. Writing to the high byte (TMODH) inhibits the TOF bit and overflow interrupts until the low byte (TMODL) is written. Reset sets the TIM counter modulo registers.

NOTE

Reset the TIM counter before writing to the TIM counter modulo registers.

### 8.9.4 TIM Channel Status and Control Registers

Each of the TIM channel status and control registers:

- Flags input captures and output compares

- Enables input capture and output compare interrupts

- Selects input capture, output compare, or PWM operation

- Selects high, low, or toggling output on output compare

- Selects rising edge, falling edge, or any edge as the active input capture trigger

- Selects output toggling on TIM overflow

- Selects 0% and 100% PWM duty cycle

- Selects buffered or unbuffered output compare/PWM operation

When ELSxB:ELSxA = 0:0, this read/write bit selects the initial output level of the TCHx pin. See Table 8-3. Reset clears the MSxA bit.

1 = Initial output level low

0 = Initial output level high

#### NOTE

Before changing a channel function by writing to the MSxB or MSxA bit, set the TSTOP and TRST bits in the TIM status and control register (TSC).

#### ELSxB and ELSxA — Edge/Level Select Bits

When channel x is an input capture channel, these read/write bits control the active edge-sensing logic on channel x.

When channel x is an output compare channel, ELSxB and ELSxA control the channel x output behavior when an output compare occurs.

When ELSxB and ELSxA are both clear, channel x is not connected to an I/O port, and pin TCHx is available as a general-purpose I/O pin. Table 8-3 shows how ELSxB and ELSxA work. Reset clears the ELSxB and ELSxA bits.

| MSxB:MSxA | ELSxB:ELSxA | Mode                                    | Configuration                                        |  |  |

|-----------|-------------|-----------------------------------------|------------------------------------------------------|--|--|

| X0        | 00          |                                         | Pin under port control;<br>initial output level high |  |  |

| X1        | 00          | Output preset                           | Pin under port control;<br>initial output level low  |  |  |

| 00        | 01          |                                         | Capture on rising edge only                          |  |  |

| 00        | 10          | Input capture Capture on falling edge o |                                                      |  |  |

| 00        | 11          |                                         | Capture on rising or<br>falling edge                 |  |  |

| 01        | 00          |                                         | Software compare only                                |  |  |

| 01        | 01          | Output compare                          | Toggle output on compare                             |  |  |

| 01        | 10          | or PWM                                  | Clear output on compare                              |  |  |

| 01        | 11          |                                         | Set output on compare                                |  |  |

| 1X        | 01          | Buffered output                         | Toggle output on compare                             |  |  |

| 1X        | 10          | compare or                              | Clear output on compare                              |  |  |

| 1X        | 11          | buffered PWM                            | Set output on compare                                |  |  |

Table 8-3. Mode, Edge, and Level Selection

#### NOTE

After iniitially enabling a TIM channel register for input capture operation, and selecting the edge sensitivity, clear CHxF to ignore any erroneous edge detection flags.

#### TOVx — Toggle On Overflow Bit

When channel x is an output compare channel, this read/write bit controls the behavior of the channel x output when the TIM counter overflows. When channel x is an input capture channel, TOVx has no effect. Reset clears the TOVx bit.

- 1 = Channel x pin toggles on TIM counter overflow

- 0 = Channel x pin does not toggle on TIM counter overflow

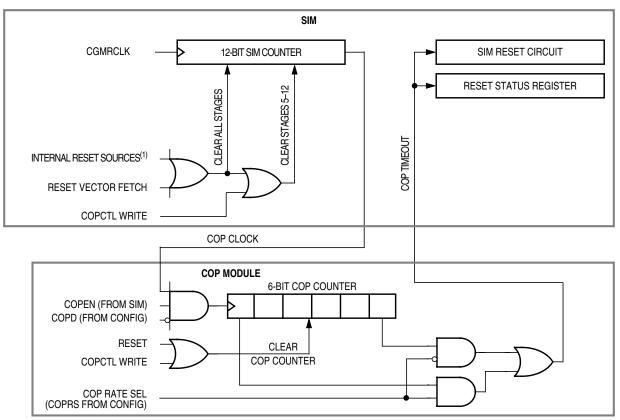

Input/Output (I/O) Ports

| Port | Bit | DDR     |        | Pin           |             |            |

|------|-----|---------|--------|---------------|-------------|------------|

|      | DIL |         | Module | Register      | Control Bit | FIII       |

|      |     |         | USB    | USBCR (\$51)  | USBEN       |            |

|      | 2   | DDRE2   | PULLUP | POCR2 (\$1B)  | PTE2P       | PTE2/D+    |

|      |     |         | PS2CLK | PS2CSR (\$19) | PS2EN       |            |

|      |     | DDRE3   | USB    | USBCR (\$51)  | USBEN       |            |

| E    | 3   |         | PULLUP | POCR2 (\$1B)  | PTE3P       | PTE3/D-    |

| E    |     |         | IRQ    | IOCR (\$1C)   | PTE3IE      |            |

|      | 4   | DDRE4   |        |               |             | PTE4/SPSCK |

|      | 5   | DDRE5   | SPI    |               | SPE         | PTE5/MOSI  |

|      | 6   | DDRE6   | OF1    | SPCR (\$4C)   | JOFE        | PTE6/MISO  |

|      | 7   | 7 DDRE7 |        |               |             | PTE7/SS    |

Table 13-1. Port Control Register Bits Summary (Continued)

### 13.2 Port A

Port A is an 8-bit general-purpose bidirectional I/O port with software configurable pullups, and it shares its pins with the keyboard interrupt module (KBI).

### 13.2.1 Port A Data Register

The port A data register contains a data latch for each of the eight port A pins.

| Address:                 | \$0000          |                     |                    |                    |                    |                    |                    |                 |  |  |  |

|--------------------------|-----------------|---------------------|--------------------|--------------------|--------------------|--------------------|--------------------|-----------------|--|--|--|

|                          | Bit 7           | 6                   | 5                  | 4                  | 3                  | 2                  | 1                  | Bit 0           |  |  |  |

| Read:<br>Write:          | PTA7            | PTA6                | PTA5               | PTA4               | PTA3               | PTA2               | PTA1               | PTA0            |  |  |  |

| Reset:                   |                 | Unaffected by reset |                    |                    |                    |                    |                    |                 |  |  |  |

| Alternative<br>Function: | KBA7            | KBA6                | KBA5               | KBA4               | KBA3               | KBA2               | KBA1               | KBA0            |  |  |  |

| Additional<br>Function:  | Optional pullup | Optional<br>pullup  | Optional<br>pullup | Optional<br>pullup | Optional<br>pullup | Optional<br>pullup | Optional<br>pullup | Optional pullup |  |  |  |

Figure 13-2. Port A Data Register (PTA)

#### PTA[7:0] — Port A Data Bits

These read/write bits are software programmable. Data direction of each port A pin is under the control of the corresponding bit in data direction register A. Reset has no effect on port A data.

#### **KBA7–KBA0** — Keyboard Interrupts

The keyboard interrupt enable bits,  $\overline{\text{KBA7}}$ – $\overline{\text{KBA0}}$ , in the keyboard interrupt enable register (KBIER), enable the port A pins as external interrupt pins and the internal pullup of the corresponding pin. (See Chapter 15 Keyboard Interrupt Module (KBI).)

#### Input/Output (I/O) Ports

PTE3 pin functions as an external interrupt when PTE3IE=1 in the IRQ option control register (IOCR) and USBEN=0 in the USB address register (USB disabled). (See 14.7 IRQ Status and Control Register.)

PTE2 pin also muxed with PS2 clock generator module. (See Chapter 12 PS2 Clock Generator (PS2CLK).)

#### D– and D+ – USB Data Pins

D- and D+ are the differential data lines used by the USB module. (See Chapter 11 USB 2.0 FS Module.)

When the USB module is enabled, PTE2/D+ and PTE3/D- function as USB data pins D- and D+. When the USB module is disabled, PTE2/D+ and PTE3/D- function as open drain high current pins for PS/2 clock and data use.

#### NOTE

PTE2/D+ pin has two programmable pullup resistors. One is used for PTE2 when the USB module is disable and another is used for D+ when the USB module is enabled.

Data direction register E (DDRE) does not affect the data direction of port E pins that are being used by the SPI module. However, the DDRE bits always determine whether reading port E returns the states of the latches or the states of the pins. (See Table 13-5 . Port C Pin Functions.)

#### **SS**, MISO, MOSI, and SPSCK — SPI Functional Pins

These are the chip select, master-input-slave-output, master-output-slave-input and clock pins for the SPI module. The SPI enable bit, SPE, in the SPI control register, SPCR, enables these pins as the SPI functional pins and overrides any control from port I/O logic. See Chapter 10 Serial Peripheral Interface Module (SPI).

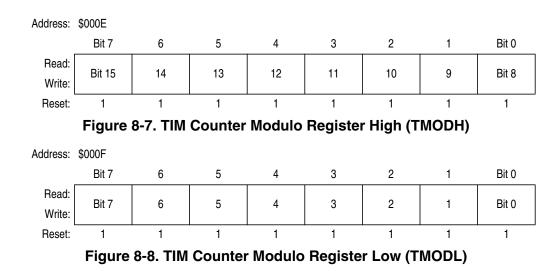

#### 13.6.2 Data Direction Register E

Data direction register E determines whether each port E pin is an input or an output. Writing a logic 1 to a DDRE bit enables the output buffer for the corresponding port E pin; a logic 0 disables the output buffer.

Figure 13-15. Data Direction Register E (DDRE)

#### DDRE[7:2] — Data Direction Register E Bits

These read/write bits control port E data direction. Reset clears DDRE[7:2], configuring all port E pins as inputs.

1 = Corresponding port E pin configured as output

0 = Corresponding port E pin configured as input

#### NOTE

Avoid glitches on port E pins by writing to the port E data register before changing data direction register E bits from 0 to 1.

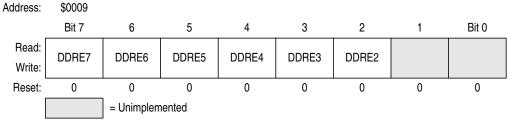

# Chapter 16 Computer Operating Properly (COP)

# 16.1 Introduction

The computer operating properly (COP) module contains a free-running counter that generates a reset if allowed to overflow. The COP module helps software recover from runaway code. Prevent a COP reset by clearing the COP counter periodically. The COP module can be disabled through the COPD bit in the CONFIG register.

### **16.2 Functional Description**

Figure 16-1 shows the structure of the COP module.

Figure 16-1. COP Block Diagram

**Computer Operating Properly (COP)**

# 16.6 Monitor Mode

The COP is disabled in monitor mode when  $V_{TST}$  is present on the  $\overline{IRQ}$  pin or on the  $\overline{RST}$  pin.

### 16.7 Low-Power Modes

The WAIT and STOP instructions put the MCU in low-power consumption standby modes.

### 16.7.1 Wait Mode

The COP remains active during wait mode. To prevent a COP reset during wait mode, periodically clear the COP counter in a CPU interrupt routine.

### 16.7.2 Stop Mode

Stop mode turns off the CGMRCLK input to the COP and clears the COP prescaler. Service the COP immediately before entering or after exiting stop mode to ensure a full COP timeout period after entering or exiting stop mode.

The STOP bit in the configuration register (CONFIG) enables the STOP instruction. To prevent inadvertently turning off the COP with a STOP instruction, disable the STOP instruction by clearing the STOP bit.

## 16.8 COP Module During Break Mode

The COP is disabled during a break interrupt when  $V_{TST}$  is present on the  $\overline{RST}$  pin.

Break Module (BRK)

#### BRKE — Break Enable Bit

This read/write bit enables breaks on break address register matches. Clear BRKE by writing a logic 0 to bit 7. Reset clears the BRKE bit.

- 1 = Breaks enabled on 16-bit address match

- 0 = Breaks disabled on 16-bit address match

#### BRKA — Break Active Bit

This read/write status and control bit is set when a break address match occurs. Writing a logic 1 to BRKA generates a break interrupt. Clear BRKA by writing a logic 0 to it before exiting the break routine. Reset clears the BRKA bit.

- 1 = (When read) Break address match

- 0 = (When read) No break address match

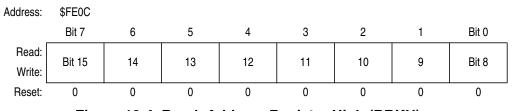

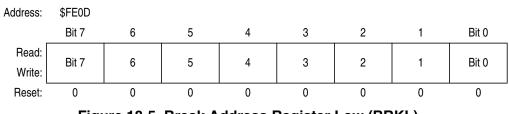

#### 18.5.2 Break Address Registers

The break address registers (BRKH and BRKL) contain the high and low bytes of the desired breakpoint address. Reset clears the break address registers.

Figure 18-4. Break Address Register High (BRKH)

Figure 18-5. Break Address Register Low (BRKL)

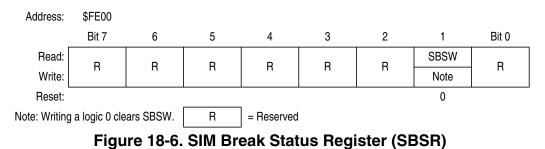

#### 18.5.3 SIM Break Status Register

The SIM break status register (SBSR) contains a flag to indicate that a break caused an exit from wait mode. This register is used only in emulation mode.

#### **Crystal Oscillator Characteristics**

### **19.8 Crystal Oscillator Characteristics**

#### Table 19-7. Oscillator Characteristics

| Characteristic                                            | Symbol            | Min | Тур              | Мах | Unit |

|-----------------------------------------------------------|-------------------|-----|------------------|-----|------|

| Crystal frequency <sup>(1)</sup>                          | f <sub>XCLK</sub> | 1   | 4                | 4   | MHz  |

| External clock<br>Reference frequency <sup>(1), (2)</sup> | fxclk             | dc  | _                | 4   | MHz  |

| Crystal load capacitance <sup>(3)</sup>                   | CL                | _   | _                | _   | pF   |

| Crystal fixed capacitance <sup>(3)</sup>                  | C <sub>1</sub>    | _   | 2×C <sub>L</sub> | _   | pF   |

| Crystal tuning capacitance <sup>(3)</sup>                 | C <sub>2</sub>    | _   | 2×C <sub>L</sub> | _   | pF   |

| Feedback bias resistor                                    | R <sub>B</sub>    | —   | 1                | _   | MΩ   |

| Series resistor <sup>(3), (4)</sup>                       | R <sub>S</sub>    | _   | _                | _   | Ω    |

1. The USB module is designed to function at  $f_{XCLK} = 4MHz$ . 2. No more than 10% duty cycle deviation from 50%.

3. Consult crystal vendor data sheet.

4. Not required for high-frequency crystals.

# **19.9 USB DC Electrical Characteristic**

The USB electrical performance is compliant to the USB specification 2.0.

| Table 19-8. | USB DC | Electrical | Characteristics |

|-------------|--------|------------|-----------------|

|-------------|--------|------------|-----------------|

| Characteristic <sup>(1)</sup>   | Symbol                 | Conditions                            | Min | Тур  | Max | Unit |

|---------------------------------|------------------------|---------------------------------------|-----|------|-----|------|

| Hi-Z state data line leakage    | I <sub>LO</sub>        | 0V <v<sub>IN&lt;3.3V</v<sub>          | -10 |      | +10 | μA   |

| Voltage input high (driven)     | V <sub>IH</sub>        |                                       | 2.0 |      |     | V    |

| Voltage input high (floating)   | V <sub>IHZ</sub>       |                                       | 2.7 |      | 3.6 | V    |

| Voltage input low               | V <sub>IL</sub>        |                                       |     |      | 0.8 | V    |

| Differential input sensitivity  | V <sub>DI</sub>        | l(D+) – (D–)l                         | 0.2 |      |     | V    |

| Differential common mode range  | V <sub>CM</sub>        | Includes V <sub>DI</sub><br>Range     | 0.8 |      | 2.5 | V    |

| Static output low               | V <sub>OL</sub>        | R <sub>L</sub> of 1.425 K<br>to 3.6 V |     |      | 0.3 | V    |

| Static output high              | V <sub>OH</sub>        | R <sub>L</sub> of 14.25 K<br>to GND   | 2.8 |      | 3.6 | V    |

| Output signal crossover voltage | V <sub>CRS</sub>       |                                       | 1.3 | —    | 2.0 | V    |

| Regulator bypass capacitor      | C <sub>REGBYPASS</sub> |                                       |     | 0.47 |     | μF   |

| Regulator bulk capacitor        | C <sub>REGBULK</sub>   |                                       | 4.7 |      |     | μF   |

1.  $V_{DD}$  = 3.9 to 5.5 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H,$  unless otherwise noted.

**Electrical Specifications**

# **19.10 Timer Interface Module Characteristics**

#### Table 19-9. Timer Interface Characteristics

| Characteristic            | Symbol                              | Min | Max | Unit             |

|---------------------------|-------------------------------------|-----|-----|------------------|

| Input capture pulse width | t <sub>TIH</sub> , t <sub>TIL</sub> | 1   | —   | t <sub>CYC</sub> |

# 19.11 FLASH Program/Erase Timing

### Table 19-10. Flash Program/Erase Timing

| Characteristic                 | Symbol             | Min | Max | Unit |

|--------------------------------|--------------------|-----|-----|------|

| PROG/ERASE to NVSTR setup time | T <sub>nvs</sub>   | 5   | _   | μs   |

| NVSTR hold time                | T <sub>nvh</sub>   | 5   | _   | μs   |

| NVSTR hold time (mass erase)   | T <sub>nvhl</sub>  | 100 | _   | μs   |

| NVSTR to program setup time    | T <sub>pgs</sub>   | 10  | —   | μs   |

| Program Time                   | T <sub>prog</sub>  | 20  | 40  | μs   |

| Page Erase Time                | T <sub>erase</sub> | 20  | —   | ms   |

| Mass Erase Time                | T <sub>me</sub>    | 200 | —   | ms   |

| Recovery time                  | T <sub>rcv</sub>   | 1   | —   | μs   |

| Accumulative program HV period | T <sub>hv</sub>    | —   | 8   | ms   |

# **19.12 CGM Electrical Specifications**

### Table 19-11. CGM Electrical Specifications

| Characteristic                | Symbol            | Min | Тур | Max | Unit |

|-------------------------------|-------------------|-----|-----|-----|------|

| Operating Voltage             | V <sub>DD</sub>   | 3.5 | _   | 5.5 | V    |

| Reference frequency           | f <sub>RDV</sub>  | —   | 4   | —   | MHz  |

| VCO center-of-range frequency | f <sub>VRS</sub>  | —   | 48M | —   | Hz   |

| VCO multiply factor           | N                 | 1   | _   | 6   |      |

| VCO prescale multiplier       | 2 <sup>P</sup>    | 0   | _   | 1   |      |

| Reference divider factor      | R                 | 1   | 1   | 1   |      |

| VCO operating frequency       | f <sub>VCLK</sub> | 24  | _   | 48  | MHz  |

| Manual acquisition time       | t <sub>LOCK</sub> | —   | -   | 5   | ms   |

| Automatic lock time           | t <sub>LOCK</sub> | —   | -   | 5   | ms   |