Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | 8032                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 40MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                            |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 35                                                                      |

| Program Memory Size        | 160KB (160K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                               |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 52-TQFP                                                                 |

| Supplier Device Package    | -                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/upsd3433ev-40t6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **List of figures**

| Figure 1.  | Block diagram                                                                        | 21    |

|------------|--------------------------------------------------------------------------------------|-------|

| Figure 2.  | LQFP52 connections                                                                   | 22    |

| Figure 3.  | LQFP80 connections                                                                   | 23    |

| Figure 4.  | Functional modules                                                                   | 29    |

| Figure 5.  | UPSD34xx memories                                                                    | 30    |

| Figure 6.  | Comparison of UPSD34xx with standard 8032 performance                                | 33    |

| Figure 7.  | Instruction pre-fetch queue and branch cache                                         | 34    |

| Figure 8.  | PFQ operation on multi-cycle instructions                                            | 35    |

| Figure 9.  | UPSD34xx multi-cycle instructions compared to standard 8032                          | 36    |

| Figure 10. | 8032 MCU registers                                                                   | 38    |

| Figure 11. | 8032 MCU registers                                                                   | . 40  |

| Figure 12. | Enabling and polling interrupts                                                      | 64    |

| Figure 13. | Clock generation logic                                                               | 70    |

| Figure 14. | Oscillator and clock connections                                                     | 77    |

| Figure 15. | MCU module port pin function routing                                                 | 80    |

| Figure 16. | MCU I/O cell block diagram for port 1                                                | . 80  |

| Figure 17. | MCU I/O cell block diagram for port 3                                                | 81    |

| Figure 18. | MCU I/O cell block diagram for port 4                                                | 81    |

| Figure 19. | Connecting external devices using ports A and B for address AD[15:0]                 | 87    |

| Figure 20. | Connecting external devices using port A and an external latch for address AD[15:0]. | 87    |

| Figure 21. | A RD or PSEN bus cycle set to 5 MCU_CLK                                              | 88    |

| Figure 22. | Supervisor reset generation                                                          | 91    |

| Figure 23. | Watchdog counter                                                                     | 93    |

| Figure 24. | Timer/counter mode 0: 13-bit counter                                                 | . 100 |

| Figure 25. |                                                                                      |       |

| Figure 26. | Timer/counter mode 3: two 8-bit counters                                             | . 100 |

| Figure 27. | Timer 2 in capture mode                                                              | . 105 |

| Figure 28. | Timer 2 in auto-reload mode                                                          | . 106 |

| Figure 29. | Timer 2 in baud rate generator mode                                                  |       |

| Figure 30. | UART mode 0, block diagram                                                           | . 113 |

| Figure 31. | UART mode 0, timing diagram                                                          |       |

| Figure 32. | UART mode 1, block diagram                                                           |       |

| Figure 33. | UART mode 1, timing diagram                                                          |       |

| Figure 34. | UART mode 2, block diagram                                                           |       |

| Figure 35. | UART mode 2, timing diagram                                                          |       |

| Figure 36. | UART mode 3, block diagram                                                           |       |

| Figure 37. | UART mode 3, timing diagram                                                          |       |

| Figure 38. | IrDA interface                                                                       |       |

| Figure 39. | Pulse shaping by the IrDA interface                                                  |       |

| Figure 40. | Typical I2C bus configuration                                                        |       |

| Figure 41. | Data transfer on an I <sup>2</sup> C bus                                             |       |

| Figure 42. | I <sup>2</sup> C interface SIOE block diagram                                        |       |

| Figure 43. | SPI device connection examples                                                       |       |

| Figure 44. | SPI full-duplex data exchange                                                        |       |

| Figure 45. | SPI receive operation example                                                        |       |

| Figure 46. | SPI transmit operation example                                                       |       |

| Figure 47. | SPI interface, master mode only                                                      |       |

| Figure 48  | USB module block diagram                                                             | 151   |

| Figure 49. | USB packets in a USB transfer example                                   | 153 |

|------------|-------------------------------------------------------------------------|-----|

| Figure 50. | IN and OUT bulk transfers                                               | 154 |

| Figure 51. | Interrupt transfer                                                      | 155 |

| Figure 52. | Control transfer                                                        | 156 |

| Figure 53. | FIFOs with no pairing                                                   | 158 |

| Figure 54. | FIFO pairing example (1/2 IN paired and 3/4 OUT paired)                 | 159 |

| Figure 55. | Typical self powered example                                            | 177 |

| Figure 56. | 10-bit ADC                                                              | 179 |

| Figure 57. | PCA0 block diagram                                                      | 181 |

| Figure 58. | Timer mode                                                              | 184 |

| Figure 59. | PWM mode - (x8), fixed frequency                                        | 185 |

| Figure 60. | PWM mode - (x8) programmable frequency                                  | 186 |

| Figure 61. | PSD module block diagram                                                | 191 |

| Figure 62. | Memory page register                                                    |     |

| Figure 63. | Typical system memory map                                               | 198 |

| Figure 64. | PSDsoft express memory mapping                                          | 199 |

| Figure 65. | Mapping: split second Flash in half                                     | 200 |

| Figure 66. | Mapping: all Flash in code space                                        | 201 |

| Figure 67. | Mapping: small code / big data                                          | 201 |

| Figure 68. | PSD module memory priority                                              | 202 |

| Figure 69. | VM register control of memories                                         | 204 |

| Figure 70. | VM register example corresponding to memory map example                 | 204 |

| Figure 71. | Data polling flowchart                                                  | 214 |

| Figure 72. | Data polling flowchart                                                  | 215 |

| Figure 73. | DPLD and GPLD                                                           | 221 |

| Figure 74. | DPLD and GPLD                                                           | 223 |

| Figure 75. | GPLD: one OMC, one IMC, and one I/O port (typical pin, port A, B, or C) |     |

| Figure 76. | Detail of a single OMC                                                  | 226 |

| Figure 77. | OMC allocator  Detail of a single IMC                                   | 227 |

| Figure 78. | Detail of a single IMC                                                  | 230 |

| Figure 79. | Detail of a single I/O port (typical of ports A, B, C)                  |     |

| Figure 80. | Simple PLD logic example                                                |     |

| Figure 81. | Pin declarations in PSDsoft express for simple PLD example              |     |

| Figure 82. | Using the design assistant in PSDsoft Express for simple PLD example    |     |

| Figure 83. | Peripheral I/O mode                                                     |     |

| Figure 84. | Port A structure                                                        |     |

| Figure 85. | Port B structure                                                        | 244 |

| Figure 86. | Port C structure                                                        | 246 |

| Figure 87. | Port D structure                                                        | 247 |

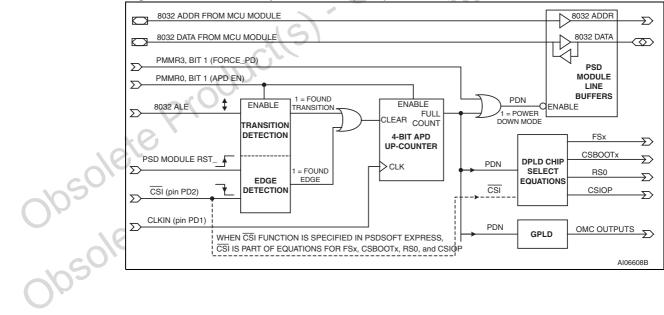

| Figure 88. | Automatic power-down (APD) unit                                         | 252 |

| Figure 89. | Power-down mode flowchart                                               | 253 |

| Figure 90. | JTAG chain in UPSD34xx package                                          | 258 |

| Figure 91. | Recommended 4-pin JTAG connections                                      | 259 |

| Figure 92. | Recommended 6-pin JTAG connections                                      | 261 |

| Figure 93. | Recommended JTAG connector                                              | 262 |

| Figure 94. | Example of chaining UPSD34xx devices                                    | 263 |

| Figure 95. | PLD ICC / frequency consumption (5 V range)                             | 265 |

| Figure 96. | PLD ICC / frequency consumption (3 V range)                             | 266 |

| Figure 97. | Switching waveforms – key                                               |     |

| Figure 98. | External READ cycle (80-pin device only)                                | 275 |

| Figure 99. | External WRITE cycle (80-pin device only)                               | 276 |

| Figure 100 | Input to output disable / enable                                        | 278 |

Table 2. Pin definitions (continued)

| Dout nin | Signal | 80-pin | 52-pin             | In/out |                                        | Function                        |                                                          |

|----------|--------|--------|--------------------|--------|----------------------------------------|---------------------------------|----------------------------------------------------------|

| Port pin | name   | No.    | No. <sup>(1)</sup> | In/out | Basic                                  | Alternate 1                     | Alternate 2                                              |

| ALE      |        | 4      | N/A                | 0      | Address Latch signal, external bus     |                                 |                                                          |

| RESET_IN |        | 68     | 44                 | I      | Active low reset input                 |                                 |                                                          |

| XTAL1    |        | 48     | 31                 | ı      | Oscillator input pin for system clock  |                                 |                                                          |

| XTAL2    |        | 49     | 32                 | 0      | Oscillator output pin for system clock |                                 | 16)                                                      |

| DEBUG    |        | 8      | 5                  | I/O    | I/O to the MCU<br>debug unit           |                                 | cila                                                     |

| PA0      |        | 35     | N/A                | I/O    | General I/O port pin                   |                                 | , o                                                      |

| PA1      |        | 34     | N/A                | I/O    | General I/O port pin                   | 010                             | All Port A pins support:                                 |

| PA2      |        | 32     | N/A                | I/O    | General I/O port pin                   |                                 | <ul><li>PLD Macrocell</li></ul>                          |

| PA3      |        | 28     | N/A                | I/O    | General I/O port pin                   | 3/6                             | outputs, or                                              |

| PA4      |        | 26     | N/A                | I/O    | General I/O port pin                   | -40                             | <ul><li>PLD inputs, or</li><li>Latched address</li></ul> |

| PA5      |        | 24     | N/A                | I/O    | General I/O port pin                   | 01                              | out (A0-A7), or                                          |

| PA6      |        | 22     | N/A                | I/O    | General I/O port pin                   | *6                              | <ul><li>Peripheral I/O mode</li></ul>                    |

| PA7      |        | 21     | N/A                | I/O    | General I/O port pin                   | S                               |                                                          |

| PB0      |        | 80     | 52                 | 1/0    | General I/O port pin                   |                                 |                                                          |

| PB1      |        | 78     | 51                 | I/O    | General I/O port pin                   |                                 | All Port B pins                                          |

| PB2      |        | 76     | 50                 | I/O    | General I/O port pin                   |                                 | support:  – PLD Macrocell                                |

| PB3      | 0      | 74     | 49                 | I/O    | General I/O port pin                   |                                 | outputs, or                                              |

| PB4      | . 0    | 73     | 48                 | I/O    | General I/O port pin                   |                                 | <ul><li>PLD inputs, or</li></ul>                         |

| PB5      |        | 71     | 46                 | I/O    | General I/O port pin                   |                                 | <ul> <li>Latched address<br/>out (A0-A7 or</li> </ul>    |

| PB6      |        | 67     | 43                 | I/O    | General I/O port pin                   |                                 | A8-A15)                                                  |

| PB7      |        | 66     | 42                 | I/O    | General I/O port pin                   |                                 |                                                          |

| JTAGTMS  | TMS    | 20     | 13                 | I      | JTAG pin (TMS)                         |                                 |                                                          |

| JTAGTCK  | TCK    | 17     | 12                 | I      | JTAG pin (TCK)                         |                                 |                                                          |

| PC2      |        | 16     | 11                 | I/O    | General I/O port pin                   |                                 | PLD Macrocell output, or PLD input                       |

| PC3      | TSTAT  | 15     | N/A                | I/O    | General I/O port pin                   | Optional JTAG<br>Status (TSTAT) | PLD, Macrocell output, or PLD input                      |

| PC4      | TERR   | 9      | N/A                | I/O    | General I/O port pin                   | Optional JTAG<br>Status (TERR)  | PLD, Macrocell output, or PLD input                      |

| JTAGTDI  | TDI    | 7      | 4                  | I      | JTAG pin (TDI)                         |                                 |                                                          |

| JTAGTDO  | TDO    | 6      | 3                  | 0      | JTAG pin (TDO)                         |                                 |                                                          |

## 4.2.1 Program memory

External program memory is addressed by the 8032 using its 16-bit program counter (PC) and is accessed with the 8032 signal, PSEN. Program memory can be present at any address in program space between 0000h and FFFFh.

After a power-up or reset, the 8032 begins program execution from location 0000h where the reset vector is stored, causing a jump to an initialization routine in firmware. At address 0003h, just following the reset vector are the interrupt service locations. Each interrupt is assigned a fixed interrupt service location in program memory. An interrupt causes the 8032 to jump to that service location, where it commences execution of the service routine. External Interrupt 0 (EXINT0), for example, is assigned to service location 0003h. If EXINT0 is going to be used, its service routine must begin at location 0003h. Interrupt service locations are spaced at 8-byte intervals: 0003h for EXINT0, 000Bh for Timer 0, 0013h for EXINT1, and so forth. If an interrupt service routine is short enough, it can reside entirely within the 8-byte interval. Longer service routines can use a jump instruction to somewhere else in program memory.

## 4.2.2 Data memory

External data is referred to as XDATA and is addressed by the 8032 using Indirect Addressing via its 16-bit data pointer register (DPTR) and is accessed by the 8032 signals, RD and WR. XDATA can be present at any address in data space between 0000h and FFFFh.

Note: The UPSD34xx has dual data pointers (source and destination) making XDATA transfers much more efficient.

## 4.2.3 Memory placement

PSD module architecture allows the placement of its external memories into different combinations of program memory and data memory spaces. This means the main Flash, the secondary Flash, and the SRAM can be viewed by the 8032 MCU in various combinations of program memory or data memory as defined by PSDsoft Express.

As an example of this flexibility, for applications that require a great deal of Flash memory in data space (large lookup tables or extended data recording), the larger main Flash memory can be placed in data space and the smaller secondary Flash memory can be placed in program space. The opposite can be realized for a different application if more Flash memory is needed for code and less Flash memory for data.

By default, the SRAM and csiop memories on the PSD module must always reside in data memory space and they are treated by the 8032 as XDATA.

The main Flash and secondary Flash memories may reside in program space, data space, or both. These memory placement choices specified by PSDsoft Express are programmed into non-volatile sections of the UPSD34xx, and are active at power-up and after reset. It is possible to override these initial settings during runtime for In-Application Programming (IAP).

Standard 8032 MCU architecture cannot write to its own program memory space to prevent accidental corruption of firmware. However, this becomes an obstacle in typical 8032 systems when a remote update to firmware in Flash memory is required using IAP. The PSD module provides a solution for remote updates by allowing 8032 firmware to temporarily "reclassify" Flash memory to reside in data space during a remote update, then returning Flash memory back to program space when finished. See the VM register (*Table 160 on page 203*) in the PSD module section of this document for more details.

## 5 8032 MCU core performance enhancements

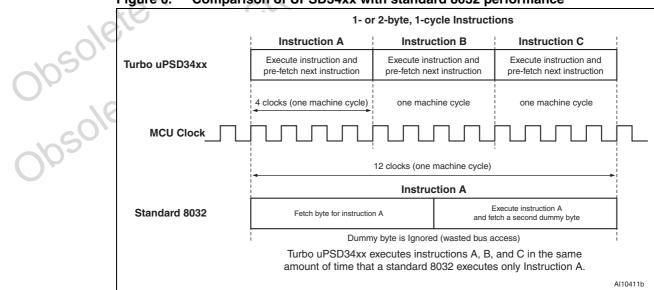

Before describing performance features of the UPSD34xx, let us first look at standard 8032 architecture. The clock source for the 8032 MCU creates a basic unit of timing called a machine-cycle, which is a period of 12 clocks for standard 8032 MCUs. The instruction set for traditional 8032 MCUs consists of 1, 2, and 3 byte instructions that execute in different combinations of 1, 2, or 4 machine-cycles. For example, there are one-byte instructions that execute in one machine-cycle (12 clocks), one-byte instructions that execute in four machine-cycles (48 clocks), two-byte, two-cycle instructions (24 clocks), and so on. In addition, standard 8032 architecture will fetch two bytes from program memory on almost every machine-cycle, regardless if it needs them or not (dummy fetch). This means for one-byte, one-cycle instructions, the second byte is ignored. These one-byte, one-cycle instructions account for half of the 8032's instructions (126 out of 255 opcodes). There are inefficiencies due to wasted bus cycles and idle bus times that can be eliminated.

The UPSD34xx 8032 MCU core offers increased performance in a number of ways, while keeping the exact same instruction set as the standard 8032 (all opcodes, the number of bytes per instruction, and the native number a machine-cycles per instruction are identical to the original 8032). The first way performance is boosted is by reducing the machine-cycle period to just 4 MCU clocks as compared to 12 MCU clocks in a standard 8032. This shortened machine-cycle improves the instruction rate for one- or two-byte, one-cycle instructions by a factor of three (*Figure 6 on page 33*) compared to standard 8051 architectures, and significantly improves performance of multiple-cycle instruction types.

The example in *Figure 6 on page 33* shows a continuous execution stream of one- or two-byte, one-cycle instructions. The 5 V UPSD34xx will yield 10 MIPS peak performance in this case while operating at 40 MHz clock rate. In a typical application however, the effective performance will be lower since programs do not use only one-cycle instructions, but special techniques are implemented in the UPSD34xx to keep the effective MIPS rate as close as possible to the peak MIPS rate at all times. This is accomplished with an instruction prefetch queue (PFQ), a branch cache (BC), and a 16-bit program memory bus as shown in *Figure 7 on page 34*.

Figure 6. Comparison of UPSD34xx with standard 8032 performance

#### 11 **Dual data pointers**

XDATA is accessed by the External Direct addressing mode, which uses a 16-bit address stored in the DPTR register. Traditional 8032 architecture has only one DPTR register. This is a burden when transferring data between two XDATA locations because it requires heavy use of the working registers to manipulate the source and destination pointers.

However, the UPSD34xx has two data pointers, one for storing a source address and the other for storing a destination address. These pointers can be configured to automatically increment or decrement after each data transfer, further reducing the burden on the 8032 and making this kind of data movement very efficient.

#### 11.1 Data pointer control register, DPTC (85h)

By default, the DPTR register of the UPSD34xx will behave no different than in a standard 8032 MCU. The DPSEL0 Bit of SFR register DPTC shown in Table 13, selects which one of the two "background" data pointer registers (DPTR0 or DPTR1) will function as the traditional DPTR register at any given time. After reset, the DPSEL0 Bit is cleared, enabling DPTR0 to function as the DPTR, and firmware may access DPTR0 by reading or writing the traditional DPTR register at SFR addresses 82h and 83h. When the DPSEL0 bit is set, then the DPTR1 register functions as DPTR, and firmware may now access DPTR1 through SFR registers at 82h and 83h. The pointer which is not selected by the DPSEL0 bit remains in the background and is not accessible by the 8032. If the DPSEL0 bit is never set, then the UPSD34xx will behave like a traditional 8032 having only one DPTR register.

To further speed XDATA to XDATA transfers, the SFR bit, AT, may be set to automatically toggle the two data pointers, DPTR0 and DPTR1, each time the standard DPTR register is accessed by a MOVX instruction. This eliminates the need for firmware to manually manipulate the DPSEL0 bit between each data transfer.

Detailed description for the SFR register DPTC is shown in Table 13.

DPTC: data pointer control register (SFR 85h, reset value 00h)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  |

|-------|-------|-------|-------|-------|-------|-------|--------|

| -     | AT    | -     | -     | _     | -     | _     | DPSEL0 |

**DPTC** register bit definition

|       | Bit 7     | Bit 6    | Bit 5         | Bit 4     | Bit 3                            | Bit 2      | Bit 1 | Bit 0  |  |  |

|-------|-----------|----------|---------------|-----------|----------------------------------|------------|-------|--------|--|--|

|       | _         | AT       | ı             | _         | ı                                | 1          | ı     | DPSEL0 |  |  |

| aloso | Table 14. | DPTC reg | jister bit de | efinition |                                  |            |       |        |  |  |

| Ob    | Bit       | Symbol   | R/W           |           |                                  | Definition |       |        |  |  |

|       | 7         | _        | -             | Reserved  |                                  |            |       |        |  |  |

| 0050  | 6         | АТ       | R,W           |           | y select data<br>Igle between    | •          | DPTR1 |        |  |  |

|       | 5-1       | _        | _             | Reserved  |                                  |            |       |        |  |  |

|       | 0         | DPSE0    | R,W           |           | selected for a<br>selected for a |            |       |        |  |  |

#### Standard 8032 timer/counters 20

There are three 8032-style 16-bit Timer/Counter registers (Timer 0, Timer 1, Timer 2) that can be configured to operate as timers or event counters.

There are two additional 16-bit Timer/Counters in the Programmable Counter Array (PCA), see Section 27.1: PCA block on page 181 for details.

#### 20.1 Standard timer SFRs

Timer 0 and Timer 1 have very similar functions, and they share two SFRs for control:

- TCON (Table 56 on page 97)

- TMOD (Table 58 on page 99).

olete Productic Timer 0 has two SFRs that form the 16-bit counter, or that can hold reload values, or that can scale the clock depending on the timer/counter mode:

- TH0 is the high byte, address 8Ch

- TL0 is the low byte, address 8Ah

Timer 1 has two similar SFRs:

- TH1 is the high byte, address 8Dh

- TL1 is the low byte, address 8Bh

Timer 2 has one control SFR:

T2CON (Table 60 on page 101)

Timer 2 has two SFRs that form the 16-bit counter, and perform other functions:

- TH2 is the high byte, address CDh

- TL2 is the low byte, address CCh

Timer 2 has two SFRs for capture and reload:

- RCAP2H is the high byte, address CBh

- RCAP2L is the low byte, address CAh

## Clock sources

When enabled in the "Timer" function, the registers THx and TLx are incremented every 1/12 of the oscillator frequency ( $f_{OSC}$ ). This timer clock source is not effected by MCU clock dividers in the CCON0, stalls from PFQ/BC, or bus transfer cycles. Timers are always clocked at 1/12 of f<sub>OSC</sub>.

When enabled in the "Counter" function, the registers THx and TLx are incremented in response to a 1-to-0 transition sampled at their corresponding external input pin: pin C0 for Timer 0; pin C1 for Timer 1; or pin T2 for Timer 2. In this function, the external clock input pin is sampled by the counter at a rate of 1/12 of  $f_{\mbox{OSC}}$ . When a logic '1' is determined in one sample, and a logic '0' in the next sample period, the count is incremented at the very next sample period (period1: sample=1, period2: sample=0, period3: increment count while continuing to sample). This means the maximum count rate is 1/24 of the  $f_{OSC}$ . There are no restrictions on the duty cycle of the external input signal, but to ensure that a given level is sampled at least once before it changes, it should be active for at least one full sample

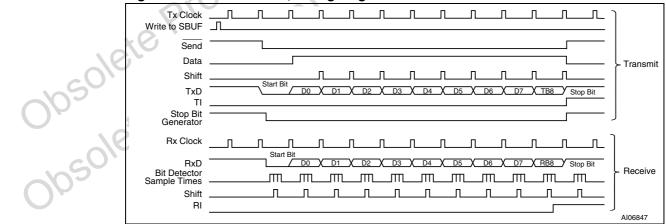

Timer1 Timer2 Internal Bus Overflow Overflow TB8 Write to SBUF TxD Pin D S ÷2 **SBUF** CL Zero Detector SMOD Start Data TCI K Tx Control Send ÷16 Tx Clock Serial Port Interrupt 0 **RCLK** ÷16 **↓↓↓↑** Sample Load SBUF Rx Clock 1-to-0 Rx Control 1FFh Shift Transition Detector Start Rx Detector Input Shift Register RxD Pin Shift SBUF Internal Bus AI06846

Figure 36. UART mode 3, block diagram

The UART1 serial channel can operate in one of four different modes as shown in Table 64 on page 108 in Section 21: Serial UART interfaces on page 107. However, when UART1 is used for IrDA communication, UART1 must operate in Mode 1 only, to be compatible with IrDA protocol up to 115.2k bps. The IrDA interface will support baud rates generated from Timer 1 or Timer 2, just like standard UART serial communication, but with one restriction. The transmit baud rate and receive baud rate must be the same (cannot be different rates as is allowed by standard UART communications).

The IrDA Interface is disabled after a reset and is enabled by setting the IRDAEN Bit in the SFR named IRDACON (Table 70 on page 120). When IrDA is disabled, the UART1's RxD and TxD signals will bypass the internal IrDA logic and instead they are routed directly to the pins RxD1 and TxD1 respectively. When IrDA is enabled, the IrDA pulse shaping logic is active and resides between UART1 and the pins RxD1 and TxD1 as shown in Figure 38 on page 119.

#### 22.1 **Baud rate selection**

The IrDA standard only supports 2.4, 9.6, 19.2, and 115.2kbps. Table 73 on page 121 informs the IrDA Interface of the baud rate of UART#1 so that it can perform pulse modulation properly. It may not be necessary to implement the BR[3:0] bits in the IRDACON register if the IrDA Interface obtains the proper timing from UART#1.

IRDACON register bit definition (SFR CEh, reset value 0Fh) Table 70.

| Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| _     | IRDAEN | PULSE | CDIV4 | CDIV3 | CDIV2 | CDIV1 | CDIV0 |

Table 71. IRDACON register bit definition

|      | 145.0 7 11 |           | it dominion |                                                                                                                          |

|------|------------|-----------|-------------|--------------------------------------------------------------------------------------------------------------------------|

|      | Bit        | Symbol    | R/W         | Definition                                                                                                               |

|      | 7          | 900       | 1           | Reserved                                                                                                                 |

| \ 0  | 6P1        | IRDAEN    | RW          | IrDA Enable  0 = IrDA Interface is disabled  1 = IrDA is enabled, UART1 outputs are disconnected from Port 1 (or Port 4) |

| 30/6 | 5          | PULSE     | RW          | IrDA Pulse Modulation Select  0 = 1.627µs  1 = 3/16 bit time pulses                                                      |

| \ C  | 4-0        | CDIV[4:0] | RW          | Specify Clock Divider (see Table 74 on page 122)                                                                         |

| c0/k | Table 72.  | Baud rate | selection   | register (SFR xxh, reset value xxh)                                                                                      |

| 3    | Bit        | Symbol    | R/W         | Definition                                                                                                               |

| ,    | 7.4        | BB[3:0]   | ВW          | Specify Baud Bate (see Table 73)                                                                                         |

Table 72. Baud rate selection register (SFR xxh, reset value xxh)

| Bit | Symbol  | R/W | Definition                                                                                                        |

|-----|---------|-----|-------------------------------------------------------------------------------------------------------------------|

| 7:4 | BR[3:0] | R,W | Specify Baud Rate (see <i>Table 73</i> )                                                                          |

| 3:2 | PULSE   | R,W | IrDA Pulse Modulation Select<br>0 = 3/16 bit time pulses (not recommended)<br>1 = 1.627μs                         |

| 1:0 | IRDAEN  | R,W | 0 = IrDA Interface is disabled<br>1 = IrDA is enabled, UART#1 outputs are disconnected from<br>Port 1 (or Port 4) |

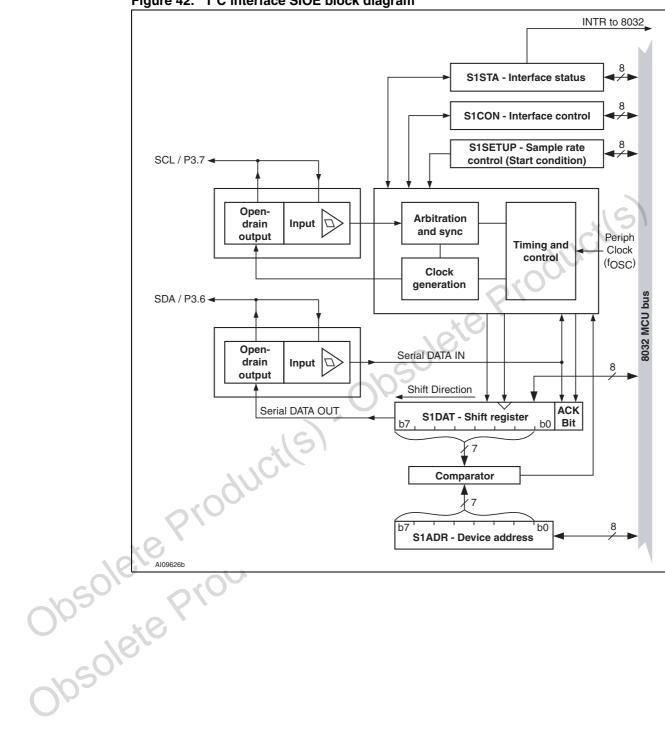

Figure 42. I<sup>2</sup>C interface SIOE block diagram

oducire)

#### 23.13.1 Interrupt service routine (ISR)

A typical I<sup>2</sup>C interrupt service routine would handle a interrupt for any of the four combinations of Master/Slave and Transmitter/Receiver. In the example routines above, the firmware sets global variables, I2C\_master and I2C\_xmitter, before enabling interrupts. These flags tell the ISR which one of the four cases to process. Following is pseudo-code for high-level steps in the I<sup>2</sup>C ISR:

### Begin I2C ISR <I2C interrupt just occurred>:

```

Clear I2C interrupt flag:

S1STA.INTR = 0

Read status of SIOE, put in to variable, status

status = S1STA

Read global variables that determine the mode

mode <= (I2C_master, I2C_slave)</pre>

```

## If mode is Master-Transmitter

```

Bus Arbitration lost? (status.BLOST=1?)

If Yes, Arbitration was lost:

```

- S1DAT = dummy, write to release bus

- Exit ISR, SIOE will switch to Slave Recv mode If No, Arbitration was not lost, continue:

ACK recvd from Slave? (status.ACK\_RESP=0?)

```

If No, an ACK was not received:

```

- S1CON.STO = 1, set Stop bus condition

- <Stop occurs after ISR exit>

- S1DAT = dummy, write to release bus

- - If Yes, ACK was received, then continue:

- S1DAT = xmit\_buf[buffer\_index], transmit byte

If No, it was not the last byte, then:

- Exit ISR, transmit next byte on next interrupt

- S1CON.STO = 1, set Stop bus condition

- S1DAT = dummy, write to release bus

- Exit ISR

#### Accessing the setup command buffer 25.3.6

Setup Packets are sent from the host to a device's Endpoint0 and consist of 8 bytes of command data. When the SIE receives a Setup packet from the host, it stores the 8 bytes of data in the Command Buffer. The command buffer is accessed via the indexed USB Setup Command Value register (USCV). The USB Setup Command Index register (USCI) is used to select the byte from the command buffer that is read when accessing the USCV register.

#### 25.4 **USB** registers

The USB module is controlled via registers mapped into the SFR space. The USB SFRs olete Product(s) consist of the following:

**UADDR: USB device address** UPAIR: USB FIFO pairing control UIE0~3: USB interrupt enable

UIF0~3: USB interrupt flags

**UCTL: USB control** USTA: USB status

USEL: USB endpoint and direction select UCON: USB selected FIFO control register

USIZE: USB selected FIFO size register UBASE: USB base address register USCI: USB setup command index

USCV: USB setup command value

The memory map for the USB SFRs, the individual bit names, and the reset values are shown in Table 99.

Table 99. UPSD34xx USB SFR register map<sup>(1)</sup>

|       | SFR           | SFR   |    |   |   |        |            | Reset    | Comment |         |                |                                     |

|-------|---------------|-------|----|---|---|--------|------------|----------|---------|---------|----------------|-------------------------------------|

| \ 0   | addr<br>(hex) | name  | 7  | 6 | 5 | 4      | 3          | 2        | 1       | 0       | value<br>(hex) | Comment                             |

|       | E2            | UADDR | 10 |   |   |        | USBADI     | DR[6:0]  |         |         | 00             | USB Address                         |

| 0/050 | E3            | UPAIR | -  | - | ı | ı      | PR3OU<br>T | PR1OUT   | PR3IN   | PR1IN   | 00             | USB Pairing<br>Control              |

| GOIE  | E4            | UIE0  | -  | ı | ı | ı      | RSTIE      | SUSPNDIE | EOPIE   | RESUMIE | 00             | USB Global<br>Interrupt<br>Enable   |

| 002   | E5            | UIE1  | _  | ı | ı | IN4IE  | IN3IE      | IN2IE    | IN1IE   | INOIE   | 00             | USB IN FIFO<br>Interrupt<br>Enable  |

|       | E6            | UIE2  | -  | ı | 1 | OUT4IE | OUT3IE     | OUT2IE   | OUT1IE  | OUT0IE  | 00             | USB OUT<br>FIFO Interrupt<br>Enable |

|       | E7            | UIE3  | -  | - | - | NAK4IE | NAK3IE     | NAK2IE   | NAK1IE  | NAK0IE  | 00             | USB IN FIFO<br>NAK Int.<br>Enable   |

| Instr.<br>Seq.            | Bus<br>Cycle 1                                                                                                  | Bus<br>Cycle 2 | Bus<br>Cycle 3 | Bus<br>Cycle 4 | Bus<br>Cycle 5 | Bus<br>Cycle 6 | Bus<br>Cycle 7 | Link                                     |

|---------------------------|-----------------------------------------------------------------------------------------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|------------------------------------------|

| Resume<br>Sector<br>Erase | Write 30h to<br>address that<br>activates FSx<br>or CSBOOTx<br>where<br>desired to<br>resume erase<br>(command) |                |                |                |                |                |                | Resume<br>sector<br>erase on<br>page 217 |

| Reset<br>Flash            | Write F0h to<br>address that<br>activates FSx<br>or CSBOOTx<br>in desired<br>array.<br>(command)                |                |                |                |                |                |                | Reset<br>Flash on<br>page 218            |

Table 163. Flash memory instruction sequences<sup>(1)(2)</sup> (continued)

- 1. All values are in hexadecimal, X = Don't care.

- 8032 addresses A12 through A15 are "Don't care" during the instruction sequence decoding. Only address

bits A0-A11 are used during decoding of Flash memory instruction sequences. The individual sector select

signal (FS0 FS7 or CSBOOT0-CSBOOT3) which is active during the instruction sequence determines the

complete address.

- 3. Directing this command to any individual sector within a Flash memory array will invoke the bulk erase of all Flash memory sectors within that array.

## 28.5.3 Reading Flash memory

Under typical conditions, the 8032 may read the Flash memory using READ operations (READ bus cycles) just as it would a ROM or RAM device. Alternately, the 8032 may use READ operations to obtain status information about a Program or Erase operation that is currently in progress. The following sections describe the kinds of READ operations.

## 28.5.4 Read memory contents

Flash memory is placed in the Read Array mode after Power-up, after a PSD module reset event, or after receiving a Reset Flash memory instruction sequence from the 8032. The 8032 can read Flash memory contents using standard READ bus cycles anytime the Flash array is in Read Array mode. Flash memories will always be in Read Array mode when the array is not actively engaged in a program or erase operation.

## 28.5.5 Reading the erase/program status bits

The Flash arrays provide several status bits to be used by the 8032 to confirm the completion of an erase or program operation on Flash memory, shown in *Table 164 on page 212*. The status bits can be read as many times as needed until an operation is complete.

The 8032 performs a READ operation to obtain these status bits while an erase or program operation is being executed by the state machine inside each Flash memory array.

## 28.5.6 Data polling flag (DQ7)

While programming either Flash memory, the 8032 may read the Data Polling Flag Bit (DQ7), which outputs the complement of the D7 Bit of the byte being programmed into Flash memory. Once the program operation is complete, DQ7 is equal to D7 of the byte just programmed into Flash memory, indicating the program cycle has completed successfully.

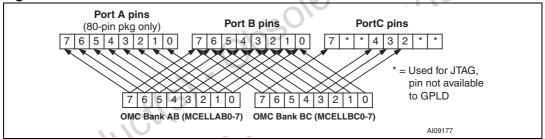

Native product terms come from the AND-OR Array. Each OMC may borrow product terms only from certain other OMCs, if they are not in use. Product term allocation does not add any propagation delay to the logic. The fitter report generated by PSDsoft Express will show any PT allocation that has occurred.

If an equation requires more product terms than are available to it through PT allocation, then "external" product terms are required, which consumes other OMCs. This is called product term expansion and also happens automatically in PSDsoft Express as needed. PT expansion causes additional propagation delay because an additional OMC is consumed by the expansion process and its output is rerouted (or fed back) into the AND-OR array. The user can examine the fitter report generated by PSDsoft Express to see resulting PT allocation and PT expansion (expansion will have signal names, such as '\*.fb\_0' or '\*.fb\_1'). PSDsoft Express will always try to fit the logic design first by using PT allocation, and if that is not sufficient then PSDsoft Express will use PT expansion.

Product term expansion may occur in the DPLD for complex chip select equations for Flash memory sectors and for SRAM, but this is a rare occurence. If PSDsoft Express does use PT expansion in the DPLD, it results in an approximate 15ns additional propagation delay for that chip select signal, which gives 15ns less time for the memory to respond. Be aware of this and consider adding a wait state to the 8032 bus access (using the SFR named, BUSCON), or lower the 8032 clock frequency to avoid problems with memory access time.

Figure 77. OMC allocator

Table 168. OMC port and data bit assignments

| 0/6               | ОМС      | Port<br>assignment <sup>(1),(2)</sup> | Native product<br>terms from AND-OR<br>array | Maximum<br>borrowed product<br>terms | Data bit on 8032<br>data bus for<br>loading or<br>reading OMC |

|-------------------|----------|---------------------------------------|----------------------------------------------|--------------------------------------|---------------------------------------------------------------|

| -1050             | MCELLAB0 | Port A0 or B0                         | 3                                            | 6                                    | D0                                                            |

| $O_{\mathcal{P}}$ | MCELLAB1 | Port A1 or B1                         | 3                                            | 6                                    | D1                                                            |

| -16               | MCELLAB2 | Port A2 or B2                         | 3                                            | 6                                    | D2                                                            |

| c0//              | MCELLAB3 | Port A3 or B3                         | 3                                            | 6                                    | D3                                                            |

| 000               | MCELLAB4 | Port A4 or B4                         | 3                                            | 6                                    | D4                                                            |

| 0.                | MCELLAB5 | Port A5 or B5                         | 3                                            | 6                                    | D5                                                            |

|                   | MCELLAB6 | Port A6 or B6                         | 3                                            | 6                                    | D6                                                            |

|                   | MCELLAB7 | Port A7 or B7                         | 3                                            | 6                                    | D7                                                            |

|                   | MCELLBC0 | Port B0                               | 4                                            | 5                                    | D0                                                            |

|                   | MCELLBC1 | Port B1                               | 4                                            | 5                                    | D1                                                            |

|                   | MCELLBC2 | Port B or C2                          | 4                                            | 5                                    | D2                                                            |

|                     | Uliaet Uai          | 171                 |                     |                     |                     |                    |                    |

|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|--------------------|--------------------|

| Bit 7               | Bit 6               | Bit 5               | Bit 4               | Bit 3               | Bit 2               | Bit 1              | Bit 0              |

| PB7                 | PB6                 | PB5                 | PB4                 | PB3                 | PB2                 | PB1                | PB0                |

| (addr A7 or<br>A15) | (addr A6 or<br>A14) | (addr A5 or<br>A13) | (addr A4 or<br>A12) | (addr A3 or<br>A11) | (Addr A2<br>or A10) | (addr A1 or<br>A9) | (addr A0 or<br>A8) |

Table 191. Latched address output, port B contro register<sup>(1)</sup> (2)(address = csiop + offeat 03h)I

- 1. Default state for register is 00h after reset or power-up.

- 2. For each bit, 1 = drive demuxed 8032 address signal on pin, 0 = pin is default mode, MCU I/O.

#### 28.5.41 Peripheral I/O mode

This mode will provide a data bus repeater function for the 8032 to interface with external parallel peripherals. The mode is only available on Port A (80-pin devices only) and the data bus signals, D0 - D7, are de-multiplexed (no address A0-A7). When active, this mode behaves like a bidirectional buffer, with the direction automatically controlled by the 8032 RD and WR signals for a specified address range. The DPLD signals PSEL0 and PSEL1 determine this address range. Figure 79 on page 232 shows the action of Peripheral I/O mode on the Output Enable logic of the tri-state output driver for a single port pin. Figure 83 on page 239 illustrates data repeater the operation. To activate this mode, choose the pin function "Peripheral I/O Mode" in PSDsoft Express on any Port A pin (all eight pins of Port A will automatically change to this mode). Next in PSDsoft, specify an address range for the PSELx signals in the "Chip-Select" section of the "Design Assistant". The user can specify an address range for either PSEL0 or PSEL1. Always qualify the PSELx equation with "PSEN is logic '1" to ensure Peripheral I/O mode is only active during 8032 data cycles, not code cycles. Only one equation is needed since PSELx signals are OR'ed together (Figure 83). Then in the 8032 initialization firmware, a logic '1' is written to the csiop VM register, Bit 7 (PIO EN) as shown in Table 154 on page 189. After this, Port A will automatically perform this repeater function whenever the 8032 presents an address (and memory page number, if paging is used) that is within the range specified by PSELx. Once Port A is designated as Peripheral I/O mode in PSDsoft Express, it cannot be used for other functions.

Note:

The user can alternatively connect an external parallel peripheral to the standard 8032 AD0-AD7 pins on an 80-pin uPSD device (not Port A), but these pins have multiplexed address and data signals, with a weaker fanout drive capability.

712011 8032 RD PSFI 0 PSEL1 PA0 - PA7 8032 data bus D0-D7 Port VM register bit 7 (PIO EN) A pins (DE-MUXED) 8032 WR AI02886A

Figure 83. Peripheral I/O mode

Table 193. Port B pin drive select register (address = csiop + offset 09h)(1) (2)

| Bit 7      | Bit 6      | Bit 5      | Bit 4      | Bit 3     | Bit 2     | Bit 1     | Bit 0     |

|------------|------------|------------|------------|-----------|-----------|-----------|-----------|

| PB7        | PB6        | PB5        | PB4        | PB3       | PB2       | PB1       | PB0       |

| open drain | open drain | open drain | open drain | slew rate | slew rate | slew rate | slew rate |

- 1. For each bit, 1 = pin drive type is selected, 0 = pin drive type is default mode, CMOS push/pull.

- 2. Default state for register is 00h after reset or power-up.

## Table 194. Port C pin drive select register (address = csiop + offset 16h) $^{(1)}$ (2)

| Bit 7      | Bit 6  | Bit 5  | Bit 4      | Bit 3      | Bit 2      | Bit 1  | Bit 0  |

|------------|--------|--------|------------|------------|------------|--------|--------|

| PC7        | N/A    | N/A    | PC4        | PC3        | PC2        | N/A    | N/A    |

| open drain | (JTAG) | (JTAG) | open drain | open drain | open drain | (JTAG) | (JTAG) |

- 1. For each bit, 1 = pin drive type is selected, 0 = pin drive type is default mode, CMOS push/pull

- 2. Default state for register is 00h after reset or power-up

## Table 195. Port D pin drive select register (address = $csiop + offset 17h)^{(1)}$ (2)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2                           | Bit 1            | Bit 0 |

|-------|-------|-------|-------|-------|---------------------------------|------------------|-------|

| N/A   | N/A   | N/A   | N/A   | N/A   | PD2 <sup>(3)</sup><br>slew rate | PD1<br>slew rate | N/A   |

- 1. For each bit, 1 = pin drive type is selected, 0 = pin drive type is default mode, CMOS push/pull

- 2. Default state for register is 00h after reset or power-up

- 3. Pin is not available on 52-pin UPSD34xx devices

## Table 196. Port A enable out register<sup>(1)</sup> (2)(address = csiop + offset 0Ch)

| Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| PA7 OE | PA6 OE | PA5 OE | PA4 OE | PA3 OE | PA2 OE | PA1 OE | PA0 OE |

- 1. Port A not available on 52-pin UPSD34xx devices

- 2. For each bit, 1 = pin drive is enabled as an output, 0 = pin drive is off (high-impedance, pin used as input)

## Table 197. Port B enable out register (address = $csiop + offset 0Dh)^{(1)}$

| Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| PB7 OE | PB6 OE | PB5 OE | PB4 OE | PB3 OE | PB2 OE | PB1 OE | PB0 OE |

## Table 198. Port C enable out register (address = $csiop + offset 1Ah)^{(1)}$

| 1. For each bit, 1 = pin drive is enabled as an output, 0 = pin drive is off (high-impedance, pin used as input  Table 198. Port C enable out register (address = csiop + offset 1Ah) <sup>(1)</sup> |       | PB7 OE        | PB6 OE            | PB5 OE         | PB4 OE         | PB3 OE           | PB2 OE          | PB1 OE         | PB0 OE        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------|-------------------|----------------|----------------|------------------|-----------------|----------------|---------------|

| Table 198. Port C enable out register (address = csiop + offset 1Ah) <sup>(1)</sup>                                                                                                                  | 2050  | 1. For each b | oit, 1 = pin driv | e is enabled a | s an output, 0 | = pin drive is o | ff (high-impeda | ance, pin used | as input)     |

|                                                                                                                                                                                                      |       |               |                   |                |                |                  |                 |                |               |

| Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit                                                                                                                                                        | 2/6   | Bit 7         | Bit 6             | Bit 5          | Bit 4          | Bit 3            | Bit 2           | Bit 1          | Bit 0         |

| PC7 OF I THE PC4 OF I PC3 OF I PC2 OF I THE I                                                                                                                                                        | 0050" | PC7 OE        | -                 | -              | PC4 OE         | PC3 OE           | PC2 OE          | -              | N/A<br>(JTAG) |

1. For each bit, 1 = pin drive is enabled as an output, 0 = pin drive is off (high-impedance, pin used as input)

## Table 199. Port D enable out register (address = $csiop + offset 1Bh)^{(1)}$

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2                 | Bit 1  | Bit 0 |

|-------|-------|-------|-------|-------|-----------------------|--------|-------|

| N/A   | N/A   | N/A   | N/A   | N/A   | PD2 OE <sup>(2)</sup> | PD1 OE | N/A   |

- 1. For each bit, 1 = pin drive is enabled as an output, 0 = pin drive is off (high-impedance, pin used as input)

- 2. Pin is not available on 52-pin UPSD34xx devices

assembly code example in *Table*, the PFQ will be loaded with the final instructions to command the MCU module to Power Down mode after the PDS Module goes to Power-Down mode. In this case, even though the code memory goes off-line in the PSD module, the last few MCU instruction are sourced from the PFQ.

### Forced power-down example

| PDOWN: | ANL  | A8h, #7Fh   | ; disable all interrupts                                                                                |

|--------|------|-------------|---------------------------------------------------------------------------------------------------------|

|        | ORL  | 9Dh, #C0h   | ; ensure PFQ and BC are enabled                                                                         |

|        | MOV  | DPTR, #xxC7 | ; load XDATA pointer to select PMMR3 register (xx = base ; address of csiop registers)                  |

|        | CLR  | Α           | : clear A                                                                                               |

|        | OLIT | / \         | , oldar 71                                                                                              |

|        | JMP  | LOOP        | ; first loop - fill PFQ/BQ with Power Down instructions                                                 |

|        | NOP  |             | ; second loop - fetch code from PFQ/BC and set Power-<br>; Down bits for PSD module and then MCU module |

| LOOP:  | MOVX | @DPTR, A    | ; set FORCE_PD Bit in PMMR3 in PSD module in second ; loop                                              |

|        | MOV  | 87h, A      | ; set PD Bit in PCON register in MCU module in second ; loop                                            |

|        | MOV  | A, #02h     | ; set power-down bit in the A register, but not in PMMR3 or ; PCON yet in first loop                    |

|        | JMP  | LOOP        | ; uPSD enters into Power-Down mode in second loop                                                       |

Figure 88. Automatic power-down (APD) unit

### 30 **Maximum rating**

Stressing the device above the rating listed in the absolute maximum ratings table may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents.

Table 205. Absolute maximum ratings

| Symbol                                               | Parameter                                                          | Min.  | Max. | Unit |

|------------------------------------------------------|--------------------------------------------------------------------|-------|------|------|

| T <sub>STG</sub>                                     | Storage temperature                                                | -65   | 125  | °C   |

| T <sub>LEAD</sub>                                    | Lead temperature during soldering (20 seconds max.) <sup>(1)</sup> | 411   | 235  | °C   |

| V <sub>IO</sub>                                      | Input and output voltage (Q = V <sub>OH</sub> or Hi-Z)             | -0.5  | 6.5  | V    |

| V <sub>CC</sub> , V <sub>DD</sub> , AV <sub>CC</sub> | Supply voltage                                                     | -0.5  | 6.5  | O V  |

| V <sub>ESD</sub>                                     | Electrostatic discharge voltage (human body model) <sup>(2)</sup>  | -2000 | 2000 | V    |

| ie Prof                                              | duct(s) obsolete                                                   |       |      |      |

Table 234. ISC timing (5 V PSD module) (continued)

| Symbol              | Parameter                               | Conditions | Min | Max | Unit |

|---------------------|-----------------------------------------|------------|-----|-----|------|

| t <sub>ISCPCO</sub> | ISC port clock to output                |            |     | 21  | ns   |

| t <sub>ISCPZV</sub> | ISC port high-impedance to valid output |            |     | 21  | ns   |

| t <sub>ISCPVZ</sub> | ISC port valid output to high-impedance |            |     | 21  | ns   |

- 1. For non-PLD programming, erase or in ISC bypass mode.

- 2. For program or erase PLD only.

Table 235. ISC timing (3 V PSD module)

| Symbol              | Parameter                                   | Conditions | Min | Max  | Unit |

|---------------------|---------------------------------------------|------------|-----|------|------|

| t <sub>ISCCF</sub>  | Clock (TCK, PC1) frequency (except for PLD) |            |     | 16   | MHz  |

| t <sub>ISCCH</sub>  | Clock (TCK, PC1) high time (except for PLD) | (1)        | 40  | CIL  | ns   |

| t <sub>ISCCL</sub>  | Clock (TCK, PC1) low time (except for PLD)  |            | 40  | ), o | ns   |

| t <sub>ISCCFP</sub> | Clock (TCK, PC1) frequency (PLD only)       |            | 0   | 4    | MHz  |

| t <sub>ISCCHP</sub> | Clock (TCK, PC1) high time (PLD only)       | (2)        | 90  | 115  | ns   |

| t <sub>ISCCLP</sub> | Clock (TCK, PC1) low time (PLD only)        | 18         | 90  | 10,, | ns   |

| t <sub>ISCPSU</sub> | ISC port setup time                         | 0          | -12 |      | ns   |

| t <sub>ISCPH</sub>  | ISC port hold up time                       | 0          | 5   |      | ns   |

| t <sub>ISCPCO</sub> | ISC port clock to output                    | LO.        |     | 30   | ns   |

| t <sub>ISCPZV</sub> | ISC port high-impedance to valid output     | 6)         |     | 30   | ns   |

| t <sub>ISCPVZ</sub> | ISC port valid output to high-impedance     |            |     | 30   | ns   |

- 1. For non-PLD programming, erase or in ISC bypass mode.

- 2. For program or erase PLD only.

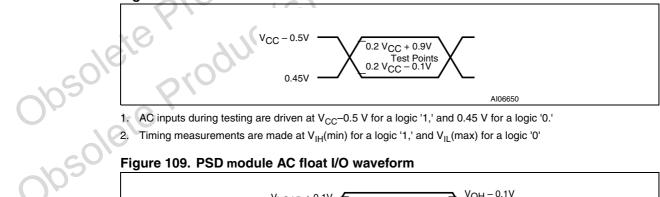

## Figure 108. MCU module AC measurement I/O waveform

- 1. AC inputs during testing are driven at  $V_{CC}$ =0.5 V for a logic '1,' and 0.45 V for a logic '0.'

- Timing measurements are made at V<sub>IH</sub>(min) for a logic '1,' and V<sub>IL</sub>(max) for a logic '0'

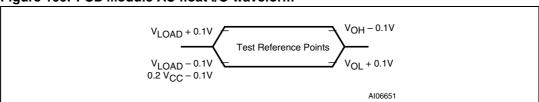

## Figure 109. PSD module AC float I/O waveform

- For timing purposes, a port pin is considered to be no longer floating when a 100 mV change from load voltage occurs, and begins to float when a 100 mV change from the loaded V<sub>OH</sub> or V<sub>OL</sub> level occurs

- 2.  $I_{OL}$  and  $I_{OH} \ge 20$  mA

## 34 Important notes

The following sections describe the limitations that apply to the UPSD34xx devices and the differences between revision A and B silicon.

## 34.1 USB interrupts with idle mode

## **Description**

An interrupt generated by a USB related event does not bring the MCU out of idle mode for processing.

## Impact on application

Idle mode cannot be used with USB.

### Workaround

Revision A - None identified at this time.

Revision B - Corrected in silicon so that a USB interrupt that occurs will bring the MCU out of idle mode.

## 34.2 USB reset interrupt

### **Description**

When the MCU clock prescaler is set to a value other than  $f_{MCU} = f_{OSC}$  (no division), a reset signal on the USB does not cause a USB interrupt to be generated.

## Impact on application

An MCU clock other than that equal to the frequency of the oscillator cannot be used.

### Workaround

Revision A - The CPUPS field in the CCON0 register must be set to 000b (default after reset). The 3400 USB firmware examples set CCON0 register to 000b.

Revision B - Corrected in silicon so that when an MCU clock prescaler is used, a reset signal on the USB does generate an interrupt.

## 34.3 USB reset

### **Description**

A USB reset does not reset the USB SIE's registers.

## Impact on application

A USB reset does not reset the USB SIE's registers as does a power-on or hardware reset.