Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

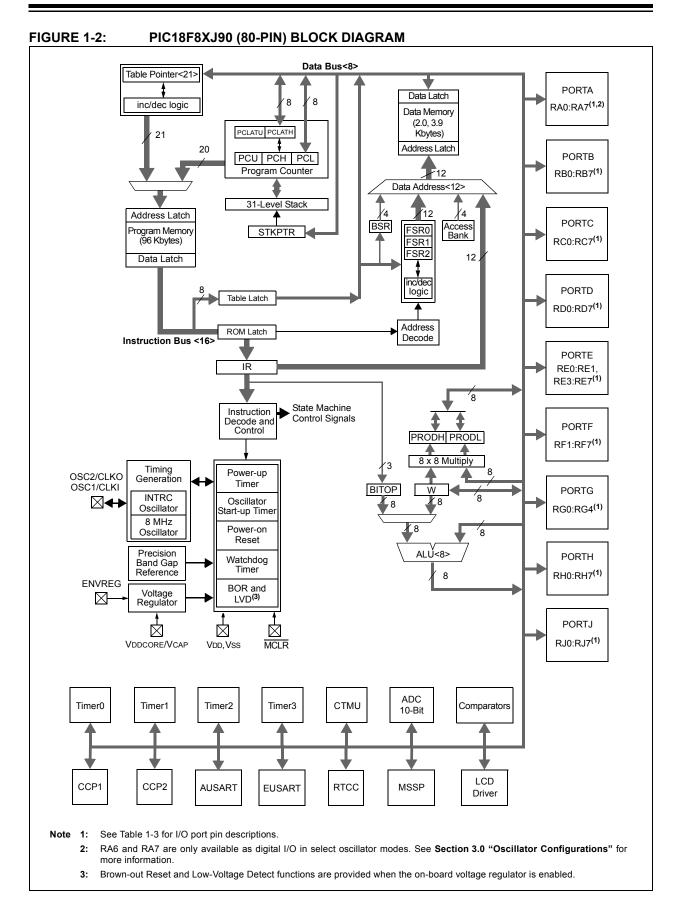

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

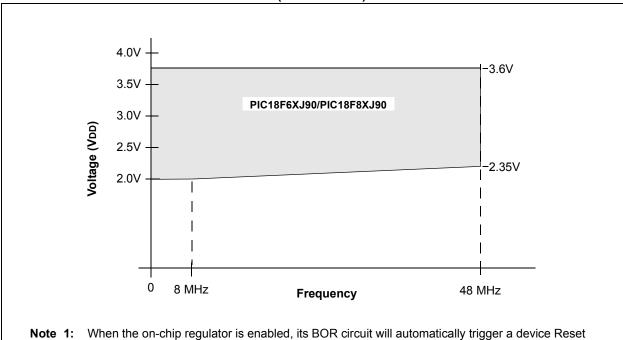

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LCD, LVD, POR, PWM, WDT                            |

| Number of I/O              | 67                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3.8K x 8                                                                   |

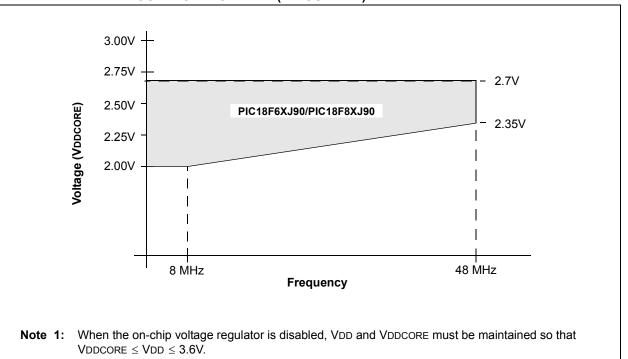

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                  |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f87j90-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                                                                                     | Pin Number       | Pin                                                      | Buffer                   | Description                                                                                                                          |  |  |  |

|----------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name                                                                                     | TQFP             | Туре                                                     | Туре                     | Description                                                                                                                          |  |  |  |

|                                                                                              |                  |                                                          |                          | PORTG is a bidirectional I/O port.                                                                                                   |  |  |  |

| RG0/LCDBIAS0<br>RG0<br>LCDBIAS0                                                              | 3                | I/O<br>I                                                 | ST<br>Analog             | Digital I/O.<br>BIAS0 input for LCD.                                                                                                 |  |  |  |

| RG1/TX2/CK2<br>RG1<br>TX2<br>CK2                                                             | 4                | I/O<br>O<br>I/O                                          | ST<br>—<br>ST            | Digital I/O.<br>AUSART asynchronous transmit.<br>AUSART synchronous clock (see related RX2/DT2).                                     |  |  |  |

| RG2/RX2/DT2/VLCAP1<br>RG2<br>RX2<br>DT2<br>VLCAP1                                            | 5                | I/O<br>I<br>I/O<br>I                                     | ST<br>ST<br>ST<br>Analog | Digital I/O.<br>AUSART asynchronous receive.<br>AUSART synchronous data (see related TX2/CK2).<br>LCD charge pump capacitor input.   |  |  |  |

| RG3/VLCAP2<br>RG3<br>VLCAP2                                                                  | 6                | I/O<br>I                                                 | ST<br>Analog             | Digital I/O.<br>g LCD charge pump capacitor input.                                                                                   |  |  |  |

| RG4/SEG26/RTCC<br>RG4<br>SEG26<br>RTCC                                                       | 8                | I/O<br>O<br>O                                            | ST<br>Analog<br>—        | Digital I/O.<br>SEG26 output for LCD.<br>RTCC output                                                                                 |  |  |  |

| Vss                                                                                          | 9, 25, 41, 56    | Р                                                        | _                        | Ground reference for logic and I/O pins.                                                                                             |  |  |  |

| Vdd                                                                                          | 26, 38, 57       | Р                                                        |                          | Positive supply for logic and I/O pins.                                                                                              |  |  |  |

| AVss                                                                                         | 20               | Р                                                        |                          | Ground reference for analog modules.                                                                                                 |  |  |  |

| AVdd                                                                                         | 19               | Р                                                        |                          | Positive supply for analog modules.                                                                                                  |  |  |  |

| ENVREG                                                                                       | 18               | Ι                                                        | ST                       | Enable for on-chip voltage regulator.                                                                                                |  |  |  |

| VDDCORE/VCAP<br>VDDCORE                                                                      | 10               | Р                                                        | _                        | Core logic power or external filter capacitor connection.<br>Positive supply for microcontroller core logic<br>(regulator disabled). |  |  |  |

| VCAP                                                                                         |                  | P — External filter capacitor connection (regulator enal |                          |                                                                                                                                      |  |  |  |

| <b>Legend:</b> TTL = TTL cc<br>ST = Schmi<br>I = Input<br>P = Power<br>$I^2C^{TM} = I^2C/SN$ | tt Trigger input | with C                                                   | MOS leve                 | CMOS = CMOS compatible input or output<br>Analog = Analog input<br>O = Output<br>OD = Open-Drain (no P diode to VDD)                 |  |  |  |

## TABLE 1-3: PIC18F6XJ90 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Default assignment for CCP2 when the CCP2MX Configuration bit is set.

2: Alternate assignment for CCP2 when the CCP2MX Configuration bit is cleared.

#### 7.5.2 FLASH PROGRAM MEMORY WRITE SEQUENCE (WORD PROGRAMMING).

The PIC18F87J90 family of devices has a feature that allows programming a single word (two bytes). This feature is enabled when the WPROG bit is set. If the memory location is already erased, the following sequence is required to enable this feature:

- 1. Load the Table Pointer register with the address of the data to be written

- 2. Write the 2 bytes into the holding registers and perform a table write

- 3. Set WPROG to enable single-word write.

- 4. Set WREN to enable write to memory.

- 5. Disable interrupts.

- 6. Write 55h to EECON2.

- 7. Write 0AAh to EECON2.

- 8. Set the WR bit. This will begin the write cycle.

- The CPU will stall for the duration of the write for Tiw (see parameter D133A).

- 10. Re-enable interrupts.

## EXAMPLE 7-4: SINGLE-WORD WRITE TO FLASH PROGRAM MEMORY

|                | MOVLW   | CODE_AI | DDR_UPPER | ; | Load TBLPTR with the base address |

|----------------|---------|---------|-----------|---|-----------------------------------|

|                | MOVWF   | TBLPTRU | U         |   |                                   |

|                | MOVLW   | CODE_AI | DDR_HIGH  |   |                                   |

|                | MOVWF   | TBLPTRI | H         |   |                                   |

|                | MOVLW   | CODE_AI | DDR_LOW   |   |                                   |

|                | MOVWF   | TBLPTRI | L         |   |                                   |

|                |         |         |           |   |                                   |

|                | MOVLW   | DATA0   |           |   |                                   |

|                | MOVWF   | TABLAT  |           |   |                                   |

|                | TBLWT*+ |         |           |   |                                   |

|                | MOVLW   | DATA1   |           |   |                                   |

|                | MOVWF   | TABLAT  |           |   |                                   |

|                | TBLWT*  |         |           |   |                                   |

|                |         |         |           |   |                                   |

|                |         |         |           |   |                                   |

| PROGRAM_MEMORY |         |         |           |   |                                   |

|                |         |         |           |   | enable single word write          |

|                |         | EECON1, |           |   | enable write to memory            |

|                |         | INTCON, | GIE       | ; | disable interrupts                |

|                | MOVLW   | 55h     |           |   |                                   |

| Required       |         | EECON2  |           | ; | write 55h                         |

| Sequence       | MOVLW   | 0AAh    |           |   |                                   |

|                |         | EECON2  |           |   | write OAAh                        |

|                |         | EECON1, |           |   | start program (CPU stall)         |

|                |         | INTCON, |           |   | re-enable interrupts              |

|                |         | EECON1, |           |   | disable single word write         |

|                | BCF     | EECON1, | WREN      | ; | disable write to memory           |

|                |         |         |           |   |                                   |

Example 8-3 shows the sequence to do a 16 x 16 unsigned multiplication. Equation 8-1 shows the algorithm that is used. The 32-bit result is stored in four registers (RES3:RES0).

#### EQUATION 8-1: 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 | = | into into into into into into into into  |

|-----------|---|------------------------------------------|

|           | = | $(ARG1H \bullet ARG2H \bullet 2^{16}) +$ |

|           |   | $(ARG1H \bullet ARG2L \bullet 2^8) +$    |

|           |   | $(ARG1L \bullet ARG2H \bullet 2^8) +$    |

|           |   | (ARG1L • ARG2L)                          |

|           |   | $(AROIL \bullet ARO2L)$                  |

## EXAMPLE 8-3: 16 x 16 UNSIGNED

## MULTIPLY ROUTINE

| 1 | MOVF   | ARG1L, W    |               |      |

|---|--------|-------------|---------------|------|

| I | MULWF  | ARG2L       | ; ARG1L * ARG | 2L-> |

|   |        |             | ; PRODH:PROD  | L    |

| 1 | MOVFF  | PRODH, RES1 | ;             |      |

| 1 | MOVFF  | PRODL, RESO | ;             |      |

| ; |        |             |               |      |

| 1 | MOVF   | ARG1H, W    |               |      |

| 1 | MULWF  | ARG2H       | ; ARG1H * ARG | 2H-> |

|   |        |             | ; PRODH:PROD  | L    |

| 1 | MOVFF  | PRODH, RES3 | ;             |      |

| I | MOVFF  | PRODL, RES2 | ;             |      |

| ; |        |             |               |      |

| 1 | MOVF   | ARG1L, W    |               |      |

| 1 | MULWF  | ARG2H       | ; ARG1L * ARG | 2H-> |

|   |        |             | ; PRODH:PROD  | L    |

| 1 | MOVF   | PRODL, W    | ;             |      |

|   | ADDWF  | RES1, F     | ; Add cross   |      |

| 1 | MOVF   |             | ; products    |      |

|   | ADDWFC | RES2, F     | ;             |      |

|   | CLRF   | WREG        | ;             |      |

|   | ADDWFC | RES3, F     | ;             |      |

| ; |        |             |               |      |

| 1 | MOVF   | ARG1H, W    | ;             |      |

| 1 | MULWF  | ARG2L       | ; ARG1H * ARG | 2L-> |

|   |        |             | ; PRODH:PROD  | L    |

| 1 | MOVF   | PRODL, W    | ;             |      |

|   | ADDWF  | RES1, F     | ; Add cross   |      |

| 1 | MOVF   | PRODH, W    | ; products    |      |

|   | ADDWFC | RES2, F     | ;             |      |

|   | CLRF   | WREG        | ;             |      |

|   | ADDWFC | RES3, F     | ;             |      |

| 1 |        |             |               |      |

Example 8-4 shows the sequence to do a 16 x 16 signed multiply. Equation 8-2 shows the algorithm used. The 32-bit result is stored in four registers (RES3:RES0). To account for the sign bits of the arguments, the MSb for each argument pair is tested and the appropriate subtractions are done.

#### EQUATION 8-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

| RES3:RES0= | ARG1H:ARG1L • ARG2H:ARG2L                                       |

|------------|-----------------------------------------------------------------|

| =          | $(ARG1H \bullet ARG2H \bullet 2^{16}) +$                        |

|            | $(ARG1H \bullet ARG2L \bullet 2^8) +$                           |

|            | $(ARG1L \bullet ARG2H \bullet 2^8) +$                           |

|            | $(ARG1L \bullet ARG2L) +$                                       |

|            | $(-1 \bullet ARG2H < 7 > \bullet ARG1H:ARG1L \bullet 2^{16}) +$ |

|            | $(-1 \bullet ARG1H < 7 > \bullet ARG2H: ARG2L \bullet 2^{16})$  |

#### EXAMPLE 8-4: 16 x 16 SIGNED MULTIPLY ROUTINE

| MOVF ARG1L, W<br>MULWF ARG2L ; ARG1L * ARG2L -><br>; PRODH:PRODL         |   |

|--------------------------------------------------------------------------|---|

|                                                                          |   |

|                                                                          |   |

|                                                                          |   |

| MOVFF PRODH, RES1 ;                                                      |   |

| MOVFF PRODL, RESO ;                                                      |   |

| i                                                                        |   |

| MOVF ARG1H, W                                                            |   |

| MULWF ARG2H ; ARG1H * ARG2H ->                                           |   |

| ; PRODH:PRODL                                                            |   |

| MOVFF PRODH, RES3 ;                                                      |   |

| MOVFF PRODL, RES2 ;                                                      |   |

| ;                                                                        |   |

| MOVF ARG1L, W                                                            |   |

| MULWF ARG2H ; ARG1L * ARG2H ->                                           |   |

| inclui inclui inclui inclui i                                            |   |

| MOVF PRODL, W ;                                                          |   |

| ADDWF RES1, F ; Add cross                                                |   |

| MOVF PRODH, W ; products                                                 |   |

| ADDWFC RES2, F ;                                                         |   |

| CLRF WREG ;                                                              |   |

| ADDWFC RES3, F ;                                                         |   |

| ;                                                                        |   |

| MOVF ARG1H, W ;                                                          |   |

| MULWF ARG2L ; ARG1H * ARG2L ->                                           |   |

| ; PRODH:PRODL                                                            |   |

| MOVF PRODL, W ;                                                          |   |

| ADDWF RES1, F ; Add cross                                                |   |

| MOVF PRODH, W ; products                                                 |   |

| ADDWFC RES2, F ;                                                         |   |

| CLRF WREG ;                                                              |   |

| ADDWFC RES3, F ;                                                         |   |

|                                                                          |   |

| BTFSS ARG2H, 7 ; ARG2H:ARG2L neg?                                        | , |

| ;<br>BTFSS ARG2H, 7 ; ARG2H:ARG2L neg?<br>BRA SIGN_ARG1 ; no, check ARG1 |   |

| MOVF ARG1L, W ;                                                          |   |

| SUBWF RES2 ;                                                             |   |

| MOVF ARG1H, W ;                                                          |   |

| SUBWFB RES3                                                              |   |

| ;                                                                        |   |

| ,<br>SIGN_ARG1                                                           |   |

| BTFSS ARG1H, 7 ; ARG1H:ARG1L neg?                                        | , |

| BRA CONT_CODE ; no, done                                                 |   |

| MOVF ARG2L, W ;                                                          |   |

| SUBWF RES2 ;                                                             |   |

| MOVF ARG2H, W ;                                                          |   |

| SUBWFB RES3                                                              |   |

| :                                                                        |   |

| ,<br>CONT_CODE                                                           |   |

|                                                                          |   |

|                                                                          |   |

| bit 7<br>Legend:<br>R = Readable bit<br>-n = Value at POR<br>bit 7 RB<br>1 =<br>0 =<br>bit 6 INT<br>1 = | PU: PORT<br>All PORT<br>PORTB p<br>EDG0: Ext                    | INTEDG1<br>W = Writable t<br>'1' = Bit is set<br>B Pull-up Enab<br>B pull-ups are o<br>ull-ups are ena<br>ternal Interrupt | le bit<br>disabled        | U = Unimplem<br>'0' = Bit is clea |       | INT3IP<br>d as '0'<br>x = Bit is unkn | RBIP<br>bit |  |  |  |  |

|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------------------------|-------|---------------------------------------|-------------|--|--|--|--|

| Legend:<br>R = Readable bit<br>-n = Value at POR<br>bit 7 RB<br>1 =<br>0 =<br>bit 6 INT<br>1 =          | PU: PORT<br>All PORT<br>PORTB p<br>EDG0: Ext                    | '1' = Bit is set<br>B Pull-up Enab<br>B pull-ups are o<br>ull-ups are ena                                                  | le bit<br>disabled        | -                                 |       |                                       |             |  |  |  |  |

| R = Readable bit<br>-n = Value at POR<br>bit 7 RB<br>1 =<br>0 =<br>bit 6 INT<br>1 =                     | PU: PORT<br>All PORT<br>PORTB p<br>EDG0: Ext                    | '1' = Bit is set<br>B Pull-up Enab<br>B pull-ups are o<br>ull-ups are ena                                                  | le bit<br>disabled        | -                                 |       |                                       | own         |  |  |  |  |

| bit 7 <b>RB</b><br>1 =<br>0 =<br>bit 6 <b>INT</b><br>1 =                                                | PU: PORT<br>All PORT<br>PORTB p<br>EDG0: Ext                    | '1' = Bit is set<br>B Pull-up Enab<br>B pull-ups are o<br>ull-ups are ena                                                  | le bit<br>disabled        | -                                 |       |                                       | own         |  |  |  |  |

| bit 7 <b>RB</b><br>1 =<br>0 =<br>bit 6 <b>INT</b><br>1 =                                                | PU: PORT<br>All PORT<br>PORTB p<br>EDG0: Ext                    | B Pull-up Enab<br>B pull-ups are o<br>ull-ups are ena                                                                      | disabled                  | ʻ0' = Bit is clea                 | ared  | x = Bit is unkn                       | own         |  |  |  |  |

| 1 =<br>0 =<br>bit 6 INT<br>1 =                                                                          | All PORT<br>PORTB p<br>EDG0: Ext                                | B pull-ups are o<br>ull-ups are ena                                                                                        | disabled                  |                                   |       |                                       |             |  |  |  |  |

| 1 =<br>0 =<br>bit 6 INT<br>1 =                                                                          | All PORT<br>PORTB p<br>EDG0: Ext                                | B pull-ups are o<br>ull-ups are ena                                                                                        | disabled                  |                                   |       |                                       |             |  |  |  |  |

| bit 6 INT<br>1 =                                                                                        | EDG0: Ex                                                        | •                                                                                                                          | ماتينا المستحيية المسالية |                                   |       |                                       |             |  |  |  |  |

| 1 =                                                                                                     |                                                                 | ternal Interrupt                                                                                                           | iblea by individ          | dual port latch v                 | alues |                                       |             |  |  |  |  |

|                                                                                                         | Interrupt of                                                    |                                                                                                                            | 0 Edge Select             | t bit                             |       |                                       |             |  |  |  |  |

| 0 =                                                                                                     |                                                                 | on rising edge                                                                                                             |                           |                                   |       |                                       |             |  |  |  |  |

|                                                                                                         |                                                                 | on falling edge                                                                                                            |                           |                                   |       |                                       |             |  |  |  |  |

|                                                                                                         |                                                                 | ternal Interrupt                                                                                                           | 1 Edge Select             | t bit                             |       |                                       |             |  |  |  |  |

|                                                                                                         |                                                                 | rupt on rising edge<br>rupt on falling edge                                                                                |                           |                                   |       |                                       |             |  |  |  |  |

|                                                                                                         |                                                                 | •••                                                                                                                        | 2 Edge Select             | t bit                             |       |                                       |             |  |  |  |  |

|                                                                                                         |                                                                 | xternal Interrupt 2 Edge Select bit<br>on rising edge                                                                      |                           |                                   |       |                                       |             |  |  |  |  |

|                                                                                                         |                                                                 | on falling edge                                                                                                            |                           |                                   |       |                                       |             |  |  |  |  |

| bit 3 INT                                                                                               | EDG3: Ext                                                       | ternal Interrupt                                                                                                           | 3 Edge Select             | t bit                             |       |                                       |             |  |  |  |  |

| 1 =                                                                                                     | Interrupt of                                                    | on rising edge                                                                                                             |                           |                                   |       |                                       |             |  |  |  |  |

| 0 =                                                                                                     | Interrupt of                                                    | errupt on falling edge                                                                                                     |                           |                                   |       |                                       |             |  |  |  |  |

| bit 2 TM                                                                                                | ROIP: TMF                                                       | R0 Overflow Inte                                                                                                           | errupt Priority           | bit                               |       |                                       |             |  |  |  |  |

|                                                                                                         | High prior                                                      |                                                                                                                            |                           |                                   |       |                                       |             |  |  |  |  |

|                                                                                                         | Low prior                                                       | •                                                                                                                          |                           |                                   |       |                                       |             |  |  |  |  |

|                                                                                                         |                                                                 | External Interru                                                                                                           | ipt Priority bit          |                                   |       |                                       |             |  |  |  |  |

|                                                                                                         | <ul> <li>1 = High priority</li> <li>0 = Low priority</li> </ul> |                                                                                                                            |                           |                                   |       |                                       |             |  |  |  |  |

|                                                                                                         | -                                                               | t Change Interi                                                                                                            | runt Priority bit         |                                   |       |                                       |             |  |  |  |  |

|                                                                                                         | High prior                                                      | •                                                                                                                          | upt i nonty bit           |                                   |       |                                       |             |  |  |  |  |

|                                                                                                         | Low prior                                                       |                                                                                                                            |                           |                                   |       |                                       |             |  |  |  |  |

|                                                                                                         | ·                                                               | -                                                                                                                          |                           |                                   |       |                                       |             |  |  |  |  |

#### REGISTER 9-2: INTCON2: INTERRUPT CONTROL REGISTER 2

**Note:** Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global interrupt enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

## 9.6 INTx Pin Interrupts

External interrupts on the RB0/INT0, RB1/INT1, RB2/INT2 and RB3/INT3 pins are edge-triggered. If the corresponding INTEDGx bit in the INTCON2 register is set (= 1), the interrupt is triggered by a rising edge; if the bit is clear, the trigger is on the falling edge. When a valid edge appears on the RBx/INTx pin, the corresponding flag bit, INTxIF, is set. This interrupt can be disabled by clearing the corresponding enable bit, INTxIE. Flag bit, INTxIF, must be cleared in software in the Interrupt Service Routine before re-enabling the interrupt.

All external interrupts (INT0, INT1, INT2 and INT3) can wake-up the processor from the power-managed modes if bit, INTxIE, was set prior to going into the power-managed modes. If the Global Interrupt Enable bit, GIE, is set, the processor will branch to the interrupt vector following wake-up.

Interrupt priority for INT1, INT2 and INT3 is determined by the value contained in the Interrupt Priority bits, INT1IP (INTCON3<6>), INT2IP (INTCON3<7>) and INT3IP (INTCON2<1>). There is no priority bit associated with INT0. It is always a high-priority interrupt source.

### 9.7 TMR0 Interrupt

In 8-bit mode (which is the default), an overflow in the TMR0 register (FFh  $\rightarrow$  00h) will set flag bit, TMR0IF. In 16-bit mode, an overflow in the TMR0H:TMR0L register pair (FFFFh  $\rightarrow$  0000h) will set TMR0IF. The interrupt can be enabled/disabled by setting/clearing enable bit, TMR0IE (INTCON<5>). Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit, TMR0IP (INTCON2<2>). See Section 11.0 "Timer0 Module" for further details on the Timer0 module.

## 9.8 **PORTB Interrupt-on-Change**

An input change on PORTB<7:4> sets flag bit, RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit, RBIE (INTCON<3>). Interrupt priority for PORTB interrupt-on-change is determined by the value contained in the interrupt priority bit, RBIP (INTCON2<0>).

## 9.9 Context Saving During Interrupts

During interrupts, the return PC address is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the Fast Return Stack. If a fast return from interrupt is not used (see **Section 6.3 "Data Memory Organization"**), the user may need to save the WREG, STATUS and BSR registers on entry to the Interrupt Service Routine (ISR). Depending on the user's application, other registers may also need to be saved. Example 9-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

| EXAMPLE 9-1: | SAVING STATUS, WREG AND BSR REGISTERS IN RAM |

|--------------|----------------------------------------------|

|--------------|----------------------------------------------|

| MOVWF<br>MOVFF<br>MOVFF<br>; | W_TEMP<br>STATUS, STATUS_TEMP<br>BSR, BSR_TEMP    | ; W_TEMP is in virtual bank<br>; STATUS_TEMP located anywhere<br>; BSR_TMEP located anywhere |

|------------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------|

| ; USER                       | ISR CODE                                          |                                                                                              |

| ,<br>MOVFF<br>MOVF<br>MOVFF  | BSR_TEMP, BSR<br>W_TEMP, W<br>STATUS_TEMP, STATUS | ; Restore BSR<br>; Restore WREG<br>; Restore STATUS                                          |

| Pin Name     | Pin Name Function Set |   | I/O | l/O<br>Type          | Description                                                                                                    |  |  |  |

|--------------|-----------------------|---|-----|----------------------|----------------------------------------------------------------------------------------------------------------|--|--|--|

| RC0/T1OSO/   | RC0                   | 0 | 0   | DIG                  | LATC<0> data output.                                                                                           |  |  |  |

| T13CKI       |                       | 1 | -   | ST                   | PORTC<0> data input.                                                                                           |  |  |  |

|              | T10S0                 | x | 0   | ANA                  | Timer1 oscillator output; enabled when Timer1 oscillator enabled. Disables digital I/O and LCD segment driver. |  |  |  |

|              | T13CKI                | 1 | Ι   | ST                   | Timer1/Timer3 counter input.                                                                                   |  |  |  |

| RC1/T1OSI/   | RC1                   | 0 | 0   | DIG                  | LATC<1> data output.                                                                                           |  |  |  |

| CCP2/SEG32   |                       | 1 | Ι   | ST                   | PORTC<1> data input.                                                                                           |  |  |  |

|              | T10SI                 | x | Ι   | ANA                  | Timer1 oscillator input.                                                                                       |  |  |  |

|              | CCP2 <sup>(1)</sup>   | 0 | 0   | DIG                  | CCP2 compare/PWM output.                                                                                       |  |  |  |

|              |                       | 1 | Ι   | ST                   | CCP2 capture input.                                                                                            |  |  |  |

|              | SEG32                 | x | 0   | ANA                  | LCD Segment 32 output; disables all other pin functions.                                                       |  |  |  |

| RC2/CCP1/    | RC2                   | 0 | 0   | DIG                  | LATC<2> data output.                                                                                           |  |  |  |

| SEG13        |                       | 1 | Ι   | ST                   | PORTC<2> data input.                                                                                           |  |  |  |

|              | CCP1                  | 0 | 0   | DIG                  | CCP1 compare/PWM output; takes priority over port data.                                                        |  |  |  |

|              |                       | 1 | Ι   | ST                   | CCP1 capture input.                                                                                            |  |  |  |

|              | SEG13                 | x | 0   | ANA                  | LCD Segment 13 output; disables all other pin functions.                                                       |  |  |  |

|              |                       | 0 | DIG | LATC<3> data output. |                                                                                                                |  |  |  |

| SEG17        |                       | 1 | -   | ST                   | PORTC<3> data input.                                                                                           |  |  |  |

|              | SCK                   | 0 | 0   | DIG                  | SPI clock output (MSSP module); takes priority over port data.                                                 |  |  |  |

|              |                       | 1 | Ι   | ST                   | SPI clock input (MSSP module).                                                                                 |  |  |  |

|              | SCL                   | 0 | 0   | DIG                  | I <sup>2</sup> C <sup>™</sup> clock output (MSSP module); takes priority over port data.                       |  |  |  |

|              |                       | 1 | Ι   | I2C                  | I <sup>2</sup> C clock input (MSSP module); input type depends on module setting.                              |  |  |  |

|              | SEG17                 | x | 0   | ANA                  | LCD Segment 17 output; disables all other pin functions.                                                       |  |  |  |

| RC4/SDI/SDA/ | RC4                   | 0 | 0   | DIG                  | LATC<4> data output.                                                                                           |  |  |  |

| SEG16        |                       | 1 | Ι   | ST                   | PORTC<4> data input.                                                                                           |  |  |  |

|              | SDI                   |   | Ι   | ST                   | SPI data input (MSSP module).                                                                                  |  |  |  |

|              | SDA                   | 1 | 0   | DIG                  | I <sup>2</sup> C data output (MSSP module); takes priority over port data.                                     |  |  |  |

|              |                       | 1 | Ι   | I2C                  | I <sup>2</sup> C data input (MSSP module); input type depends on module setting.                               |  |  |  |

|              | SEG16                 | x | 0   | ANA                  | LCD Segment 16 output; disables all other pin functions.                                                       |  |  |  |

| RC5/SDO/     | RC5                   | 0 | 0   | DIG                  | LATC<5> data output.                                                                                           |  |  |  |

| SEG12        |                       | 1 | Ι   | ST                   | PORTC<5> data input.                                                                                           |  |  |  |

|              | SDO                   | 0 | 0   | DIG                  | SPI data output (MSSP module).                                                                                 |  |  |  |

|              | SEG12                 | x | 0   | ANA                  | LCD Segment 12 output; disables all other pin functions.                                                       |  |  |  |

| RC6/TX1/CK1/ | RC6                   | 0 | 0   | DIG                  | LATC<6> data output.                                                                                           |  |  |  |

| SEG27        |                       | 1 | Ι   | ST                   | PORTC<6> data input.                                                                                           |  |  |  |

|              | TX1                   | 1 | 0   | DIG                  | Synchronous serial data output (EUSART module); takes priority over port data.                                 |  |  |  |

|              | CK1                   | 1 | 0   | DIG                  | Synchronous serial data input (EUSART module); user must configure as an input                                 |  |  |  |

|              |                       | 1 | I   | ST                   | Synchronous serial clock input (EUSART module).                                                                |  |  |  |

|              | SEG27                 | x | 0   | ANA                  | LCD Segment 27 output; disables all other pin functions.                                                       |  |  |  |

| RC7/RX1/DT1/ | RC7                   | 0 | 0   | DIG                  | LATC<7> data output.                                                                                           |  |  |  |

| SEG28        |                       | 1 | Ι   | ST                   | PORTC<7> data input.                                                                                           |  |  |  |

|              | RX1                   | 1 | I   | ST                   | Asynchronous serial receive data input (EUSART module).                                                        |  |  |  |

|              | DT1                   | 1 | 0   | DIG                  | Synchronous serial data output (EUSART module); takes priority over port data.                                 |  |  |  |

|              |                       | 1 | Ι   | ST                   | Synchronous serial data input (EUSART module); user must configure as an input                                 |  |  |  |

|              | SEG28                 | x | 0   | ANA                  | LCD Segment 28 output; disables all other pin functions.                                                       |  |  |  |

## TABLE 10-7: PORTC FUNCTIONS

**Legend:** O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Trigger Buffer Input, TTL = TTL Buffer Input,  $I2C = I^2C/SMBus$  Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

**Note 1:** Default assignment for CCP2 when CCP2MX Configuration bit is set.

#### 15.1.1 RTCC CONTROL REGISTERS

## **REGISTER 15-1: RTCCFG: RTCC CONFIGURATION REGISTER<sup>(1)</sup>**

| R/W-0                | U-0                                                                                                                                 | R/W-0                                                                              | R-0                    | R-0                                   | R/W-0          | R/W-0            | R/W-0          |  |  |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------|---------------------------------------|----------------|------------------|----------------|--|--|--|

| RTCEN <sup>(2)</sup> |                                                                                                                                     | RTCWREN                                                                            | RTCSYNC                | HALFSEC <sup>(3)</sup>                | RTCOE          | RTCPTR1          | RTCPTR0        |  |  |  |

| oit 7                |                                                                                                                                     |                                                                                    |                        |                                       |                |                  | bit (          |  |  |  |

|                      |                                                                                                                                     |                                                                                    |                        |                                       |                |                  |                |  |  |  |

| Legend:              | hit                                                                                                                                 | \// - \//ritabla                                                                   | hit.                   | II – Unimplom                         | opted bit rea  | d oo 'O'         |                |  |  |  |

| R = Readable         |                                                                                                                                     | W = Writable<br>'1' = Bit is set                                                   |                        | U = Unimplem                          |                |                  |                |  |  |  |

| n = Value at         | PUR                                                                                                                                 | I = BILIS SEL                                                                      |                        | '0' = Bit is clea                     | irea           | x = Bit is unkr  | IOWN           |  |  |  |

| bit 7                | RTCEN: RTC                                                                                                                          | C Enable bit <sup>(2)</sup>                                                        | )                      |                                       |                |                  |                |  |  |  |

|                      |                                                                                                                                     | odule is enable                                                                    |                        |                                       |                |                  |                |  |  |  |

|                      | 0 = RTCC m                                                                                                                          | odule is disable                                                                   | ed                     |                                       |                |                  |                |  |  |  |

| bit 6                | Unimplemen                                                                                                                          | ted: Read as '                                                                     | 0'                     |                                       |                |                  |                |  |  |  |

| bit 5                | RTCWREN:                                                                                                                            | RTCC Value Re                                                                      | egisters Write         | Enable bit                            |                |                  |                |  |  |  |

|                      |                                                                                                                                     |                                                                                    | U U                    | an be written to l                    |                |                  |                |  |  |  |

|                      | 0 = RTCVAL                                                                                                                          | H and RTCVAL                                                                       | L registers ar         | e locked out fro                      | m being writte | en to by the use | r              |  |  |  |

| oit 4                |                                                                                                                                     |                                                                                    | •                      | Synchronizatior                       |                |                  |                |  |  |  |

|                      |                                                                                                                                     | H, RTCVALL and ALRMRPT registers can change while reading due to a rollover ripple |                        |                                       |                |                  |                |  |  |  |

|                      | resulting in an invalid data read. If the register is read twice and results in the same data, the data can be assumed to be valid. |                                                                                    |                        |                                       |                |                  |                |  |  |  |

|                      |                                                                                                                                     |                                                                                    |                        | PT registers ca                       | n be read wit  | thout concern o  | over a rollove |  |  |  |

|                      | ripple                                                                                                                              | ,                                                                                  |                        | 0                                     |                |                  |                |  |  |  |

| bit 3                | HALFSEC: ⊦                                                                                                                          | lalf-Second Sta                                                                    | tus bit <sup>(3)</sup> |                                       |                |                  |                |  |  |  |

|                      |                                                                                                                                     | half period of a                                                                   |                        |                                       |                |                  |                |  |  |  |

|                      |                                                                                                                                     | period of a sec                                                                    |                        |                                       |                |                  |                |  |  |  |

| bit 2                |                                                                                                                                     | RTCOE: RTCC Output Enable bit                                                      |                        |                                       |                |                  |                |  |  |  |

|                      | <ul> <li>1 = RTCC clock output enabled</li> <li>0 = RTCC clock output disabled</li> </ul>                                           |                                                                                    |                        |                                       |                |                  |                |  |  |  |

|                      |                                                                                                                                     | -                                                                                  |                        |                                       |                |                  |                |  |  |  |

| bit 1-0              |                                                                                                                                     |                                                                                    | -                      | ndow Pointer bit                      |                |                  | /ALL registers |  |  |  |

|                      |                                                                                                                                     |                                                                                    |                        | gisters when rea<br>every read or wri |                |                  |                |  |  |  |

|                      | RTCVALH:                                                                                                                            |                                                                                    |                        |                                       |                |                  |                |  |  |  |

|                      | 00 = Minutes                                                                                                                        |                                                                                    |                        |                                       |                |                  |                |  |  |  |

|                      | 01 = Weekda                                                                                                                         | ıy                                                                                 |                        |                                       |                |                  |                |  |  |  |

|                      | 10 = Month                                                                                                                          |                                                                                    |                        |                                       |                |                  |                |  |  |  |

|                      | 11 = Reserve                                                                                                                        | a                                                                                  |                        |                                       |                |                  |                |  |  |  |

|                      | RTCVALL:<br>00 = Second:                                                                                                            | e                                                                                  |                        |                                       |                |                  |                |  |  |  |

|                      | 01 = Hours                                                                                                                          | <u> </u>                                                                           |                        |                                       |                |                  |                |  |  |  |

|                      | 10 <b>= Day</b>                                                                                                                     |                                                                                    |                        |                                       |                |                  |                |  |  |  |

|                      | 11 = Year                                                                                                                           |                                                                                    |                        |                                       |                |                  |                |  |  |  |

|                      | e RTCCFG regi<br>en if the device                                                                                                   |                                                                                    | cted by a PO           | R. For resets ot                      | her than POR   | , RTCC will con  | tinue to run   |  |  |  |

- 2: A write to the RTCEN bit is only allowed when RTCWREN = 1.

- **3:** This bit is read-only; it is cleared to '0' on a write to the lower half of the MINSEC register.

| FIGURE 15-6:    | TIMER PULSE GENERATION |

|-----------------|------------------------|

| RTCEN b         | it                     |

| ALRMEN b        | it                     |

| RTCC Alarm Ever | nt / / /               |

| RTCC Pi         |                        |

## 15.4 Sleep Mode

The timer and alarm continue to operate while in Sleep mode. The operation of the alarm is not affected by Sleep, as an alarm event can always wake-up the CPU.

The Idle mode does not affect the operation of the timer or alarm.

## 15.5 Reset

#### 15.5.1 DEVICE RESET

When a device Reset occurs, the ALCFGRPT register is forced to its Reset state causing the alarm to be disabled (if enabled prior to the Reset). If the RTCC was enabled, it will continue to operate when a basic device Reset occurs.

#### 15.5.2 POWER-ON RESET (POR)

The RTCCFG and ALRMRPT registers are reset only on a POR. Once the device exits the POR state, the clock registers should be reloaded with the desired values.

The timer prescaler values can be reset only by writing to the SECONDS register. No device Reset can affect the prescalers.

#### 16.4.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR2L register and CCP2CON<5:4> bits.

- Make the CCP2 pin an output by clearing the appropriate TRIS bit.

- 4. Set the TMR2 prescale value, then enable Timer2 by writing to T2CON.

- 5. Configure the CCP2 module for PWM operation.

| Name    | Bit 7                                    | Bit 6        | Bit 5    | Bit 4    | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Reset<br>Values<br>on Page |

|---------|------------------------------------------|--------------|----------|----------|----------|--------|---------|---------|----------------------------|

| INTCON  | GIE/GIEH                                 | PEIE/GIEL    | TMR0IE   | INT0IE   | RBIE     | TMR0IF | INT0IF  | RBIF    | 59                         |

| RCON    | IPEN                                     | _            | CM       | RI       | TO       | PD     | POR     | BOR     | 60                         |

| PIR1    | —                                        | ADIF         | RC1IF    | TX1IF    | SSPIF    | _      | TMR2IF  | TMR1IF  | 62                         |

| PIE1    | _                                        | ADIE         | RC1IE    | TX1IE    | SSPIE    |        | TMR2IE  | TMR1IE  | 62                         |

| IPR1    | _                                        | ADIP         | RC1IP    | TX1IP    | SSPIP    | -      | TMR2IP  | TMR1IP  | 62                         |

| TRISC   | TRISC7                                   | TRISC6       | TRISC5   | TRISC4   | TRISC3   | TRISC2 | TRISC1  | TRISC0  | 62                         |

| TRISE   | TRISE7                                   | TRISE6       | TRISE5   | TRISE4   | TRISE3   |        | TRISE1  | TRISE0  | 62                         |

| TRISG   | SPIOD                                    | CCP2OD       | CCP10D   | TRISG4   | TRISG3   | TRISG2 | TRISG1  | TRISG0  | 62                         |

| TMR2    | Timer2 Reg                               | gister       |          |          |          |        |         |         | 60                         |

| PR2     | Timer2 Per                               | iod Register |          |          |          |        |         |         | 60                         |

| T2CON   | _                                        | T2OUTPS3     | T2OUTPS2 | T2OUTPS1 | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | 60                         |

| CCPR1L  | Capture/Compare/PWM Register 1 Low Byte  |              |          |          |          |        |         | 63      |                            |

| CCPR1H  | Capture/Compare/PWM Register 1 High Byte |              |          |          |          |        |         | 63      |                            |

| CCP1CON | _                                        | _            | DC1B1    | DC1B0    | CCP1M3   | CCP1M2 | CCP1M1  | CCP1M0  | 63                         |

| CCPR2L  | Capture/Compare/PWM Register 2 Low Byte  |              |          |          |          |        |         | 64      |                            |

| CCPR2H  | Capture/Compare/PWM Register 2 High Byte |              |          |          |          |        |         | 63      |                            |

| CCP2CON |                                          |              | DC2B1    | DC2B0    | CCP2M3   | CCP2M2 | CCP2M1  | CCP2M0  | 64                         |

## TABLE 16-5: REGISTERS ASSOCIATED WITH PWM AND TIMER2

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PWM or Timer2.

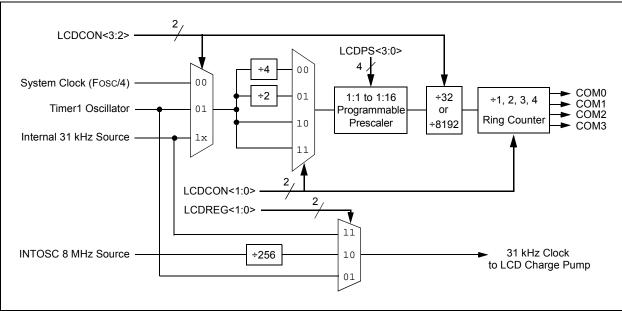

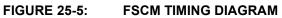

## 17.2 LCD Clock Source

The LCD driver module generates its internal clock from 3 possible sources:

- System clock (Fosc/4)

- · Timer1 oscillator

- INTRC source

The LCD clock generator uses a configurable divide-by-32/divide-by-8192 postscaler to produce a baseline frequency of about 1 kHz nominal, regardless of the source selected. The clock source selection and the postscaler configuration are determined by the Clock Source Select bits, CS<1:0> (LCDCON<3:2>).

An additional programmable prescaler is used to derive the LCD frame frequency from the 1 kHz baseline. The prescaler is configured using the LP<3:0> bits (LCDPS<3:0>) for any one of 16 options, ranging from 1:1 to 1:16.

Proper timing for waveform generation is set by the LMUX<1:0> bits (LCDCON<1:0>). These bits determine which Commons Multiplexing mode is to be used and divide down the LCD clock source as required. They also determine the configuration of the ring counter that is used to switch the LCD commons on or off.

#### 17.2.1 LCD VOLTAGE REGULATOR CLOCK SOURCE

In addition to the clock source for LCD timing, a separate 31 kHz nominal clock is required for the LCD charge pump. This is provided from a distinct branch of the LCD clock source.

The charge pump clock can use either the Timer1 oscillator or the INTRC source, as well as the 8 MHz INTOSC source (after being divided by 256 by a prescaler). The charge pump clock source is configured using the CKSEL<1:0> bits (LCDREG<1:0>).

## 17.2.2 CLOCK SOURCE CONSIDERATIONS

When using the system clock as the LCD clock source, it is assumed that the system clock frequency is a nominal 32 MHz (for a Fosc/4 frequency of 8 MHz). Because the prescaler option for the Fosc/4 clock selection is fixed at divide-by-8192, system clock speeds that differ from 32 MHz will produce frame frequencies and refresh rates different than discussed in this chapter. The user will need to keep this in mind when designing the display application.

The Timer1 and INTRC sources can be used as LCD clock sources when the device is in Sleep mode. To use the Timer1 oscillator, it is necessary to set the T1OSCEN bit (T1CON<3>). Selecting either Timer1 or INTRC as the LCD clock source will not automatically activate these sources.

Similarly, selecting the INTOSC as the charge pump clock source will not turn the oscillator on. To use INTOSC, it must be selected as the system clock source by using the FOSC2 Configuration bit.

If Timer1 is used as a clock source for the device, either as an LCD clock source or for any other purpose, LCD segment 32 become unavailable.

#### FIGURE 17-2: LCD CLOCK GENERATION

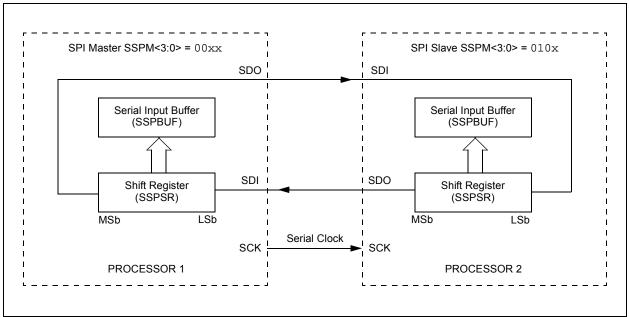

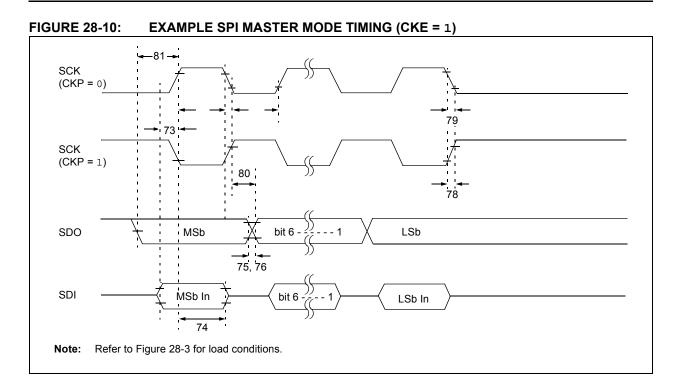

#### 18.3.3 ENABLING SPI I/O

To enable the serial port, the MSSP Enable bit, SSPEN (SSPCON1<5>), must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, reinitialize the SSPCON registers and then set the SSPEN bit. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed as follows:

- SDI is automatically controlled by the SPI module

- SDO must have TRISC<5> bit cleared

- SCK (Master mode) must have TRISC<3> bit cleared

- SCK (Slave mode) must have TRISC<3> bit set

- SS must have TRISF<7> bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

#### 18.3.4 OPEN-DRAIN OUTPUT OPTION

The drivers for the SDO output and SCK clock pins can be optionally configured as open-drain outputs. This feature allows the voltage level on the pin to be pulled to a higher level through an external pull-up resistor, and allows the output to communicate with external circuits without the need for additional level shifters.

The open-drain output option is controlled by the SPIOD bit (TRISG<7>). Setting this bit configures both pins for open-drain operation.

## 18.3.5 TYPICAL CONNECTION

Figure 18-2 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- · Master sends data Slave sends dummy data

- · Master sends data Slave sends data

- Master sends dummy data Slave sends data

#### FIGURE 18-2: SPI MASTER/SLAVE CONNECTION

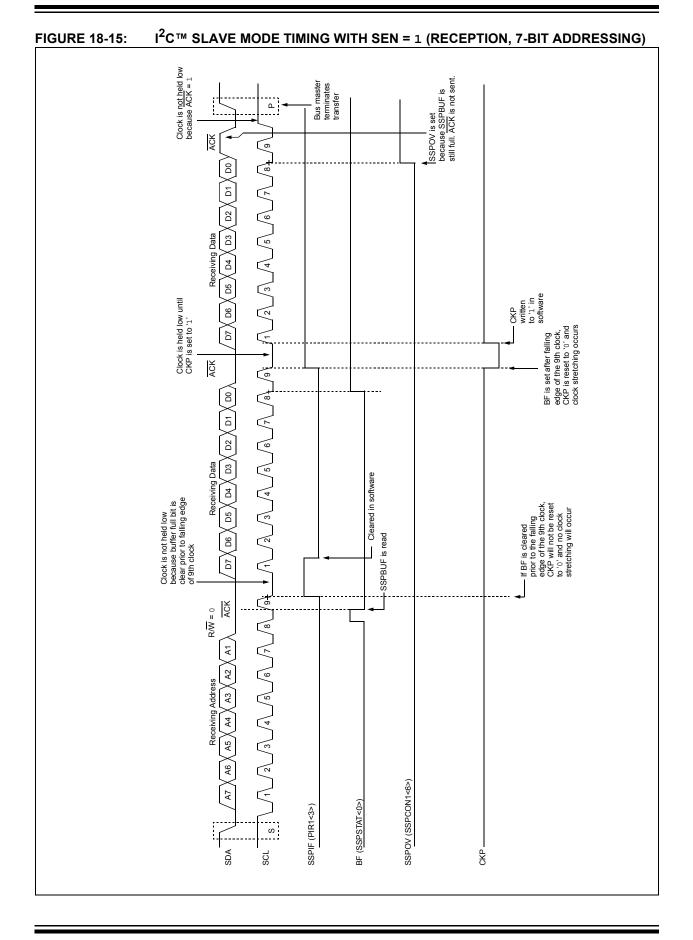

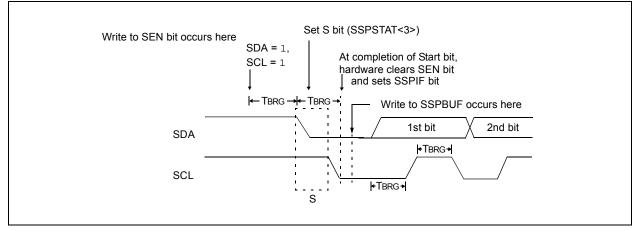

## 18.4.8 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition, the user sets the Start Enable bit, SEN (SSPCON2<0>). If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA pin being driven low while SCL is high is the Start condition and causes the S bit (SSPSTAT<3>) to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit (SSPCON2<0>) will be automatically cleared by hardware. The Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

Note: If, at the beginning of the Start condition, the SDA and SCL pins are already sampled low, or if during the Start condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs. The Bus Collision Interrupt Flag, BCLIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its Idle state.

#### 18.4.8.1 WCOL Status Flag

If the user writes the SSPBUF when a Start sequence is in progress, the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

**Note:** Because queueing of events is not allowed, writing to the lower 5 bits of SSPCON2 is disabled until the Start condition is complete.

#### FIGURE 18-21: FIRST START BIT TIMING

## 24.3.2 CAPACITANCE CALIBRATION

There is a small amount of capacitance from the internal A/D Converter sample capacitor as well as stray capacitance from the circuit board traces and pads that affect the precision of capacitance measurements. A measurement of the stray capacitance can be taken by making sure the desired capacitance to be measured has been removed. The measurement is then performed using the following steps:

- 1. Initialize the A/D Converter and the CTMU.

- 2. Set EDG1STAT (= 1).

- 3. Wait for a fixed delay of time, t.

- 4. Clear EDG1STAT.

- 5. Perform an A/D conversion.

- 6. Calculate the stray and A/D sample capacitances:

$$COFFSET = CSTRAY + CAD = (I \cdot t)/V$$

where I is known from the current source measurement step, t is a fixed delay and V is measured by performing an A/D conversion.

This measured value is then stored and used for calculations of time measurement or subtracted for capacitance measurement. For calibration, it is expected that the capacitance of CSTRAY + CAD is approximately known; CAD is approximately 4 pF.

An iterative process may need to be used to adjust the time, t, that the circuit is charged to obtain a reasonable voltage reading from the A/D Converter. The value of t may be determined by setting COFFSET to a theoretical value, then solving for t. For example, if CSTRAY is theoretically calculated to be 11 pF, and V is expected to be 70% of VDD, or 2.31V, then t would be:

$$(4 \text{ pF} + 11 \text{ pF}) \cdot 2.31 \text{V}/0.55 \text{ }\mu\text{A}$$

or 63 µs.

See Example 24-3 for a typical routine for CTMU capacitance calibration.

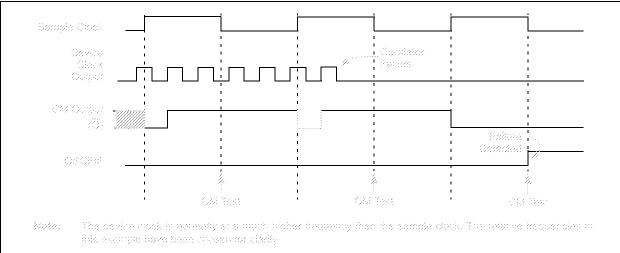

## 25.5.2 EXITING FAIL-SAFE OPERATION

The Fail-Safe condition is terminated by either a device Reset or by entering a power-managed mode. On Reset, the controller starts the primary clock source specified in Configuration Register 2H (with any required start-up delays that are required for the oscillator mode, such as the OST or PLL timer). The INTRC oscillator provides the device clock until the primary clock source becomes ready (similar to a Two-Speed Start-up). The clock source is then switched to the primary clock (indicated by the OSTS bit in the OSCCON register becoming set). The Fail-Safe Clock Monitor then resumes monitoring the peripheral clock.

The primary clock source may never become ready during start-up. In this case, operation is clocked by the INTOSC multiplexor. The OSCCON register will remain in its Reset state until a power-managed mode is entered.

#### 25.5.3 FSCM INTERRUPTS IN POWER-MANAGED MODES

By entering a power-managed mode, the clock multiplexor selects the clock source selected by the OSCCON register. Fail-Safe Clock Monitoring of the power-managed clock source resumes in the power-managed mode.

If an oscillator failure occurs during power-managed operation, the subsequent events depend on whether or not the oscillator failure interrupt is enabled. If enabled (OSCFIF = 1), code execution will be clocked by the INTRC multiplexor. An automatic transition back to the failed clock source will not occur.

## 25.5.4 POR OR WAKE-UP FROM SLEEP

The FSCM is designed to detect oscillator failure at any point after the device has exited Power-on Reset (POR) or low-power Sleep mode. When the primary device clock is either EC or INTRC mode, monitoring can begin immediately following these events.

For HS or HSPLL modes, the situation is somewhat different. Since the oscillator may require a start-up time considerably longer than the FSCM sample clock time, a false clock failure may be detected. To prevent this, the internal oscillator block is automatically configured as the device clock and functions until the primary clock is stable (the OST and PLL timers have timed out). This is identical to Two-Speed Start-up mode. Once the primary clock is stable, the INTRC returns to its role as the FSCM source.

Note: The same logic that prevents false oscillator failure interrupts on POR, or wake from Sleep, will also prevent the detection of the oscillator's failure to start at all following these events. This can be avoided by monitoring the OSTS bit and using a timing routine to determine if the oscillator is taking too long to start. Even so, no oscillator failure interrupt will be flagged.

As noted in Section 25.4.1 "Special Considerations for Using Two-Speed Start-up", it is also possible to select another clock configuration and enter an alternate power-managed mode while waiting for the primary clock to become stable. When the new power-managed mode is selected, the primary clock is disabled.

## 26.2.2 EXTENDED INSTRUCTION SET

| ADD       | FSR            | Add Liter        | Add Literal to FSR                    |       |        |           |  |  |  |

|-----------|----------------|------------------|---------------------------------------|-------|--------|-----------|--|--|--|

| Synta     | ax:            | ADDFSR           | ADDFSR f, k                           |       |        |           |  |  |  |

| Operands: |                | $0 \le k \le 63$ | $0 \le k \le 63$                      |       |        |           |  |  |  |